Page 1

S530 Parametric Test System

Test Subroutine Library User’s Manual

S530-907-01 Rev. A / September 2015

www.keithley.com

*PS53090701A*

S530-907-01A

A Greater Measure of Condence

A Tektr onix Company

Page 2

Test Subroutine Library

S530 Parametric Test System

User's Manual

© 2015, Keithley Instruments

Cleveland, Ohio, U.S.A.

All rights reserved.

Any unauthorized reproduction, photocopy, or use of the information herein, in whole or in part,

without the prior written approval of Keithley Instruments is strictly prohibited.

All Keithley Instruments product names are trademarks or registered trademarks of Keithley

Instruments. Other brand names are trademarks or registered trademarks of their respective

holders.

Document number: S530-907-01 Rev. A / September 2015

Page 3

Safety precautions

The following safety precautions should be observed before using this product and any associated instrumentation. Although

some instruments and accessories would normally be used with nonhazardous voltages, there are situations where hazardous

conditions may be present.

This product is intended for use by qualified personnel who recognize shock hazards and are familiar with the safety precautions

required to avoid possible injury. Read and follow all installation, operation, and maintenance information carefully before using

the product. Refer to the user documentation for complete product specifications.

If the product is used in a manner not specified, the protection provided by the product warranty may be impaired.

The types of product users are:

Responsible body is the individual or group responsible for the use and maintenance of equipment, for ensuring that the

equipment is operated within its specifications and operating limits, and for ensuring that operators are adequately trained.

Operators use the product for its intended function. They must be trained in electrical safety procedures and proper use of the

instrument. They must be protected from electric shock and contact with hazardous live circuits.

Maintenance personnel perform routine procedures on the product to keep it operating properly, for example, setting the line

voltage or replacing consumable materials. Maintenance procedures are described in the user documentation. The procedures

explicitly state if the operator may perform them. Otherwise, they should be performed only by service personnel.

Service personnel are trained to work on live circuits, perform safe installations, and repair products. Only properly trained

service personnel may perform installation and service procedures.

Keithley Instruments products are designed for use with electrical signals that are measurement, control, and data I/O

connections, with low transient overvoltages, and must not be directly connected to mains voltage or to voltage sources with high

transient overvoltages. Measurement Category II (as referenced in IEC 60664) connections require protection for high transient

overvoltages often associated with local AC mains connections. Certain Keithley measuring instruments may be connected to

mains. These instruments will be marked as category II or higher.

Unless explicitly allowed in the specifications, operating manual, and instrument labels, do not connect any instrument to mains.

Exercise extreme caution when a shock hazard is present. Lethal voltage may be present on cable connector jacks or test

fixtures. The American National Standards Institute (ANSI) states that a shock hazard exists when voltage levels greater than

30 V RMS, 42.4 V peak, or 60 VDC are present. A good safety practice is to expect that hazardous voltage is present in any

unknown circuit before measuring.

Operators of this product must be protected from electric shock at all times. The responsible body must ensure that operators

are prevented access and/or insulated from every connection point. In some cases, connections must be exposed to potential

human contact. Product operators in these circumstances must be trained to protect themselves from the risk of electric shock. If

the circuit is capable of operating at or above 1000 V, no conductive part of the circuit may be exposed.

Do not connect switching cards directly to unlimited power circuits. They are intended to be used with impedance-limited

sources. NEVER connect switching cards directly to AC mains. When connecting sources to switching cards, install protective

devices to limit fault current and voltage to the card.

Before operating an instrument, ensure that the line cord is connected to a properly-grounded power receptacle. Inspect the

connecting cables, test leads, and jumpers for possible wear, cracks, or breaks before each use.

When installing equipment where access to the main power cord is restricted, such as rack mounting, a separate main input

power disconnect device must be provided in close proximity to the equipment and within easy reach of the operator.

For maximum safety, do not touch the product, test cables, or any other instruments while power is applied to the circuit under

test. ALWAYS remove power from the entire test system and discharge any capacitors before: connecting or disconnecting

cables or jumpers, installing or removing switching cards, or making internal changes, such as installing or removing jumpers.

Do not touch any object that could provide a current path to the common side of the circuit under test or power line (earth)

ground. Always make measurements with dry hands while standing on a dry, insulated surface capable of withstanding the

voltage being measured.

Page 4

For safety, instruments and accessories must be used in accordance with the operating instructions. If the instruments or

accessories are used in a manner not specified in the operating instructions, the protection provided by the equipment may be

impaired.

Do not exceed the maximum signal levels of the instruments and accessories, as defined in the specifications and operating

information, and as shown on the instrument or test fixture panels, or switching card.

When fuses are used in a product, replace with the same type and rating for continued protection against fire hazard.

Chassis connections must only be used as shield connections for measuring circuits, NOT as protective earth (safety ground)

connections.

If you are using a test fixture, keep the lid closed while power is applied to the device under test. Safe operation requires the use

of a lid interlock.

If a screw is present, connect it to protective earth (safety ground) using the wire recommended in the user documentation.

The symbol on an instrument means caution, risk of danger. The user must refer to the operating instructions located in the

user documentation in all cases where the symbol is marked on the instrument.

The symbol on an instrument means caution, risk of electric shock. Use standard safety precautions to avoid personal

contact with these voltages.

The symbol on an instrument shows that the surface may be hot. Avoid personal contact to prevent burns.

The symbol indicates a connection terminal to the equipment frame.

If this symbol is on a product, it indicates that mercury is present in the display lamp. Please note that the lamp must be

properly disposed of according to federal, state, and local laws.

The WARNING heading in the user documentation explains dangers that might result in personal injury or death. Always read

the associated information very carefully before performing the indicated procedure.

The CAUTION heading in the user documentation explains hazards that could damage the instrument. Such damage may

invalidate the warranty.

Instrumentation and accessories shall not be connected to humans.

Before performing any maintenance, disconnect the line cord and all test cables.

To maintain protection from electric shock and fire, replacement components in mains circuits — including the power

transformer, test leads, and input jacks — must be purchased from Keithley Instruments. Standard fuses with applicable national

safety approvals may be used if the rating and type are the same. Other components that are not safety-related may be

purchased from other suppliers as long as they are equivalent to the original component (note that selected parts should be

purchased only through Keithley Instruments to maintain accuracy and functionality of the product). If you are unsure about the

applicability of a replacement component, call a Keithley Instruments office for information.

To clean an instrument, use a damp cloth or mild, water-based cleaner. Clean the exterior of the instrument only. Do not apply

cleaner directly to the instrument or allow liquids to enter or spill on the instrument. Products that consist of a circuit board with

no case or chassis (e.g., a data acquisition board for installation into a computer) should never require cleaning if handled

according to instructions. If the board becomes contaminated and operation is affected, the board should be returned to the

factory for proper cleaning/servicing.

Safety precaution revision as of January 2013.

Page 5

General information .................................................................................................. 1-1

Table of Contents

Introduction .......................................................................................................................... 1-1

Manual contents ................................................................................................................... 1-1

Contact information .............................................................................................................. 1-1

Using the test subroutine library ............................................................................. 2-1

How to use the library reference .......................................................................................... 2-1

Categorized subroutine lists ................................................................................................. 2-2

Bipolar subroutines ................................................................................................................... 2-3

Resistors, diodes, capacitors, and special structure subroutines .............................................. 2-4

MOSFET subroutines ................................................................................................................ 2-4

FET and JFET subroutines ....................................................................................................... 2-5

Math and support subroutines ................................................................................................... 2-5

Test subroutine library reference ............................................................................ 3-1

Subroutine descriptions........................................................................................................ 3-1

beta1 ......................................................................................................................................... 3-1

beta2 ......................................................................................................................................... 3-3

beta2a ....................................................................................................................................... 3-4

beta3a ....................................................................................................................................... 3-6

bice ........................................................................................................................................... 3-8

bkdn .......................................................................................................................................... 3-9

bvcbo ...................................................................................................................................... 3-10

bvcbo1 .................................................................................................................................... 3-11

bvceo ...................................................................................................................................... 3-13

bvceo2 .................................................................................................................................... 3-14

bvces ....................................................................................................................................... 3-15

bvces1 ..................................................................................................................................... 3-16

bvdss ....................................................................................................................................... 3-17

bvdss1 ..................................................................................................................................... 3-19

bvebo ...................................................................................................................................... 3-20

cap .......................................................................................................................................... 3-21

deltl1 ....................................................................................................................................... 3-23

deltw1 ...................................................................................................................................... 3-24

ev ............................................................................................................................................ 3-25

fimv ......................................................................................................................................... 3-27

fnddat ...................................................................................................................................... 3-28

fndtrg ....................................................................................................................................... 3-29

fvmi ......................................................................................................................................... 3-29

gamma1 .................................................................................................................................. 3-31

gd ............................................................................................................................................ 3-32

gm ........................................................................................................................................... 3-34

ibic1 ......................................................................................................................................... 3-35

icbo ......................................................................................................................................... 3-37

iceo ......................................................................................................................................... 3-38

ices .......................................................................................................................................... 3-39

id1 ........................................................................................................................................... 3-40

idsat ........................................................................................................................................ 3-42

idss .......................................................................................................................................... 3-43

iebo ......................................................................................................................................... 3-44

idvsvg ...................................................................................................................................... 3-45

Page 6

Table of Contents S530 Parametric Test System Test Subroutine Library User's Manual

isubmx ..................................................................................................................................... 3-46

kdelay ...................................................................................................................................... 3-47

leak ......................................................................................................................................... 3-48

logstp ...................................................................................................................................... 3-49

rcsat ........................................................................................................................................ 3-50

re ............................................................................................................................................. 3-53

res ........................................................................................................................................... 3-55

res2 ......................................................................................................................................... 3-56

res4 ......................................................................................................................................... 3-57

resv ......................................................................................................................................... 3-58

rvdp ......................................................................................................................................... 3-59

tdelay ...................................................................................................................................... 3-60

tox ........................................................................................................................................... 3-61

vbes ........................................................................................................................................ 3-62

vf ............................................................................................................................................. 3-63

vg2 .......................................................................................................................................... 3-64

vgsat ....................................................................................................................................... 3-66

vp ............................................................................................................................................ 3-67

vp1 .......................................................................................................................................... 3-69

vt14 ......................................................................................................................................... 3-70

vtati ......................................................................................................................................... 3-71

vtext ........................................................................................................................................ 3-73

vtext2 ...................................................................................................................................... 3-76

vtext3 ...................................................................................................................................... 3-78

Index ........................................................................................................................... I-1

Page 7

In this section:

Introduction .............................................................................. 1-1

Manual contents ....................................................................... 1-1

Contact information .................................................................. 1-1

Section 1

General information

Introduction

The S530 Test Subroutine Library (PARLib) is a parameter extraction and data analysis software

system. The PARLib subroutines are used to analyze data associated with S530 parametric tests.

This manual contains detailed descriptions of the S530 PARLib subroutines. It is intended as a

reference guide for experienced users.

Manual contents

This manual is organized into the following sections:

General information: A definition of what the S530 Test Subroutine Library (PARLib) is, the

organization of the manual, and how you can contact us if you have questions.

Using the test subroutine library: Information about how the descriptions of the subroutines are

presented and a categorized list of the subroutines with links to the individual subroutine

descriptions.

Test subroutine library reference: Detailed information about each of the subroutines, in

alphabetical order. Descriptions include subroutine purpose, usage (syntax and parameters),

information about placement and relationship to other subroutines, and schematics (where

applicable).

Contact information

If you have any questions after you review the information in this documentation, please contact your

local Keithley Instruments office, sales partner, or distributor. You can also call Keithley Instruments

corporate headquarters (toll-free inside the U.S. and Canada only) at 1-800-935-5595, or from

outside the U.S. at +1-440-248-0400. For worldwide contact numbers, visit the Keithley website

(http://www.keithley.com).

Page 8

In this section:

How to use the library reference .............................................. 2-1

Categorized subroutine lists ..................................................... 2-2

Section 2

Using the test subroutine library

How to use the library reference

The subroutines in the Test subroutine library reference (on page 3-1) are in the C programming

language. Each subroutine is presented in a standard format that follows the pattern below:

Purpose statement: The first line of text under the subroutine heading contains a brief

explanation of what the subroutine does.

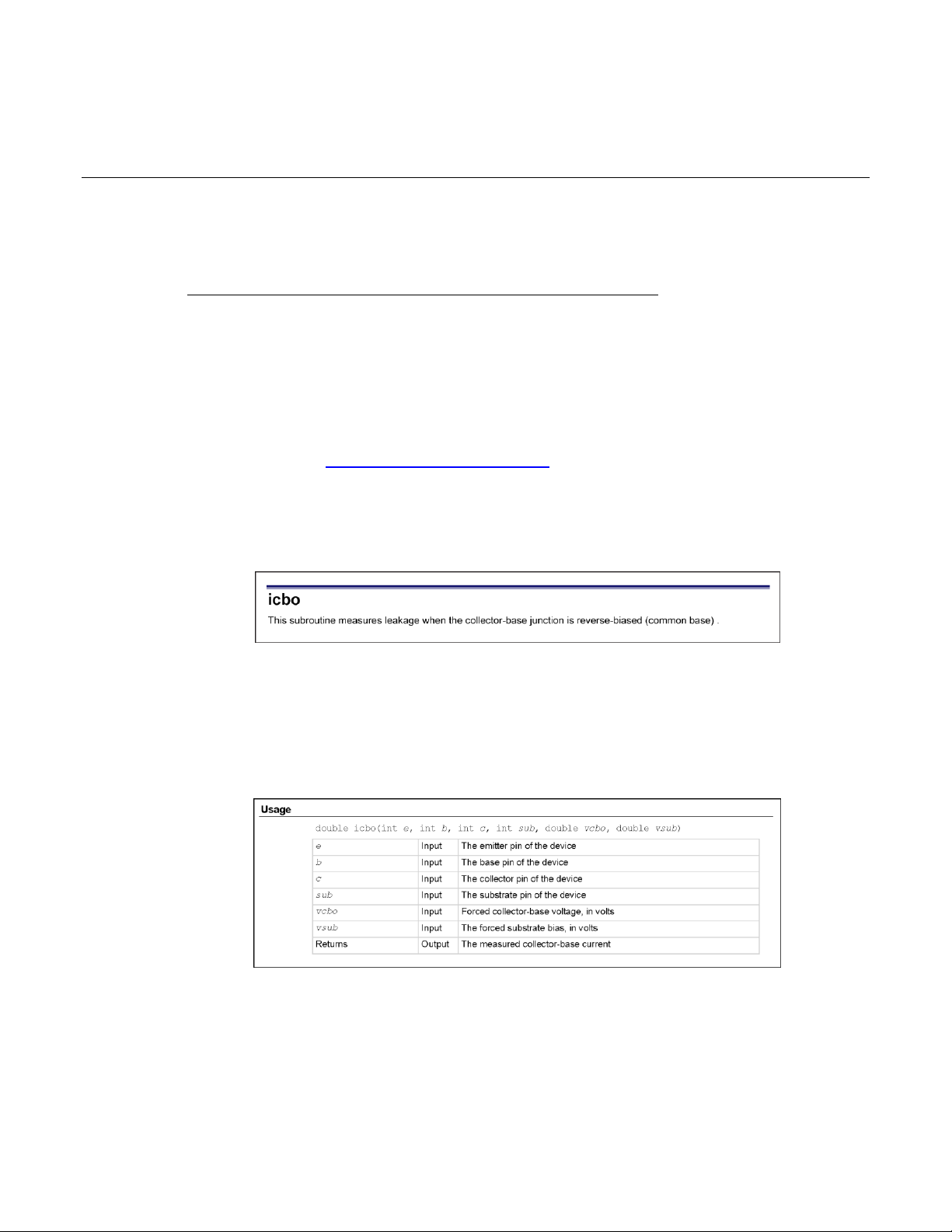

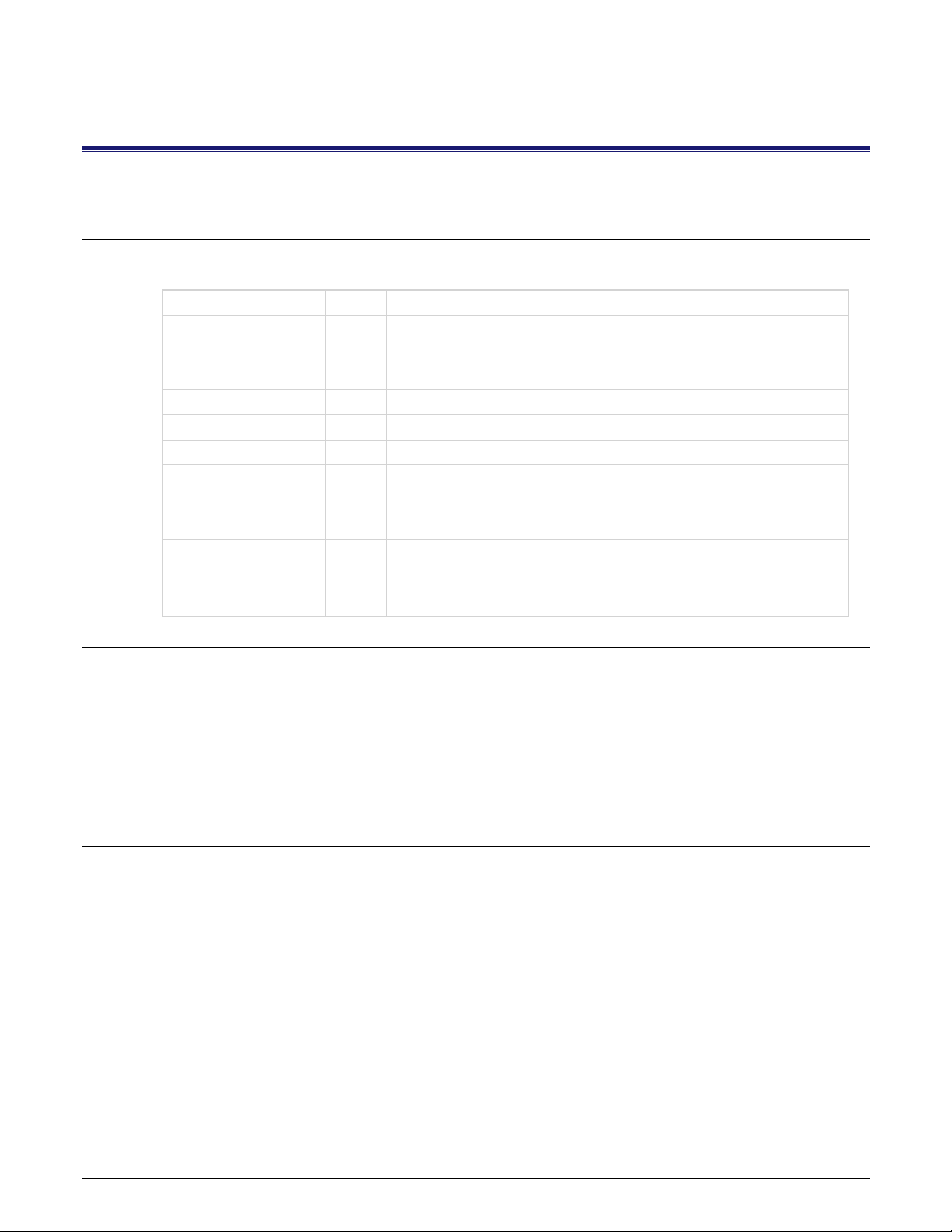

Figure 1: Example purpose statement

Usage: A line of code representing the prototype of the subroutine, followed by a table listing the

input and output parameters for the subroutine. Parameters that you specify are shown in

monospace italic font; parameters preceded by an asterisk (*) are pointers to information

that is returned. Each parameter is preceded by one of the following declarations that specifies

the data type for the parameter: int (integer), double (double-precision floating-point), and

char (a single character value).

Figure 2: Example syntax and parameter definition

Page 9

Section 2: Using the test subroutine library S530 Parametric Test System Test Subroutine Library User's Manual

2-2 S530-907-01 Rev. A / September 2015

Details: Additional information about using the subroutine.

Figure 3: Example details

V/I polarities: The polarities of the current or voltage flow between the pins of the device; based

on whether you are using an NPN or PNP transistor. This information is only applicable in some

subroutines.

Figure 4: Example V/I polarities information

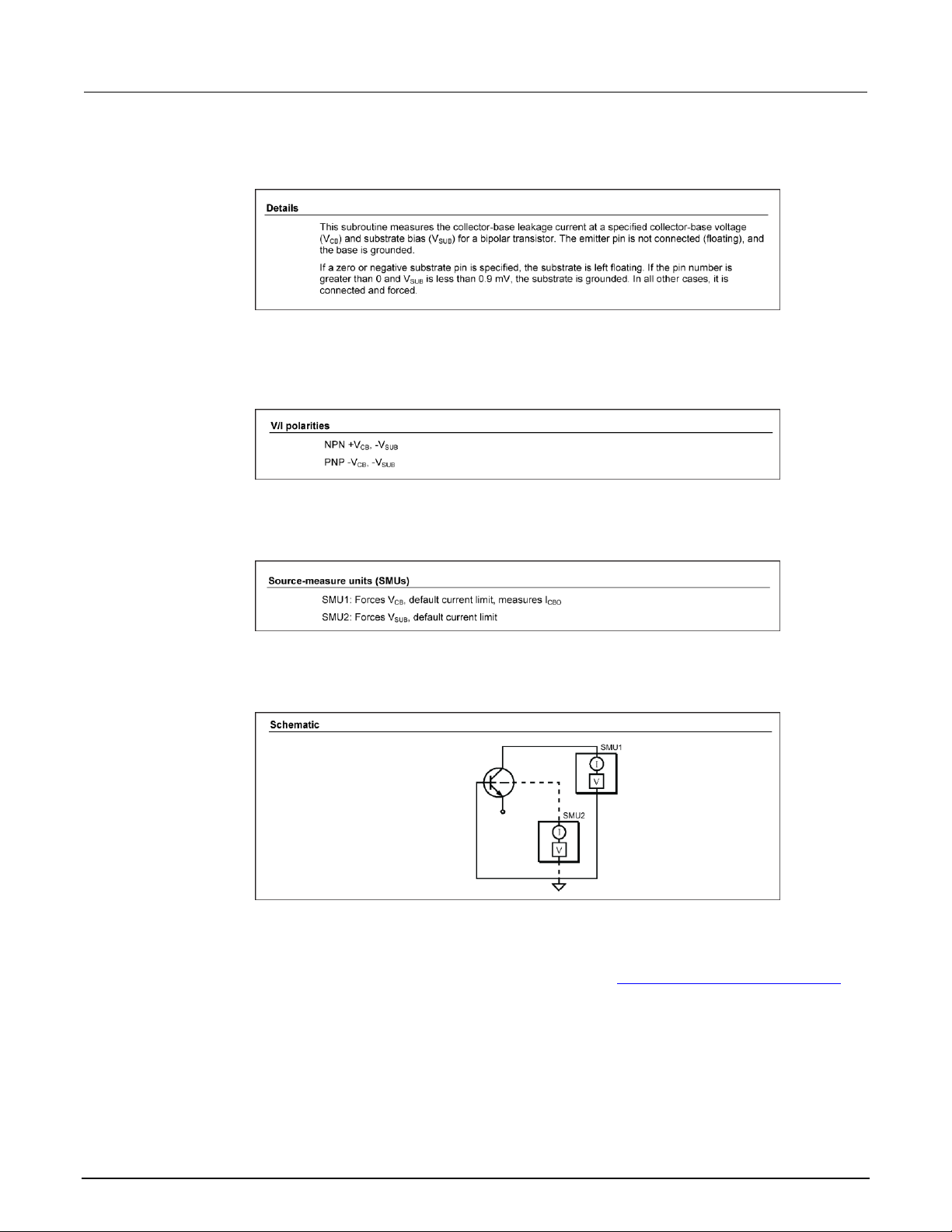

Source-measure units (SMUs): A description of what each SMU in the test configuration does in

the subroutine. This information is only applicable in some subroutines.

Figure 5: Example SMUs description

Schematic: A simplified schematic showing the configuration of the instruments and devices for

the subroutine. This information is only applicable in some subroutines.

Figure 6: Example schematic

Categorized subroutine lists

The subroutine descriptions are listed in alphabetical order in the Test subroutine library reference

(on page 3-1) section of this manual. The tables that follow contain all of the subroutines grouped by

function, with a brief description of the purpose of the subroutine and a hyperlink to the full subroutine

description.

Page 10

S530 Parametric Test System Test Subroutine Library User's Manual Section 2: Using the test subroutine library

S530-907-01 Rev. A / September 2015 2-3

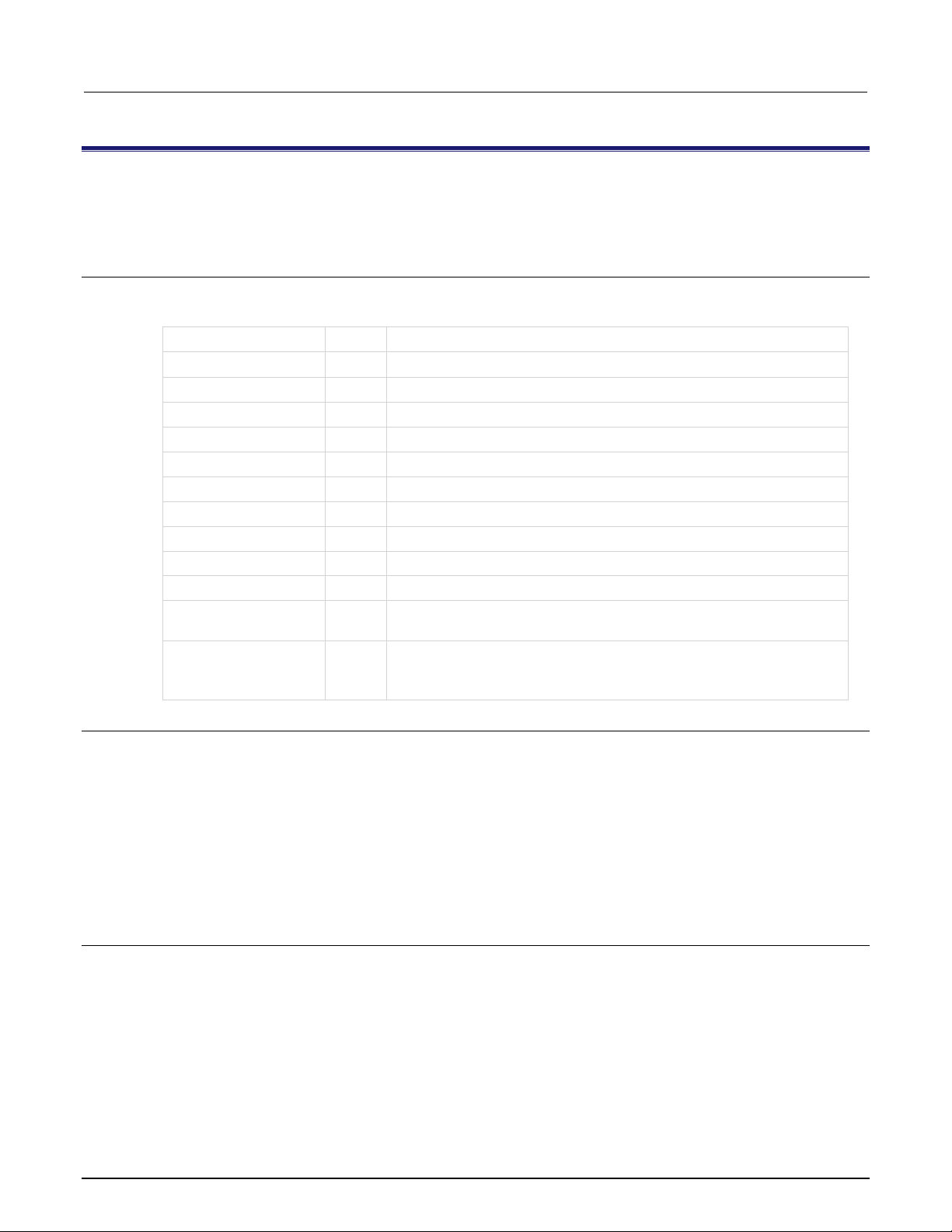

Bipolar subroutines

Subroutine

Description

Link

beta1

Calculate DC at specified IE and VCB

beta1 (on page 3-1)

beta2

Calculate DC and VBE at specified IC and

VCE

beta2 (on page 3-3)

beta2a

Calculate at VCB and ICE with search on IE

beta2a (on page 3-4)

beta3a

Calculate at VCE and ICE with search on IBE

beta3a (on page 3-6)

bice

Calculate when VBE swept, at VCE and V

SUB

bice (on page 3-8)

bvcbo

Measure collector-base breakdown voltage,

emitter open

bvcbo (on page 3-10)

bvcbo1

Measure collector-base breakdown voltage

using LPTLib bsweepv subroutine

bvcbo1 (on page 3-11)

bvceo

Measure collector-emitter breakdown voltage,

base open

bvceo (on page 3-13)

bvceo2

Measure collector-emitter breakdown voltage

using LPTLib bsweepv subroutine

bvceo2 (on page 3-14)

bvces

Measure collector-emitter breakdown voltage

bvces (on page 3-15)

bvebo

Measure emitter-base breakdown voltage,

collector open

bvebo (on page 3-20)

ibic1

Measure ICE, IBE and calculate at VCE, VBE,

V

SUB

ibic1 (on page 3-35)

icbo

Measure collector-base leakage at VCB and

V

SUB

icbo (on page 3-37)

iceo

Measure collector-emitter leakage at VCE and

V

SUB

iceo (on page 3-38)

ices

Measure emitter-collector leakage at V

CES

and V

SUB

ices (on page 3-39)

iebo

Measure emitter-base leakage at VEB and

V

SUB

iebo (on page 3-44)

rcsat

Estimate rcsat when IC and IB swept at

constant

rcsat (on page 3-50)

re

Estimate emitter resistance

re (on page 3-53)

vbes

Measure base-emitter voltage at specified IE

(VC = VB)

vbes (on page 3-62)

Page 11

Section 2: Using the test subroutine library S530 Parametric Test System Test Subroutine Library User's Manual

2-4 S530-907-01 Rev. A / September 2015

Resistors, diodes, capacitors, and special structure subroutines

Subroutine

Description

Link

bkdn

Measure breakdown voltage (force I,

measure V)

bkdn (on page 3-9)

cap

Measure two-terminal capacitance

cap (on page 3-21)

fimv

Force current and measure voltage on device

with four high pins and four ground pins

fimv (on page 3-27)

fvmi

Force voltage and measure current on device

with four input pins and four ground pins

fvmi (on page 3-29)

leak

Measure leakage current at specified voltage

leak (on page 3-48)

res

2-terminal resistance (force I, measure V)

res (on page 3-55)

res2

2-terminal resistance with voltage limit

res2 (on page 3-56)

res4

4-terminal resistance (force I, measure V)

res4 (on page 3-57)

resv

2-terminal resistance (force V, measure I)

resv (on page 3-58)

rvdp

4-terminal van der Pauw measurement

rvdp (on page 3-59)

tox

Calculate oxide thickness from capacitance

tox (on page 3-61)

vf

Measure the forward junction voltage of a

diode

vf (on page 3-63)

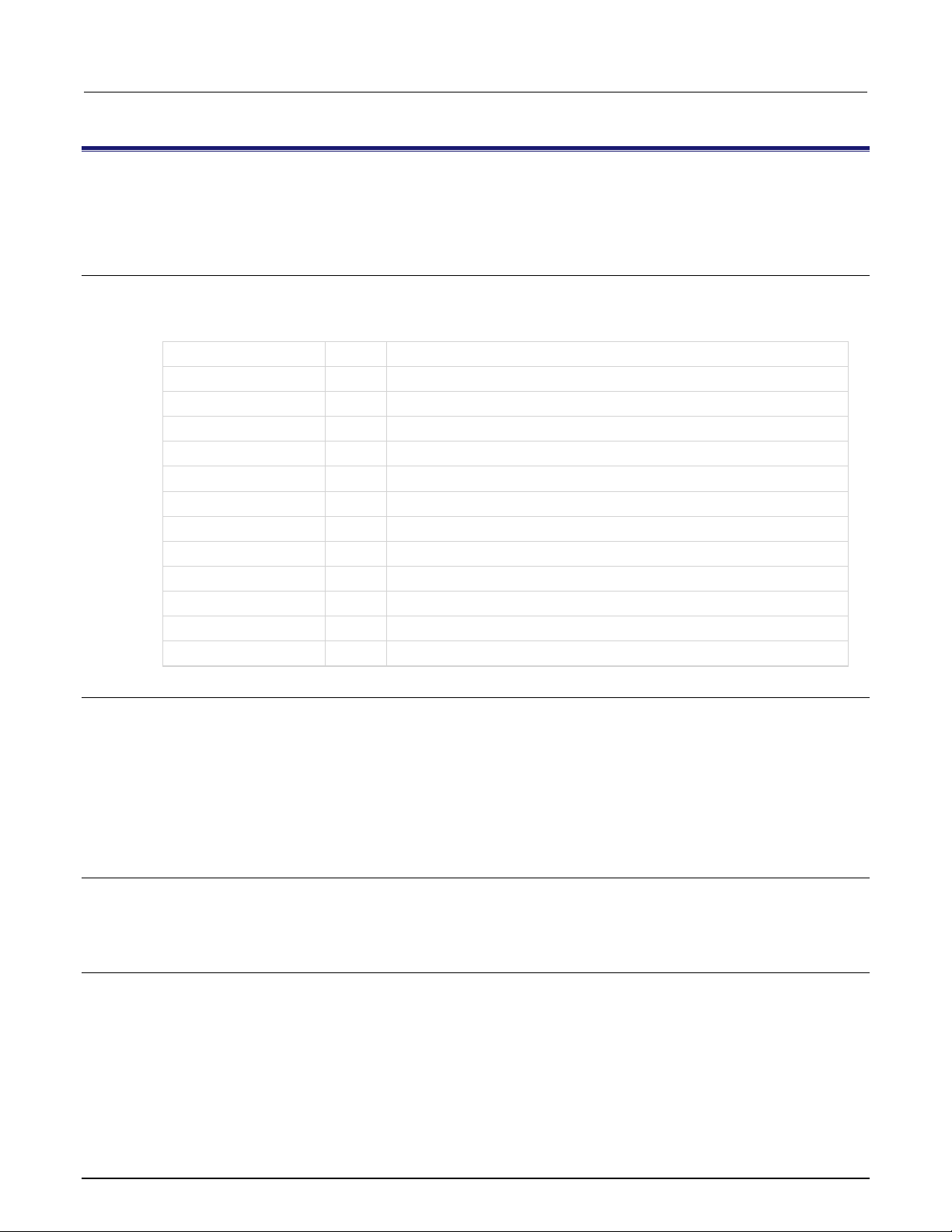

Subroutine

Description

Link

bvdss

Measure drain-source breakdown voltage

(VG = 0)

bvdss (on page 3-17)

bvdss1

Measure drain-source breakdown voltage

using LPTLib bsweepv subroutine

bvdss1 (on page 3-19)

deltl1

Estimate delta L MOSFET parameter

deltl1 (on page 3-23)

deltw1

Estimate delta W for a MOSFET

deltw1 (on page 3-24)

gamma1

Estimate body effect ()

gamma1 (on page 3-31)

gd

Calculate drain conductance of a MOSFET

gd (on page 3-32)

id1

Measure drain current at specified VGS, VDS,

and VBS

id1 (on page 3-40)

idsat

Measure drain current at VDS, VBS (VD = VG)

idsat (on page 3-42)

idgsvg

Measure IDS when VGS is swept at constant

VDS and VBS

idvsvg (on page 3-45)

isubmx

Find peak substrate current at VDS,VBS

isubmx (on page 3-46)

vg2

Measure gate-source voltage at IDS, VDS, VBS

vg2 (on page 3-64)

vgsat

Measure V

GSAT

at specified IDS (VGS = VD)

vgsat (on page 3-66)

vt14

Estimate VT using two-point technique

vt14 (on page 3-70)

vtati

Find VT to produce specified IDS

vtati (on page 3-71)

vtext

Extrapolate gate-source threshold voltage

vtext (on page 3-73)

vtext2

Estimate VT using modified vtext subroutine

method

vtext2 (on page 3-76)

vtext3

Calculate VT using max slope method

vtext3 (on page 3-78)

MOSFET subroutines

Page 12

S530 Parametric Test System Test Subroutine Library User's Manual Section 2: Using the test subroutine library

S530-907-01 Rev. A / September 2015 2-5

FET and JFET subroutines

Subroutine

Description

Link

gm

Estimate MESFET transconductance at VDS,

VGS

gm (on page 3-34)

idss

Estimate MESFET I

DSS

and V

DSAT

at V

DSS

idss (on page 3-43)

vp

Estimate FET pinch-off voltage for a MESFET

vp (on page 3-67)

vp1

Estimate MESFET pinch-off at IDS (IP) and

VDS

vp1 (on page 3-69)

Subroutine

Description

Link

fnddat

Search an array, return a new array

fnddat (on page 3-28)

fndtrg

Determine which native mode trigger to use

fndtrg (on page 3-29)

kdelay

Delay, based on current and voltage values

kdelay (on page 3-47)

logstp

Create an array using logarithmic steps

logstp (on page 3-49)

tdelay

Return calculated delay time

tdelay (on page 3-60)

Math and support subroutines

Page 13

In this section:

Subroutine descriptions ............................................................ 3-1

e

Input

The emitter pin of the device

b

Input

The base pin of the device

c

Input

The collector pin of the device

sub

Input

The substrate pin of the device

ie

Input

The forced emitter current, in amperes

vcb

Input

The forced c to b bias, in volts

type

Input

Type of transistor: "N" or "P"

Returns

Output

The calculated beta of the device:

-1.0 = TYPE not "N" or "P"

-2.0 = SMU2 overload

-3.0 = Divide by 0, or < 0.01

-4.0 = > 10 K or I

B

wrong sign

-5.0 = Emitter voltage limit reached; developed emitter voltage is

within 98 % of the 3 V voltage limit

Section 3

Test subroutine library reference

Subroutine descriptions

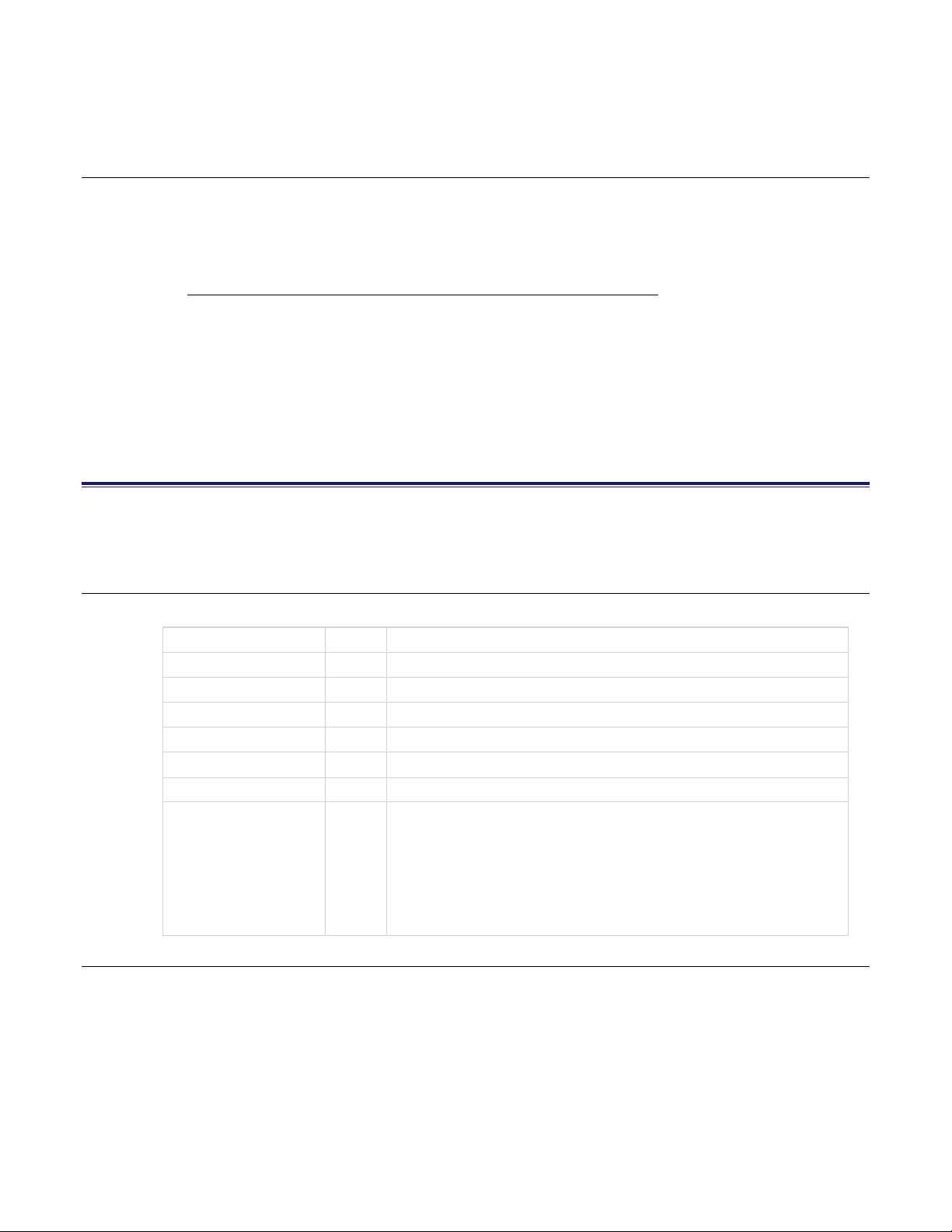

beta1

This subroutine calculates the DC beta () of a test device at constant emitter current (IE) and collector-base bias

(VCB). The device is in the common-base configuration.

Usage

double beta1(int e, int b, int c, int sub, double ie, double vcb, char type);

Details

If a positive substrate pin is specified, the substrate is grounded. If a positive substrate pin is not

specified, the substrate is left floating.

A delay is incorporated into the beta1 subroutine; this delay is the calculated time required for stable

forcing of emitter current with a 3 V voltage limit.

Page 14

Section 3: Test subroutine library reference S530 Parametric Test System Test Subroutine Library User's Manual

3-2 S530-907-01 Rev. A / September 2015

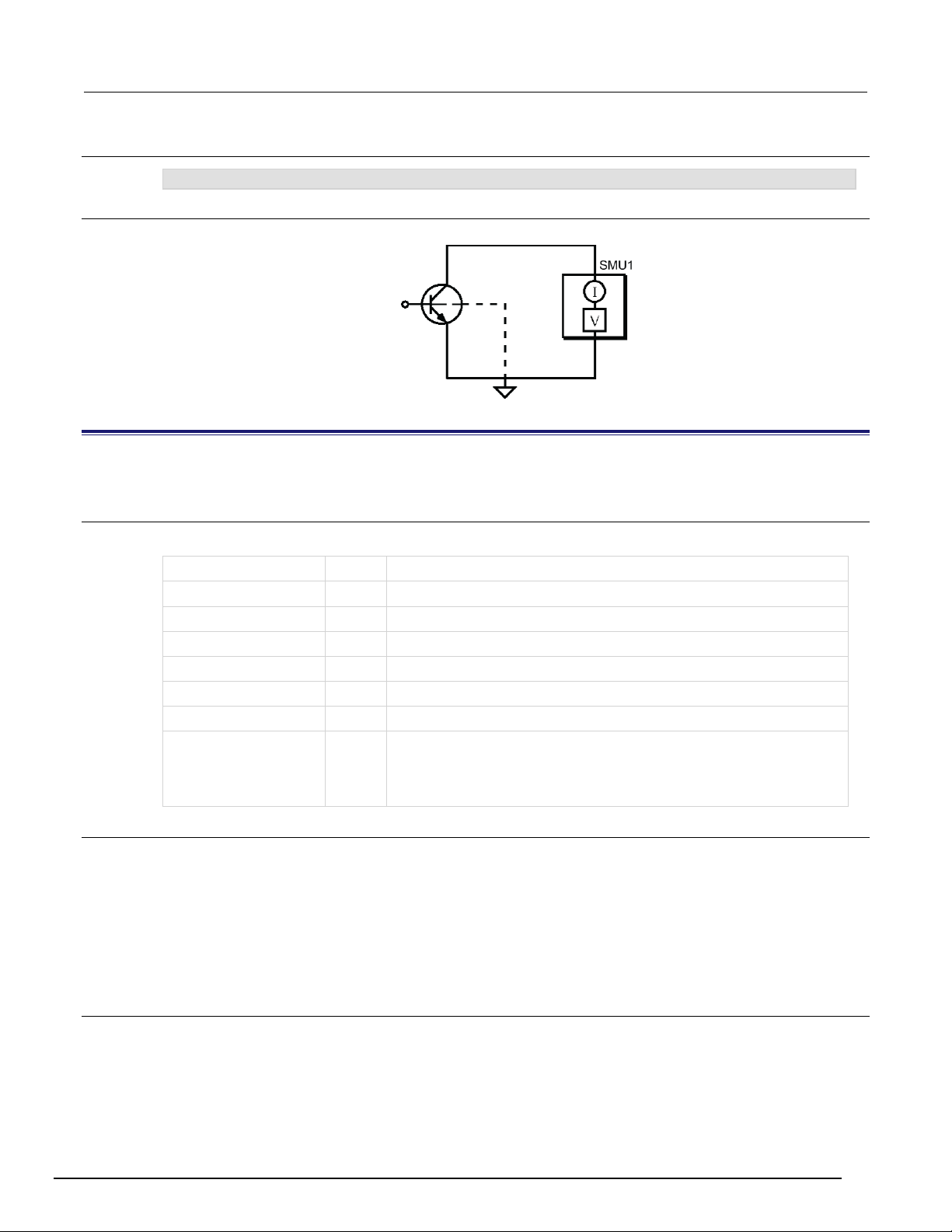

V/I polarities

result = beta1(e, b, c, sub, ie, vcb, type);

Source-measure units (SMUs)

SMU1: Forces V

SMU2: Forces 0.0 V, measures base current (I

The polarities of VCB and IE are determined by device type.

Example

Schematic

SMU3: Forces I

, default current limit

CB

, 3 V voltage limit

E

)

B

Page 15

S530 Parametric Test System Test Subroutine Library User's Manual Section 3: Test subroutine library reference

S530-907-01 Rev. A / September 2015 3-3

beta2

e

Input

The emitter pin of the device

b

Input

The base pin of the device

c

Input

The collector pin of the device

sub

Input

The substrate pin of the device

ice

Input

The targeted collector current, in amperes

vce

Input

The forced collector-emitter voltage, in volts

type

Input

Type of transistor: "N" or "P"

vbeout

Output

The measured base voltage

icout

Output

The measured collector current

Returns

Output

The calculated beta:

-1.0 = TYPE not "N" or "P"

-2.0 = SMU2 overload

-3.0 = Divide by 0, or < 0.01

-4.0 = > 10 K

-5.0 = Too many iterations

-6.0 = Emitter voltage limit reached; developed emitter voltage is

within 98 % of the 3 V voltage limit

This subroutine calculates beta () and base-emitter voltage (VBE) at a specified collector current (IC) and

collector-emitter bias (VCE).

Usage

double beta2(int e, int b, int c, int sub, double ice, double vce, double *vbeout,

double *icout, char type);

Details

If a positive substrate pin is specified, the substrate is grounded. If a positive substrate pin is not

specified, the substrate is left floating.

A delay is incorporated into the beta2 subroutine; this delay is the calculated time required for stable

forcing of emitter current with a 3 V voltage limit.

A faster and simpler subroutine to use is beta2a (on page 3-4).

V/I polarities

The polarities of VCE and IE are determined by device type.

Source-measure units (SMUs)

SMU1: Forces I

SMU2: Forces V

SMU3: Forces 0.0 V, measures base current (I

, 3 V voltage limit

E

, maximum current limit, measures ICE

CE

)

B

Page 16

Section 3: Test subroutine library reference S530 Parametric Test System Test Subroutine Library User's Manual

3-4 S530-907-01 Rev. A / September 2015

Example

result = beta2 (e, b, c, sub, ice, vce, &vbeout, &icout, type);

e

Input

The emitter pin of the device

b

Input

The base pin of the device

c

Input

The collector pin of the device

sub

Input

The substrate pin of the device

ice

Input

The targeted collector current, in amperes

vcb

Input

The forced c to b bias, in volts

ie1

Input

The start of the emitter current search, in amperes

ie2

Input

The end of the emitter current search, in amperes

vsub

Input

The forced substrate bias, in volts

icmeas

Output

The final measured collector-emitter current

ieout

Output

The final forced value of emitter current

error

Output

The percent error between the target collector current (ICE) and the final

measured collector current (I

CMEAS

)

Returns

Output

The calculated beta:

-1.0 = Target ICE = 0.0

-2.0 = Collector current limit reached

-3.0 = Emitter voltage limit reached

Schematic

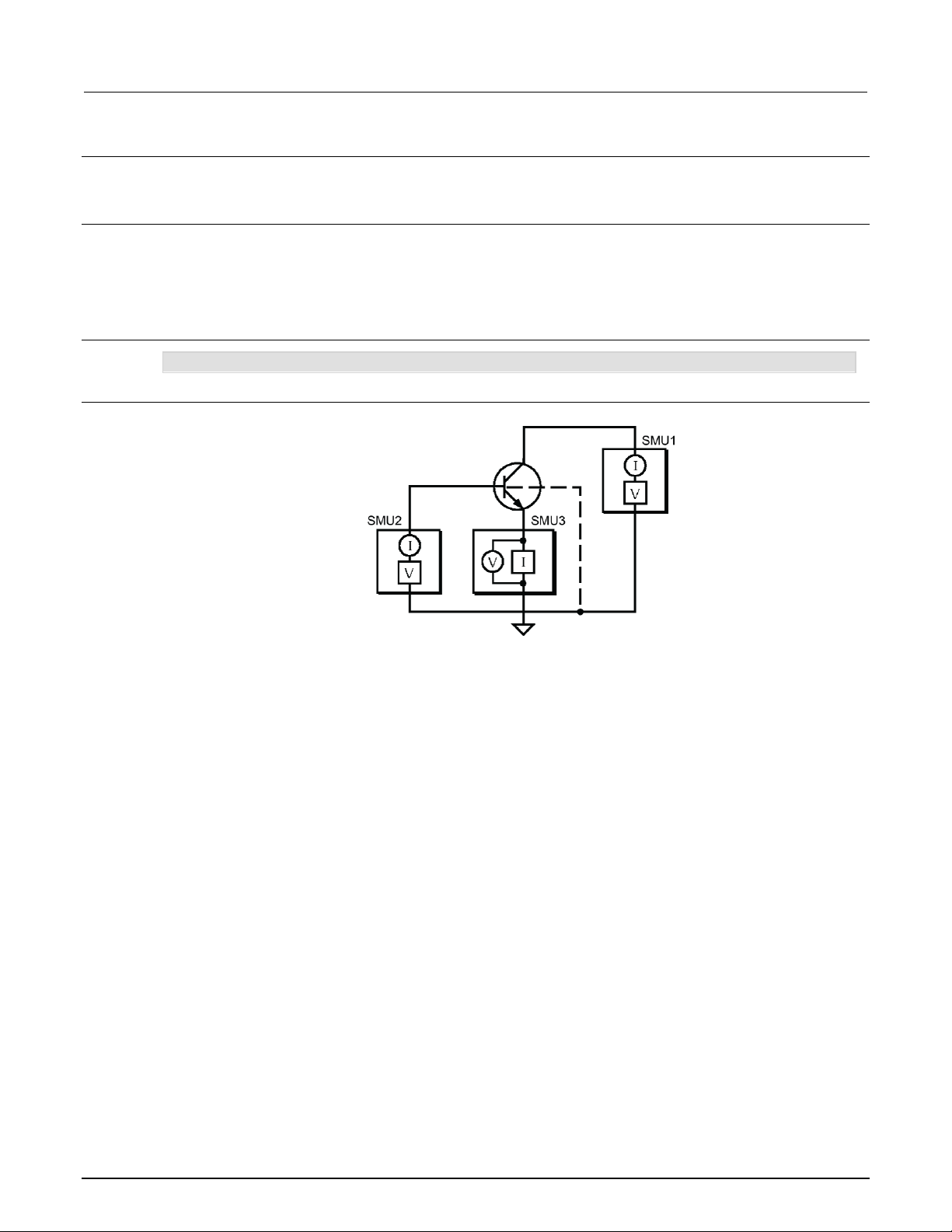

beta2a

This subroutine calculates beta () at collector-base voltage (VCB) and collector-emitter current (ICE) using the

searchi and trig LPTLib functions to search emitter current (IE) until the target ICE is reached. The device is in

the common-base configuration.

Usage

double beta2a(int e, int b, int c, int sub, double ice, double vcb, double ie1,

double ie2, double vsub, double *icmeas, double *ieout, double *error);

Page 17

S530 Parametric Test System Test Subroutine Library User's Manual Section 3: Test subroutine library reference

S530-907-01 Rev. A / September 2015 3-5

Details

result = beta2a(e, b, c, sub, ice, vcb, ie1, ie2, vsub, &icmeas, &ieout, &error);

This subroutine is a revised version of the beta2 (on page 3-3) subroutine that uses the LPTLib

searchi and trig functions to search IE until the target ICE is reached.

This subroutine sets the current trigger on SMU1 at the specified ICE. The emitter current is searched

until the trigger is set. The emitter current is then forced, the collector current measured, and is

calculated.

The percent error (error) is calculated between the target ICE and the final measured ICE and

returned.

If a zero or negative substrate pin is specified, the substrate is left floating. If the pin number is

greater than 0 and V

connected and forced.

V/I polarities

is less than 0.9 mV, the substrate is grounded. In all other cases, it is

SUB

NPN +ICE, +VCB, IE, -V

PNP -ICE, -VCB, +IE, -V

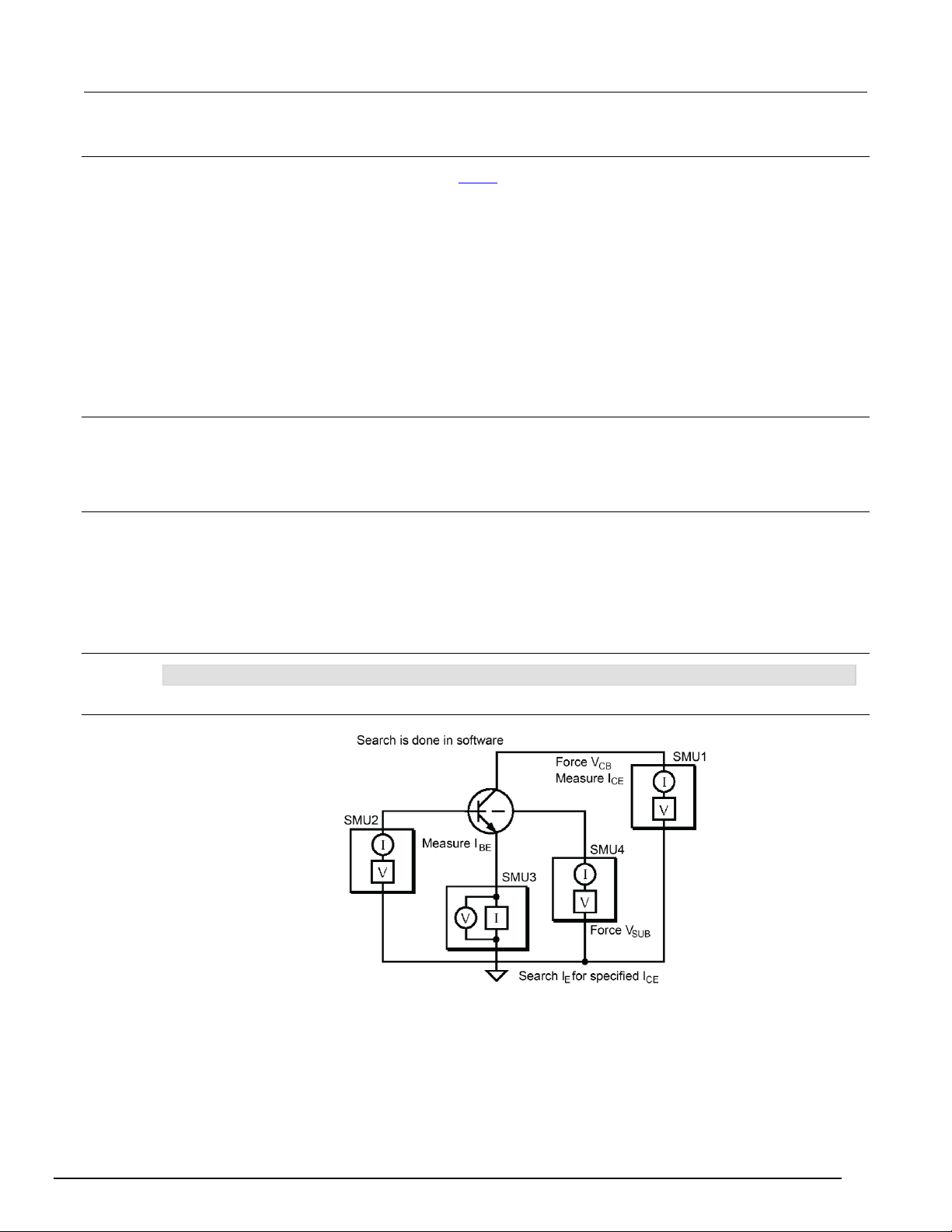

Source-measure units (SMUs)

SMU1: Forces V

SMU2: Forces 0.0 V, measures I

SMU3: Searches I

Example

Schematic

SMU4: Forces V

SUB

SUB

, maximum current limit, triggers on ICE

CB

BE

, 3 V voltage limit

E

, default current limit

SUB

Page 18

Section 3: Test subroutine library reference S530 Parametric Test System Test Subroutine Library User's Manual

3-6 S530-907-01 Rev. A / September 2015

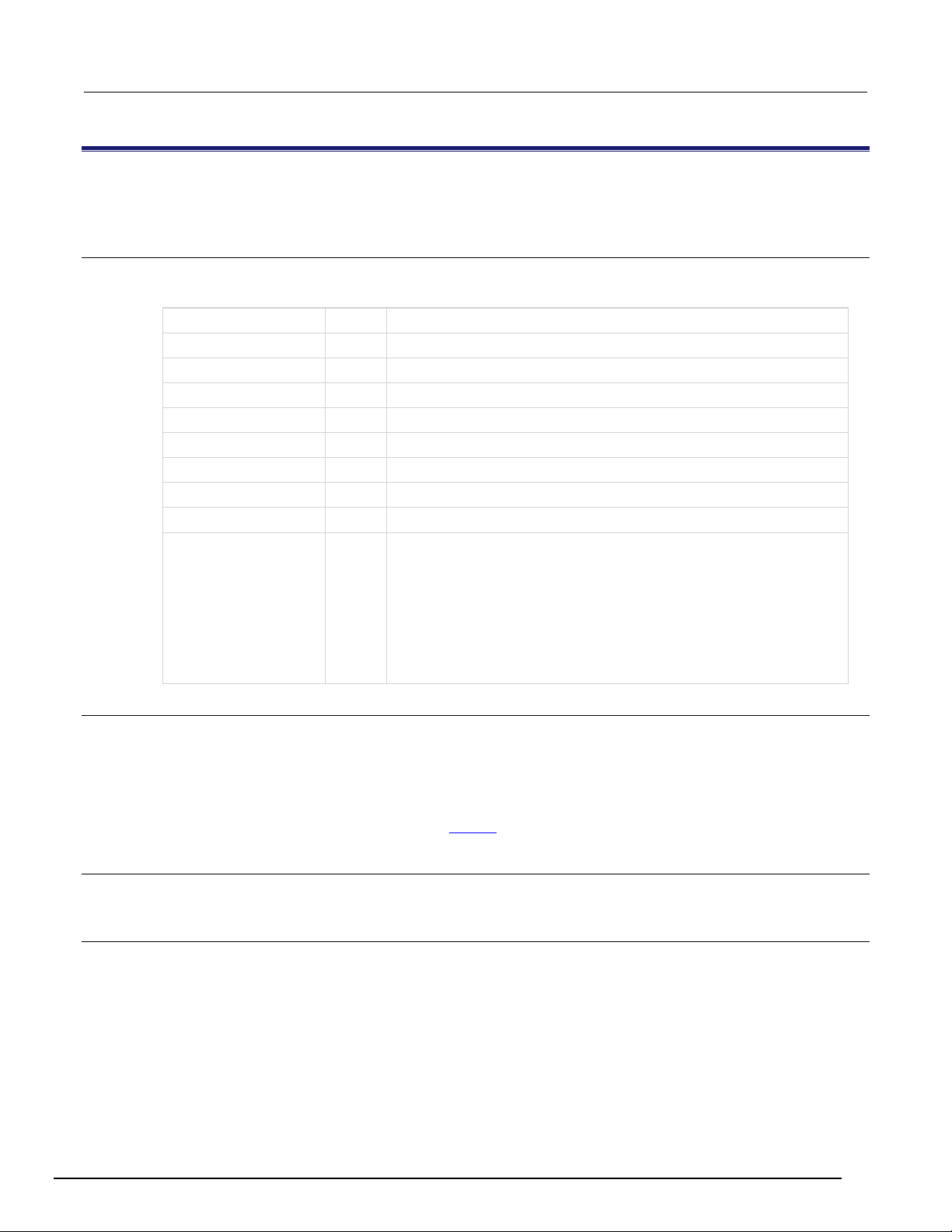

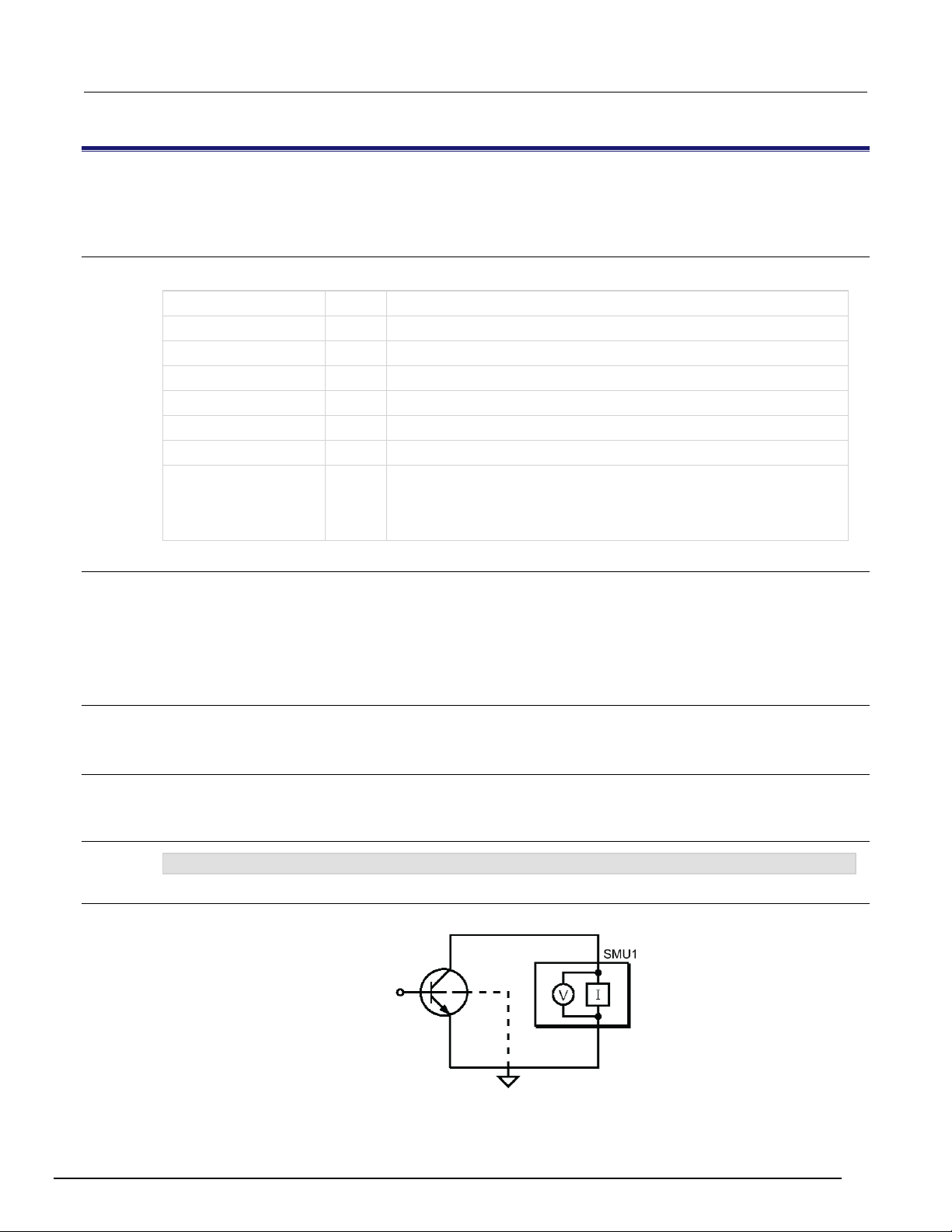

beta3a

e

Input

The emitter pin of the device

b

Input

The base pin of the device

c

Input

The collector pin of the device

sub

Input

The substrate pin of the device

ice

Input

The targeted collector current, in amperes

vce

Input

The forced collector-emitter voltage, in volts

ibe1

Input

The start of the base-emitter current (IBE) search, in amperes

ibe2

Input

The end of the base-emitter current (IBE) search, in amperes

vsub

Input

The forced substrate bias, in volts

ibe

Output

The final measured emitter-base current

icmeas

Output

The final measured collector-emitter current

error

Output

The percent error between the target collector current (ICE) and the final

measured collector current (I

CMEAS

)

Returns

Output

The calculated beta:

-1.0 = Target ICE = 0.0

-2.0 = Base voltage limit reached

This subroutine calculates beta () at collector-emitter voltage (VCE) and collector-emitter current (ICE) using the

searchi and trig LPTLib functions to search base-emitter current (IBE) until the target ICE is reached. The

device is in the common-emitter configuration.

Usage

double beta3a(int e, int b, int c, int sub, double ice, double vce, double ibe1,

double ibe2, double vsub, double *ibe, double *cmeas, double *error);

Details

This subroutine sets the current trigger on SMU1 at the specified ICE. The base current is searched

until the trigger is set. The base current is then forced, the collector current measured, and is

calculated.

The percent error (error) is calculated between the target ICE and the final measured ICE and

returned.

If a zero or negative substrate pin is specified, the substrate is left floating. If the pin number is

greater than 0 and V

connected and forced.

V/I polarities

NPN +ICE, +VCE, +I

PNP -ICE, -VCE, -IBE, -V

is less than 0.9 mV, the substrate is grounded. In all other cases, it is

SUB

-V

SUB

SUB

BE,

Page 19

S530 Parametric Test System Test Subroutine Library User's Manual Section 3: Test subroutine library reference

S530-907-01 Rev. A / September 2015 3-7

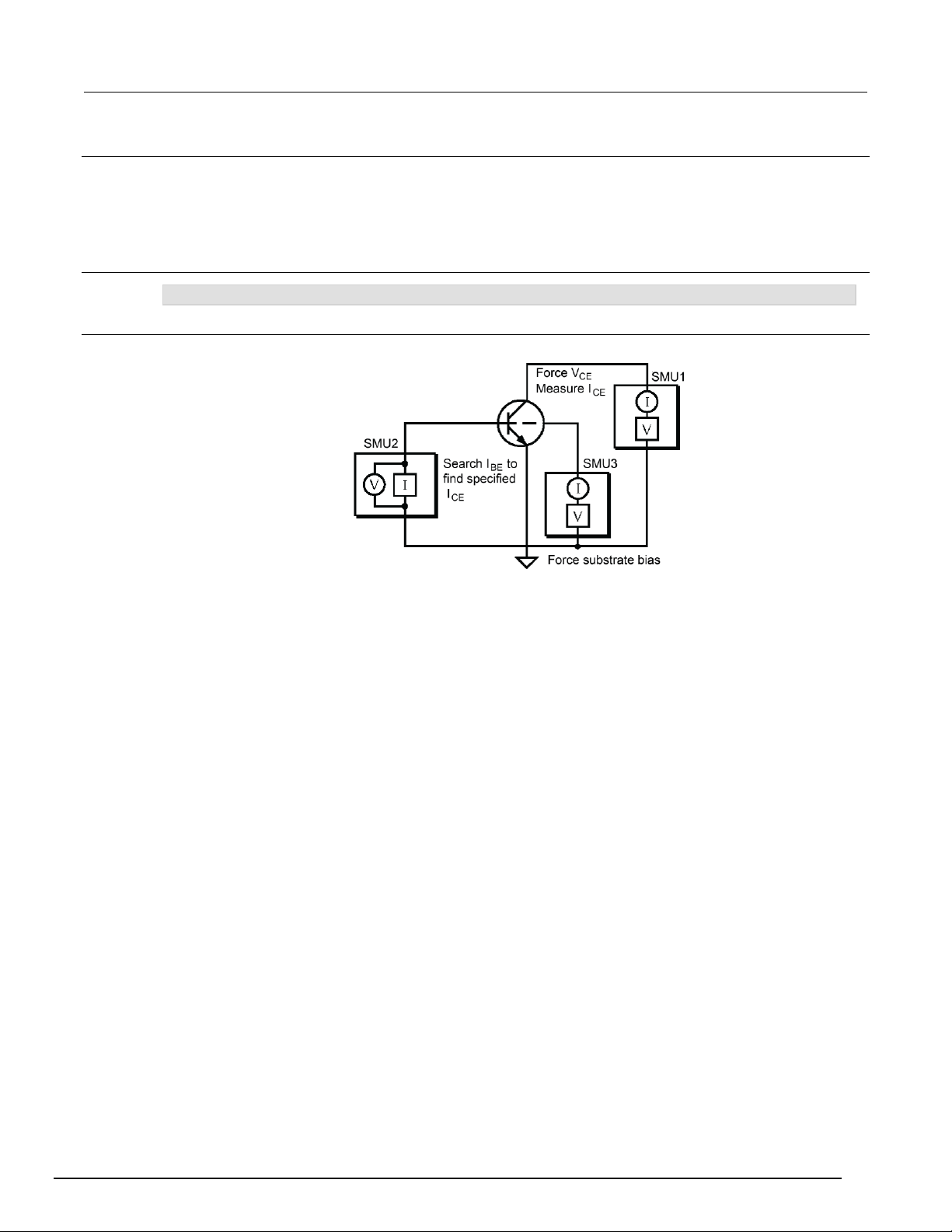

Source-measure units (SMUs)

result = beta3a(e, b, c, sub, ice, vce, ibe1, ibe2, vsub, &ibe, &cmeas, &error);

Example

Schematic

SMU1: Forces V

SMU2: Searches I

SMU3: Forces V

, maximum current limit, triggers on ICE

CE

, 3 V voltage limit

BE

, default current limit

SUB

Page 20

Section 3: Test subroutine library reference S530 Parametric Test System Test Subroutine Library User's Manual

3-8 S530-907-01 Rev. A / September 2015

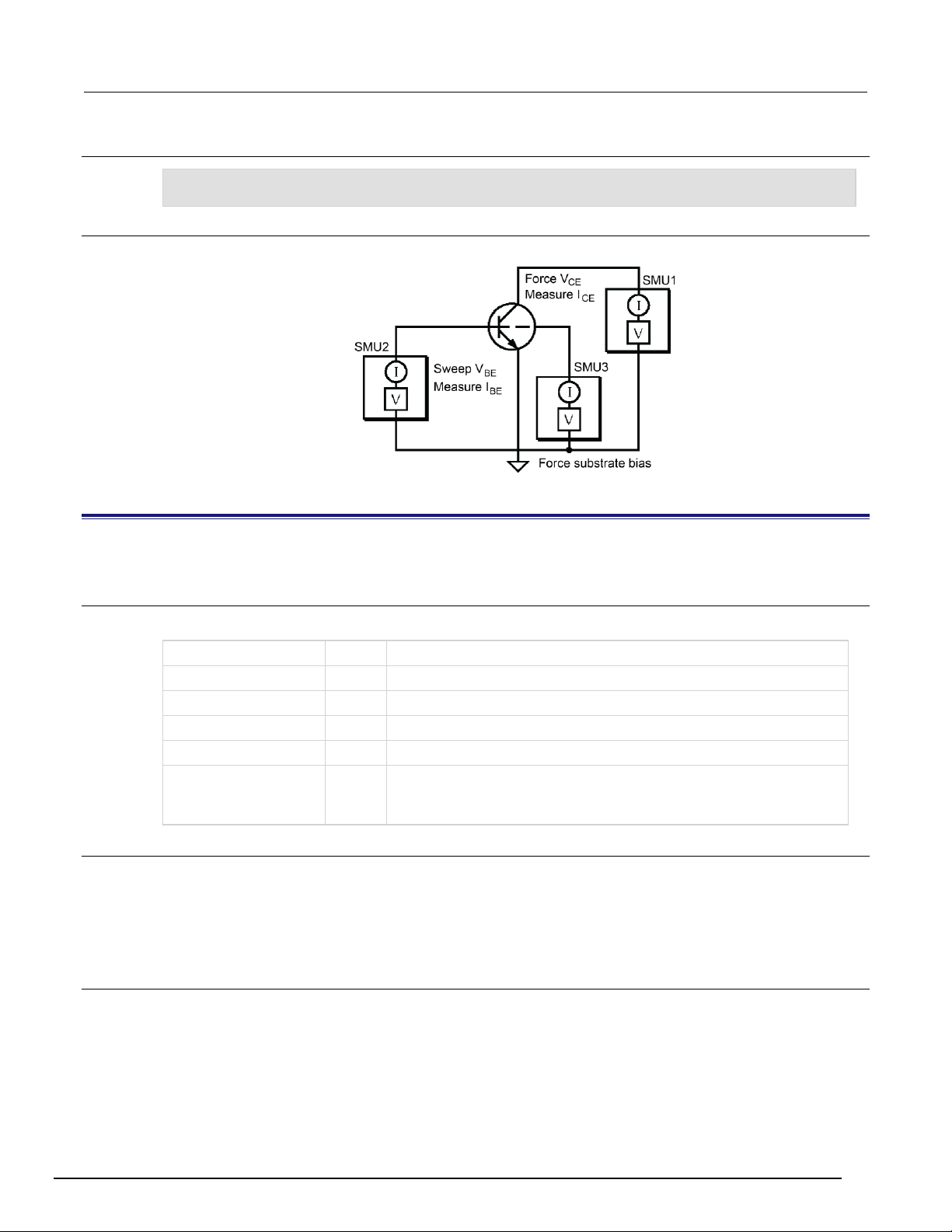

bice

e

Input

The emitter pin of the device

b

Input

The base pin of the device

c

Input

The collector pin of the device

sub

Input

The substrate pin of the device

vce

Input

The forced collector-emitter voltage, in volts

vbe1

Input

The start point of the VBE sweep, in volts

vbe2

Input

The end point of the VBE sweep, in volts

vsub

Input

Substrate bias, in volts

npts

Input

The number of points in the sweep

ice_last

Output

The measured ICE array

beta_last

Output

The calculated beta array

beta_max

Output

The maximum beta in the array

ic_max

Output

The ICE at maximum beta

This subroutine sweeps the emitter-base voltage (VBE), measures the resulting collector-emitter current (ICE), and

calculates beta ()at each value of V

configuration.

Usage

void bice(int e, int b, int c, int sub, double vce, double vbe1, double vbe2,

double vsub, int npts, double ice_last, double *beta_last, double *beta_max,

double *ic_max);

for a bipolar transistor. The device is connected in the common-emitter

BE

Details

The collector-emitter voltage (V

In addition to the and I

maximum (ic_max) are returned.

If a zero or negative substrate pin is specified, the substrate is left floating. If the pin number is

greater than 0 and V

connected and forced.

V/I polarities

NPNs +VCE, +IBE, and -V

PNPs -VCE, -IBE, and -V

Source-measure units (SMUs)

SMU1: Forces V

SMU2: Sweeps V

SMU3: Forces V

) and the substrate voltage (V

CE

return arrays, the maximum (beta_max) and collector current at

CE

is less than 0.9 mV, the substrate is grounded. In all other cases, it is

SUB

SUB

SUB

, maximum current limit, measures ICE

CE

, maximum current limit, measures IBE

BE

, default current limit

SUB

) are held constant.

SUB

Page 21

S530 Parametric Test System Test Subroutine Library User's Manual Section 3: Test subroutine library reference

S530-907-01 Rev. A / September 2015 3-9

Example

result = bice(e, b, c, sub, vce, vbe1, vbe2, vsub, npts, ice_last, &beta_last,

&beta_max, &ic_max);

hi

Input

The HI pin of the device

lo

Input

The LO pin of the device

sub

Input

The substrate pin of the device

ipgm

Input

The forced current, in amperes

vlim

Input

The voltage limit, in volts

Returns

Output

The measured breakdown voltage:

+2.0E + 21 = Measured voltage is within 98 % of the specified voltage

limit

Schematic

bkdn

This subroutine forces a current and measures breakdown voltage on a two-terminal device.

Usage

double bkdn(int hi, int lo, int sub, double ipgm, double vlim);

Details

If a positive substrate pin is specified, the substrate is grounded. If a positive substrate pin is not

specified, the substrate is left floating.

A delay is incorporated into the bkdn subroutine; this delay is the calculated time required for stable

Source-measure units (SMUs)

forcing of ipgm within the vlim voltage limit.

SMU1: Forces ipgm, programmable voltage limit, measures breakdown voltage

Page 22

Section 3: Test subroutine library reference S530 Parametric Test System Test Subroutine Library User's Manual

3-10 S530-907-01 Rev. A / September 2015

Example

result = bkdn(hi, lo, sub, ipgm, vlim);

e

Input

The emitter pin of the device

b

Input

The base pin of the device

c

Input

The collector pin of the device

sub

Input

The substrate pin of the device

ipgm

Input

The forced collector-base current (ICB), in amperes

vlim

Input

The collector voltage limit, in volts

type

Input

Type of transistor: "N" or "P"

Returns

Output

Collector-base voltage:

-1.0 = TYPE not "N" or "P"

+2.0E + 21 = Voltage limit reached; measured voltage is within

98 % of the specified voltage limit (vlim)

Schematic

bvcbo

This subroutine forces a collector current (I

emitter open.

Usage

double bvcbo(int e, int b, int c, int sub, double ipgm, double vlim, char type);

Details

) and measures the collector-base breakdown voltage (VCB) with the

CBO

If a positive substrate pin is specified, the substrate is grounded. If a positive substrate pin is not

specified, the substrate is left floating.

A delay is incorporated into the bvcbo subroutine; this delay is the calculated time required for stable

forcing of ipgm within the vlim voltage limit.

V/I polarities

The polarity of ipgm is determined by the device type.

Source-measure units (SMUs)

SMU1: Forces I

, programmed voltage limit, measures bvcbo

CBO

Page 23

S530 Parametric Test System Test Subroutine Library User's Manual Section 3: Test subroutine library reference

S530-907-01 Rev. A / September 2015 3-11

Example

result = bvcbo(e, b, c, sub, ipgm, vlim, type);

e

Input

The emitter pin of the device

b

Input

The base pin of the device

c

Input

The collector pin of the device

sub

Input

The substrate pin of the device

vcbmin

Input

The starting collector-base voltage (VCB), in volts

vcbmax

Input

The ending VCB, in volts

nstep

Input

The number of voltage steps

ipgm

Input

The targeted collector-base current (ICB), in amperes

udelay

Input

Delay between VCB steps, in seconds

type

Input

Type of transistor: "N" or "P"

Returns

Output

Collector-base voltage:

-1.0 = TYPE not "N" or "P"

+1.0E + 21 = Device triggered on vcbmin

+2.0E + 21 = Device triggered on vcbmax

Schematic

bvcbo1

This subroutine uses the bsweepv LPTLib function to measure collector-base breakdown voltage at a specified

current with the emitter open.

Usage

double bvcbo1(int e, int b, int c, int sub, double vcbmin, double vcbmax, int

nstep, double ipgm, double udelay, char type);

Page 24

Section 3: Test subroutine library reference S530 Parametric Test System Test Subroutine Library User's Manual

3-12 S530-907-01 Rev. A / September 2015

Details

Result = bvcbo1(e, b, c, sub, vcbmin, vcbmax, nstep, ipgm, udelay, type);

This subroutine sweeps the collector-base voltage from vcbstart to vcbstop while monitoring the

collector current with the emitter open. When the programmed current level (ipgm) is reached, the

last collector-base voltage increment is returned as BVCBO1.

If a positive substrate pin is specified, the substrate is grounded. If a positive substrate pin is not

specified, the substrate is left floating.

The udelay parameter should be programmed to approximate c * vcbmax / ipgm, where c =

junction capacitance of the device under test.

V/I polarities

The polarities of vcbmin, vcbmax, and ipgm are determined by device type.

Source-measure units (SMUs)

Example

Schematic

SMU1: Forces V

, programmed current limit = 1.25 * ipgm, measures collector current (I

CB

CBO

)

Page 25

S530 Parametric Test System Test Subroutine Library User's Manual Section 3: Test subroutine library reference

S530-907-01 Rev. A / September 2015 3-13

bvceo

e

Input

The emitter pin of the device

b

Input

The base pin of the device

c

Input

The collector pin of the device

sub

Input

The substrate pin of the device

ipgm

Input

The forced collector-emitter current (ICE), in amperes

vlim

Input

The collector voltage limit, in volts

type

Input

Type of transistor: "N" or "P"

Returns

Output

Collector-emitter voltage:

-1.0 = TYPE not "N" or "P"

+2.0E + 21 = Voltage limit reached; measured voltage is within

98 % of the specified voltage limit (vlim)

result = bvceo(e, b, c, sub, ipgm, vlim, type);

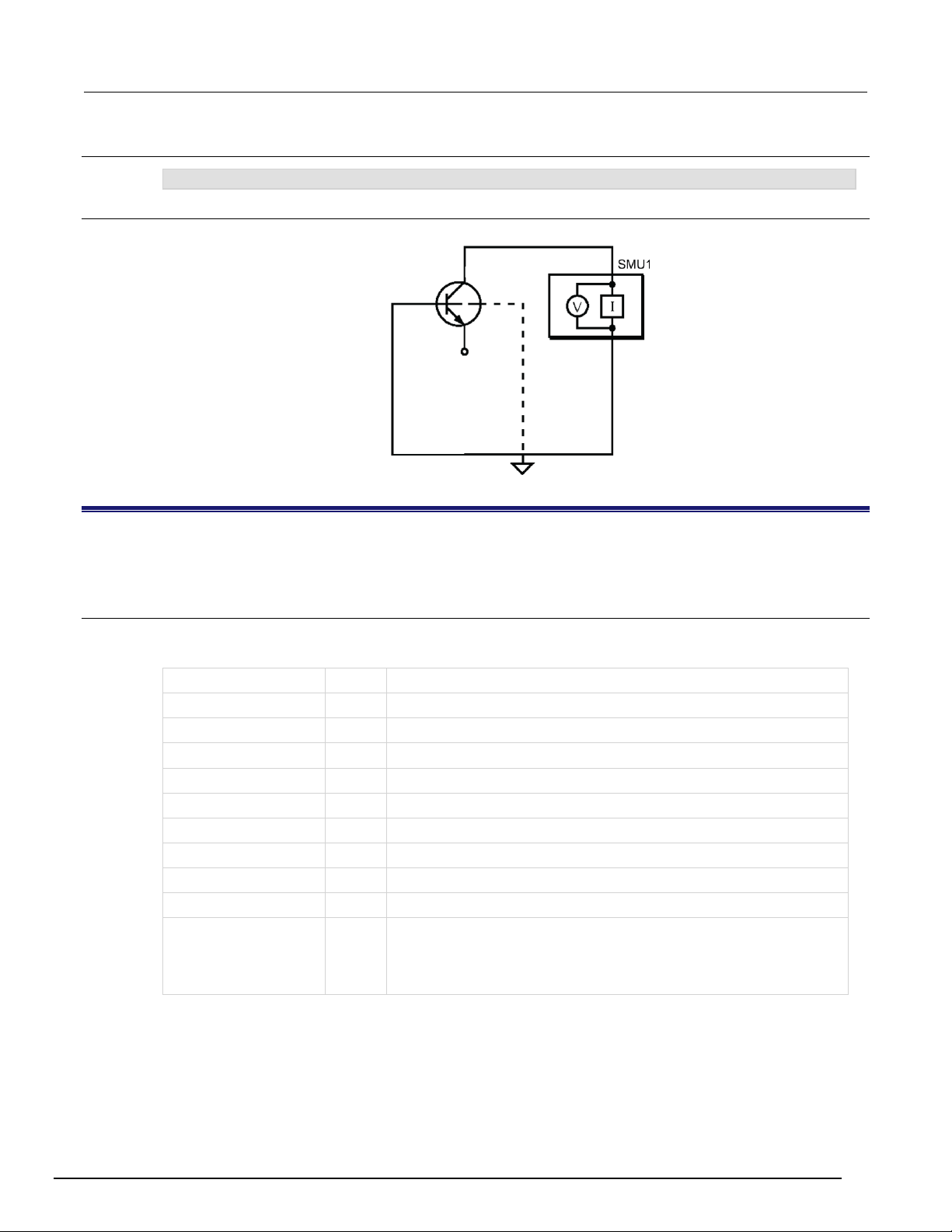

This subroutine measures the collector-emitter breakdown voltage (VCE) when the collector current (IC) is forced

with the base terminal left open.

Usage

double bvceo(int e, int b, int c, int sub, double ipgm, double vlim, char type);

Details

If a positive substrate pin is specified, the substrate is grounded. If a positive substrate pin is not

specified, the substrate is left floating.

A delay is incorporated into the bvceo subroutine; this delay is the calculated time required for stable

forcing of ipgm within the vlim voltage limit.

V/I polarities

The polarity of ipgm is determined by the device type.

Source-measure units (SMUs)

SMU1: Forces I

Example

Schematic

, programmed voltage limit, measures bvceo

CEO

Page 26

Section 3: Test subroutine library reference S530 Parametric Test System Test Subroutine Library User's Manual

3-14 S530-907-01 Rev. A / September 2015

bvceo2

e

Input

The emitter pin of the device

b

Input

The base pin of the device

c

Input

The collector pin of the device

sub

Input

The substrate pin of the device

vcemin

Input

The starting collector-emitter voltage (VCE), in volts

vcemax

Input

The ending VCE, in volts

nstep

Input

The number of voltage steps

ipgm

Input

The targeted collector-emitter current (ICE), in amperes

udelay

Input

The delay between VCE steps, in seconds

type

Input

Type of transistor: "N" or "P"

Returns

Output

Collector-emitter voltage:

-1.0 = TYPE not "N" or "P"

+1.0E + 21 = Device triggered on vcemin

+2.0E + 21 = Device triggered on vcemax

This subroutine measures collector-emitter breakdown voltage using the bsweepV LPTLib function.

Usage

double bvceo2(int e, int b, int c, int sub, double vcemin, double vcemax, int

nstep, double ipgm, double udelay, char type);

Details

This subroutine sweeps VCE from vcemin to vcemax while monitoring the collector current with the

base open. When the specified current level (ipgm) is reached, the last collector-emitter voltage

increment is returned as bvceo2.

If a positive substrate pin is specified, the substrate is grounded. If a positive substrate pin is not

specified, the substrate is left floating.

Set the udelay parameter to approximate C * vcemax / ipgm, where C = Junction capacitance of

the device under test.

V/I polarities

The polarities of vcemin, vcemax, and ipgm are determined by device type.

Source-measure units (SMUs)

SMU1: Forces V

, programmed current limit = 1.25 *ipgm, measures I

CE

CEO

Page 27

S530 Parametric Test System Test Subroutine Library User's Manual Section 3: Test subroutine library reference

S530-907-01 Rev. A / September 2015 3-15

Example

result = bvceo2(e, b, c, sub, vcemin, vcemax, nstep, ipgm, udelay, type);

e

Input

The emitter pin of the device

b

Input

The base pin of the device

c

Input

The collector pin of the device

sub

Input

The substrate pin of the device

ipgm

Input

The forced I

CES

, in amperes

vlim

Input

The collector voltage limit, in volts

type

Input

Type of transistor: "N" or "P"

Returns

Output

Collector-emitter/base voltage:

-1.0 = TYPE not "N" or "P"

+2.0E + 21 = Voltage limit reached; measured voltage is within

98 % of the specified voltage limit (vlim)

Schematic

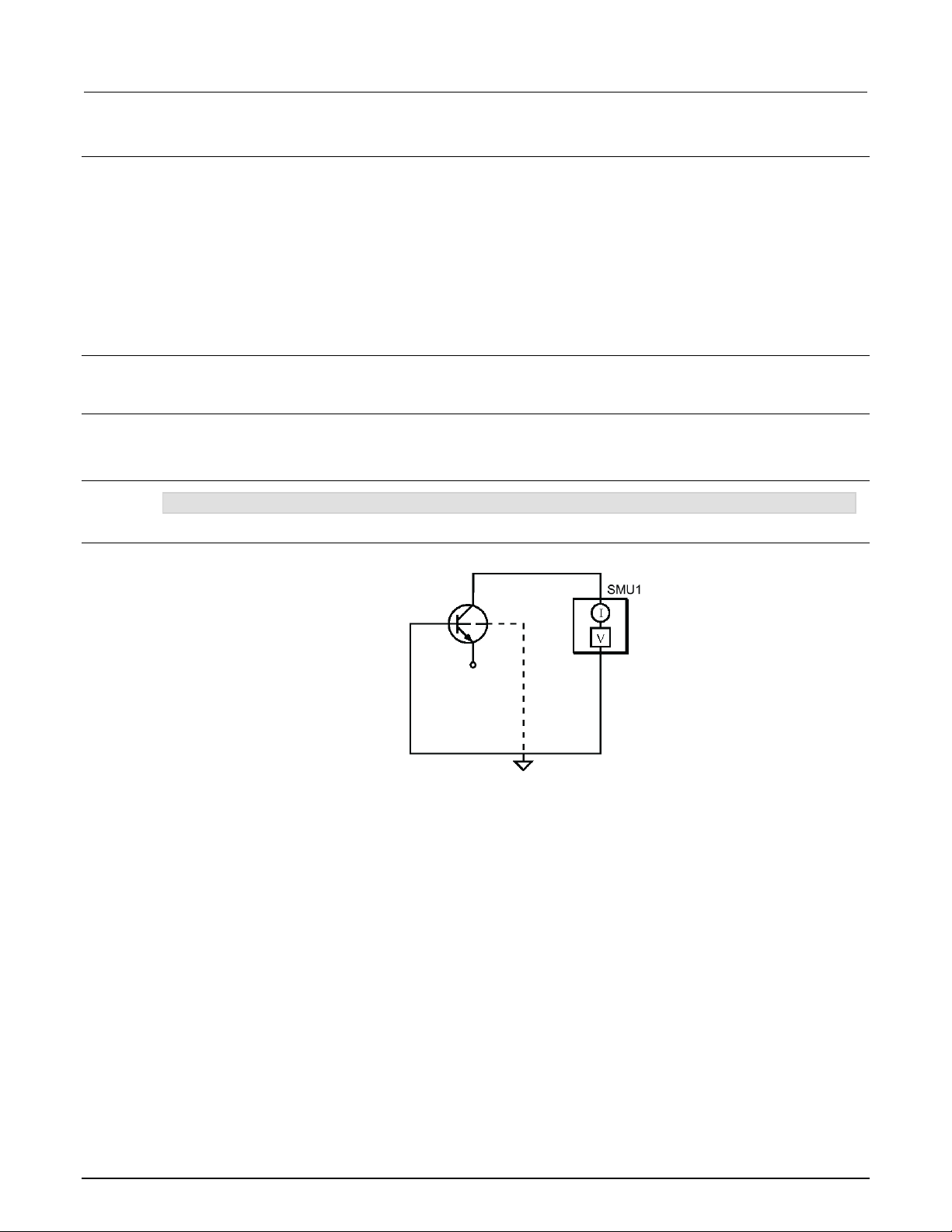

bvces

This subroutine measures the collector-emitter/base breakdown voltage by forcing a collector current (I

Usage

double bvces(int e, int b, int c, int sub, double ipgm, double vlim, char type);

Details

CES

).

This subroutine measures collector-to-emitter breakdown voltage at a specified current with the base

shorted to the emitter.

If a positive substrate pin is specified, the substrate will be grounded. If a positive substrate pin is not

specified, it is left floating.

A delay is incorporated into the bvces subroutine; this delay is the calculated time required for stable

forcing of ipgm within the vlim voltage limit.

V/I polarities

The polarity of ipgm is determined by the device type.

Page 28

Section 3: Test subroutine library reference S530 Parametric Test System Test Subroutine Library User's Manual

3-16 S530-907-01 Rev. A / September 2015

Source-measure units (SMUs)

resu1t = bvces(e, b, c, sub, ipgm, vlim, type);

e

Input

The emitter pin of the device

b

Input

The base pin of the device

c

Input

The collector pin of the device

sub

Input

The substrate pin of the device

vcemin

Input

The starting collector-emitter voltage (VCE), in volts

vcemax

Input

The ending VCE, in volts

nstep

Input

The number of voltage steps

ipgm

Input

The targeted collector-emitter current (ICE), in amperes

udelay

Input

The delay between VCE steps, in seconds

type

Input

Type of transistor: "N" or "P"

Returns

Output

Collector-emitter voltage:

-1.0 = TYPE not "N" or "P"

+1.0E + 21 = Device triggered on vcemin

+2.0E + 21 = Device triggered on vcemax

SMU1: Forces I

, programmed voltage limit, measures bvces

CES

Example

Schematic

bvces1

This subroutine measure the collector-emitter breakdown voltage using the bsweepV LPTLib function.

Usage

double bvces1(int e, int b, int c, int sub, double vcemin, double vcemax, int

nstep, double ipgm, double udelay, char type);

Page 29

S530 Parametric Test System Test Subroutine Library User's Manual Section 3: Test subroutine library reference

S530-907-01 Rev. A / September 2015 3-17

Details

result = bvces1(e, b, c, sub, vcemin, vcemax, nstep, ipgm, udelay, type);

d

Input

The drain pin of the device

g

Input

The gate pin of the device

s

Input

The source pin of the device

sub

Input

The substrate pin of the device

ipgm

Input

The forced drain current, in amperes

vlim

Input

The drain voltage limit, in volts

Returns

Output

Measured breakdown voltage:

+2.0E + 21 = Voltage limit reached; measured voltage is within

98 % of the specified voltage limit (vlim)

This subroutine sweeps the collector-emitter voltage from vcemin to vcemax while monitoring the

collector current with the base shorted to the emitter. When the programmed current level (ipgm) is

reached, the last collector-emitter voltage increment is returned as bvces1.

If a positive substrate pin is specified, the substrate is grounded. If a positive substrate pin is not

specified, the substrate is left floating.

Set the udelay parameter to approximate C * vcemax / ipgm, where C = Junction capacitance of

the device under test.

V/I polarities

Source-measure units (SMUs)

The polarities of vcemin, vcemax, and ipgm are determined by device type.

SMU1: Forces V

, programmed current limit = 1.25 *ipgm, measures I

CE

CEO

Example

Schematic

bvdss

This subroutine measure drain-source breakdown voltage (VG = 0) when the gate is grounded with the source.

Usage

double bvdss(int d, int g, int s, int sub, double ipgm, double vlim);

Page 30

Section 3: Test subroutine library reference S530 Parametric Test System Test Subroutine Library User's Manual

3-18 S530-907-01 Rev. A / September 2015

Details

result = bvdss(d, g, s, sub, ipgm, vlim);

This subroutine measures the drain-to-source breakdown voltage of a field-effect transistor (FET) with

the gate grounded with the source, at a specified current (magnitude and polarity).

If a positive substrate pin is specified, the substrate is grounded. If a positive substrate pin is not

specified, the substrate is left floating.

A delay is incorporated into the bvdss subroutine; this delay is the calculated time required for stable

forcing of ipgm within the vlim voltage limit.

V/I polarities

N-channel +Ipgm

Source-measure units (SMUs)

P-channel -Ipgm

SMU1: Forces ipgm, programmed voltage limit, measures bvdss

Example

Schematic

Page 31

S530 Parametric Test System Test Subroutine Library User's Manual Section 3: Test subroutine library reference

S530-907-01 Rev. A / September 2015 3-19

bvdss1

d

Input

The drain pin of the device

g

Input

The gate pin of the device

s

Input

The source pin of the device

sub

Input

The substrate pin of the device

vdsmin

Input

The starting drain-source voltage (VDS), in volts

vdsmax

Input

The ending VDS, in volts

nstep

Input

The number of voltage steps

ipgm

Input

Target drain-source current (VCS), in amperes

udelay

Input

The delay between VDS steps, in seconds

type

Input

Type of transistor: "N" or "P"

Returns

Output

Measured breakdown voltage:

-1.0 = TYPE not "N" or "P"

+1.0E+21 = Device triggered on vdsmin

+2.0E+21 = Device triggered on vdsmax

This subroutine measures the drain-source breakdown voltage using the bsweepv LPTLib function.

Usage

double bvdss1 (int d, int g, int s, int sub, double vdsmin, double vdsmax, int

nstep, double ipgm, double udelay, char type);

Details

This subroutine sweeps the drain-source voltage from vdsmin to vdsmax while monitoring the drain

current with the gate grounded to the source. When the specified current level (ipgm) is reached, the

last drain-source voltage increment is returned as bvdss1.

If a positive substrate pin is specified, the substrate is grounded. If a positive substrate pin is not

specified, the substrate is left floating.

Set the udelay parameter to approximate C * vdsmax / ipgm, where C = junction capacitance of

the device under test.

V/I polarities

The polarities of vdsmin, vdsmax, and ipgm are determined by device type.

Source-measure units (SMUs)

SMU1: Forces V

, programmed current limit = 1.25*ipgm, measures IDS

DS

Page 32

Section 3: Test subroutine library reference S530 Parametric Test System Test Subroutine Library User's Manual

3-20 S530-907-01 Rev. A / September 2015

Example

result = bvdss1(d, g, s, sub, vdsmin, vdsmax, nstep, ipgm, udelay, type);

e

Input

The emitter pin of the device

b

Input

The base pin of the device

c

Input

The collector pin of the device

sub

Input

The substrate pin of the device

ipgm

Input

The forced emitter-base current (IEB), in amperes

vlim

Input

The emitter voltage limit, in volts

type

Input

Type of transistor: "N" or "P"

Returns

Output

Emitter-base voltage:

-1.0 = TYPE not "N" or "P"

+2.0E + 21 = Voltage limit reached; measured voltage is within

98 % of the specified voltage limit (vlim)

Schematic

S

bvebo

This subroutine measures emitter-base breakdown voltage at a specified current with the collector open.

Usage

double bvebo(int e, int b, int c, int sub, double ipgm, double vlim, char type);

Details

This subroutine measures the emitter-base breakdown voltage by forcing an emitter current with the

collector pin open. Always call this subroutine last when testing transistors.

At high values of I

, degradation of the emitter-base junction can occur, which will lower beta ().

EBO

If a positive substrate pin is specified, the substrate is grounded. If a positive substrate pin is not

specified, the substrate is left floating.

A delay is incorporated into the bvebo subroutine; this delay is the calculated time required for stable

forcing of ipgm within the vlim voltage limit.

V/I polarities

The polarity of ipgm is determined by the device type.

Page 33

S530 Parametric Test System Test Subroutine Library User's Manual Section 3: Test subroutine library reference

S530-907-01 Rev. A / September 2015 3-21

Source-measure units (SMUs)

result = bvebo(e, b, c, sub, ipgm, vlim, type);

hi

Input

The HI pin of the device

lo

Input

The LO pin of the device

sub

Input

The substrate pin of the device

vbias

Input

The voltage bias on the device, in volts

Returns

Output

Measured capacitance

SMU1: Forces I

, programmed voltage limit, measures bvebo

EBO

Example

Schematic

cap

This subroutine measures the capacitance of a two-terminal device.

Usage

Details

double cap(int hi, int lo, int sub, double vbias);

This subroutine measures the capacitance of a two-terminal capacitor at a specified voltage. The

voltage is provided by the internal capacitance meter bias supply. The result is returned in farads.

If a positive substrate pin is specified, the substrate is grounded. If a positive substrate pin is not

specified, the substrate is left floating.

When using this routine for junction capacitance measurements, make sure the junction never

becomes forward biased. To prevent this, make sure the forward voltage is less than one-half the

barrier potential (for silicon, this means that the forward voltage (VF) should not exceed 300 mV to

350 mV).

At the onset of conduction in a forward-biased diode (V > 300 mV), the current flow causes

unpredictable readings in the capacitance meter (usually overrange, 1022).

Page 34

Section 3: Test subroutine library reference S530 Parametric Test System Test Subroutine Library User's Manual

3-22 S530-907-01 Rev. A / September 2015

Example

result = cap(hi, lo, sub, vbias);

Schematic

Page 35

S530 Parametric Test System Test Subroutine Library User's Manual Section 3: Test subroutine library reference

S530-907-01 Rev. A / September 2015 3-23

deltl1

d1

Input

The drain pin of Q1

g1

Input

The gate pin of Q1

s1

Input

The source pin of Q1

sub1

Input

The substrate pin of Q1

l1

Input

Drawn gate length of Q1, in microns

d2

Input

The drain pin of Q2

g2

Input

The gate pin of Q2

s2

Input

The source pin of Q2

sub2

Input

The substrate pin of Q2

l2

Input

Drawn gate length of Q2, in microns

vlow

Input

Start of the gate-source voltage (VGS) search, in volts

vhigh

Input

End of the VGS search, in volts

vds

Input

Drain bias, in volts

vbs

Input

Substrate bias, in volts

ithr

Input

Drain-source trigger current (IDS), in amperes

vstep

Input

VGS step size, in volts

npts

Input

Number of points in the VGS sweep

kflag

Output

Returned status flag:

0 = Normal completion

1 = First g

m

measurement failed

2 = Second g

m

measurement failed

Returns

Output

Estimated gate length reduction

This subroutine estimates MOSFET gate length reduction (L) using transconductance (gm) data obtained from

the vtext2 subroutine for two different transistors.

Usage

double deltl1(int d1, int g1, int s1, int sub1, double l1, int d2, int g2, int s2,

int sub2, double l2, double vlow, double vhigh, double vds, double vbs, double

ithr, double vstep, int npts, int *kflag)

Details

The npts parameter must be greater than 5. If a value less than 5 is used, the subroutine uses 5

points by default.

The equation used for this calculation is:

L = ((Slope1 / Slope2) (L1 - L2) / (Slope1 /Slope2 - 1.0)

Use this subroutine to infer the variability in the channel length based on the transconductance

comparison of two devices, where the reference device is considerably larger than the second device.

Page 36

Section 3: Test subroutine library reference S530 Parametric Test System Test Subroutine Library User's Manual

3-24 S530-907-01 Rev. A / September 2015

Source-measure units (SMUs)

Result = deltl1(d1, g1, s1, sub1, l1, d2, g2, s2, sub2, l2, vlow, vhigh, vds,

vbs, ithr, vstep, npts, &kflag)

d1

Input

The drain pin of Q1

g1

Input

The gate pin of Q1

s1

Input

The source pin of Q1

sub1

Input

The substrate pin of Q1

w1

Input

The drawn gate width of Q1, in microns

d2

Input

The drain pin of Q2

g2

Input

The gate pin of Q2

s2

Input

The source pin of Q2

sub2

Input

The substrate pin of Q2

w2

Input

The drawn gate width of Q2, in microns

vlow

Input

Start of the gate-source voltage (VGS) search, in volts

vhigh

Input

End of the VGS search, in volts

vds

Input

Drain bias, in volts

vbs

Input

Substrate bias, in volts

ithr

Input

Drain-source trigger current (IDS), in amperes

vstep

Input

VGS step size, in volts

npts

Input

Number of points in the VGS sweep

kflag

Output

Returned status flag:

0 = Normal completion

1 = First V

T

measurement failed

2 = Second V

T

measurement failed

Returns

Output

Estimated gate width reduction

See the vtext2 (on page 3-76) subroutine.

Example

deltw1

This subroutine estimates the gate width reduction parameter (W) for a MOSFET using two values of threshold

voltage (VT) obtained from the vtext2 subroutine.

Usage

double deltw1(int d1, int g1, int s1, int sub1, double w1, int d2, int g2, int s2,

int sub2, double w2, double vlow, double vhigh, double vds, double vbs, double

ithr, double vstep, int npts, int *kflag)

Page 37

S530 Parametric Test System Test Subroutine Library User's Manual Section 3: Test subroutine library reference

S530-907-01 Rev. A / September 2015 3-25

Details

result = deltw1(d1, g1, s1, sub1, w1, d2, g2, s2, sub2, w2, vlow, vhigh, vds,

vbs, ithr, vstep, npts, &kflag)

e

Input

The emitter pin of the device

b

Input

The base pin of the device

c

Input

The collector pin of the device

sub

Input

The substrate pin of the device

ibe

Input

Forced base current, in amperes

vstart

Input

The start of the collector-emitter voltage (VCE) sweep

vstop

Input

The end of the VCE sweep

npts

Input

The number of points in the sweep

vsub

Input

Substrate bias, in volts

slope

Output

The calculated inductance

iflag

Output

Status flag:

0 = Normal completion

1 = No valid data for fit

2 = Calculated slope = 0.0

3 = Developed base voltage is within 98 % of the 3 V voltage limit

r

Output

Correlation coefficient

early

Output

Calculated early voltage

W is calculated using the following equation:

L = ((Slope2 / Slope1) W1 - W2) / (Slope2 /Slope1 - 1.0)

The npts parameter must be greater than 5. If a value less than 5 is used, the subroutine uses 5

points by default.

Source-measure units (SMUs)

See the vtext2 (on page 3-76) subroutine.

Example

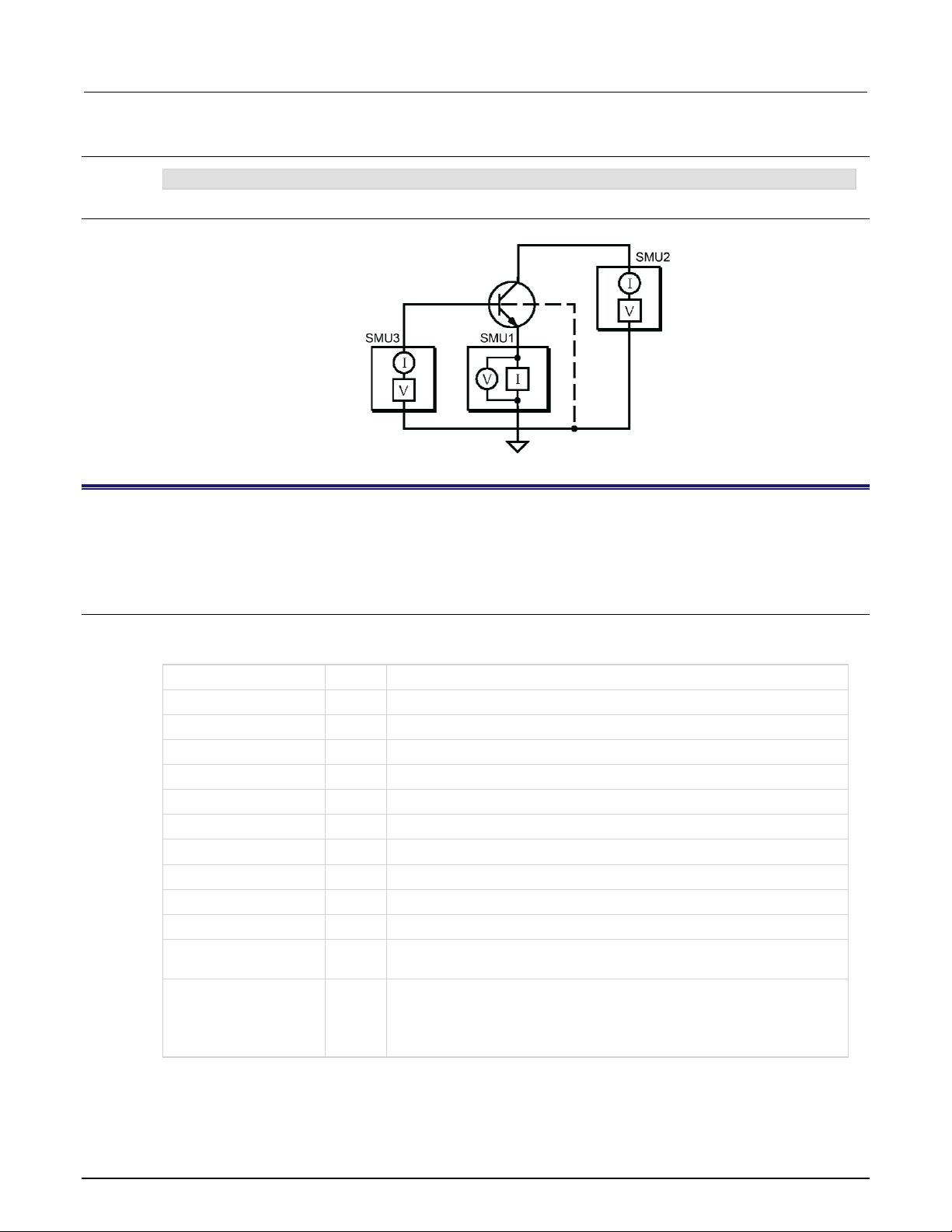

ev

This subroutine calculates the early voltage at constant base-emitter current (IBE).

Usage

void ev(int e, int b, int c, int sub, double ibe, double vstart, double vstop, int

npts, double vsub, double *slope, double *iflag, double *r, double *early);

Page 38

Section 3: Test subroutine library reference S530 Parametric Test System Test Subroutine Library User's Manual

3-26 S530-907-01 Rev. A / September 2015

Details

ev(e, b, c, sub, ibe, vstart, vstop, npts, vsub, &slope, &iflag, &r, &early);

This subroutine estimates the forward early voltage of a bipolar device at constant IBE. The device is

connected in the common-emitter configuration, and a collector-emitter voltage (VCE) and collectoremitter current (ICE) data set is generated. A linear least squares (LLSQ) line is fit to the data, and

the X-intercept is returned as the forward early voltage. The correlation coefficient is returned as an

estimate of the fit.

When calling this routine, make sure the VCE start and stop values have the device well into

saturation.

If a zero or negative substrate pin is specified, the substrate is left floating. If the pin number is

greater than 0 and V

connected and forced.

V/I polarities

NPN +VCE, +IBE and -VSUB

is less than 0.9 mV, the substrate is grounded. In all other cases, it is

SUB

Source-measure units (SMUs)

SMU1: Sweeps VCE, default current limit, measures ICE

SMU2: Forces ibe, 3 V voltage limit

PNP -VCE, -IBE and -VSUB

Example

Schematic

SMU3: Forces vsub, default current limit

Page 39

S530 Parametric Test System Test Subroutine Library User's Manual Section 3: Test subroutine library reference

S530-907-01 Rev. A / September 2015 3-27

fimv

h1

Input

HI pin 1

h2

Input

HI pin 2

h3

Input

HI pin 3

h4

Input

HI pin 4

l1

Input

LO pin 1

l2

Input

LO pin 2

l3

Input

LO pin 3

l4

Input

LO pin 4

v

Output

Measured voltage

i

Input

Forced current, in amperes

Returns

Output

Measured voltage:

0.0 = All high or low pins are <1

result = fimv(h1, h2, h3, h4, l1, l2, l3, l4, &v, i);

This subroutine forces a current and measures a voltage on a device with four high (source) pins and four ground

pins. This is an alternate version of the fvmi subroutine.

Usage

double fimv(int h1, int h2, int h3, int h4, int l1, int l2, int l3, int l4, double

*v, double i);

Details

Input a -1 if the pin is not to be used.

A delay is incorporated into the fimv subroutine; this delay is the calculated time required for stable

forcing of i with a 30 V voltage limit (default).

Source-measure units (SMUs)

SMU1: Forces current, default voltage limit, measures voltage

Example

Schematic

Figure 7: Schematic for the fimv subroutine

Page 40

Section 3: Test subroutine library reference S530 Parametric Test System Test Subroutine Library User's Manual

3-28 S530-907-01 Rev. A / September 2015

fnddat

x

Input

Input x array

npts

Input

Number of points in the input array

y

Input

Input y array

npts1

Input

Number of points in the input array

x1

Input

Minimum valid point

x2

Input

Maximum valid point

xnew

Output

Screened x array

np1

Input

Number of points in the output array

ynew

Output

Screened y array

npt2

Input

Number of points in the output array

np

Output

Number of points in the output array

code

Input

Search "x" or "y" data array

Returns

Output

The new array

fnddat(&x, npts, &y, npts1, x1, x2, &xnew, np1, &ynew, np2, &np, code)

This subroutine searches an array and returns a new array.

Usage

void fnddat(double *x, int npts, double *y, int npts1, double x1, double x2, double

*xnew, int np1, double *ynew, int np2, int *np, char code)

Details

Example

This subroutine searches a data set of x and y values for a specified range of data and returns two

new arrays with the screened data. Use this routine in other routines to remove unwanted or bad

points from measured data.

The x, y, xnew, and ynew parameters are all adjustable dimensioned arrays. The calling routine

should dimension them all the same.

The code parameter searches either the x data or y data. For example, in most measurement

routines, either the voltage or current is fixed, and the other variable is measured. The measured

variable is normally what is screened.

Page 41

S530 Parametric Test System Test Subroutine Library User's Manual Section 3: Test subroutine library reference

S530-907-01 Rev. A / September 2015 3-29

fndtrg

low

Input

The low value

high

Input

The high value

Returns

Output

TRUE = Use the Less Than trigger

FALSE = Use the Greater Than trigger

result = fndtrg(low, high)

h1

Input

HI pin 1

h2

Input

HI pin 2

h3

Input

HI pin 3

h4

Input

HI pin 4

l1

Input

LO pin 1

l2

Input

LO pin 2

l3

Input

LO pin 3

l4

Input

LO pin 4

v

Input

Forced voltage, in volts

i

Output

Measured current

Returns

Output

Measured current:

0.0 = All high or low pins are < 1

+4.0E+21 = Measured voltage is within 98 % of the default current

limit

This subroutine determines which native mode trigger to use.

Usage

int fndtrg(double low, double high)

Details

This subroutine compares the algebraic magnitudes of the input parameters and sets its return value

TRUE if TRIGL should be used or FALSE if TRIGH should be used.

Example

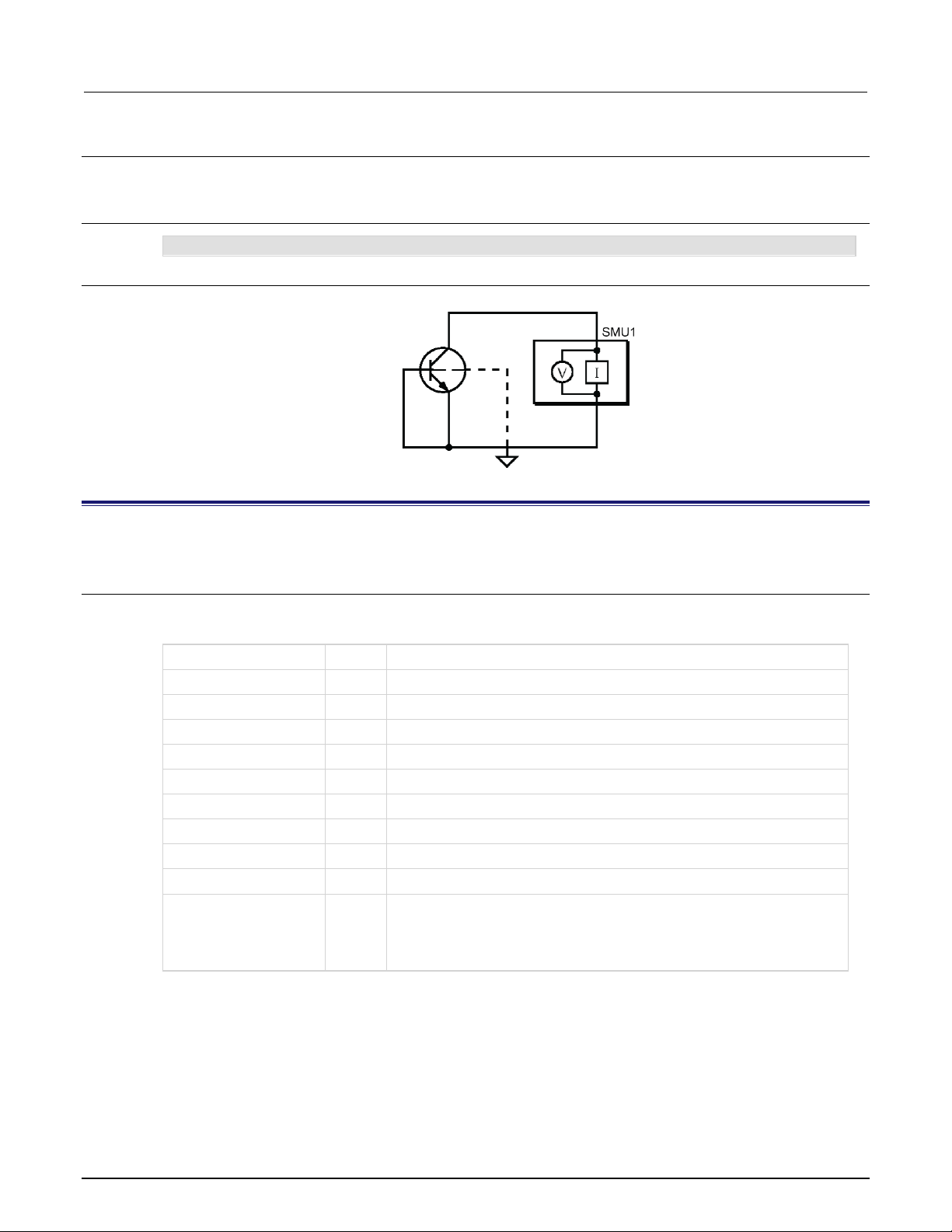

fvmi

This primitive subroutine forces a voltage and measures a current on a device with four input pins and four ground

pins.

Usage

double fvmi(int h1, int h2, int h3, int h4, int l1, int l2, int l3, int l4, double

v, double *i);

Details

This subroutine is normally used for defect structures with multiple high pins and ground pins.

Page 42

Section 3: Test subroutine library reference S530 Parametric Test System Test Subroutine Library User's Manual

3-30 S530-907-01 Rev. A / September 2015

Source-measure units (SMUs)

result = fvmi(h1, h2, h3, h4, l1, l2, l3, l4, v, &i);

Example

Schematic

SMU1: Forces voltage, default current limit, measures current

Figure 8: Schematic for the fvmi subroutine

Page 43

S530 Parametric Test System Test Subroutine Library User's Manual Section 3: Test subroutine library reference

S530-907-01 Rev. A / September 2015 3-31

gamma1

d

Input