Page 1

KPCI-PIO32IOA & KPCI-PDISO8A

PCI Bus Isolated I/O Board

User’s Manual

A GREATER MEASURE OF CONFIDENCE

Page 2

WARRANTY

Hardware

Keithley Instruments, Inc. warrants that, for a period of three (3) years from the date of shipment, the Keithley Hardware product will be free from defects

in materials or workmanship. This warranty will be honored provided the defect has not been caused by use of the Keithley Hardware not in accordance

with the instructions for the product. This warranty shall be null and void upon: (1) any modification of Keithley Hardware that is made by other than Keithley and not approved in writing by Keithley or (2) operation of the Keithley Hardware outside of the environmental specifications therefore.

Upon receiving notification of a defect in the Keithley Hardware during the warranty period, Keithley will, at its option, either repair or replace such

Keithley Hardware. During the first ninety days of the warranty period, Keithley will, at its option, supply the necessary on site labor to return the

product to the condition prior to the notification of a defect. Failure to notify Keithley of a defect during the warranty shall relieve Keithley of its obligations and liabilities under this warranty.

Other Hardware

The portion of the product that is not manufactured by Keithley (Other Hardware) shall not be covered by this warranty, and Keithley shall have no

duty of obligation to enforce any manufacturers' warranties on behalf of the customer. On those other manufacturers’ products that Keithley purchases for resale, Keithley shall have no duty of obligation to enforce any manufacturers’ warranties on behalf of the customer.

Software

Keithley warrants that for a period of one (1) year from date of shipment, the Keithley produced portion of the software or firmware (Keithley Software)

will conform in all material respects with the published specifications provided such Keithley Software is used on the product for which it is intended

and otherwise in accordance with the instructions therefore. Keithley does not warrant that operation of the Keithley Software will be uninterrupted or

error-free and/or that the Keithley Software will be adequate for the customer's intended application and/or use. This warranty shall be null and void

upon any modification of the Keithley Software that is made by other than Keithley and not approved in writing by Keithley.

If Keithley receives notification of a Keithley Software nonconformity that is covered by this warranty during the warranty period, Keithley will review

the conditions described in such notice. Such notice must state the published specification(s) to which the Keithley Software fails to conform and the

manner in which the Keithley Software fails to conform to such published specification(s) with sufficient specificity to permit Keithley to correct such

nonconformity. If Keithley determines that the Keithley Software does not conform with the published specifications, Keithley will, at its option, provide

either the programming services necessary to correct such nonconformity or develop a program change to bypass such nonconformity in the Keithley

Software. Failure to notify Keithley of a nonconformity during the warranty shall relieve Keithley of its obligations and liabilities under this warranty.

Other Software

OEM software that is not produced by Keithley (Other Software) shall not be covered by this warranty, and Keithley shall have no duty or obligation

to enforce any OEM's warranties on behalf of the customer.

Other Items

Keithley warrants the following items for 90 days from the date of shipment: probes, cables, rechargeable batteries, diskettes, and documentation.

Items not Covered under Warranty

This warranty does not apply to fuses, non-rechargeable batteries, damage from battery leakage, or problems arising from normal wear or failure to

follow instructions.

Limitation of Warranty

This warranty does not apply to defects resulting from product modification made by Purchaser without Keithley's express written consent, or by

misuse of any product or part.

Disclaimer of Warranties

EXCEPT FOR THE EXPRESS WARRANTIES ABOVE KEITHLEY DISCLAIMS ALL OTHER WARRANTIES, EXPRESS OR IMPLIED,

INCLUDING WITHOUT LIMITATION, ALL IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. KEITHLEY DISCLAIMS ALL WARRANTIES WITH RESPECT TO THE OTHER HARDWARE AND OTHER SOFTWARE.

Limitation of Liability

KEITHLEY INSTRUMENTS SHALL IN NO EVENT, REGARDLESS OF CAUSE, ASSUME RESPONSIBILITY FOR OR BE LIABLE FOR:

(1) ECONOMICAL, INCIDENTAL, CONSEQUENTIAL, INDIRECT, SPECIAL, PUNITIVE OR EXEMPLARY DAMAGES, WHETHER

CLAIMED UNDER CONTRACT, TORT OR ANY OTHER LEGAL THEORY, (2) LOSS OF OR DAMAGE TO THE CUSTOMER'S DATA OR

PROGRAMMING, OR (3) PENALTIES OR PENALTY CLAUSES OF ANY DESCRIPTION OR INDEMNIFICATION OF THE CUSTOMER

OR OTHERS FOR COSTS, DAMAGES, OR EXPENSES RELATED TO THE GOODS OR SERVICES PROVIDED UNDER THIS WARRANTY.

Keithley Instruments, Inc. 28775 Aurora Road • Cleveland, Ohio 44139 • 440-248-0400 • Fax: 440-248-6168

1-888-KEITHLEY (534-8453) • www.keithley.com

Sales Offices:BELGIUM: Bergensesteenweg 709 • B-1600 Sint-Pieters-Leeuw • 02-363 00 40 • Fax: 02/363 00 64

CHINA: Yuan Chen Xin Building, Room 705 • 12 Yumin Road, Dewai, Madian • Beijing 100029 • 8610-6202-2886 • Fax: 8610-6202-2892

FINLAND: Tietäjäntie 2 • 02130 Espoo • Phone: 09-54 75 08 10 • Fax: 09-25 10 51 00

FRANCE: 3, allée des Garays • 91127 Palaiseau Cédex • 01-64 53 20 20 • Fax: 01-60 11 77 26

GERMANY: Landsberger Strasse 65 • 82110 Germering • 089/84 93 07-40 • Fax: 089/84 93 07-34

GREAT BRITAIN: Unit 2 Commerce Park, Brunel Road • Theale • Berkshire RG7 4AB • 0118 929 7500 • Fax: 0118 929 7519

INDIA: Flat 2B, Willocrissa • 14, Rest House Crescent • Bangalore 560 001 • 91-80-509-1320/21 • Fax: 91-80-509-1322

ITALY: Viale San Gimignano, 38 • 20146 Milano • 02-48 39 16 01 • Fax: 02-48 30 22 74

JAPAN: New Pier Takeshiba North Tower 13F • 11-1, Kaigan 1-chome • Minato-ku, Tokyo 105-0022 • 81-3-5733-7555 • Fax: 81-3-5733-7556

KOREA: 2FL., URI Building • 2-14 Yangjae-Dong • Seocho-Gu, Seoul 137-888 • 82-2-574-7778 • Fax: 82-2-574-7838

NETHERLANDS: Postbus 559 • 4200 AN Gorinchem • 0183-635333 • Fax: 0183-630821

SWEDEN: c/o Regus Business Centre • Frosundaviks Allé 15, 4tr • 169 70 Solna • 08-509 04 679 • Fax: 08-655 26 10

SWITZERLAND: Kriesbachstrasse 4 • 8600 Dübendorf • 01-821 94 44 • Fax: 01-820 30 81

TAIWAN: 1FL., 85 Po Ai Street • Hsinchu, Taiwan, R.O.C. • 886-3-572-9077• Fax: 886-3-572-9031

4/02

Page 3

KPCI-PIO32IOA & KPCI-PDISO8A

PCI Bus Isolated I/O Board

User’s Manual

Windows and WindowsNT are registered trademarks of Microsoft Corporation.

DriverLINX is a registered trademark of Scientific Software Tools, Inc.

©2002, Keithley Instruments, Inc.

All rights reserved.

Cleveland, Ohio, U.S.A.

Second Printing, August 2002

Document Number: KPCIPIO32IOA-901-01B

Page 4

Manual Print History

The print history shown below lists the printing dates of all Revisions and Addenda created for this manual. The

Revision Level letter increases alphabetically as the manual undergoes subsequent updates. Addenda, which are

released between Revisions, contain important change information that the user should incorporate immediately into

the manual. Addenda are numbered sequentially. When a new Revision is created, all Addenda associated with the

previous Revision of the manual are incorporated into the new Revision of the manual. Each new Revision includes a

revised copy of this print history page.

Revision A (Document Number KPCIPIO32IOA-901-01A) ............................................................ February 2002

Revision B (Document Number KPCIPIO32IOA-901-01A) ...............................................................August 2002

All Keithley product names are trademarks or registered trademarks of Keithley Instruments, Inc.

Other brand and product names are trademarks or registered trademarks of their respective holders.

Page 5

Safety Precautions

The following safety precautions should be observed before using

this product and any associated instrumentation. Although some instruments and accessories would normally be used with non-hazardous voltages, there are situations where hazardous conditions

may be present.

This product is intended for use by qualified personnel who recognize shock hazards and are familiar with the safety precautions required to avoid possible injury. Read and follow all installation,

operation, and maintenance information carefully before using the

product. Refer to the manual for complete product specifications.

If the product is used in a manner not specified, the protection provided by the product may be impaired.

The types of product users are:

Responsible body is the individual or group responsible for the use

and maintenance of equipment, for ensuring that the equipment is

operated within its specifications and operating limits, and for ensuring that operators are adequately trained.

Operators use the product for its intended function. They must be

trained in electrical safety procedures and proper use of the instrument. They must be protected from electric shock and contact with

hazardous live circuits.

Maintenance personnel perform routine procedures on the product

to keep it operating properly, for example, setting the line voltage

or replacing consumable materials. Maintenance procedures are described in the manual. The procedures explicitly state if the operator

may perform them. Otherwise, they should be performed only by

service personnel.

Service personnel are trained to work on live circuits, and perform

safe installations and repairs of products. Only properly trained service personnel may perform installation and service procedures.

Keithley products are designed for use with electrical signals that

are rated Installation Category I and Installation Category II, as described in the International Electrotechnical Commission (IEC)

Standard IEC 60664. Most measurement, control, and data I/O signals are Installation Category I and must not be directly connected

to mains voltage or to voltage sources with high transient over-voltages. Installation Category II connections require protection for

high transient over-voltages often associated with local AC mains

connections. Assume all measurement, control, and data I/O connections are for connection to Category I sources unless otherwise

marked or described in the Manual.

Exercise extreme caution when a shock hazard is present. Lethal

voltage may be present on cable connector jacks or test fixtures. The

American National Standards Institute (ANSI) states that a shock

hazard exists when voltage levels greater than 30V RMS, 42.4V

peak, or 60VDC are present. A good safety practice is to expect

that hazardous voltage is present in any unknown circuit before

measuring.

Operators of this product must be protected from electric shock at

all times. The responsible body must ensure that operators are prevented access and/or insulated from every connection point. In

some cases, connections must be exposed to potential human contact. Product operators in these circumstances must be trained to

protect themselves from the risk of electric shock. If the circuit is

capable of operating at or above 1000 volts, no conductive part of

the circuit may be exposed.

Do not connect switching cards directly to unlimited power circuits.

They are intended to be used with impedance limited sources.

NEVER connect switching cards directly to AC mains. When connecting sources to switching cards, install protective devices to limit fault current and voltage to the card.

Before operating an instrument, make sure the line cord is connected to a properly grounded power receptacle. Inspect the connecting

cables, test leads, and jumpers for possible wear, cracks, or breaks

before each use.

When installing equipment where access to the main power cord is

restricted, such as rack mounting, a separate main input power disconnect device must be provided, in close proximity to the equipment and within easy reach of the operator.

For maximum safety, do not touch the product, test cables, or any

other instruments while power is applied to the circuit under test.

ALWAYS remove power from the entire test system and discharge

any capacitors before: connecting or disconnecting cables or jumpers, installing or removing switching cards, or making internal

changes, such as installing or removing jumpers.

Do not touch any object that could provide a current path to the common side of the circuit under test or power line (earth) ground. Always

make measurements with dry hands while standing on a dry, insulated

surface capable of withstanding the voltage being measured.

The instrument and accessories must be used in accordance with its

specifications and operating instructions or the safety of the equipment may be impaired.

Do not exceed the maximum signal levels of the instruments and accessories, as defined in the specifications and operating information, and as shown on the instrument or test fixture panels, or

switching card.

When fuses are used in a product, replace with same type and rating

for continued protection against fire hazard.

Chassis connections must only be used as shield connections for

measuring circuits, NOT as safety earth ground connections.

If you are using a test fixture, keep the lid closed while power is applied to the device under test. Safe operation requires the use of a

lid interlock.

5/02

Page 6

If or is present, connect it to safety earth ground using the

wire recommended in the user documentation.

!

The symbol on an instrument indicates that the user should refer to the operating instructions located in the manual.

The symbol on an instrument shows that it can source or measure 1000 volts or more, including the combined effect of normal

and common mode voltages. Use standard safety precautions to

avoid personal contact with these voltages.

The WARNING heading in a manual explains dangers that might

result in personal injury or death. Always read the associated information very carefully before performing the indicated procedure.

The CAUTION heading in a manual explains hazards that could

damage the instrument. Such damage may invalidate the warranty.

Instrumentation and accessories shall not be connected to humans.

Before performing any maintenance, disconnect the line cord and

all test cables.

To maintain protection from electric shock and fire, replacement

components in mains circuits, including the power transformer, test

leads, and input jacks, must be purchased from Keithley Instruments. Standard fuses, with applicable national safety approvals,

may be used if the rating and type are the same. Other components

that are not safety related may be purchased from other suppliers as

long as they are equivalent to the original component. (Note that selected parts should be purchased only through Keithley Instruments

to maintain accuracy and functionality of the product.) If you are

unsure about the applicability of a replacement component, call a

Keithley Instruments office for information.

To clean an instrument, use a damp cloth or mild, water based

cleaner. Clean the exterior of the instrument only. Do not apply

cleaner directly to the instrument or allow liquids to enter or spill

on the instrument. Products that consist of a circuit board with no

case or chassis (e.g., data acquisition board for installation into a

computer) should never require cleaning if handled according to instructions. If the board becomes contaminated and operation is affected, the board should be returned to the factory for proper

cleaning/servicing.

Page 7

Table of Contents

1 Overview

How the manual is organized ............................................................................................................................. 1-2

How to distinguish special text items ................................................................................................................. 1-2

Safety symbols and terms ................................................................................................................................... 1-3

How to move around the electronic version of the manual ............................................................................... 1-3

2 General Description

Specifications ..................................................................................................................................................... 2-2

System requirements .......................................................................................................................................... 2-2

Functional description ........................................................................................................................................ 2-2

Solid-state relay switching ......................................................................................................................... 2-2

Other I/O characteristics ............................................................................................................................ 2-3

Software ............................................................................................................................................................. 2-3

3 Installation

Installing the software ........................................................................................................................................ 3-2

Software options ........................................................................................................................................ 3-2

Installing DriverLINX ............................................................................................................................... 3-3

Installing application software and drivers ................................................................................................ 3-4

Installing the KPCI-PIO32IOA and KPCI-PDISO8A boards ........................................................................... 3-4

Configuring and checking the board and DriverLINX installations .................................................................. 3-6

Configuring the combined board and DriverLINX installations ............................................................... 3-6

Checking the combined board and DriverLINX installations .................................................................... 3-6

Connecting the KPCI-PIO32IOA and KPCI-PDISO8A boards ........................................................................ 3-8

Identifying I/O connector pin assignments ................................................................................................ 3-8

Connecting interface accessories ............................................................................................................. 3-10

Wiring I/O to your external circuits ........................................................................................................ 3-12

Input and output precautions .................................................................................................................... 3-12

Input and output connections ................................................................................................................... 3-13

I/O considerations .................................................................................................................................... 3-14

Combining output channels ..................................................................................................................... 3-15

4 External Interrupts

External interrupt description ............................................................................................................................. 4-2

Interrupt pins .............................................................................................................................................. 4-2

Data latching .............................................................................................................................................. 4-3

External interrupt application ............................................................................................................................. 4-3

i

Page 8

5 Troubleshooting

Identifying symptoms and possible causes ......................................................................................................... 5-2

Systematic problem isolation ............................................................................................................................. 5-3

General problem isolation procedure ......................................................................................................... 5-3

Specified tests ................................................................................................................................................... 5-11

Checking for board as a PCI resource ...................................................................................................... 5-11

I/O test ...................................................................................................................................................... 5-12

Block diagram .................................................................................................................................................. 5-14

Technical support ............................................................................................................................................. 5-15

A Specifications

B I/O Address Mapping

General PCI address assignments ...................................................................................................................... B-2

Register assignments ......................................................................................................................................... B-3

Control and data registers .......................................................................................................................... B-3

Interrupt control/status register .................................................................................................................. B-4

Manipulating control and data registers ............................................................................................................ B-7

General approach to manipulating control and data registers ................................................................... B-7

C Glossary

ii

Page 9

List of Illustrations

3 Installation

Figure 3-1 KPCI-PIO32IOA board configuration ....................................................................................................... 3-8

Figure 3-2 KPCI-PDISO8A board configuration ........................................................................................................ 3-9

Figure 3-3 Connections to STP-36 screw terminal connector accessory .................................................................. 3-11

Figure 3-4 Typical KPCI-PIO32IOA and KPCI-PDISO8A input/output connections ............................................. 3-13

5 Troubleshooting

Figure 5-1 Problem isolation flowchart ....................................................................................................................... 5-4

Figure 5-2 Mating connector wiring for I/O test ....................................................................................................... 5-13

Figure 5-3 KPCI board block diagram ...................................................................................................................... 5-14

iii

Page 10

List of Tables

2 General Description

Table 2-1 System requirements .................................................................................................................................. 2-2

3 Installation

Table 3-1 KPCI-PIO32IOA and KPCI-PDISO8A I/O connector pin assignments ................................................... 3-9

Table 3-2 STP-36 screw terminal designations ........................................................................................................ 3-10

4 External Interrupts

Table 4-1 Connector pins used for external interrupt function .................................................................................. 4-2

Table 4-2 External-interrupt responses ....................................................................................................................... 4-4

5 Troubleshooting

Table 5-1 Basic troubleshooting information ............................................................................................................. 5-2

Table 5-2 DriverLINX board channel assignments .................................................................................................. 5-12

B I/O Address Mapping

Table B-1 Register mapping ...................................................................................................................................... B-3

Table B-2 Control register bit functions for each port ............................................................................................... B-4

Table B-3 Bit functions for interrupt control/status register ...................................................................................... B-5

v

Page 11

1

Overview

Page 12

•

•

•

•

•

•

•

•

•

•

•

•

•

1-2 Overview KPCI-PIO32IOA and KPCI-PDISO8A User’s Manual

This manual contains descriptive information and installation and use instructions for the KPCIPIO32IOA and KPCI-PDISO8A isolated I/O boards.

The manual is intended for data acquisition system designers, engineers, technicians, scientists,

and other users responsible for setting up, cabling, and wiring signals to KPCI-PIO32IOA and

KPCI-PDISO8A boards. To follow the information and instructions contained in this manual,

you must be familiar with the operation of Windows 98, Me, NT, 2000, or XP with basic dataacquisition principles, and with your application. However, if you find unfamiliar terms in this

manual, check the Glossary in Appendix C. To locate topics discussed in this manual, search the

index.

To use this manual effectively, review the remaining brief topics in this preface:

The organization of the manual.

The special font/typeface conventions used in the manual.

Moving quickly to cross-referenced parts of the manual (in the electronic [PDF] version).

How the manual is organized

In addition to this Overview, the

nized as follows:

Section 2 briefly describes features and characteristics of the KPCI-PIO32IOA and KPCI-

PDISO8A.

Section 3 first describes software options and installation notes and then the following oper-

ations (which must be done after the software is installed):

– Installing the board.

– Configuring the combined board and software installations.

– Checking the combined board and software installation.

– Installing accessories, and connecting signals.

Section 4 briefly describes the ability to configure two of the I/O lines as external interrupt

enable and external interrupt request lines and identifies the connector pins used.

Section 5 describes how to troubleshoot your system and obtain technical support.

Appendix A contains KPCI-PIO32IOA and KPCI-PDISO8A specifications.

Appendix B describes memory-mapping information for special situations. Appendix B can

be disregarded under normal conditions. Use the DriverLINX driver provided with your

board for virtually all programming situations.

Appendix C is a glossary of some terms used in this manual.

An Index completes the manual.

KPCI-PIO32IOA and KPCI-PDISO8A User’s Manual is orga-

How to distinguish special text items

Italic, bold, and upper-case letters, the Courier font, and quotation marks distinguish certain text

items from the general text. The following text conventions are used (exclusive of headings):

10 point Times Bold distinguishes the following:

– All Windows 98/Me/NT/2000/XP user-interaction items: commands, screen messages,

menu names, menu options, and dialog-box items—including captions, user selections,

and typed user inputs (but not including dialog box names, which are in regular text).

10 point Times Italic distinguishes the following:

– Emphasis in general.

– Cross-references to other documents, such as other manuals or books.

– NOTE statements.

Page 13

•

•

•

•

•

•

•

KPCI-PIO32IOA and KPCI-PDISO8A User’s Manual Overview 1-3

10 POINT TIMES UPPER CASE distinguishes the following:

– Switches, such as ON and OFF.

– Keyboard keys, such as ENTER.

•

10 point Courier

“Double quote marks” distinguish the following:

– Cross references to other manual sections, such as “Troubleshooting.”

– Literals, such as when referring to the “5V” labels on I/O connectors.

distinguishes software code statements.

Safety symbols and terms

The following symbols and terms may be found on the board or used in this manual.

!

The symbol indicates that the user should refer to the operating instructions located in the

manual.

The symbol shows that high voltage may be present on the terminal(s). Use standard safety

precautions to avoid personal contact with these voltages.

The WARNING heading used in this manual explains dangers that might result in personal

injury or death. Always read the associated information very carefully before performing the

indicated procedure.

The CAUTION heading used in this manual explains hazards that could damage the board.

Such damage may invalidate the warranty.

How to move around the electronic version of the manual

When reading the electronic PDF version of this manual, use Acrobat Reader View and Tools

menu selections to move generally through the manual. Additionally, mouse-click on special

links in the manual to jump directly to the page of a referenced item, as follows:

Mouse-click the top margin of any page to jump to the Table of Contents.

Mouse-click on any Index or Table of Contents (TOC) page number to jump to the page.

Mouse-click on any of these cross references to jump to the cross-referenced figure, table,

section, or subsection. Cross references are not framed in red—in contrast to page numbers

in the Index and Table of Contents.

– Figure number headings, such as Figure 3-1.

– Table number headings, such as Table 3-1.

– Section and subsection headings that are enclosed in quotes, such as “How the manual is

organized.”

To return from the referenced item to what you were reading before you jumped to the referenced item—the Index, TOC, top page margin, or cross reference—do either of the following:

Hold down the CONTROL key and press the [ - ] key (i.e. press CONTROL + -).

In the Acrobat Reader View menu, click Go Back .

Page 14

2

General Description

Page 15

•

•

2-2 General Description KPCI-PIO32IOA and KPCI-PDISO8A User’s Manual

Specifications

General specifications are listed in “Specifications,” Appendix A. I/O connections are identified

in Section 3, and I/O addresses (needed by advanced programmers, only) are defined in “I/O

Address Mapping,” Appendix B.

System requirements

The system capabilities required to run the KPCI-PIO32IOA and KPCI-PDISO8A board, and to

use the DriverLINX software supplied with the board, are listed in Table 2-1.

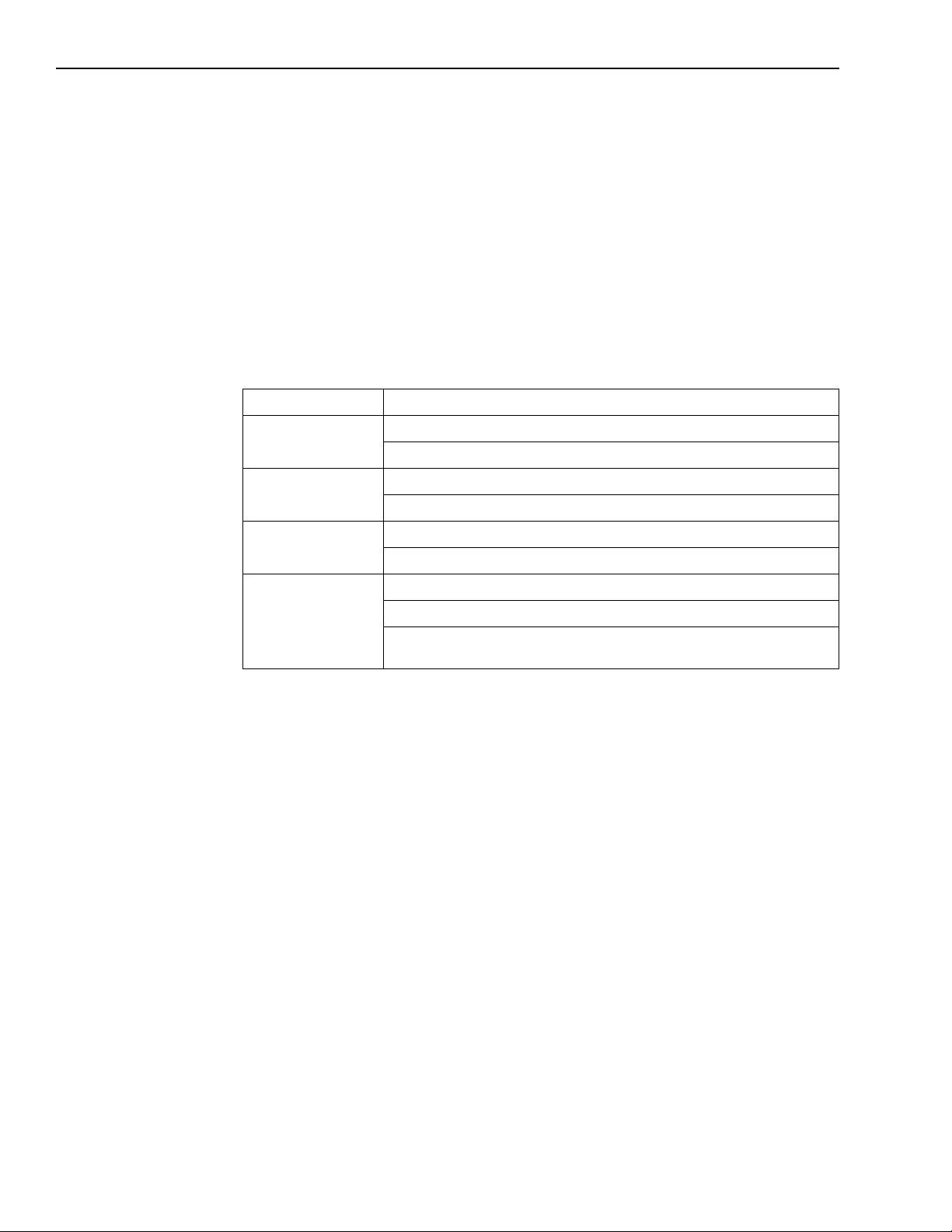

Table 2-1

System requirements

CPU Type

Operating System

Memory

Hard Disk Space

Other

* Any CD-ROM drive that came installed with the required computer should be satisfactory. However, if you have

post-installed an older CD-ROM drive or arrived at your present system by updating the microprocessor or replacing

the motherboard, be aware that some early CD-ROM drives do not support the long file names often used in 32-bit

Windows files.

Functional description

The KPCI-PIO32IOA and KPCI-PDISO8A each contain isolated control inputs and isolated

solid-state relay switching outputs on a PCI interface board. Both cards work in a Windows

environment and take advantage of the 32-bit bus width.

Pentium or higher processor on motherboard with PCI bus version 2.1.

Windows® 95, 98, or Me.

Windows® NT (version 4.0 or higher), 2000, or XP.

16 MB or greater RAM when running Windows® 95, 98, or Me.

32 MB or greater RAM when running Windows® NT, 2000, or XP.

4 MB for minimum installation.

50 MB for maximum installation.

A CD-ROM drive*.

A free PCI bus expansion slot.

Enough reserve computer power supply capacity to power the board,

which draws 500mA from the 5V supply (maximum).

Solid-state relay switching

The KPCI-PIO32IOA’s 32 isolated I/O lines and KPCI-PDISO8A’s 16 isolated I/O lines include:

Control inputs are solid-state, opto-isolated (16 for the KPCI-PIO32IOA; 8 for the

KPCI-PDISO8A). Maximum control input voltages are: ±60V DC (logic high); ±1V DC

(logic low).

Relay outputs are solid-state, opto-isolated, N.O. form A (16 for the KPCI-PIO32IOA; 8 for

the KPCI-PDISO8A). Outputs can switch both DC voltages (±60V DC maximum) and AC

voltages (30V RMS maximum) with a maximum load current of 350mA. A relay output will

close when a logic high is applied to the corresponding control input.

Page 16

•

•

•

•

•

KPCI-PIO32IOA and KPCI-PDISO8A User’s Manual General Description 2-3

Under Windows 98/Me, most existing port I/O application programs and data acquisition packages designed for ISA boards work with the KPCI-PIO32IOA and KPCI-PDISO8A board. The

PCI-BIOS-assigned base address is entered in place of a user-assigned base address. (Use of

such programs under Windows NT/2000/XP, not recommended, is much more involved.)

Other I/O characteristics

Additional I/O port characteristics are summarized below:

Two of the KPCI-PIO32IOA and KPCI-PDISO8A general-purpose I/O lines can be alternatively configured via software to be external interrupt enable input, INT_ENN, and external

interrupt request input, INT_REQ.

The KPCI-PIO32IOA and KPCI-PDISO8A can switch currents up to 350mA. Output current capabilities allow the boards to control some motors, solenoids, and relays.

+5V power from the computer power supply is made available at the I/O connector, for use

in external circuits.

Software

NOTE

Control inputs and relay outputs interface via standard 36-pin connector(s). The

KPCI-PIO32IOA has two 36-pin connectors, and the KPCI-PDISO8A has one 36-pin

connector.

Output ports can always be read-accessed without switching the output states, allowing the

output states to be read at any time by the controlling program.

The user can select a fully integrated data acquisition software package (e.g., TestPoint or

LabVIEW) or write a custom program supported by DriverLINX. DriverLINX software is

included with the hardware.

DriverLINX supports programmers who wish to create custom applications using Visual C/C++,

Visual Basic, or Delphi. DriverLINX accomplishes foreground and background tasks to perform

data acquisition. TestPoint is a fully featured, integrated application package with a graphical

drag-and-drop interface, which can be used to create data acquisition applications without programming. LabVIEW is a fully featured graphical programming language used to create virtual

instrumentation.

Refer to Section 3, “Installation,” for more information about software.

The maximum current on each +5V and digital ground pin is 1A. The

+5V supply is not isolated and is available for use only when isolation is

not required by the application.

Page 17

3

Installation

Page 18

•

•

•

•

•

•

•

•

•

3-2 Installation KPCI-PIO32IOA and KPCI-PDISO8A User’s Manual

•

Section 3 describes the following operations, in the order in which they should be performed:

Reviewing software options and installing software (installation notes that supplement the

Read this first sheet).

Preparing for and doing physical installation of the board.

Configuring the installed software and board.

Identifying I/O connector pins, connecting the board to interface accessories, and wiring the

I/O to external circuits.

NOTE

Installing the software

Software options

The KPCI-PIO32IOA and KPCI-PDISO8A boards have two software options. The user can

select a fully integrated data acquisition software package (e.g., TestPoint or LabVIEW). The

user can also run a custom program in Visual C/C++, Visual Basic, or Delphi using DriverLINX

(included with the hardware). A summary of the pros and cons of using integrated packages or

writing custom programs is provided in the Keithley Full Line Catalog. The KPCI-PIO32IOA

and KPCI-PDISO8A have fully functional driver support for use under Windows.

NOTE

DriverLINX driver software for Windows

DriverLINX software, supplied by Keithley with the KPCI-PIO32IOA and KPCI-PDISO8A

board, provides convenient interfaces to configure and set I/O bits without register-level programming. DriverLINX supports Windows 98, Me, NT, 2000, and XP.

Install the DriverLINX software before installing the KPCI-PIO32IOA

or KPCI-PDISO8A board. Otherwise, the device drivers will be more

difficult to install.

DriverLINX must be installed to run any applications for the board,

whether they are custom-programmed applications or integrated software packages, such as TestPoint or LabVIEW.

Most importantly, however, DriverLINX supports those programmers who wish to create custom applications using Visual C/C++, Visual Basic, or Delphi. DriverLINX accomplishes foreground and background tasks to perform data acquisition. The software includes memory and

data buffer management, event triggering, extensive error checking, and context sensitive online

help.

More specifically, DriverLINX provides application developers a standardized interface to over

100 services for creating foreground and background tasks for the following:

Analog input and output

Digital input and output

Time and frequency measurement

Event counting

Pulse output

Period measurement

Page 19

•

•

•

KPCI-PIO32IOA and KPCI-PDISO8A User’s Manual Installation 3-3

In addition to basic I/O support, DriverLINX also provides:

B

•

uilt-in capabilities to handle memory and data buffer management.

A selection of starting and stopping trigger events, including pre-triggering, mid-point triggering, and post-triggering protocols.

Extensive error checking.

Context-sensitive on-line help system.

Refer to your DriverLINX documentation to determine which services are supported by your

KPCI-PIO32IOA or KPCI-PDISO8A board.

DriverLINX applications can be independent of some differences in data acquisitions boards

because its portable APIs work across various operating systems. This capability eliminates

unnecessary programming when changing operating system platforms.

TestPoint

TestPoint is a fully featured, integrated application package that incorporates many commonly

used math, analysis, report generation, and graphics functions. TestPoint’s graphical

drag-and-drop interface can be used to create data acquisition applications for IEEE-488 instruments, data acquisition boards, and RS232-485 instruments and devices.

TestPoint includes features for controlling external devices, responding to events, processing

data, creating report files, and exchanging information with other Windows programs. It provides libraries for controlling most popular GPIB instruments. OCX and ActiveX controls plug

directly into TestPoint, allowing additional features from third party suppliers.

LabVIEW

LabVIEW is a fully featured graphical programming language used to create virtual instrumentation. It consists of an interactive user interface, complete with knobs, slides, switches, graphs,

strip charts, and other instrument panel controls. Its data driven environment uses function

blocks that are virtually wired together and pass data to each other. The function blocks, which

are selected from palette menus, range from arithmetic functions to advanced acquisition, control, and analysis routines. Also included are debugging tools, help windows, execution highlighting, single stepping, probes, and breakpoints to trace and monitor the data flow execution.

LabVIEW can be used to create professional applications with minimal programming.

Virtual instruments (VIs) compatible with LabVIEW are available for the KPCI-PIO32IOA and

KPCI-PDISO8A.

Installing DriverLINX

Refer to the Read this first document that accompanies your board for installation instructions.

NOTE

Always install DriverLINX before installing the board or LabVIEW support. Both TestPoint and LabVIEW support require DriverLINX to

access the board’s hardware resources.

Page 20

•

•

•

•

3-4 Installation KPCI-PIO32IOA and KPCI-PDISO8A User’s Manual

Installing application software and drivers

Installing the TestPoint support

TestPoint provides an object for control of digital I/O channels based on the DriverLINX driver.

In the directory where TestPoint is installed (C:\TESTPT), find and open DLDIO.TST. The

DLINX.DIO object from this example can be copied and pasted into your custom application.

Check with the following concerning driver updates with TestPoint support for the

KPCI-PIO32IOA and KPCI-PDISO8A:

The TestPoint technical support page of the Keithley web site (www.keithley.com).

The TestPoint manufacturer, Capital Equipment Corporation (CEC).

Installing the LabVIEW software and driver

If you plan to use only run-time LabVIEW applications with your KPCI-PIO32IOA or

KPCI-PDISO8A board, you need not install DriverLINX’s LabVIEW support package.

LabVIEW run-time support is automatically installed when you install and configure

DriverLINX.

However, if you plan to develop custom applications using the LabVIEW Integrated

Development Environment, you must install the DriverLINX Virtual Instruments (VIs). These

VIs are provided on your DriverLINX CD-ROM but do not install automatically when you

install DriverLINX and your board. You must first install the LabVIEW application program and

DriverLINX, then install the DriverLINX VIs.

If you do not install the VIs during the same session in which you install DriverLINX (refer to

your Read this first document), you may install them later as follows:

1. Start setup.exe on the DriverLINX CD-ROM. The DriverLINX Browser introduction screen

appears.

2. Click Next on the DriverLINX Browser introduction screen (or wait a few seconds). The

DriverLINX CD Navigator screen appears.

3. On the DriverLINX CD Navigator screen, click Install DriverLINX . An Install These

DriverLINX Components screen appears.

4. On the Install These DriverLINX Components screen, click LabVIEW™ Support .

5. Follow the series of on-screen instructions that appear.

Installing the KPCI-PIO32IOA and KPCI-PDISO8A boards

This subsection helps you to do the following:

Prepare for the board installation.

Physically install the board.

WARNING Turn off the computer power and disconnect all external circuits

from the board to avoid a possible shock hazard.

CAUTION Handle the board in a static-controlled workstation; wear a

grounded wrist strap. Discharge static voltage differences between

the wrapped board and the handling environment before removing

the board from its protective wrapper. Failure to discharge static

electricity before and during handling may damage semiconductor

circuits on the board.

Handle the board using the mounting bracket. Do not touch the circuit traces or connector contacts when handling the board.

Page 21

KPCI-PIO32IOA and KPCI-PDISO8A User’s Manual Installation 3-5

Checking resources for the board

Ensure that your computer has sufficient resources, particularly power resources, to run your

KPCI-PIO32IOA or KPCI-PDISO8A board. Check the capacity of the computer power supply

and the power requirements of your computer and presently installed boards. Then check the

additional power requirements for this board. (Refer to Appendix A, “Specifications.”) If necessary, free resources by uninstalling other boards.

System responsibility

The system integrator has final responsibility for the EMC of a system containing Keithley

KPCI-PIO32IOA and KPCI-PDISO8A boards. The user must not assume that installation of the

CE-marked KPCI-PIO32IOA or KPCI-PDISO8A in a CE-marked PC will result in a system

with acceptable RFI emissions.

Unwrapping and inspecting the board

NOTE

After you remove the wrapped board from its outer shipping carton, unwrap and inspect it as

follows:

1. Your board is packaged at the factory in an anti-static wrapper. Do not remove the anti-static

wrapper until you have discharged any static electricity voltage differences between the

wrapped board and the environment. Wear a grounded wrist strap. A grounded wrist strap

discharges static electricity from the wrapped board as soon as you hold it. Keep the wrist

strap on until you have finished installing the board.

2. Remove the board from its anti-static wrapping material. (Store the wrapping material for

future use.)

3. Inspect the board for damage. If damage is apparent, arrange to return the board to the factory. Refer to Section 5, “Troubleshooting.”

4. Check the remaining contents of your package against the packing list and immediately

report any missing items.

5. If the inspection is satisfactory, proceed to “Installing the board.”

Install the DriverLINX software before installing the KPCI-PIO32IOA

or KPCI-PDISO8A board. Otherwise, the device drivers will be more

difficult to install.

Installing the board

Install a board in a PCI expansion slot on your computer as follows:

1. Turn power OFF to the computer and to any external circuits attached to the board.

2. Remove the computer chassis cover.

3. Select an unoccupied PCI expansion slot in the rear panel, and remove the corresponding

dummy mounting plate.

4. Insert the PCI connector of the board into the selected PCI slot of the computer. Take care

not to interfere with neighboring boards. Ensure that the board is properly seated in the slot.

5. Secure the mounting bracket of the board to the chassis, using the retaining screw that you

removed when you removed the dummy mounting plate.

6. Continue with the next subsection, “Configuring and checking the board and DriverLINX

installations.”

Page 22

•

•

•

•

3-6 Installation KPCI-PIO32IOA and KPCI-PDISO8A User’s Manual

Configuring and checking the board and DriverLINX installations

This subsection helps you to do the following:

Configure the combined board and DriverLINX installations, using the DriverLINX Plug

and Play Wizard.

Check the combined board and DriverLINX installations by checking the ability to start the

DriverLINX PIO Control Panel.

Configuring the combined board and DriverLINX installations

After physically installing the board, turn on and reboot the computer. The DriverLINX Plug

and Play Wizard screen appears automatically. Run the Wizard immediately by following the

progressive instructions on the screen.

If you do not run the Wizard immediately (you cancel the Wizard after rebooting) it will

normally appear automatically on subsequent reboots until you complete the final page of the

Wizard. However, it is also possible to manually restart it later during the same computer

session, as follows:

1. Open the Windows Explorer.

2. Double click on X:\DrvLINX4\Help\kcpi.bat, where X = the letter of the drive on which you

installed DriverLINX. The Wizard appears.

NOTE

3. On the Windows 98/Me Plug and Play Wizard, click Wizard and follow the series of onscreen instructions that appear. The wizard will first lead you through the steps of installing

your hardware—from a software viewpoint—and configuring it.

4. After you have finished configuring the board and DriverLINX, continue with the next subsection “Checking the combined board and DriverLINX installations.”

You can also start this batch file directly from the CD-ROM by double

clicking on Y:\DrvLINX4\Help\KPCIISO.BAT, where Y = the letter of

your CD-ROM drive.

Checking the combined board and DriverLINX installations

Before making any connections to the board, check the combined board and DriverLINX installations. The ability to start the AIO Panel utility, which is available after you install DriverLINX,

verifies that DriverLINX and the board are installed and configured satisfactorily and are working together.

1. Try starting the AIO Panel as follows:

a. Click the Windows Start tab.

b. In the Start menu, click Programs.

c. Under DriverLINX ➧ Test Panels, find the AIO Panel entry.

d. Click on the AIO Panel entry. The AIO Panel should appear.

e. Based on the results of step 1d, do one of the following:

If you are able to start the AIO Panel, skip to the next subsection, “Connecting the

KPCI-PIO32IOA and KPCI-PDISO8A boards.”

If you are not able to start the AIO Panel, then continue with step 2.

Page 23

•

KPCI-PIO32IOA and KPCI-PDISO8A User’s Manual Installation 3-7

2. If you are unable to start the AIO Panel utility, then check to ensure that the installation is

properly configured and DriverLINX is properly installed. Refer to the subsection

“Configuring the KPCI-PIO32IOA and KPCI-PDISO8A” in the DriverLINX manual Using

DriverLINX with your Hardware—Keithley KPCI-PIO32IOA and KPCI-PDISO8A. To

access this manual on-line, do the following:

a. Click the Windows Start tab.

b. In the Start menu, click Programs.

c. Find the DriverLINX folder, under which you should find the On-line Manuals entry.

d. Click on the On-line Manuals entry. The DriverLINX Printable Documentation table of

contents opens via Acrobat reader.

e. Scroll through the DriverLINX Printable Documentation table of contents and find

Configuration.

f. Under Configuration, click Hardware References. A list of documents appears.

g. In the list of documents, click on Using DriverLINX with Your Hardware—Keithley

KPCI-PIO32IOA and KPCI-PDISO8A. The manual opens via Acrobat Reader.

h. Print the manual now, if possible, to make reference easier.

•

NOTE

3. Reconfigure the installation as required, and if necessary, also reinstall DriverLINX.

NOTE

4. Try again to start the AIO Panel (refer to step 1).

5. Based on the results of step 4, do one of the following:

If you can now start the AIO Panel, DriverLINX and the board are installed and configured properly and are working together. Proceed to the next subsection, “Connecting the

KPCI-PIO32IOA and KPCI-PDISO8A boards.”

If you are still unable to start the AIO Panel, refer to Section 5, “Troubleshooting,” for

additional procedures that may help you isolate the problem.

Acrobat Reader must already be installed. If necessary, you can first

install Acrobat Reader directly from the CD-ROM by double clicking

X:\Acrobat\setup.exe.

If your data acquisition system has no printer, you can display and print

the manual from the CD-ROM at another system. From Windows

Explorer, select the CD-ROM drive (drive “X”). To display the Using

DriverLINX with Your Hardware—Keithley PIO Series manual, double

click on X:\Drvlinx4\Docs\Notes\kpci.pdf.

If you reinstall DriverLINX, refer also to your Read this first sheet

(which is also available on the CD-ROM that came with your board).

Make sure that DriverLINX installs smoothly and completely.

Page 24

•

•

•

3-8 Installation KPCI-PIO32IOA and KPCI-PDISO8A User’s Manual

Connecting the KPCI-PIO32IOA and KPCI-PDISO8A boards

This subsection helps you to do the following:

Identify pin assignments on the board.

Connect interface accessories.

Wire the KPCI-PIO32IOA or KPCI-PDISO8A I/O to your external circuits.

Identifying I/O connector pin assignments

The KPCI-PIO32IOA board has two 36-pin mini-D type I/O connectors for I/O, while the

KPCI-PDISO8A board has one 36-pin mini-D type I/O connector for I/O. Figure 3-1 shows the

configuration of the KPCI-PIO32IOA board, and Figure 3-2 shows the KPCI-PDISO8A board.

Table 3-1 defines connector pin assignments for both boards. Note that those terminals labeled

“IP” are control inputs, while “OP” terminals are switching outputs.

Figure 3-1

KPCI-PIO32IOA board configuration

(Channels 0 through 7)

J101

Low-pass

Filter Jumpers

(Channels 8 through 15)

J102

Page 25

KPCI-PIO32IOA and KPCI-PDISO8A User’s Manual Installation 3-9

Figure 3-2

KPCI-PDISO8A board configuration

(Channels 0 through 7)

J101

Low-pass

Filter Jumpers

Table 3-1

KPCI-PIO32IOA and KPCI-PDISO8A I/O connector pin assignments

Top Connector (J101) Bottom Connector (J102. KPCI-PIO32IOA Only)

Pin Number Signal Pin Number Signal Pin Number Signal Pin Number Signal

1 +5V 19 GND 1 +5V 19 GND

2-20-2-20*3 IP7 21 IP7 *3 IP15 21 IP15

*4 IP6 22 IP6 *4 IP14 22 IP14

5 IP5 23 IP5 5 IP13 23 IP13

6 IP4 24 IP4 6 IP12 24 IP12

7 IP3 25 IP3 7 IP11 25 IP11

8 IP2 26 IP2 8 IP10 26 IP10

9 IP1 27 IP1 9 IP9 27 IP9

10 IP0 28 IP0 10 IP8 28 IP8

11 OP7 29 OP7 11 OP15 29 OP15

12 OP6 30 OP6 12 OP14 30 OP15

13 OP5 31 OP5 13 OP13 31 OP13

14 OP4 32 OP4 14 OP12 32 OP12

15 OP3 33 OP3 15 OP11 33 OP11

16 OP2 34 OP2 16 OP10 34 OP10

17 OP1 35 OP1 17 OP9 35 OP9

18 OP0 36 OP0 18 OP8 36 OP8

*Pin 3 is interrupt enable, and Pin 4 is interrupt request.

Page 26

3-10 Installation KPCI-PIO32IOA and KPCI-PDISO8A User’s Manual

Connecting interface accessories

WARNING Make sure power to all external circuits is turned OFF before con-

necting to the KPCI-PIO32IOA or KPCI-PDISO8A board to avoid a

possible shock hazard.

CAUTION Handle the board at the mounting bracket, using a grounded wrist

strap. Do not touch the circuit traces or connector contacts. If you do

not have a grounded wrist strap, periodically discharge static electricity by placing one hand firmly on a grounded metal portion of the

computer chassis.

Using cable assemblies

The KPCI-PIO32IOA and KPCI-PDISO8A I/O connectors can be mated directly to your

external circuits using locally fabricated cable assemblies. To mate a locally fabricated cable to

an I/O connector, install an IEEE-1284 (1994) connector on the cable. (Mating plug 3M part

number: 10136-6000EC.)

NOTE

The 36-pin mating connector is NOT available in a solder-cup version;

use of the specified connector will require appropriate cable and tooling

to make a reliable insulation displacement connection.

Using the STP-36 screw terminal connector accessory

The screw terminals of the STP-36 connector accessory allow you to make easy I/O connections

to the KPCI-PIO32IOA and KPCI-PDISO8A boards with screw terminals. The STP-36 connects to the board I/O connector (J101 and J102) using a CAB-1284CC cable.

As summarized in Table 3-2, the screw terminal designations (1-36) correspond to the designa-

tions of the J101 and J102 I/O connectors. For example, STP-36 screw terminal 3 corresponds to

pin 3 (IP7) on the board I/O connector J101.

WARNING When using the STP-36, the maximum allowed voltage is 30V RMS,

42.4V peak, or 60V DC. Exceeding this limit could cause an insulation breakdown and a shock hazard.

Table 3-2

STP-36 screw terminal designations

STP-36

Terminal

1 1 13 13 25 25

2 2 14 14 26 26

3 3 15 15 27 27

4 4 16 16 28 28

5 5 17 17 29 29

6 6 18 18 30 30

7 7 19 19 31 31

8 8 20 20 32 32

9 9 21 21 33 33

10 10 22 22 34 34

11 11 23 23 35 35

12 12 24 24 36 36

J101/J102

Pin

STP-36

Terminal

J101/J102

Pin

STP-36

Terminal

J101/J102

Pin

Page 27

KPCI-PIO32IOA and KPCI-PDISO8A User’s Manual Installation 3-11

Figure 3-3 shows typical STP-36 connections to the KPCI board using the designated cables.

Figure 3-3

Connections to STP-36 screw terminal connector accessory

STP-36

STP-36

(CAB-1284CC-0.5 1/2 Meter Long)

Cable

or

(CAB-1284CC-2.0 2 Meters Long)

Cable

(CAB-1284CC-0.5 1/2 Meter Long)

or

(CAB-1284CC-2.0 2 Meters Long)

KPCI-PIO32IOA board

STP-36

(CAB-1284CC-0.5 1/2 Meter Long)

Cable

or

(CAB-1284CC-2.0 2 Meters Long)

KPCI-PDISO8A board

Page 28

3-12 Installation KPCI-PIO32IOA and KPCI-PDISO8A User’s Manual

Wiring I/O to your external circuits

WARNING Ensure that both the computer and the external circuits are turned

OFF before making any connections to avoid a possible shock

hazard.

Input and output precautions

Over-current conditions

CAUTION The KPCI output channels are not designed to handle over-current

conditions. A protected source that is compatible with the KPCI

specifications should always be used. If this is not possible, external

over-current protection is required to protect both the KPCI and the

rest of the system.

Transient voltages

CAUTION The KPCI card provides limited input and output protection to pro-

tect the user PC against high voltage events such as ESD strikes and

voltage surges. If, however, voltage transients over 100V peak are

expected to occur frequently, as with highly inductive load switching, then external protection should be provided to reduce repetitive

stresses on the KPCI card, source and load.

•

Non-isolated power pins

CAUTION The KPCI card provides fuse-protected +5V and ground for conve-

nient use in external circuits. This voltage is supplied from the bus

and is not isolated from the user PC. If isolation is a requirement in

the application, then this supply should either not be used at all, or

be used with some external means of isolating this supply.

Power-up state of channels

NOTE

The power-up state of the input and output channels is as follows:

Input channels — For |V| < ≅ 45V, Z ≅ 22kΩ. For |V| > 45V,

Z ≅ 17kΩ. These channels are always configured as inputs and can

be driven at all times.

• Output channels — These are form A, N.O. SPST style contacts. The

output channels are in a high-impedance state (see specifications in

Appendix A) under any of the following conditions:

– The KPCI card is in the system reset state.

– The system and KPCI card are unpowered.

– The system and the KPCI card are powered but no software com-

mand has been given for actuation (initial state). This state is also

configurable in DriverLINX.

Page 29

KPCI-PIO32IOA and KPCI-PDISO8A User’s Manual Installation 3-13

Input and output connections

Figure 3-4 shows typical input and output connections for one channel. IPnA and IPnB are the

control inputs, while OPnA and OPnB are the switching outputs (n is the channel number). See

Table 3-2 for terminal designations).

Signal voltages are as follows:

• Maximum control input voltages are: ±60V DC (logic high); ±1V DC (logic low).

• Outputs can switch both DC voltages (±60V DC maximum) and AC voltages (30V RMS

maximum) with a maximum load current of 350mA. An output relay is turned on (closed)

when the corresponding control input is placed at a logic high.

NOTE DC control inputs require approximately 80µA at 2.5V input and

approximately 3.5mA at 60V input.

Figure 3-4

Typical KPCI-PIO32IOA and KPCI-PDISO8A input/output connections

Vec (Source)

External

Source

Ground

Optional

Switch

Control

Inputs

IPnA*

Board

IPnB*

*n = Channel Number

KPCI

OPnA*

LOAD

(Motor, Relay, etc.)

OPnB*

Switching

Outputs

Page 30

3-14 Installation KPCI-PIO32IOA and KPCI-PDISO8A User’s Manual

Using +5VDC from the computer power supply

CAUTION Do not connect the +5V DC outputs to an external +5VDC supply.

Doing so may damage the external supply, the board, and the

computer.

The +5V DC output and ground connections are fuse protected and

intended for convenient use in external circuits. This voltage is supplied from the PC bus and is not isolated from the user PC. If isolation is required, do not use this supply to power external circuits, or

use some external means of isolating this supply.

Do not draw more than 1A, total. Drawing excessive current may

damage the KPCI-PIO32IOA or KPCI-PDISO8A board and, potentially, the computer.

The board extends fuse-protected power from the +5V DC computer supply to the I/O connector(s). This power is convenient for use in light external circuits, such as pull-up resistors. If you

ensure that the conditions in the above CAUTION notice are maintained, this power may also

be used to energize external accessories, provided that your computer’s power supply is capable

of delivering the desired current.

I/O considerations

De-bouncing inputs using the low-pass filter

The optional on-card low-pass filter can be used to de-bounce the inputs. A low pass filter for a

given channel can be enabled by installing the appropriate jumper at J100 or J200. See

Figure 3-1 or Figure 3-2 for jumper locations, and the specifications in Appendix A for details

on filter characteristics. Note that use of the low-pass filter is recommended for AC sensing.

Power dissipation limitations

Because of variations in solid-state relay on resistance (3.5Ω typical to 4Ω maximum), the

actual maximum current may be reduced from the stated 350mA maximum by the maximum

power dissipation limit of 430mW. Current for a given on resistance can be calculated as

follows:

Where: I = current in amps

For example, with an on resistance of 4Ω, the maximum current is reduced to 328mA as follows:

I

P = power in watts (430mW maximum)

R = resistance in ohms

I

P

---=

R

0.43

----------=

4

Frequency response limitations

Because optically coupled relays are used for switching, AC signals with higher frequencies may

be significantly attenuated when passing through the board. For that reason, it is recommended

that you use a different board that contains suitable relays if AC performance at higher frequencies is important.

Page 31

KPCI-PIO32IOA and KPCI-PDISO8A User’s Manual Installation 3-15

Combining output channels

In some applications, it may be desired to attempt parallel operation of multiple output channels

to provide a load current that is higher than specified for one individual output channel. With

some care and a good understanding of the limitations, this method can be used successfully

with the KPCI board output channels.

Whenever KPCI channels are operated in parallel, due consideration should be given to each

channel to ensure that each channel will remain operating within specified limits. Some items to

consider while attempting this mode of operation are: KPCI PCB layout, dynamic and steadystate current unbalance, and temperature unbalances pertaining to the final circuit or system

configuration. The KPCI PCB layout has been designed to minimize stray passive and reactive

components where possible within each channel to the connector. These stray components are

generally not dominant when low-frequency operation of the isolated output channels is used.

General guidelines

• Voltage equity of the channels is assured by the parallel configuration. However, under tran-

sient conditions, voltage differentials can appear across devices due to di/dt effects in

unequal stray inductances. Strive to reduce stray inductance to values that give acceptable

overshoots at the maximum operating current.

• Cables should be reasonably matched for a given connector group of channels. Try to avoid

using significantly different cable lengths when paralleling channels that span cable connector groups.

• The power source that is to be switched should be as “stiff” as possible. For example, a volt-

age source should have very low output impedance.

• While software writes to the output channels will actuate each channel at nearly the same

time, do not assume that the output channels themselves will traverse their high-to-low

impedance characteristics at the same rates.

Steady-state current sharing

During the periods of time outside of the switching transitions, the current in a parallel group of

output MOSFET channels will distribute itself in the individual devices in inverse proportion to

their ON resistance. The channel with the lowest ON resistance will carry the highest current.

This will, to an extent, be self-compensating because the power loss in this channel will be the

highest. It will run the hottest, and the increase in ON resistance due to heating will be more than

that of the other channels, which will tend to equalize the current.

Precautions

Once the system is wired for use in an application, it is prudent to examine the switching behavior of the paralleled channels in an offline test. This will ensure that, for the particular application, there will be no unnecessary stresses to the system with the paralleled configuration. There

is no straightforward method for determining whether or not channel combining can be used

successfully in a particular application. The decision should be based on how well the system

channels can be matched, and how they are used with the particular sources and loads.

Channel combining cannot entirely avoid mismatches and during switching, transients and

stresses are placed on the KPCI output channels. Though these stresses may be minimized, they

may affect long-term reliability of the channels when high duty cycle operation is desired with

combined channels.

Page 32

4

External Interrupts

Page 33

4-2 External Interrupts KPCI-PIO32IOA and KPCI-PDISO8A User’s Manual

Using DriverLINX, you can program the driver to read or write data every time the board detects

the rising edge or the falling edge of an external interrupt signal. Section 4 explains external

interrupt signal connections and summarizes interrupt usage for the KPCI-PIO32IOA and

KPCI-PDISO8A boards. For more information, refer to Using DriverLINX with Your

Hardware-Keithley and other DriverLINX manuals.

External interrupt description

Through DriverLINX, you can alternatively configure two of the input lines for the following

external interrupt functions:

• INT_ENN (external interrupt enable, active low)

• INT_REQ (external interrupt request, edge triggered)

Interrupt pins

The interrupt pins on the I/O connector of the KPCI-PIO32IOA and KPCI-PDISO8A boards,

and the corresponding screw terminal on the STP-36 screw terminal accessory, are identified in

Table 4-1.

Table 4-1

Connector pins used for external interrupt function

Connector pins that are configurable for either

Interrupt Function

Signal

Designator

External interrupt enable INT_ENN 3, 21 3, 21 IP7

External interrupt request INT_REQ 4, 22 4, 22 IP6

Through DriverLINX, you can independently configure the input port so that an external interrupt request pulse causes the data at the input ports to be placed into a buffer.

Through DriverLINX, you can also configure interrupts to be edge-clocked for either of the following conditions:

• The rising (positive) edge of the external interrupt request signal

• The falling (negative) edge of the external interrupt request signal

NOTE Positive-edge clocking and no latching are the defaults upon power-up

or reset.

interrupt or general-purpose functions

KPCI-PIO32IOA and

KPCI-PDISO8A I/O

Connector, J101

Screw Terminal

STP-36

Corresponding

General-Purpose

FunctionDescription

Page 34

KPCI-PIO32IOA and KPCI-PDISO8A User’s Manual External Interrupts 4-3

Data latching

Latching external data is accomplished by first setting up the control register to latch on either a

rising or falling edge. Once the appropriate external edge is received on the INT_REQ line, the

current data value will be latched. The receipt of this external edge will also set the interrupt

pending bit. An actual PCI interrupt will only occur at this time if the interrupts are enabled.

This value will continue to be latched until the control register is written with a non-latching

value. This effectively turns off the latching mode. Input data will not latch regardless of any

INT_REQ edges. This state is the default power up state of the KPCI boards.

If the currently latched value was not acknowledged when the next external edge arrives, new

data will be latched. See the specifications for the register maps containing the locations of the

latch control register and interrupt enable and pending bits.

When data is currently latched, IP6 and IP7 will not be latched. These pins function as

INT_REQ and INT_ENN

In order to synchronize external data with hardware events represented on the INT_REQ data

line, it is recommended that an interrupt driven programming scheme be used.

in addition to digital input lines.

External interrupt application

Typically, you would use an external interrupt to ensure that the application program processes,

at a specific time, specific data that are present at one or more ports. You can do so with a board

external interrupt, subject to the following limitations:

• A KPCI-PIO32IOA and KPCI-PDISO8A external interrupt signal signals the driver to

transfer data from whichever port is desired: one, several at once, or several with one per

interrupt. The board provides no way to assign interrupts or intrinsically detect the interrupt

status for a specific bit. (However, you could potentially hardware-set and software-detect

certain I/O bits to tell a custom application program which ports to process for a given

interrupt, or you could compare the current and previous data sets, and then process only

changed data.)

• Conversely, if processing needs and interrupts occur too frequently, data that does need to be

processed can be missed. External interrupt signals are ignored during an interrupt service

routine (ISR) while an interrupt-pending bit is set high—except that the first interrupt miss,

only, does set an interrupt-missed bit.

Therefore, you must 1) know how fast your host computer and application software can process

data, and 2) space important data and interrupts accordingly. Of course, this requirement is not

specific to the KPCI-PIO32IOA and KPCI-PDISO8A boards. It applies to any data acquisition

board. See the specifications in Appendix A for hardware input response times.

You must also ensure, at the end of interrupt-initiated processing, that the application program

resets the interrupt-pending bit, the interrupt-missed bit, and two other bits that recorded

whether the interrupt occurred on the rising or falling edge of the interrupt request signal.

DriverLINX handles this process automatically.

Page 35

4-4 External Interrupts KPCI-PIO32IOA and KPCI-PDISO8A User’s Manual

Refer to Table 4-2 for a list of external-interrupt responses.

For an additional application illustration, refer to the “Interrupt example scenario” subsection in

Appendix B. For information on setting and configuration of external interrupts, refer to your

DriverLINX software manuals.

NOTE Do not confuse the external interrupt INT_REQ with the internal PCI

bus interrupt INTA, even though INT_REQ and INTA are linked by

hardware.

Table 4-2

External-interrupt responses

Result

Interrupt Control/Status

Register

Interrupt Control Bits

(x = don’t care)

INT Enable

Bit 12

Polarity

Bit 6 Bit 6 Bit 5

Port Group

Control Register

(x = don’t care)

External Inputs at

J101

Enable

Pins

3.21

Edge

Pins

4,22

Interrupt Control/

Status Register

Status after Edge

Transition*

Pending Bit

Bit 17

PCI-INT; No Latch 1 0 x 0 0 ↑ 1

PCI-INT; No Latch 1 1 x 0 0 ↓ 1

No PCI-INT; No Latch

0 x x00↑ or ↓ 0

(Programmed I/O Mode)

No PCI-INT; Latch Input

0 x 010↑ 1

Data

No PCI-INT; No Latch 0 x 0 1 0 ↓ 0

No PCI-INT; No Latch 0 x 1 1 0 ↑ 0

No PCI-INT; Latch Input

0 x 110↓ 1

Data

No PCI-INT; No Latch

x x xx1↑ or ↓ 0

(Programmed I/O Mode)

PCI-INT; Latch Input Data 1 0 0 1 0 ↑ 1

No PCI-INT; Latch Input

1 1 010↑ 1

Data

No PCI-INT; No Latch 1 0 0 1 0 ↓ 0

PCI-INT; No Latch 1 1 0 1 0 ↓ 1

PCI-INT; No Latch 1 0 1 1 0 ↑ 1

No PCI-INT; No Latch 1 1 1 1 0 ↑ 0

No PCI-INT; Latch Input

1 0 110↓ 1

Data

PCI-INT; Latch Input Data 1 1 1 1 0 ↓ 1

*For bit 17, assume an initial clear state before edge.

Page 36

5

Troubleshooting

Page 37

5-2 Troubleshooting KPCI-PIO32IOA and KPCI-PDISO8A User’s Manual

If your KPCI-PIO32IOA or KPCI-PDISO8A board is not operating properly, use the information in this section to isolate the problem before calling Keithley Applications Engineering. If

you then need to contact an applications engineer, refer to “Technical support.”

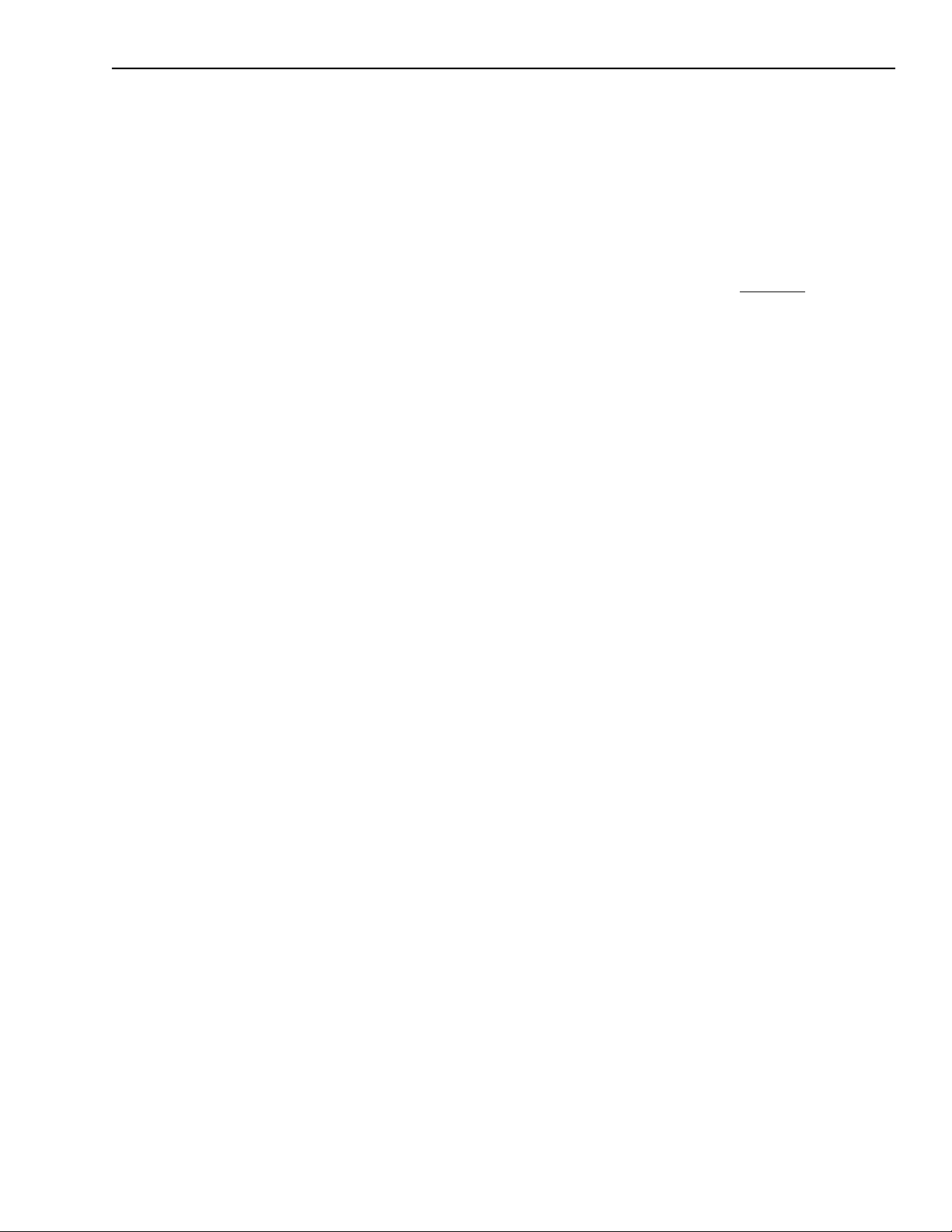

Identifying symptoms and possible causes

First try to isolate the problem using Table 5-1, which lists general symptoms and possible solu-

tions for KPCI-PIO32IOA or KPCI-PDISO8A board problems.

Table 5-1

Basic troubleshooting information

Symptom Possible Cause Possible Cause Validation/Solution

Computer does not

boot when board is

installed.

Resource conflict. KPCI-PIO32IOA or

KPCI-PDISO8A board is conflicting

with other boards in the system.

Board not seated properly. Check the installation of the board.

The power supply of the host computer

is too small to handle all the system

resources.

Board does not

respond to the AIO

DriverLINX is not installed properly

or is not configured properly.

Panel.

The board is incorrectly aligned in the

expansion slot.

The board is damaged. Contact Keithley Applications Engineering.

Data appears to be

invalid.

An open connection exists. Check screw terminal wiring.

Transducer is not connected to channel

being read.

One or more external circuits are not

compatible.

+5V power is not

available at I/0

connector.

Intermittent

operation.

External circuit digital output and

power loads exceed current capacity of

the board, tripping self-resetting fuses.

Vibrations or loose connections exist. Cushion source of vibration and tighten connections.