Kawasaki LSI KL5KUSB240 Datasheet

Kawasaki LSI • 2570 North First Street • Suite 301 • San Jose, CA 95131 • Tel: (408) 570-0555 • Fax: (408) 570-0567

•

www.klsi.com

KL5KUSB240

1

Ver. 1.2

USB2.0 to PCI BUS

General Description

The Kawasaki KL5KUS B240 is a h igh perform ance device th at transfers data betwee n the U SB2.0 highspeed BUS and the PCI 33MHz, 32 bit BUS. T his de vice e asil y interf aces with o ur USB 2 .0 tra nsceiv ers,

the KL5KUSB200 and KL5KUSB2 01. The KL5KUSB240 is an ideal so lution to conv ert a PCI device t o a

USB2.0 interface with its HS_SIE USB2. 0 Transceiver interface, 4 sets of hi gh-speed bulk packet size

buffers, PCI interface and PCI master 2DMA channel support.

Features

• 33MHz PCI interface

• 30MHz USB 2.0 SIE BUS for High-Speed SIE

operation

• Double packet buffer - 512x2 HS, 64Bx2 FS

• Internal DMA operation between the High- Sp ee d

SIE and Double Buffer

• Interfaces with USB 2.0 PHY

• High-Speed chirp protocol

• High-Speed/Full-Speed compatibility

• USB basic operation and transaction

control

• Up to 5 endpoints

• PCI interface for Target and Master (2

DMA) modes

• Page and Descriptor DMA Modes

• USB data access by PCI target or DMA

• 0.35u Std cell technology

• V

dd

= 3.3V, Ta = 0~70°C

• 144 pin LQFP package (20 mm

2

)

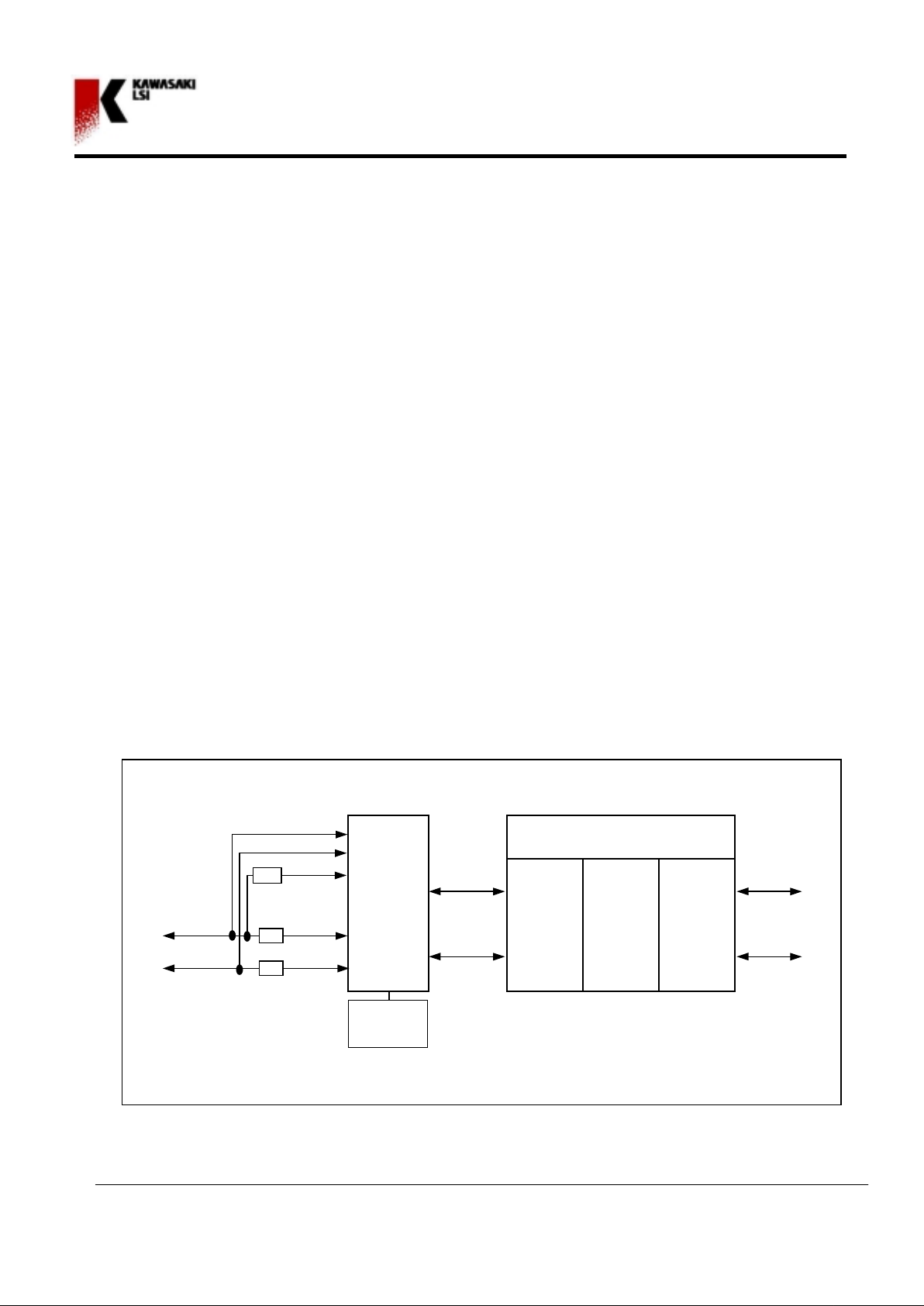

Block Diagram

HS D+

HS D-

SIE 16 b

USB 2.0 D-

USB 2.0 D+

KL5KUSB

200/201

RPU_EN

Rpu

Rs

Rs

HS_SIE DBUF PCI IF

KL5KUSB240

30 MHz

PCI 32 b

33 MHz

Clock

Generator

Kawasaki LSI • 2570 North First Street • Suite 301 • San Jose, CA 95131 • Tel: (408) 570-0555 • Fax: (408) 570-0567

•

www.klsi.com

KL5KUSB240

2

Ver. 1.2

USB2.0 to PCI BUS

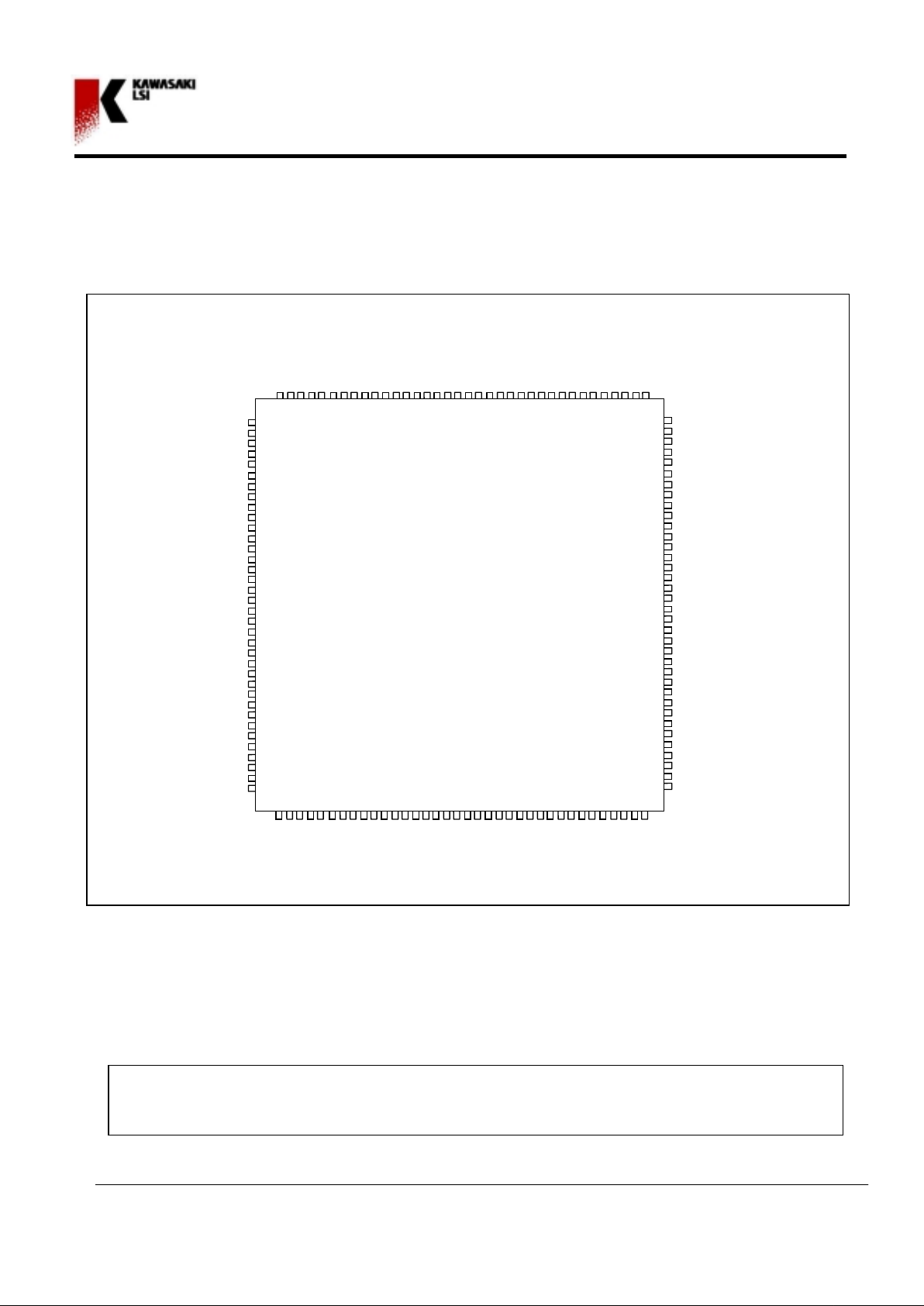

Pin Diagram 144LQFP

October 2001 • Copyright 2001 • Kawasaki LSI • Printed in U.S.A

Kawasaki LSI assumes no responsibility or liability for (1) any errors or inaccuracies contained in the information herein and (2) the use of the

information or a portion thereof in any application, including any claim for (a) copyright or patent infringement or (b) direct, indirect, special or

consequential damages. There are no warranties extended or granted by this document. The information herein is subject to change without notice

form Kawasaki LSI

GND

VDD

AD[28]

AD[27]

GND

AD[26]

AD[25]

AD[24]

VDD

GND

GND

VDD

CBEN[3]

IDSEL

AD[23]

GND

GND

AD[22]

AD[21]

AD[20]

GND

VDD

AD[19]

AD[18]

GND

GND

VDD

AD[17]

AD[16]

CBEN[2]

GND

VDD

FRAMEN

IRDYN

GND

TRDYN

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

DEVSELN

STOPN

GND

VDD

PAR

CBEN[1]

GND

AD[15]

AD[14]

AD[13]

GND

VDD

AD[12]

AD[11]

GND

GND

GND

VDD

AD[10]

AD[9]

AD[8]

GND

VDD

CBEN[0]

AD[7]

GND

AD[6]

AD[5]

AD[4]

GND

VDD

AD[3]

AD[2]

GND

AD[1]

AD[0]

3738394041424344454647484950515253545556575859606162636465666768697071

72

GND

SIE_DAT[3]

SIE_DAT[4]

VDD

SIE_DAT[5]

SIE_DAT[6]

SIE_DAT[7]

VDD

GND

GND

SIE_DAT[8]

SIE_DAT[9]

VDD

SIE_DAT[10]

SIE_DAT[11]

GND

SIE_DAT[12]

SIE_DAT[13]

SIE_DAT[14]

CKOUT

SIE_DAT[15]

GND

PU_SE0N

FS_HSN

CRCACT

TXACT

WDVLD

VDD

GND

TXRDY

RXERR

CRCERR

RXVLD

RXACT

VDD

GND

108

107

106

105

104

103

102

101

100

99

98

97

96

95

94

93

92

91

90

89

88

87

86

85

84

83

82

81

80

79

78

77

76

75

74

73

AD[29]

AD[30]

AD[31]

GND

REQN

GNTN

CLK

RSTN

INTAN

VDD

VDD

GND

TESTO

TESTI[0]

TESTI[1]

TESTI[2]

TESTI[3]

VBDET

GND

GND

P_MODE[0]

P_MODE[1]

P_MODE[2]

MODE[0]

MODE[1]

MODE[2]

MODE[3]

URSTN

VDD

VDD

SUSPN

BSTAT[0]

BSTAT[1]

SIE_DAT[0]

SIE_DAT[1]

SIE_DAT[2]

144

143

142

141

140

139

138

137

136

135

134

133

132

131

130

129

128

127

126

125

124

123

122

121

120

119

118

117

116

115

114

113

112

111

110

109

KL5KUSB240

Loading...

Loading...