JRC NJU6635CH Datasheet

NJU6635

16-CHARACTER 2-LINE DOT MATRIX LCD

GENERAL DESCRIPTION

■

NJU6635

The

driver for up to 16-character 2-line display with double

height function.

It contains microprocessor Interface circuits,

Instruction decoder controller, character generator

ROM/RAM and common and segment drivers.

The bleeder resistance generates for LCD Bias

voltage Internally.

The CR oscillator Inc orporates C and R, ther efore no

external components for oscillation are required.

The microprocessor Interface circuits which operate

2MHz frequency, can be connected directly to 4/8bit

microprocessor.

The character generator consists of 9,600 bits ROM

and 32 x 5 bits RAM. The standard version ROM is

coded with 240 characters including capital and small

letter fonts.

The 16-common and 80-segment drive up to

16-character 2-line LCD panel which divided two

common electrode blocks.

The rectangle outlook is very applicable to COG.

FEATURES

■

is a 1Chip Dot Matrix LCD controller

PRELIMINARY

CONTROLLER DRIVER

PACKAGE OUTLINE

■

NJU6635CH

●

16-character 2-line Dot Matrix LCD Controller Driver

●

4/8 Bit Microprocessor direct Interface

●

Display Data RAM :32 x 8 bits : Maximum 16-character 2line Display

●

Character Generator ROM :9,600 bits ; 240 characters for 5 x 8 dots

●

Character Generator RAM :32 x 5 bits ; 4 Patterns( 5 x 8 dots)

●

Microprocessor direst accessing to Display Data RAM and Character Generator RAM

●

High Voltage LCD Driver :16-common / 80-segment

●

Duty Ratio :1/16 Duty

●

Maximum Display Characters ; 32 Characters

●

Useful Instruction Set

Clear Display, Returns Home, Display ON/OFF Cont, Cursor ON/OFF Cont, Display Blink, Cursor Shift,

Character Shift, Double Height Function.

●

Power On Reset / Hardware Reset Function

●

Oscillation Circuit on chip

●

Bleeder Resistance on chip

●

Low Power Consumption

●

Operating Voltage --- +5V

●

Package Outline --- Bumped Chip

●

C-MOS Technology

00/01/15

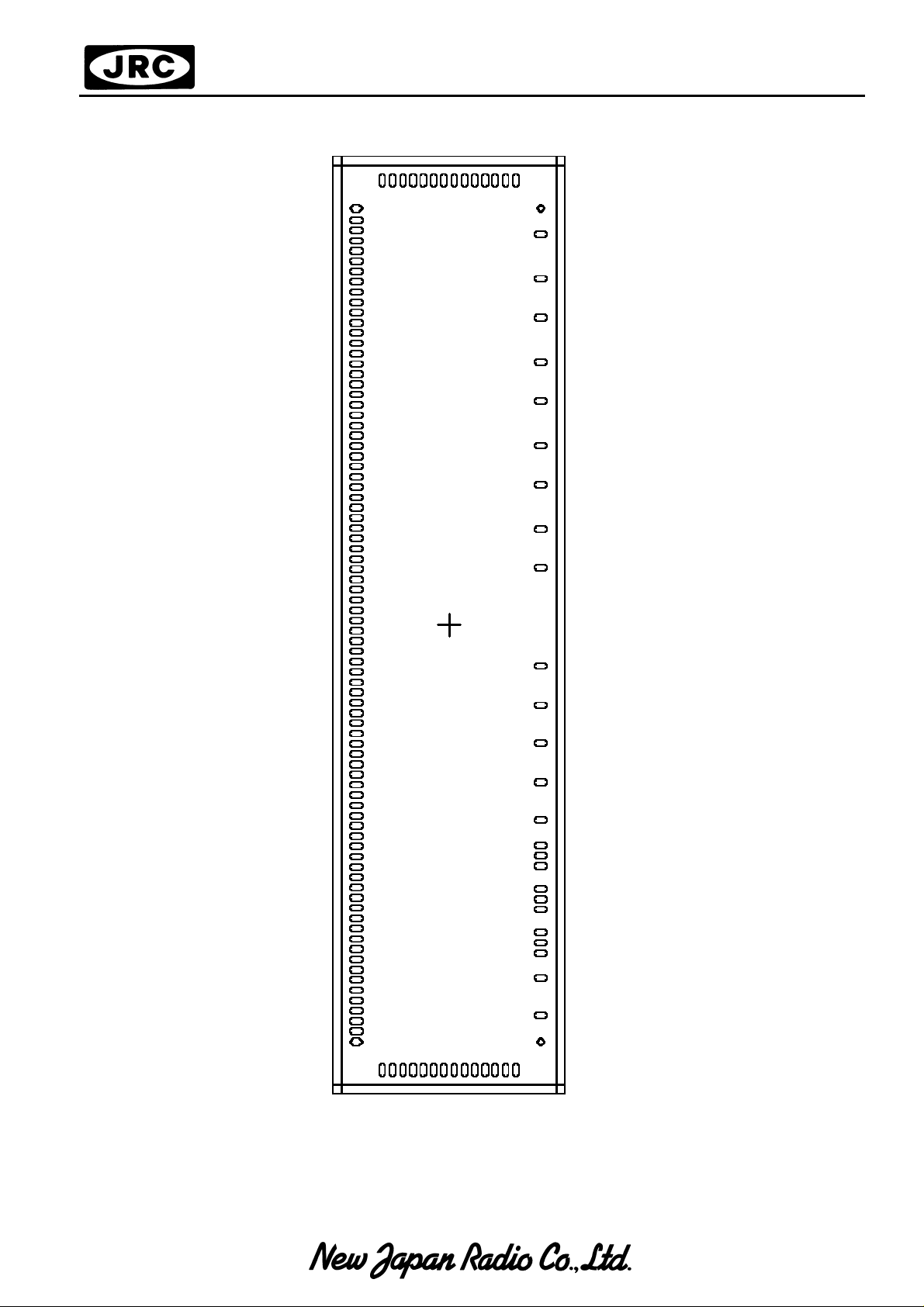

PAD LOCATION

■

CHIP SIZE :5.49 x 1.37mm BUMP SIZE :45 x 83µm

CHIP CENTER :X=0µm, Y=0µm BUMP HEIGHT :17.5µm Typ.

BUMP MATERIAL :Au

1

NJU6635

NJU6635

PAD COORDINATES

■

PAD No.

1 DMY_1 DMY_1 -2435 -534 70 SEG28 SEG53 750 541

2 OSC1 OSC1 -2282 -534 71 SEG29 SEG52 690 541

3 OSC2 OSC2 -2061 -534 72 SEG30 SEG51 630 541

4 VSS V

5 VSS V

6 VSS V

7 VDD V

8 VDD V

9 VDD V

10 V5 V

11 V5 V

12 V5 V

13 V3 V

14 V2 V

15 RESET RESET -689 -534 84 SEG42 SEG39 -90 541

16 RS RS -468 -534 85 SEG43 SEG38 -150 541

17 RW RW -239 -534 86 SEG44 SEG37 -210 541

18 E E 336 -534 87 SEG45 SEG36 -270 541

19 DB0 DB0 561 -534 88 SEG46 SEG35 -330 541

20 DB1 DB1 820 -534 89 SEG47 SEG34 -390 541

21 DB2 DB2 1049 -534 90 SEG48 SEG33 -450 541

22 DB3 DB3 1308 -534 91 SEG49 SEG32 -510 541

23 DB4 DB4 1537 -534 92 SEG50 SEG31 -570 541

24 DB5 DB5 1797 -534 93 SEG51 SEG30 -630 541

25 DB6 DB6 2025 -534 94 SEG52 SEG29 -690 541

26 DB7 DB7 2285 -534 95 SEG53 SEG28 -750 541

27 DMY_2 DMY_2 2435 -534 96 SEG54 SEG27 -810 541

28 DMY_3 DMY_3 2600 -390 97 SEG55 SEG26 -870 541

29 DMY_4 DMY_4 2600 -330 98 SEG56 SEG25 -930 541

30 DMY_5 DMY_5 2600 -270 99 SEG57 SEG24 -990 541

31 DMY_6 DMY_6 2600 -210 100 SEG58 SEG23 -1050 541

32 COM1 COM9 2600 -150 101 SEG59 SEG22 -1110 541

33 COM2 COM10 2600 -90 102 SEG60 SEG21 -1170 541

34 COM3 COM11 2600 -30 103 SEG61 SEG20 -1230 541

35 COM4 COM12 2600 30 104 SEG62 SEG19 -1290 541

36 COM5 COM13 2600 90 105 SEG63 SEG18 -1350 541

37 COM6 COM14 2600 150 106 SEG64 SEG17 -1410 541

38 COM7 COM15 2600 210 107 SEG65 SEG16 -1470 541

39 COM8 COM16 2600 270 108 SEG66 SEG15 -1530 541

40 DMY_7 DMY_7 2600 330 109 SEG67 SEG14 -1590 541

41 DMY_8 DMY_8 2600 390 110 SEG68 SEG13 -1650 541

42 DMY_9 DMY_9 2435 541 111 SEG69 SEG12 -1710 541

43 SEG1 SEG80 2370 541 112 SEG70 SEG11 -1770 541

44 SEG2 SEG79 2310 541 113 SEG71 SEG10 -1830 541

45 SEG3 SEG78 2250 541 114 SEG72 SEG9 -1890 541

46 SEG4 SEG77 2190 541 115 SEG73 SEG8 -1950 541

47 SEG5 SEG76 2130 541 116 SEG74 SEG7 -2010 541

48 SEG6 SEG75 2070 541 117 SEG75 SEG6 -2070 541

49 SEG7 SEG74 2010 541 118 SEG76 SEG5 -2130 541

50 SEG8 SEG73 1950 541 119 SEG77 SEG4 -2190 541

51 SEG9 SEG72 1890 541 120 SEG78 SEG3 -2250 541

52 SEG10 SEG71 1830 541 121 SEG79 SEG2 -2310 541

53 SEG11 SEG70 1770 541 122 SEG80 SEG1 -2370 541

54 SEG12 SEG69 1710 541 123 DMY_10 DMY_10 -2435 541

55 SEG13 SEG68 1650 541 124 DMY_11 DMY_11 -2600 390

56 SEG14 SEG67 1590 541 125 DMY_12 DMY_12 -2600 330

57 SEG15 SEG66 1530 541 126 COM16 COM8 -2600 270

58 SEG16 SEG65 1470 541 127 COM15 COM7 -2600 210

59 SEG17 SEG64 1410 541 128 COM14 COM6 -2600 150

60 SEG18 SEG63 1350 541 129 COM13 COM5 -2600 90

61 SEG19 SEG62 1290 541 130 COM12 COM4 -2600 30

62 SEG20 SEG61 1230 541 131 COM11 COM3 -2600 -30

63 SEG21 SEG60 1170 541 132 COM10 COM2 -2600 -90

64 SEG22 SEG59 1110 541 133 COM9 COM1 -2600 -150

65 SEG23 SEG58 1050 541 134 DMY_13 DMY_13 -2600 -210

66 SEG24 SEG57 990 541 135 DMY_14 DMY_14 -2600 -270

67 SEG25 SEG56 930 541 136 DMY_15 DMY_15 -2600 -330

68 SEG26 SEG55 870 541 137 DMY_16 DMY_16 -2600 -390

69 SEG27 SEG54 810 541

PAD Name

A mode B mode

Chip Size(5490µm x 1370µm)

X= um Y= um

-1916 -534 73 SEG31 SEG50 570 541

SS

-1856 -534 74 SEG32 SEG49 510 541

SS

-1796 -534 75 SEG33 SEG48 450 541

SS

-1661 -534 76 SEG34 SEG47 390 541

DD

-1601 -534 77 SEG35 SEG46 330 541

DD

-1541 -534 78 SEG36 SEG45 270 541

DD

-1407 -534 79 SEG37 SEG44 210 541

5

-1347 -534 80 SEG38 SEG43 150 541

5

-1287 -534 81 SEG39 SEG42 90 541

5

-1138 -534 82 SEG40 SEG41 30 541

3

-918 -534 83 SEG41 SEG40 -30 541

2

PAD Name

PAD No.

A mode B mode

X= um Y= um

BLOCK DIAGRAM

(ID)

register

Latch

Driver

Driver

(

)

g

(

)

■

OSC1

OSC2

CR

OSC

RS

R/W

E

DB4–

DB0–

DB

DB

4

I/O Buffer

7

4

3

VSS

V

DD

R

for LCD Driver

R

V

2

R

V3

R

R

VSS V5

NJU6635

8 7

Instruction

Decoder

Display Data RAM (DD RAM)

7

32 x 8 bits

8

5

8

8

8

DR

ister

Instruction

re

DR

Character

5

Data register

Generator

(CG RAM)

32 x 5bits

Busy

Flag

5

Parallel to serial Converter

1

V

1

1

V

2

1

V

3

1

V

4

1

Address

counter

7

8

8

Character

Generator

(CG RAM)

9,600bits

5

Timing

Generator

7

Cursor Blink Controller

80-bit

Shift resister

Power

On

RESET

16 16

16-bit Shift

Common

80 80

80-bit

Segment

80

RESET

COM1–

COM

SEG1–

SEG

80

16

TERMINAL DESCRIPTION

■

NJU6635

PAD No.

SYMBOL I/O F U N C T I O N

A mode B mode

4 – 9 4 – 9 VDD, VSS – Power Source : VDD = +5V, GND : VSS = 0V

10 – 14 10 – 14 V2, V3, V5 –

LCD driving Power Source

2 2 OSC1 I Oscillation Frequency Adjustment Terminals. Normally Open.

(Oscillation C and R are Incorporated, Osc Freq.=540kHZ)

3 3

OSC

O Oscillation Frequency Adjustment Terminals. Normally Open.

2

This terminal also operates as the clock frequency monitor.

16 16

RS

I Resister selection signal Input

"0":Instruct ion Resister (Writing)

Busy Flag (Reading)

"1":Data Register (Writing / Reading)

17 17 R/W I Read/Write selection signal Input

"0":Write "1":Read

18 18 E I Read/write activation Signal Input

26 – 23 26 – 23 DB7 – DB4 I/O 3-state Data Bus(Upper) to transfer the data between MPU and

NJU6635

DB

.

is also used for the Busy Flag reading.

7

19 – 22 19 – 22 DB3 – DB0 I/O 3-state Data Bus(Lower) to transfer the data between MPU and

NJU6635

.

In serial and 4bit parallel mode, these terminals are not used

and should be open.

32 – 39,

126 – 133

133 – 126,

39 – 32

COM1 –

COM

43 – 122 122 – 43 SEG1 –

SEG

15 15

1,

27 – 31,

40 – 42,

123 – 125,

134 – 137

1,

27 – 31,

40 – 42,

123 – 125,

134 – 137

RESET

DUMMY1

–

DUMMY

80

O LCD Common driving signal Terminals

16

O LCD segment driving signal Terminals

I Reset Terminal. When the “L” level Input over than 1.2ms to

this terminal, the system will be reset.(f

O Dummy Terminal

These terminals are electrically open.

15

=540kHz)

OSC

FUNCTIONAL DESCRIPTION

■

(1)Description for each blocks

(1-1)Register

NJU6635

The

The Register (IR) stores Instruction codes suc h as “Clear Display” and “Ret urn Home”, and addres s

data for Display Data RAM (DD RAM) an d Character Generator RAM (C G RAM). The MPU can wr ite

the Instruction code and address data to the Register (IR), but it can not read out from the Register (IR).

The Register (DR) is a tem porary storing r egister, the data in the Register ( DR) is written into the DD

RAM or CG RAM and read out from the DD RAM or CG RAM.

The data in the Regis ter (D R) writte n b y the MP U is tr ansf erred f rom the Reg ister autom atical l y to the

DD RAM or CG RAM by Internal operation.

After reading the data in th e Register (DR) b y the MPU, the next address data in the DD RAM or C G

RAM is transferred automatically to the Register (DR) for the next MPU reading.

These two registers are selected by the selection signal RS as shown below:

Table 1. Register operation control by RS and R/W signals.

RS R/W Operation

0 0 Write

0 1 Read busy flag (DB7) and address counter (DB0 to DB7)

1 0 Write (DR to DD or CG RAM)

1 1 Read (DD or CG RAM to DR)

(1-2)Busy Flag (BF)

When the internal circuits are operating, the busy flag is “1”, and any instruction reading is inhibited.

The busy flag (BF) is output from DB

The next instruction should be written after busy flag (BF) goes to “0”.

(1-3)Address Counter(AC)

The address Counter (AC) addresses the DD RAM and CG RAM.

When the address setting instruction is written into the Register (IR), the address information is

transferred from Register (IR) to th e counter (AC) . The selection of either the DD RAM or CG RAM is

also determined by this instruction.

After writing (or reading) the display data to (or from) the DD RAM or CG RAM, the counter (AC)

increments (or decrements) “1” automatically.

The address data in the Co unter (AC) is outp ut from DB

in table 1.

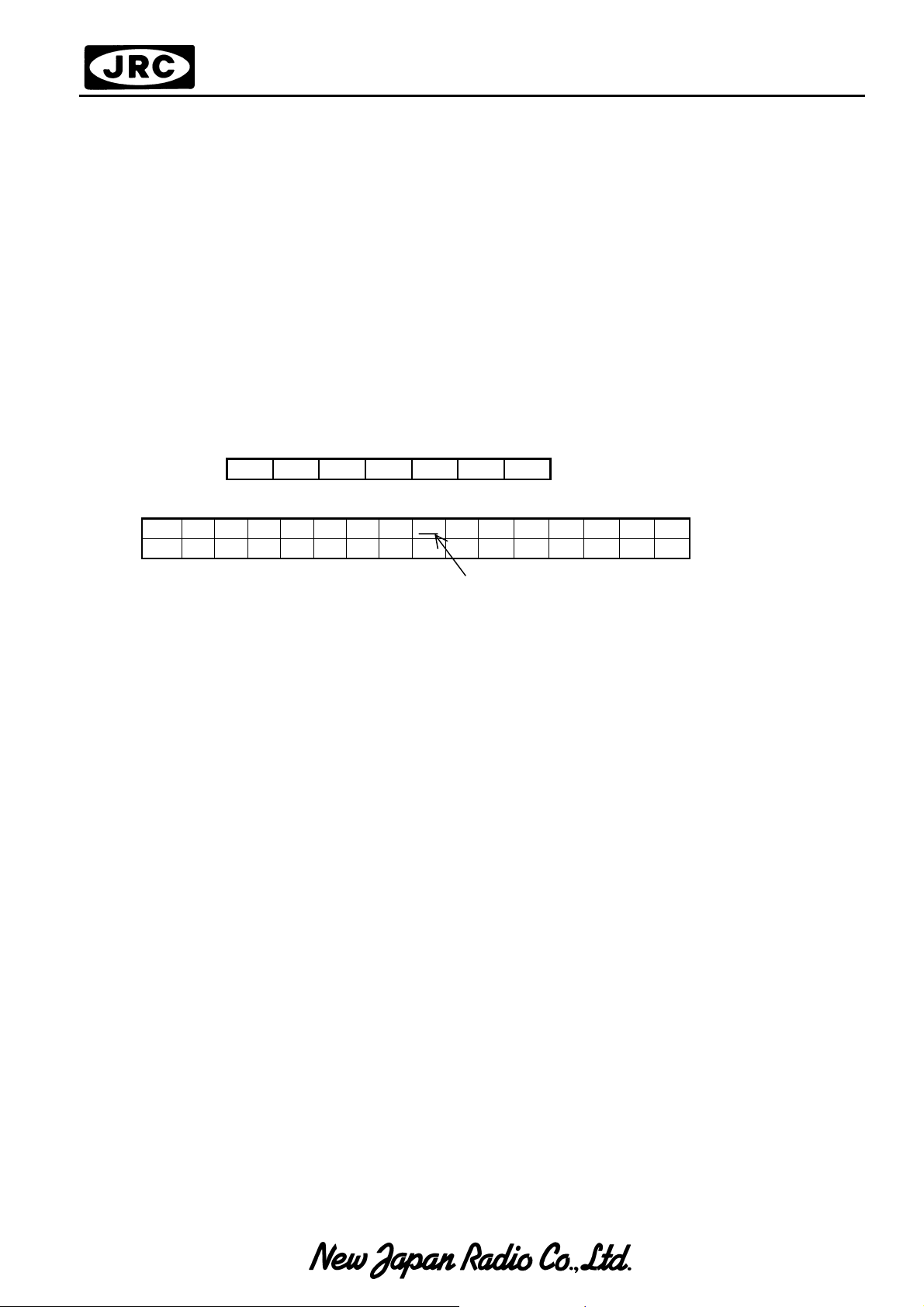

(1-4)Display Data RAM (DD RAM)

The display data RAM (DD RAM) consisting of 32 x 8 bits stores up to 32-character display data

represented in 8-bit code.

The DD RAM address data set in the address Counter (AC) is represented in hexadecimal.

←Higher order bit Lower order bit→ (Example) DD RAM address “ 08 ”

AC AC

incorporates two 8-bit registers, an Instruction Register (IR) and a Data Register (DR).

AC5 AC4 AC3 AC2 AC1 AC0 0 0 0 1 0 0 0

6

Hexadecimal

Table 1. Register Operation

when RS=”0” and R/W=”1” as shown in table 1.

7

to DB0 when RS=”0” and R/W=”1” as shown

6

Hexadecimal

0

NJU6635

8

NJU6635

(1-4-1)16-character 2-line Display

NJU6635

The

which is determined by the Function Set Instruction (A=0 and 1).

“Addressing mode 1” us es sequential address of (00)

last half 16-character. “Addressing mode 2 “ does not use sequential address lik e as (00)

and (40)H through (4F)H for front half 16-character and last half 16-character respectively.

(1F)

H

•

Addressing mode 1: A=0

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16

1st line 00 01 02 03 04 05 06 07 08 09 0A 0B 0C 0D 0E 0F

2nd line 10 11 12 13 14 15 16 17 18 19 1A 1B 1C 1D 1E 1F (Hexadecimal)

The relation between DD RAM address and display position on the LCD shown below.

[ Left Shift Display ]

(00) ←

(10) ←

01 02 03 04 05 06 07 08 09 0A 0B 0C 0D 0E 0F 10

11 12 13 14 15 16 17 18 19 1A 1B 1C 1D 1E 1F 00

[ Right Sift Display ]

1F 00 01 02 03 04 05 06 07 08 09 0A 0B 0C 0D 0E

0F 10 11 12 13 14 15 16 17 18 19 1A 1B 1C 1D 1E

•

Addressing mode 2: A=1

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16

1st line 00 01 02 03 04 05 06 07 08 09 0A 0B 0C 0D 0E 0F

2nd line 40 41 42 43 44 45 46 47 48 49 4A 4B 4C 4D 4E 4F (Hexadecimal)

The relation between DD RAM address and display position on the LCD shown below.

[ Left Shift Display ]

(00) ←

(40) ←

01 02 03 04 05 06 07 08 09 0A 0B 0C 0D 0E 0F 00

41 11 12 13 14 15 16 17 18 19 1A 1B 1C 1D 1E 1F

[ Right Sift Display ]

0F 00 01 02 03 04 05 06 07 08 09 0A 0B 0C 0D 0E

4F 40 41 42 43 44 45 46 47 48 49 4A 4B 4C 4D 4E

(1-4-2)The relation between DD RAM address and display position on the LCD shown below.

Correspondence between DD RAM Address and display position on the LCD panel.

In case of doub le height size Displa y function, the address of DD RAM which is set as fol lows the

display, operates as 16-character 1-line and the addressing mode is ignored.

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16

1st line 00 01 02 03 04 05 06 07 08 09 0A 0B 0C 0D 0E 0F

2nd line 00 01 02 03 04 05 06 07 08 09 0A 0B 0C 0D 0E 0F (Hexadecimal)

When the display shift is performed, the DD RAM address changes as follows.

[ Left Shift Display ]

(00) ←

(00) ←

01 02 03 04 05 06 07 08 09 0A 0B 0C 0D 0E 0F 00

01 02 03 04 05 06 07 08 09 0A 0B 0C 0D 0E 0F 00

[ Right Sift Display ]

0F 00 01 02 03 04 05 06 07 08 09 0A 0B 0C 0D 0E

0F 00 01 02 03 04 05 06 07 08 09 0A 0B 0C 0D 0E

has two kinds of addressing mode as “ Addressing mode 1 ” and “ Addressing mode 2 ”

through (1F)H for front half 16-character and

H

through

H

←Display Position

←DD RAM Address

→ (0F)

→ (1F)

← Display Position

← DD RAM Address

→ (0F)

→ (4F)

(Double Height Sized display Function).

← Display Position

← DD RAM Address

→ (0F)

→ (0F)

NJU6635

Lower 4 bit (Hexadecimal)

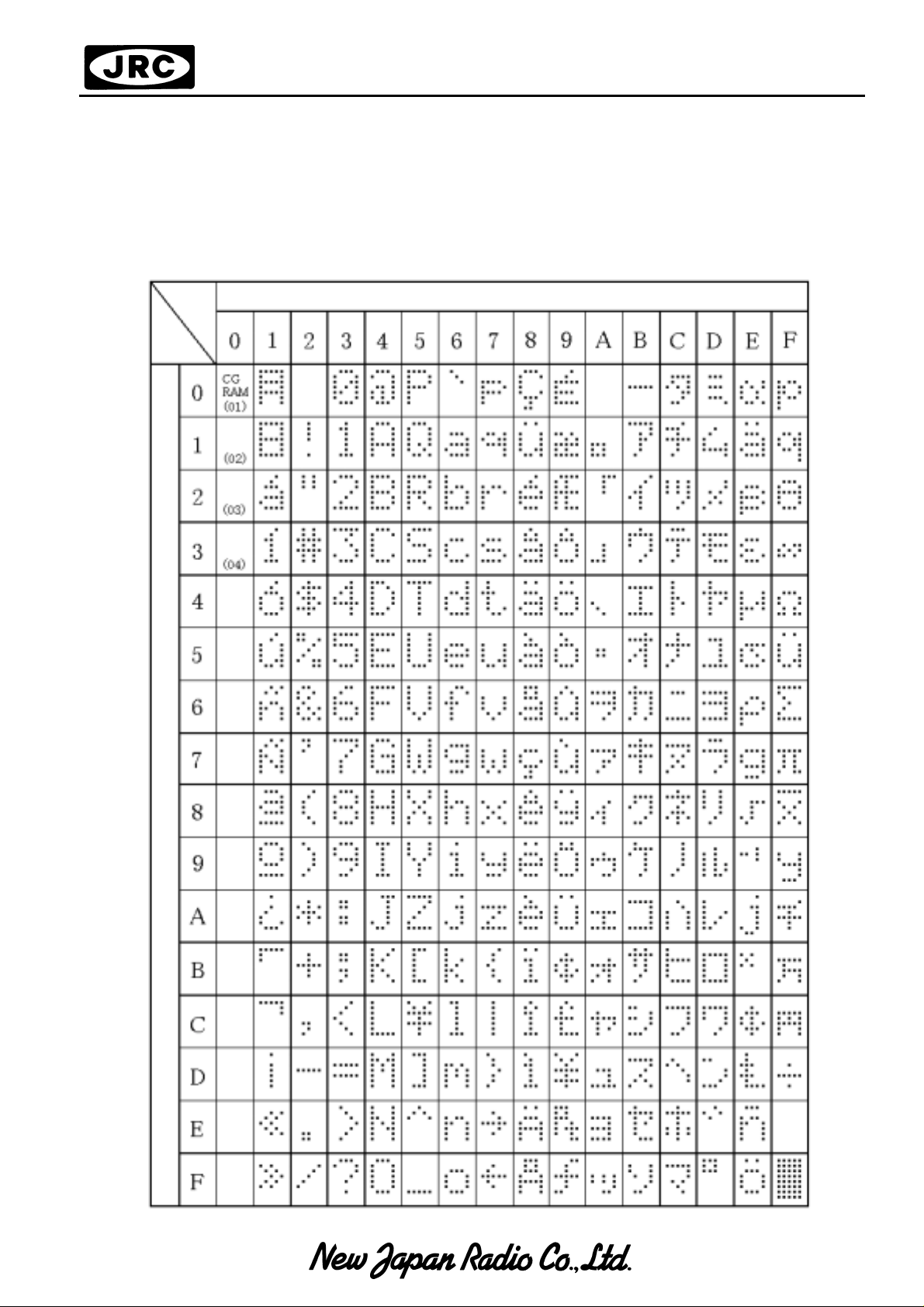

(1-5)Character Generator ROM(CG ROM)

The Character Gen erator ROM (CG ROM) g enerates 5 x 8 dots c h arac ter patt ern r epres en ted i n 8-bi t

character codes.

The storage capacity is up to 240 kinds of 5 x 8 dots character pattern. The correspondence

between character code and standard character pattern is shown in Table 2.

User-defined character pattern ( Custom Font ) are also available by mask option.

Table 2. CG ROM Character Pattern ( ROM version –02 )

Upper 4 bit (Hexadecimal)

NJU6635

(1-6)Character Generator RAM

The character gen erator RAM (CG RAM) s tor es any kinds of character pattern in 5 x 8 dots written by

the user program to dis pla y us er ’s orig inal c harac ter p attern. The CG RAM stores 4 k inds of charac ter

in 5 x 8 dots mode.

To display user’s original character pattern stored in the CG RAM, the address data (00)

should be written to the DD RAM as shown in Table 2.

Table 3. shows the correspondence among the character pattern, CG RAM address and data.

Table 3. Correspondence of CG RAM address, DD RAM character code

and CG RAM character pattern (5 x 8 dots)

Character Code

(DD RAM Data)

7 6 5 4 3 2 1 0

← →

Upper bit Lower bit

0 0 0 0 ∗ ∗ 0 0

0 0 0 0 ∗ ∗ 0 1

0 0 0

!

!

!

!

!

0 0 0 0 ∗ ∗ 1 1

Notes: 1. Character code bits 0 and 1 correspond to the CG RAM address 3 and 4 ( 2bits : 4 patterns).

2. CG RAM address 0, 1 and 2 designate a character pattern line position.

The 8th line is the cursor position and the display is performed by logical OR with cursor.

Therefore, in case of the cursor display, the data of 8th line should be “0”.

If there is “1” in the 8th line, the bit “1” is always displayed on the cursor position regardless of

cursor existence.

3. Character pattern row position cor responding to the CG RAM data bits 0 to 4 are all shown abo ve.

The bits 5 to 7 of the CG RAM do not exist.

4. CG RAM ch aracter p atterns ar e selected when ch aracter code bits 4 t o 7 are al l “0” and address ed

by character code bits 0 and 1. Theref ore the address (00)

same character pattern as shown In table 2 and Table 3.

5. ”1” for CG RAM data corresponds to display On and “0” to display Off.

CG RAM Address

4 3 2 1 0

← →

Upper bit Lower bit

0 0 0

0 0 1

0 1 0

0 1 1

00

1 0 0

1 0 1

1 1 0

1 1 1

0 0 0

0 0 1

0 1 0

0 1

!

!

!

!

!

1 1

0 1 1

1 0 0

1 0 1

1 1 0

1 1 1

0 0 1

1 0 0

1 0 1

1 1 0

1 1 1

Character

Pattern

(CG RAM Data)

4 3 2 1 0

← →

Upper Lower

bit bit

1 1 1 1 0

1 0 0 0 1

1 0 0 0 1

1 1 1 1 0

1 0 1 0 0

1 0 0 1 0

1 0 0 0 1

0 0 0 0 0

1 0 0 0 1

0 1 0 1 0

1 1 1 1 1

0 0 1 0 0

1 1 1 1 1

0 0 1 0 0

0 0 1 0 0

0 0 0 0 0

!

!

!

!

!

!

!

!

!

!

, (04)H, (08)H and (0C)H, select the

H

Character

Pattern

Example (1)

←Cursor Position

Character

Pattern

Example (2)

← Cursor Position

– (03)H

H

NJU6635

(1-7)Timing Generator

The timing generator generates a timing signals for the DD RAM, CG RAM, CG ROM and other

internal circuit operation.

RAM read timing for the display and internal operation timing for MPU access are separately

generated, so that they may not interfere with each other.

Therefore, when the d ata write to the DD R AM for exam ple, there wil l be undesirable Influence, suc h

as flickering, in areas other than the display area.

(1-8)LCD Driver

LCD driver consists of 16-common driver and 80-segment driver.

The 80 bits of charac ter pattern d ata ar e s hifted in th e s hift-r egister and la tched when the 40 bits shift

performed completely. This latched data controls display driver to output LCD driving waveform.

(1-9)Cursor Blinking Control Circuit

This circuits controls cursor On/Off and cursor position character blinks. The cursor or blinks

appears in the digit position at the DD RAM address set in the address counter(AC).

When the address counter is (08)

AC

AC 0 0 0 1 0 0 0

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16

1st line 00 01 02 03 04 05 06 07 08 09 0A 0B 0C 0D 0E 0F

2nd line 10 11 12 13 14 15 16 17 18 19 1A 1B 1C 1D 1E 1F (Hexadecimal)

Note) The cursor or blinks appears when the address counter (AC) selects the CG RAM.

But the displayed cursor and blink are meaningless.

If the AC stores the CG RAM address data, the cursor and blink are displayed in the meaningless

position.

AC5 AC4 AC3 AC2 AC1 AC0

6

, a cursor position is shown as follows:

H

Cursor Position

← Display Position

← DD RAM Address

Loading...

Loading...