NJU6475B

PRELIMINARY

12-Character 4-Line Dot Matrix Low Power

LCD Controller Driver with key Scan Function

GENERAL DESCRIPTION PACKAGE OUTLINE

The NJU6475B is a Dot Matrix LCD Controller Driver for

12-character 4-line with Icon display in single chip. It contains

voltage converter, voltage regulator, bleeder resistance, CR

oscillator, instruction decoder, character generator ROM/RAM,

high voltage operation controller/driver and key scan circuit.

The voltage converter generates (about 8V) from the

supply voltage (3V) and regulated by the regulator. The bias

level of LCD driving voltage is generated of high value bleeder

resistance and the buffer amplifier matches the

impedance. 16-step contrast control function is incorporated

for its adjustment. Therefore, simple power supply circuit and NJU6475B

easy contrast adjustment are available. The complete CR

oscillator is incorporated without external components for

oscillation circuit. The microprocessor interface circuit w hich

operates by 1MHz, can be selected serial interface.

The character generator ROM consisting of 10,080bits stores

252 kinds of character Font.

Each 160bits CG RAM and Icon display RAM can story

4 kinds of special character to display on the dot matrix

display area or 128 kinds of Icon on the display area.

FEATURES

12-Character 4-Line Dot Matrix LCD Controller Driver

•

Maximum 128-Icon Display

•

Serial CPU Interface

•

Display Data RAM - 48 x 8 Bits :Maximum 12-Character 4-Line Display

•

Character Generator ROM - 10,080 Bits:252 Characters (5 x 8 Dots)

•

Character Generator RAM - 32 x 5 Bits :4 Patterns (5 x 8 Dots)

•

Icon Display RAM - 32 x 5 Bits :Maximum 128-Icon

•

High Voltage LCD Driver : 37-Common/63-Segment

•

Duty & Bias Ratio : 1/36 duty 1/7Bias

•

Useful Instruction Set : Clear Display, Return Home, Display On/Off Control

•

Common and Segment Driver location Order Select Function (Mode-A, Mode-B)

•

Power On Reset Circuit On Chip

•

Hardware Reset

•

Voltage Regulator On Chip

•

Electrical Variable Resistance On Chip

•

32-key scan function (8 x 4 Matrix)

•

Oscillation circuit On Chip

•

Voltage Converter (Doubler,Tripler) On Chip

•

Bleeder Resistance On Chip

•

Low Oprating Current

•

Operating Voltage - 2.4V to 3.6V (Except For LCD Driving Voltage)

•

Package Outline - Bumped-Chip / TCP

•

C-MOS Technology

•

Display Blink,Cursor Shift, Character Shift

NJU6475B

PAD LOCATION

NJU6475B

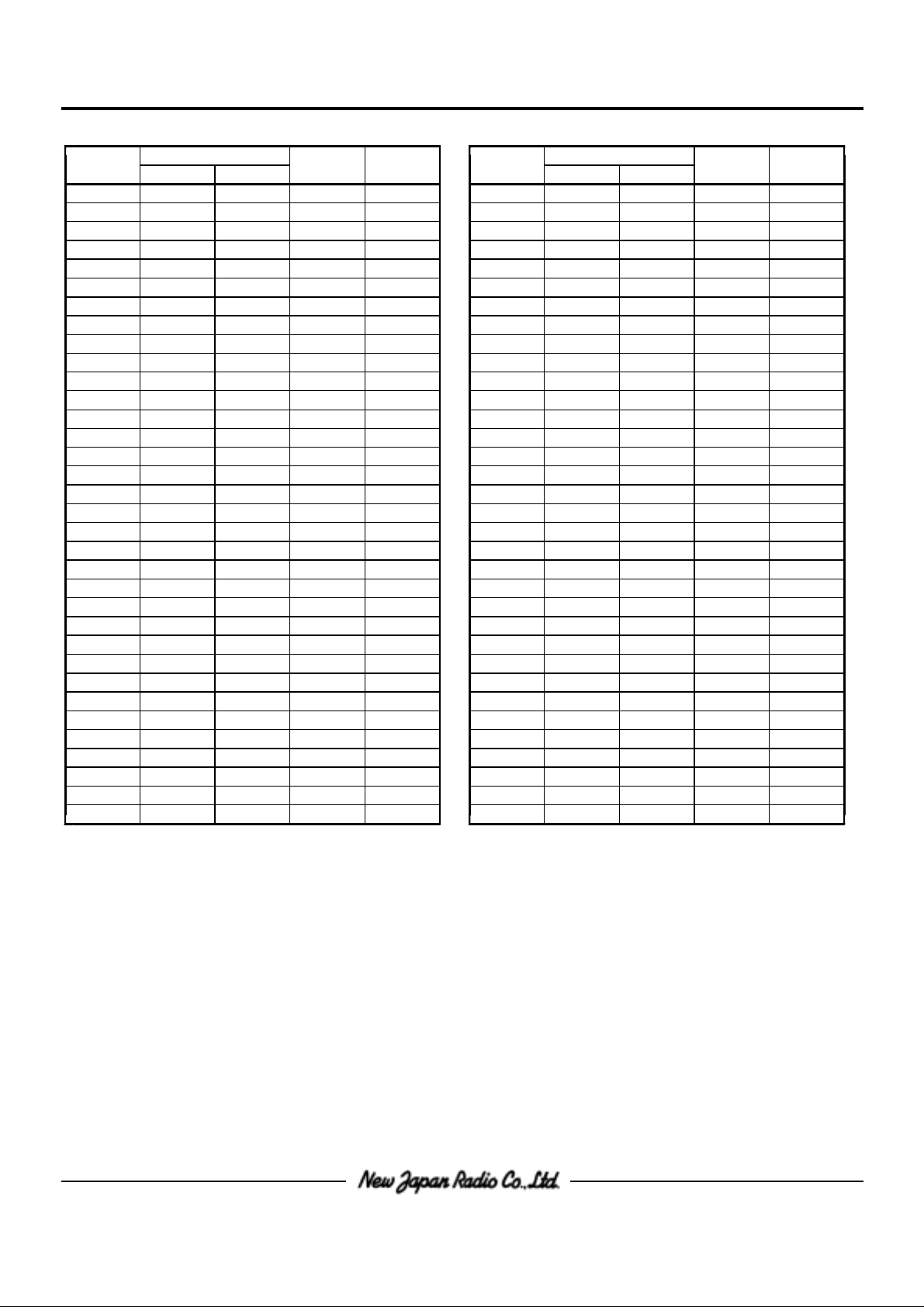

PAD COORDINATES

Chip Size 11.22×2.5mm (Chip Center X=0um,Y=0um)

PAD No. PAD No.

PAD Name PAD Name

Mode A Mode B Mode A Mode B

1 ALI-A1 ALI-A1 -6240 -1090 51 NC NC 5817 1090

2 OSC OSC -6020 -1090 52 NC NC 5617 1090

3 OSC OSC -5775 -1090 53 NC NC 5417 1090

4 V V -5479 -1090 54 NC NC 5217 1090

5 V V -4979 -1090 55 NC NC 5017 1090

6 V V -4479 -1090 56 NC NC 4817 1090

7 C2 C2 -3979 -1090 57 NC NC 4617 1090

8 C2 C2 -3479 -1090 58 NC NC 4417 1090

9 C1 C1 -2979 -1090 59 NC NC 4217 1090

10 C1 C1 -2479 -1090 60 NC NC 4017 1090

11 V V -1979 -1090 61 NC NC 3817 1090

11

22

55

SS SS

5OUT 5OUT

--

++

--

++

DD DD

12 VR VR -1479 -1090 62 NC NC 3617 1090

13 V V - 979 -1090 63 NC NC 3417 1090

REG REG

14 TEST TEST - 531 -1090 64 SEGS SEGS 3160 1090

15 SEL SEL - 302 -1090 65 COM COM 2780 1090

16 - 74 -1090 66 COM COM 2700 1090

RESET RESET

17 P/S P/S 155 -1090 67 COM COM 2620 1090

18 RS RS 383 -1090 68 COM COM 2540 1090

19 R/W R/W 612 -1090 69 COM COM 2460 1090

20 E/SCL E/SCL 840 -1090 70 COM COM 2380 1090

21 1069 -1090 71 COM COM 2300 1090

LCD/KEY LCD/KEY

22 REQ REQ 1298 -1090 72 COM COM 2220 1090

23 DB /CS DB /CS 1536 -1090 73 COM COM 2140 1090

24 1773 -1090 74 COM COM 2060 1090

25 DB DB 2010 -1090 75 COM COM 1980 1090

26 DB DB 2247 -1090 76 COM COM 1900 1090

27 DB DB 2484 -1090 77 COM COM 1820 1090

28 DB DB 2721 -1090 78 COM COM 1740 1090

29 DB DB 2958 -1090 79 COM COM 1660 1090

30 DB DB 3195 -1090 80 COM COM 1580 1090

31 K K 3466 -1090 81 SEGM SEGM 1500 1090

32 K K 3632 -1090 82 SEG SEG 1420 1090

33 K K 3903 -1090 83 SEG SEG 1340 1090

34 K K 4068 -1090 84 SEG SEG 1260 1090

35 S S 4244 -1090 85 SEG SEG 1180 1090

36 S S 4352 -1090 86 SEG SEG 1100 1090

37 S S 4460 -1090 87 SEG SEG 1020 1090

38 S S 4568 -1090 88 SEG SEG 940 1090

39 S S 4676 -1090 89 SEG SEG 860 1090

40 S S 4784 -1090 90 SEG SEG 780 1090

41 S S 4892 -1090 91 SEG SEG 700 1090

42 S S 5000 -1090 92 SEG SEG 620 1090

77 25 25

66

DB /SIO DB /SIO

55 27 27

44 28 28

33 29 29

22 30 30

11 31 31

00 32 32

00 12

11 160

22 259

33 358

00 457

11 556

22 655

33 754

44 853

55 952

66 10 51

77 11 50

43 NC NC 5217 -1090 93 SEG SEG 540 1090

44 NC NC 5417 -1090 94 SEG SEG 460 1090

45 NC NC 5617 -1090 95 SEG SEG 380 1090

46 NC NC 5817 -1090 96 SEG SEG 300 1090

47 NC NC 6017 -1090 97 SEG SEG 220 1090

48 ALI-A2 ALI-A2 6217 -1090 98 SEG SEG 140 1090

49 ALI-B2 ALI-B2 6217 1090 99 SEG SEG 60 1090

50 NC NC 6017 1090 100 SEG SEG - 20 1090

X=(um) Y=(um) X=(um) Y=(um)

11

99

10 10

11 11

12 12

13 13

14 14

15 15

16 16

26 26

12 49

13 48

14 47

15 46

16 45

17 44

18 43

19 42

NJU6475B

PAD No. PAD No.

101 SEG SEG - 100 1090 135 SEG SEG -2820 1090

102 SEG SEG - 180 1090 136 SEG SEG -2900 1090

103 SEG SEG - 260 1090 137 SEG SEG -2980 1090

104 SEG SEG - 340 1090 138 SEG SEG -3060 1090

105 SEG SEG - 420 1090 139 SEG SEG -3140 1090

106 SEG SEG - 500 1090 140 SEG SEG -3220 1090

107 SEG SEG - 580 1090 141 SEG SEG -3300 1090

108 SEG SEG - 660 1090 142 SEGM SEGM -3380 1090

109 SEG SEG - 740 1090 143 COM COM -3460 1090

110 SEG SEG - 820 1090 144 COM COM -3540 1090

111 SEG SEG - 900 1090 145 COM COM -3620 1090

112 SEG SEG - 980 1090 146 COM COM -3700 1090

113 SEG SEG -1060 1090 147 COM COM -3780 1090

114 SEG SEG -1140 1090 148 COM COM -3860 1090

115 SEG SEG -1220 1090 149 COM COM -3940 1090

116 SEG SEG -1300 1090 150 COM COM -4020 1090

117 SEG SEG -1380 1090 151 COM COM -4100 1090

118 SEG SEG -1460 1090 152 COM COM -4180 1090

119 SEG SEG -1540 1090 153 COM COM -4260 1090

120 SEG SEG -1620 1090 154 COM COM -4340 1090

121 SEG SEG -1700 1090 155 COM COM -4420 1090

122 SEG SEG -1780 1090 156 COM COM -4500 1090

123 SEG SEG -1860 1090 157 COM COM -4580 1090

124 SEG SEG -1940 1090 158 COM COM -4660 1090

125 SEG SEG -2020 1090 159 COMM COMM -4740 1090

126 SEG SEG -2100 1090 160 COMM COMM -4820 1090

127 SEG SEG -2180 1090 161 COMM COMM -4900 1090

128 SEG SEG -2260 1090 162 COMM COMM -4980 1090

129 SEG SEG -2340 1090 163 COMS COMS -5085 1090

130 SEG SEG -2420 1090 164 NC NC -5285 1090

131 SEG SEG -2500 1090 165 NC NC -5485 1090

132 SEG SEG -2580 1090 167 NC NC -5885 1090

133 SEG SEG -2660 1090 168 NC NC -6085 1090

134 SEG SEG -2740 1090 169 ALI-B2 ALI-B2 -6240 1090

PAD Name PAD Name

Mode A Mode B Mode A Mode B

20 41 54 7

21 40 55 6

22 39 56 5

23 38 57 4

24 37 58 3

25 36 59 2

26 35 60 1

27 34 21

28 33 24 24

29 32 23 23

30 31 22 22

31 30 21 21

32 29 20 20

33 28 19 19

34 27 18 18

35 26 17 17

36 25 88

37 24 77

38 23 66

39 22 55

40 21 44

41 20 33

42 19 22

43 18 11

44 17 44

45 16 33

46 15 22

47 14 11

48 13 11

49 12

50 11

51 10

52 9

53 8

X=(um) Y=(um) X=(um) Y=(um)

BLOCK DIAGRAM

NJU6475B

NJU6475B

TERMINAL DESCRIPTION

PAD No. Symbol I/O F u n c t i o n

11,5 V ,V - P ower Source : V =+3V GND : V =0V

4 V - LCD driving voltage

2,3 OSC , I/O System clock terminal

DD SS DD SS

5

1

2

OSC Oscillation C and R are incorporated. (Normally Open)

For external clock operation, the clock should be input on OSC .

17 P/S I Serial input select terminal (fixed to "L")

Register selection signal input terminal

18 RS I "0" instruction r egister. (Writing)

"1" Data register. (Writing, Reading)

19 R/W I Read(R) / Write(W) selection signal input terminal

20 E/SCL I Serial clock input terminal

23 DB /CS I Chip select signal

24 DB /SIO I/O Data input terminal (3-state data bus.)

25 - 30 DB - DB I I/O port output terminal

7

6

05

1

22 REQ O This terminal normally output "L".

When confirm a key action, REQ terminal output puls.

21 LCD/KEY I Fix to "H" Level

35 - 42 S -S O Key scan signal data output terminal

o7

Open Drain Output

31 - 34 K - K I Key scan data input terminal

03

In case of non use, fix to "H".

158 - 151 COM - COM O Common signal output terminal

132

65 - 72

150 - 143

73 - 80

162 - 159 COMM - O Icon common display signal output terminal

163 COMS O Static driving common signal output terminal

82 - 141 SEG - SEG O Segment signal output terminal

1

COMM

160

4

1

When power down mode V or V levels are output.

DD SS

81,142 SEGM ,SEGM O Icon segment driving signal output terminal

12

PAD No. Symbol I/O F u n c t i o n

NJU6475B

57 SEGS O Static driving segment signal output terminal

10,9 C1 C1 I/O Step up voltage capacitor connecting terminal

8,7 C2 ,C2

6 V O Step up voltage output terminal

13 V O Voltage regulator output terminal

1

+-

+-

5OUT

REG

When power down mode V or V level are output.

DD SS

Connect the resistor between this terminal and VR terminal.

12 VR I Reference voltage for voltage regulator input terminal

Connect the resistor between this reference voltage and

DD

V terminal.

Reset terminal

16 RESET I When the "L" level input over than 1.2ms to this terminal,

the system is reset (at f =180KHz).

osc

Common and Segment driver location order select terminal.

15 SEL I "0" Mode A location (See PAD COORDINATES)

"1" Mode B location (See PAD COORDINATES)

14 TEST I Maker test terminal

This terminal should be connected to V (or open.)

SS

43 - 47 NC - Non connection terminal

50 - 63

These terminals are electrically open.

164 - 168

169 ALI-A1 Alignment mark

49 ALI-A2 - These terminals are electrically open.

1ALI-B1

48 ALI-B2

NJU6475B

FUNCTIONAL DESCRIPTION

(1) Description for each blocks

(1-1) Register

The NJU6475B incorporates three 8-bit registers, an instruction register (IR), and a Data Register (DR), Key

Register (KR). The register (IR) stores an instruction code such as "clear display" and "cursor shift" or address

data for Display Data RAM (DD RAM), Character Generator RAM (CG RAM) and Icon Display RAM (MK RAM).

The MPU can write the instruction code and address data to the register (IR), but it cannot read out from

register (IR). The Register (DR) is a temporary register, the data stored in the Register (DR) is written into

DD RAM, MK RAM. A register from these two registers is selected by the register select signal (RS). Register

(KR) is an only temporary register for key scan data. This Register (KR) can read out the contents when

selected Key signal at "H" signal. And non relation ship with signal of register select (RS).

The Relation ship with RS, R/W register as shown below.

<Table-1> Register selection

RS R/W O p e r a t i o n

0 0 IR write & internal register operation mode

0 1 Read out (KR)

1 0 Write (DR) & internal register operation mode

1 1 Read out (KR)

(Clear Display etc...)

(DR DD RAM/CG RAM/MK RAM)

(1-2) Address Counter (AC)

The address counter (AC) addresses the DD RAM, CG RAM or MK RAM. When the address setting instruction is written into register (IR), the address information is transferred from register (IR) to the address counter

(AC). The selection of DD RAM, CG RAM or MK RAM is also determined by this instruction.

After writing (or reading) the display data to (or from) the DD RAM, CG RAM or MK RAM, the address counter

(AC) increments (or decrements) automatically.

(1-3) Display Data RAM (DD RAM)

The display data RAM (DD RAM) consisting of 48 x 8 bits stores up to 48-character display data represented

in 8-bit code.

The DD RAM address data set in the address counter (AC) is represented in Hexadecimal code.

(Example) DD RAM Address "08"

upper order bit lower order bit

ACACACACACACACAC 0 001000

6543210

hexadecimal hexadecimal 0 8

(1-3-1) The relation between DD RAM address and display position on the LCD

12-Characters 4-Line Display

-

123 4567 89101112 DisplayPosition

1stLine000102030405060708090A0B DDRAMAddress

2ndLine101112131415161718191A1B

3rdLine202122232425262728292A2B

4thLine303132333435363738393A3B

When the display shift is performed, the DD RAM address changes as follows:

[Left shift display]

(00) 01 02 03 04 05 06 07 08 09 0A 0B 00

NJU6475B

(Hexadecimal)

(10) 11 12 13 14 15 16 17 18 19 1A 1B 10

(20) 21 22 23 24 25 26 27 28 29 2A 2B 20

(30) 31 32 33 34 35 36 37 38 39 3A 3B 30

[Right shift display]

0B 00 01 02 03 04 05 06 07 08 09 0A (0B)

1B 10 11 12 13 14 15 16 17 18 19 1A (1B)

2B 20 21 22 23 24 25 26 27 28 29 2A (2B)

3B 30 31 32 33 34 35 36 37 38 39 3A (3B)

(1-4) Character Generator ROM (CG ROM)

The Character Generator ROM (CG ROM) stores 5 x 8 dots character pattern represented in 8-bit character

code. The capacity is up to 252 kinds of 5 x 8 dots character pattern.

The correspondence between character code and standard character pattern of NJU6475B is shown in table 2.

User defined character patterns (Custom Font) are also available by mask option. (in this case, the address

H

(20) are using for "Space Pattern".)

NJU6475B

<Table-2> The Correspondence Between Character Code

and Standard Character Pattern (ROM Version -02)

NJU6475B

(1-5) Character Generator RAM (CG RAM)

The Character Generator RAM stores any kinds of character pattern in 5 x 8 dots written by the user

program to display user's original character pattern. The CG RAM can store 4 kinds of character in 5 x 8 dots

mode.

To display user's original character pattern stored in the CG RAM, the address data (00) -(03) should

be written to the DD RAM as shown in Table-3.

Table-3> Correspondence of CG RAM address, DD RAM character code

<

and CG RAM character pattern (5 x 8 dots)

HH

Character Code Character Pattern

(DD RAM Data) (CG RAM Data)

76543210 76543 210 43210

Upper Lower

Bits Bits Upper Lower Upper Lower

00000000 01000 100 0 0011

00000011 01011

CG RAM Address

000 01111

11001 000

010 000 CharacterPattern11

011 0 Example(1)1111

101 00 011

11110 000

111 00000 CursorPosition

11000 000

001 0 0 011

0 1 0 Character Pattern11111

011 00 00 Example(2)1

1111100000001 01001 100

101 00 001

110 00 001

111 00000 CursorPosition

000

001

100

101

110

111

Notes : 1. Character code bit 0,1 correspond to the CG RAM address bit 3,4 (2bits ; 4patterns).

2. CG RAM address 0 to 2 designate character pattern line position. The 8th line should be "0".

If there is "1" in the 8th line, but bit "1" is always displayed on the cursor position regardless of cursor

existence.

3. Row position character pattern correspond to CG RAM data bits 0 to 4 are shown above.

4. CG RAM character patterns are selected when character code bits 2 to 7 are all "0" and these are

addressed by character code bits "0" and "1".

5. "1" for CG RAM data corresponds to display on and "0" to display off.

NJU6475B

(1-6) Icon display RAM (MK RAM)

The NJU6475B can display maximum 128 Icons.

The Icon display can be controlled by writing the data into MK RAM corresponding to the Icons.

The relation between MK RAM address and Icon display position is shown in Table-4.

Table-4> Correspondence among Icon Position, MK RAM Address and Data

<

MK RAM Address Bits for Icon Position MK RAM Address and Data

HH 76543210

(60-7F) DDDDDDDD

0110000060 ***123497

0110000161 ***567898 COMMLineand

0110010165 ***21222324102

0110011066 *******103 (COM,COM,COM,COM)

0110011167 *******104

0110100068 ***25262728105

0110100169 ***29303132106 COMMLineand

011011016D***45464748110

011011106E*******111 (COM,COM,COM,COM)

011011116F*******112

0111000070 ***49505152113

0111000171 ***53545556114 COMMLineand

0111010175 ***69707172118

0111011076 *******119 (COM,COM,COM,COM)

0111011177 *******120

0111100078 ***73747576121

0111100179 ***77787980122 COMMLineand

011111017D***93949596126

011111107E*******127 (COM,COM,COM,COM)

011111117F*******128

H

H 1

H

H 1357

H

H

H 2

H

H 9111315

H

H

H 3

H

H 17 19 21 23

H

H

H 4

H

H 25 27 29 31

H

Both besides of 1st Line

Both besides of 2nd Line

Both besides of 3rd Line

Both besides of 4th Line

Notes : 1. When the Icon display function using, the system should be initialized by the software initialization

Because the MK RAM is not initialized by the power on reset and hardware.

2. The cross-points between segments (SEGM and SEGM ) and commons (COMM to COMM and

232

COM to COM ) are always set "OFF" level.

12 14

3. In the table 4, * mark are invalid, therefore both of "0" or "1" can be written but these are no meaning.

NJU6475B

(1-7) Timing generator

The timing generator generates a timing signals for the DD RAM, CG RAM and MK RAM and other

internal circuits. RAM and timing for the display and internal operation timing for MPU access are separately

generated, so that may not interfere with each other.

Therefore, when the data write to the DD RAM for example, there will be undesirable influence, such as

flickering, in areas other than display area.

(1-8) LCD Driver

LCD Driver consists of 37-common driver and 63-segment driver. The character pattern data are latched

to the addressed segment-register respectively.

This latched data controls display driver to output LCD driving waveform.

(1-9) Cursor Blinking control circuit

This circuit controls cursor On / Off and cursor position character blinking. The cursor or blinking appear in

the digit locating at the DD RAM address set in the address counter (AC). When the address counter is (08) ,

a cursor position is shown as bellow.

6543210

AC AC AC AC AC AC AC

AC0001000

H

4-Line Display

1 2 3 4 5 6 7 8 9 10 11 12 Display position

1stLine000102030405060708090A0B DDRAMAddress

(Hexadecimal)

2nd Line 10 11 12 13 14 15 16 17 18 19 1A 1B

3rdLine202122232425262728292A2B

4thLine303132333435363738393A3B

Cursor position

Note : The cursor or blinking also appear when the address counter (AC) selects the CG RAM or the MK RAM.

But the displayed cursor and blinking are meaningless.

If the AC stores the CG or MK RAM address data, the cursor and blinking are displayed in the meaningless position.

NJU6475B

(2) Power on Initialization by internal circuits

(2-1) Internal Reset circuits Initialization

The NJU6475B is automatically initialized by internal power on initialization circuits when the power is turned

on. In the internal power on initialization, following instructions are executed.

During the Internal power on initialization, the busy flag (BF) is "1" and this status is kept during 6ms

OSC DD

(f =180KHz) after V rose to 2.4V.

Initialization sequence

Set Function PD=1 : Power down OFF

Contrast Control Set (00) to the contrast register

H

Display ON/OFF D=0 : Display OFF

Control C=0 : Cursor OFF

B=0 : Cursor Blink OFF

I/D=1 : Increment by 1

Set Mode Entry S=0 : Non shift

Clear Display

END

Note : If the condition of power supply rise time described in the Electrical Characteristics is not satisfied, the

internal Power On Initialization will not performed.

In this case, the software initialization by MPU is required.

(2-2) Hardware Initialization

The NJU6475B prepares RESET terminal to initialize the all system.

When the "L" level is input over 1.2ms to the RESET terminal, reset sequence is executed. In this time, the

busy signal is output during 6ms (f =180KHz) after RESET terminal went to "H".

OSC

-Timing Chart

External Reset

Signal

BUSY

Over 1.2ms

6ms

Loading...

Loading...