JRC NJU3555L, NJU3555FA1 Datasheet

NJU3555

4-BIT SINGLE CHIP OTP MICRO CONTROLLER

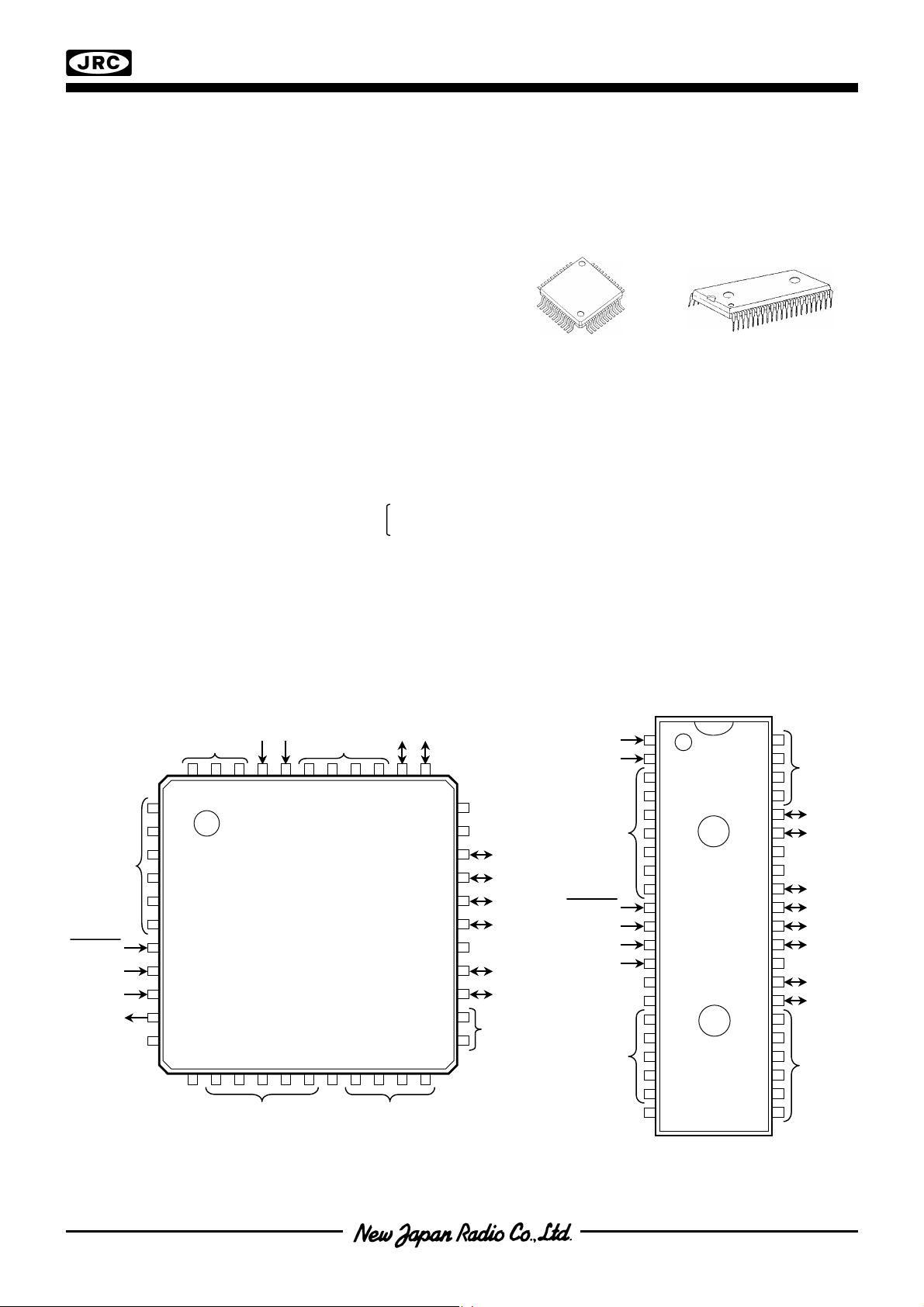

PACKAGE OUTLINE

GENERAL DESCRIPTION

■

NJU3555

The

is the C-MOS 4-bit Single Chip OT P type

Micro Controller with programmable Flash Memory.

It is completely compatible with the

and the pin configuration. Therefore, the

suitable for the final evaluation before

NJU3505

NJU3505

in function

NJU3555

mask

generation, the small quantity production and short leadtime.

* In this data sheet, only OTP programming and the

difference between NJU3555 and NJU3505 are

mentioned mainly.

Therefore the detail function and specification should

be referred on the NJU3505 data sheet.

FEATURES

■

●

Internal One Time Programmable ROM 8,192 X 8bits

8,128 X 8bits (Program area)

64 X 8bits (Option area)

●

Internal Data RAM 256 X 4bits

●

Wide operating voltage range 2.7V ~ 5.5V

●

Package outline QFP44-A1 / SDIP42 (Compatible with

●

ROM programmer “SUPERPRO/L” by XELTEK co,.

PIN CONFIGURATION IN OTP PROGRAMMING MODE

■

■

is

NJU3555FA1 NJU3555L

PRELIMINARY

NJU3505

)

Open

RESET

PROM

CLK

REQ

[ QFP44-A1 ]

D6

37

19

36

20

D7

35

21

Open

34

33

32

31

30

29

28

27

26

25

24

23

22

V

DD

Open

D5

D4

D3

D2

Open

D1

D0

Open

CNT1

44

Open

43

42

CNT2

41

40

39

Open

38

1

2

3

4

5

6

NJU3555FA1

7

8

9

10

SS

11

12

13

14

15

16

17

18

SS

V

V

DD

V

Open

Note) The pin configuration in Normal operating mode is the same as

[ SDIP42 ]

CNT1

CNT2

Open

RESET

PROM

CLK

REQ

Open

V

SS

V

SS

V

DD

NJU3505

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

42

41

40

39

38

37

36

35

34

33

32

31

30

NJU3555L

29

28

27

26

25

24

23

21 22

.

Open

D7

D6

V

DD

Open

D5

D4

D3

D2

Open

D1

D0

Open

- 1 -

NJU3555

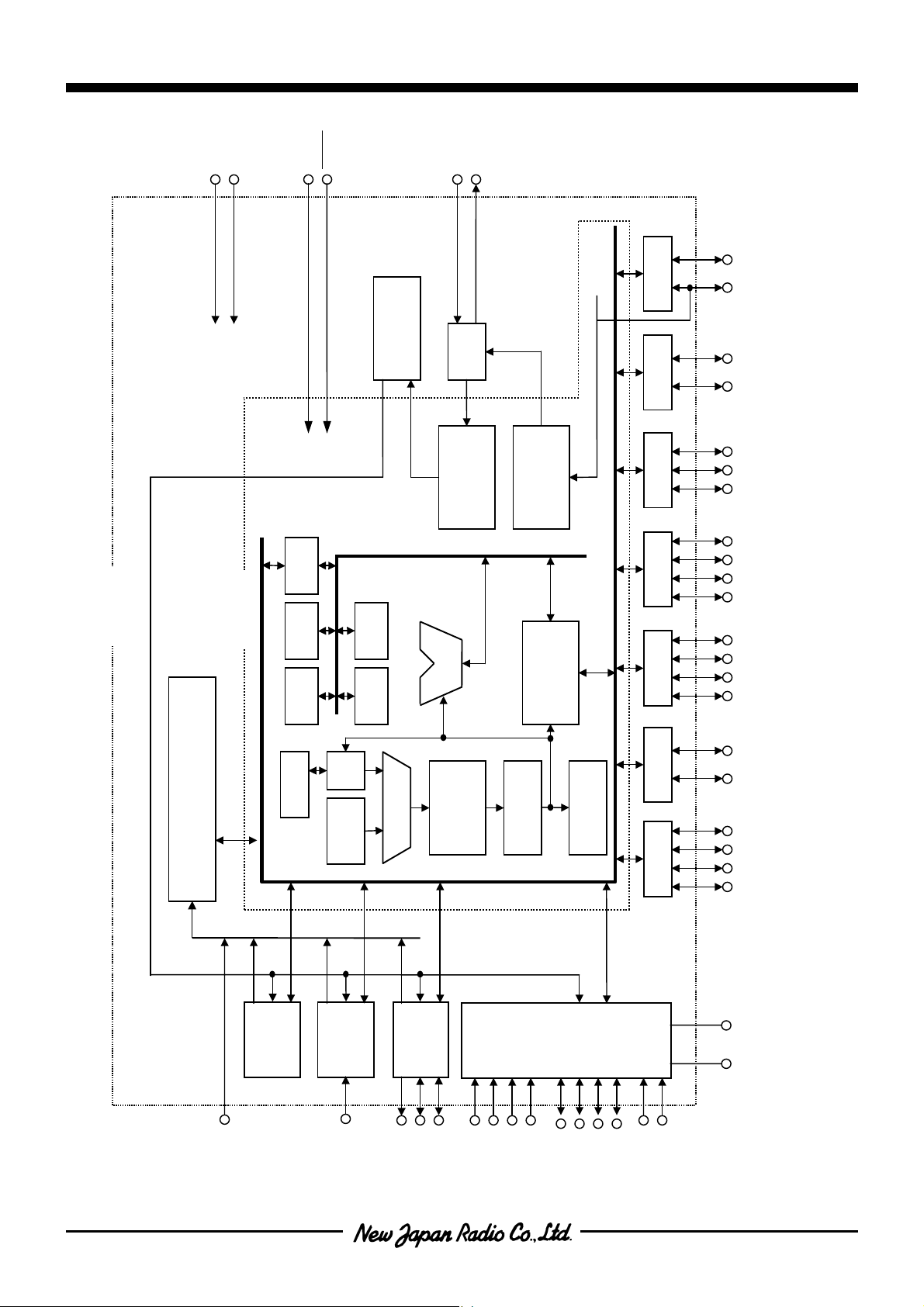

BLOCK DIAGRAM

■

NJU3555

DD

SS

V

V

CPU CORE

TEST

AC Y Reg X Reg

RESET

PRESCALER

Y’ Reg X’ Reg

OSC1

OSC2

PH1

PORT_H

OSC

PORT_G

CPU

TIMING

GENERATOR

STANDBY

CONTROLLER

PORT_F

PORT_E

ALU

RAM

256 x 4 bits

PORT_D

PH0

PG1

PG0

PF2

PF1

PF0

PE3

PE2

PE1

PE0

PD3

PD2

PD1

PD0

PC1

PC

STACK

MUX

OTP ROM

SIO

SDI(O)/PL1

8192 x 8 bits

AIN0/PI0

SCK/CKOUT

Interrupt Logic

INT2

INT1

TIMER1

EXTI/PK0

INT3

TLU addr

TIMER2

CNTI/PK1

INT4

SDO/PL0

I R

AIN1/PI1

AIN3/PI3

AIN2/PI2

I D

A/D

AIN5/PA1

AIN4/PA0

AIN6/PA2

PORT_C

PORT_B

/PJ0

REF

V

AIN7/PA3

ADCK/PJ1

PC0

PB3

PB2

PB1

PB0

AVDD

AVSS

Refer [INPUT OUTPUT TERMINAL TYPE]

*

- 2 -

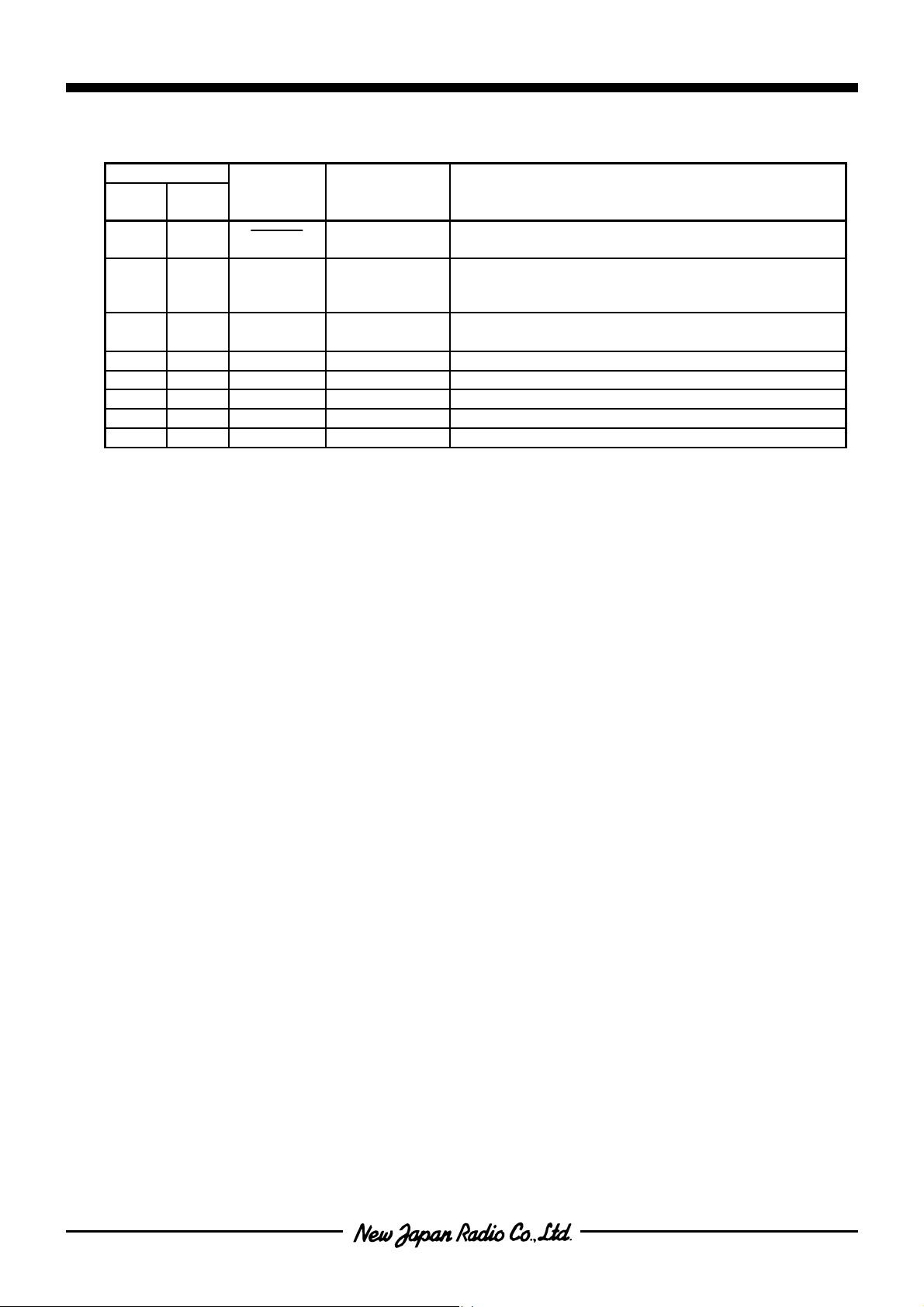

TERMINAL DESCRIPTION IN OTP PROGRAMMING MODE

■

No.

NJU

3555F

25, 26,

28-31,

34, 35

18, 33 21, 36 VDD - Power Source (5V)

11, 12 14, 15 VSS - Power Source (0V)

Note 1) Use at V

2) Non connect anything to the other terminals.

NJU

3555L

7 10 RESET INPUT

28, 29,

31-34,

37, 38

1 40, CNT1 INPUT

2 41 CNT2 INPUT

10 13 REQ OUTPUT Request output terminal

9 12 CLK INPUT Clock input terminal

8 11 PROM INPUT OTP programming enable terminal

SYMBOL

D0 - D7 INPUT/OUTPUT Data bus

=5V in OTP programming mode.

DD

INPUT /

OUTPUT

RESET terminal.

When the low-level input-signal, the system is initialized.

OTP control input terminal

NJU3555

F U N C T I O N

- 3 -

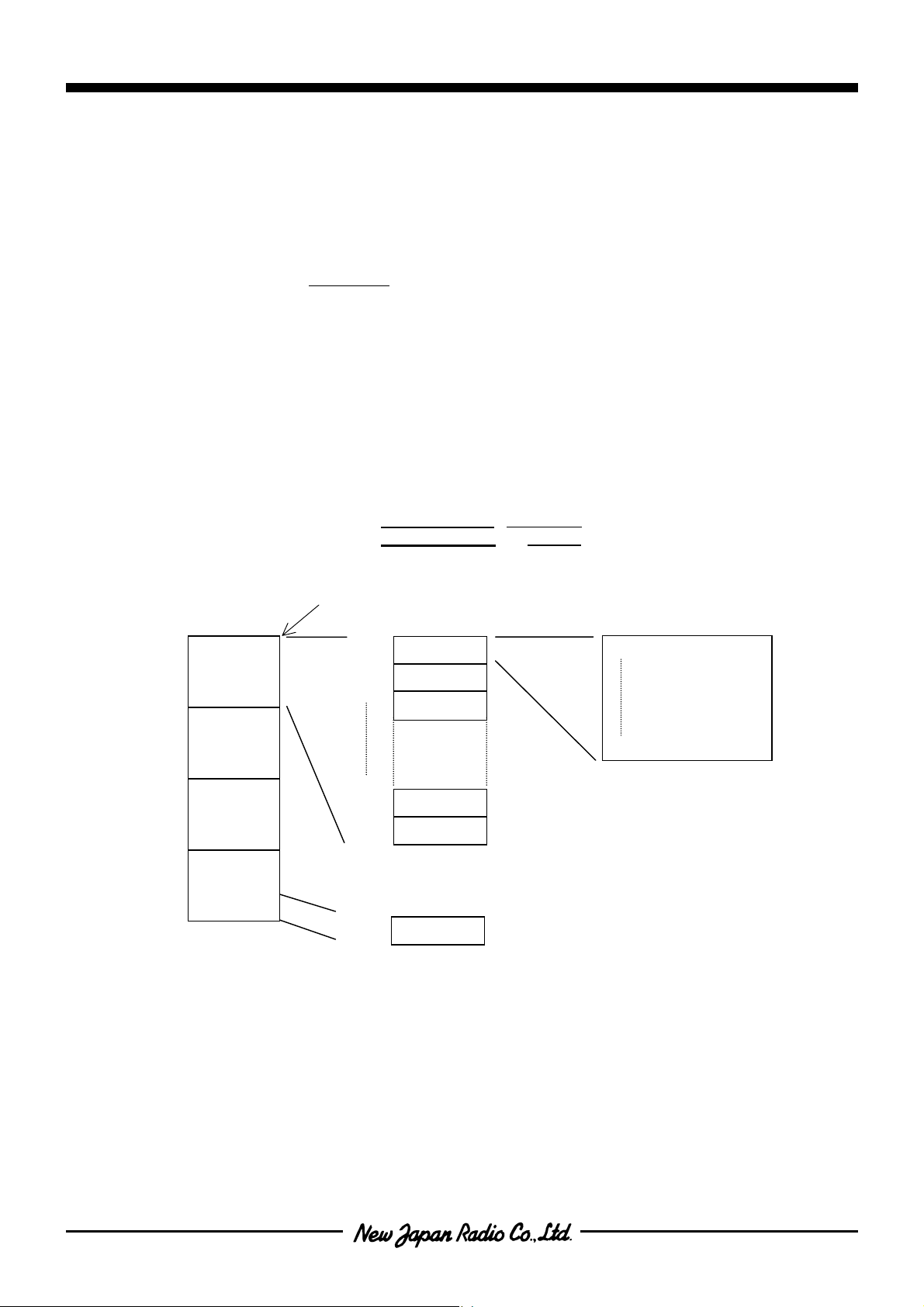

NJU3555

Difference between NJU3555 (OTP version) and NJU3505 (MASK version)

■

●

Operating mode

NJU3555

mode”.

•

Normal operating mode

•

OTP Programming mode

●

Programming memory (OTP)

The address location of pr ogramming memory (OTP) of

NJU3505

The option area is located in page 127(64bytes) in the following.

has two operating modes. One is ”Normal operating mode” and the other is “OTP programm ing

The ”TEST” terminal is set to low level. (The terminal is recommended to connect to GND.)

Operating voltage range; 2.7V ~ 5.5V

.

User program is read out from or written into the OTP by the universal programmer “SUPERPRO/ L” and

converting adapter made by XELTEK co,.(USA).

NJU3555

is compatible with the mask ed ROM of

, excepting the option area.

Program Area :

Option Area :

Addresses

Addresses

0000H ~ 1FBFH

1FC0H ~ 1FFFH

: 8,128bytes

: 64bytes

[ PROGRAM MEMORY AREA ]

Program Start Address

(Addresses) (Addresses in the bank)

0000H

07FFH

0800H

Bank 0

0000H

0040H

0080H

Page 0

Page 1

Page 2

Bank 1

0FFFH

1000H

17FFH

1800H

1FFFH

Bank 2

Bank 3

0780H

07C0H

07FFH

1FC0H

1FFFH

Page 30

Page 31

Bank 0

Option area

Page 127

∗

64 Instruction Words /Page

32 Pages / Bank

4 Banks / OTP

*

Page127 is program area.

(Addresses in the page)

00H

64 Instruction Words

3FH

8 Bits / Instruction Word

In case of NJU3505,

- 4 -

NJU3555

●

Reset Terminal Type

NJU3555 NJU3505

Internal Pull-up Resistance

●

Option information set in the initialization

When the initialization is perf orm ed(RESET ter m inal is “L” ), the operation inf orm ation stor ed in option area is

set as shown in the following timing chart . The option information is set in the term of

RESET releasing and oscillation stability time. Af ter inform ation set, the progr am c ounter is set to 0000H and

NJU3555

the

operates in normal.

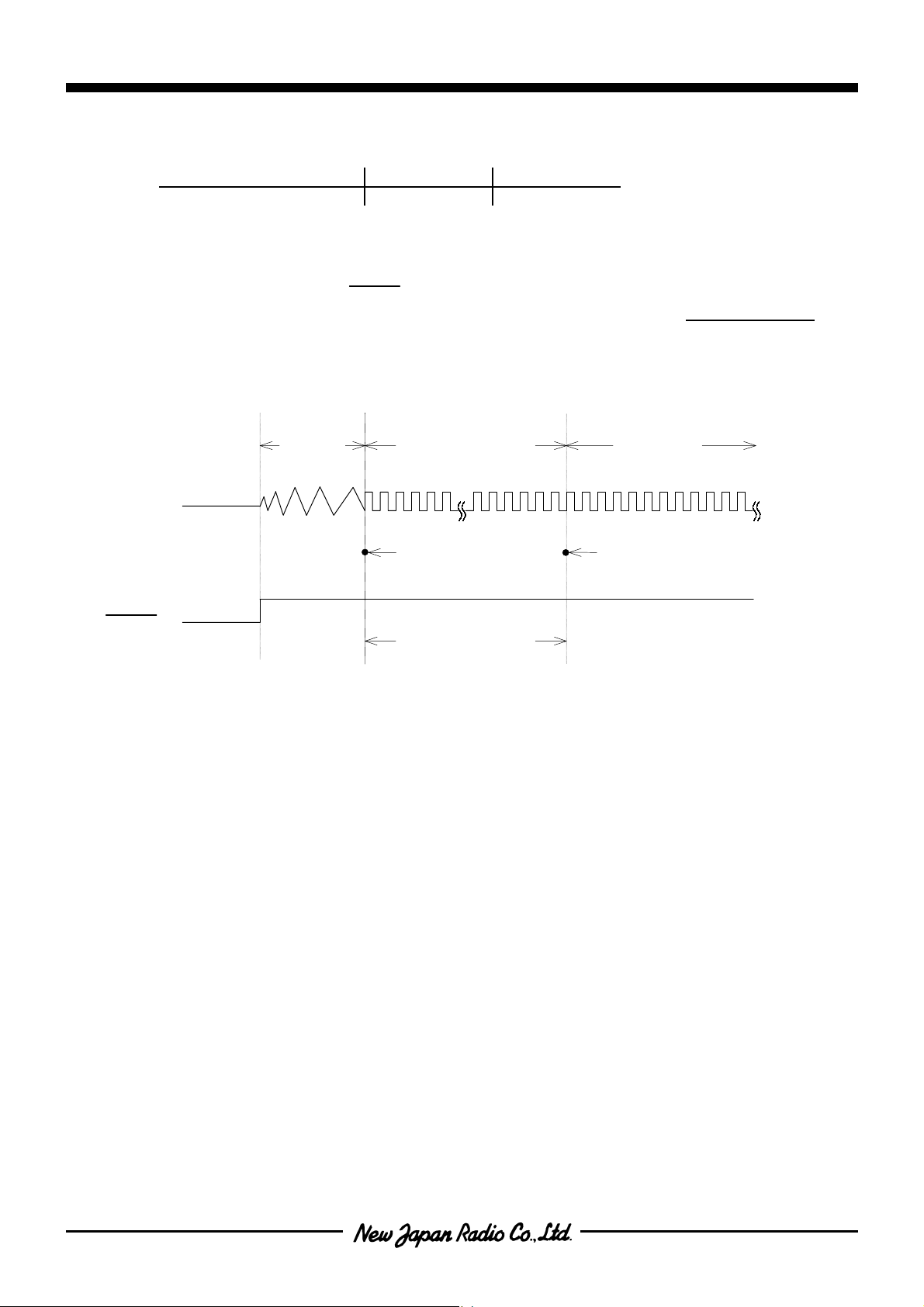

[ TIMING CHART ]

Oscillator

Clock

Oscillation

Stability

Time

RESET

With Pull-up

Option information setting

x512clock

1/f

OSC

Oscillation

Start

f

=4MHz

OSC

about 128µsec

Without Pull-up

Normal

Operation

PC=0000H

1 / f

OSC

x 512clock

after

- 5 -

NJU3555

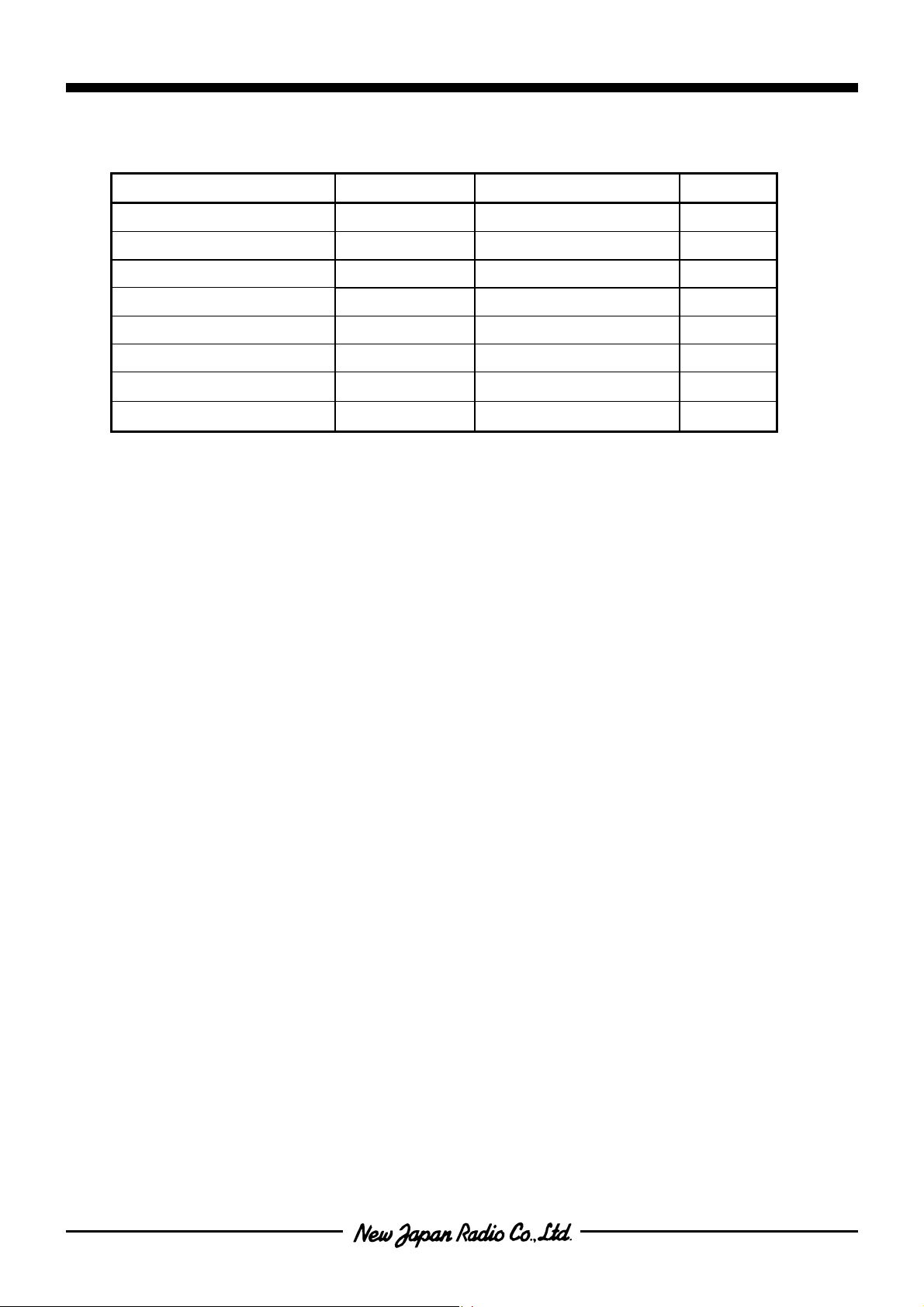

ABSOLUTE MAXIMUM RATINGS

■

(Ta=25°C)

PARAMETER SYMBOL RATINGS UNIT

Supply Voltage VDD -0.3 ~ +7.0 V

Input Voltage VIN -0.3 ~ V

Output Voltage V

-0.3 ~ V

OUT

Analog Supply Voltage AVDD -0.3 ~ V

Analog Reference Voltage V

-0.3 ~ AV

REF

Analog Input Voltage AIN0 ~ AIN7 -0.3 ~ AV

Operating Temperature

Storage Temperature

T

-20 ~ +75

opr

T

-55 ~ +125

stg

+ 0.3 V

DD

+ 0.3 V

DD

+ 0.3 V

DD

+ 0.3 V

DD

+ 0.3 V

DD

°

C

°

C

Note)

The difference of electrical characteristics between

NJU3555

(OTP version) and

NJU3505

(MASK version)

NJU3505 NJU3555

•

Supply Voltage (VDD) MIN.

2.4V

→

2.7V

•

Supply Current

5V (I

(I

(I

(I

(I

DD1

DD2

DD3

DD4

DD5

) Max.

) Max.

) Max.

) Max.

) Max.

1.2mA

1.2mA

1.6mA

4.0mA

4.0µA

→

→

→

30mA

30mA

30mA

30mA

20µA

→

3V (I

(I

(I

(I

(I

DD1

DD2

DD3

DD4

DD5

) Max.

) Max.

) Max.

) Max.

) Max.

0.5mA

0.5mA

0.6mA

1.0mA

2.0µA

→

→

20mA

20mA

20mA

→

→

20mA

20µA

- 6 -

Loading...

Loading...