Page 1

HP6/HP12

Digitally Controlled Dimmer Rack

TTEECCHHNNIICCAALL MMAANNUUAALL

Page 2

Equipment Description ii

Revision 2 - 26 April, 2000 HP SERIES DIMMER TECHNICAL MANUAL

JANDS ELECTRONICS PTY LTD 1997

All rights reserved

DISCLAIMER

Information contained in this manual is subject to change without not ice and does not

re pr es en t a co mmit ment o n t he pa r t o f t he ve ndo r . JAN DS E LE CT RO NI CS P/ L s ha ll

not be liable for any loss or damage whatsoever arising from the use of information or

any error contained in this manual.

It is recommended that all service and repairs on this product be carr ied out by JANDS

ELECTRONICS P/L or it’s authorised service agents.

JAN DS HP S er ies d immer s mus t o nly be use d fo r t he pur po se the y we re in te nde d by

the manufacturer and in conjunction with the operating manual.

JANDS ELECTRONICS P/L cannot accept any liability whatsoever for any loss or

damage caused by service, maintenance or repair by unauthorised personnel, or by use

other t han that intended by the manufacturer.

Manufactured in Australia by:

JANDS ELECTRONICS PTY LTD ACN 001 187 837

40 KENT Rd

Locked Bag 15

MASCOT NSW 2020

AUSTRALIA

PHONE: +61-2-9582-0909

FAX: +61-2-9582-0999

EMAIL: Internet: jandsinfo@jands.com.au

Page 3

Equipment Description iii

Revision 2 - 26 April, 2000 HP SERIES DIMMER TECHNICAL MANUAL

Table of Contents

Table of Contents

1.0 Introduction

1.1 Mains supply wiring............................................................................................1-1

1.2 Phase failure........................................................................................................1-2

1.3 Circuit breakers................................................................................................... 1-2

1.3.1 Overloads and Inrush................................................................................ 1-3

1.3.2 Short Circuits............................................................................................1-3

1.4 Outdoor Systems.................................................................................................1-3

2.0 Equipment Description

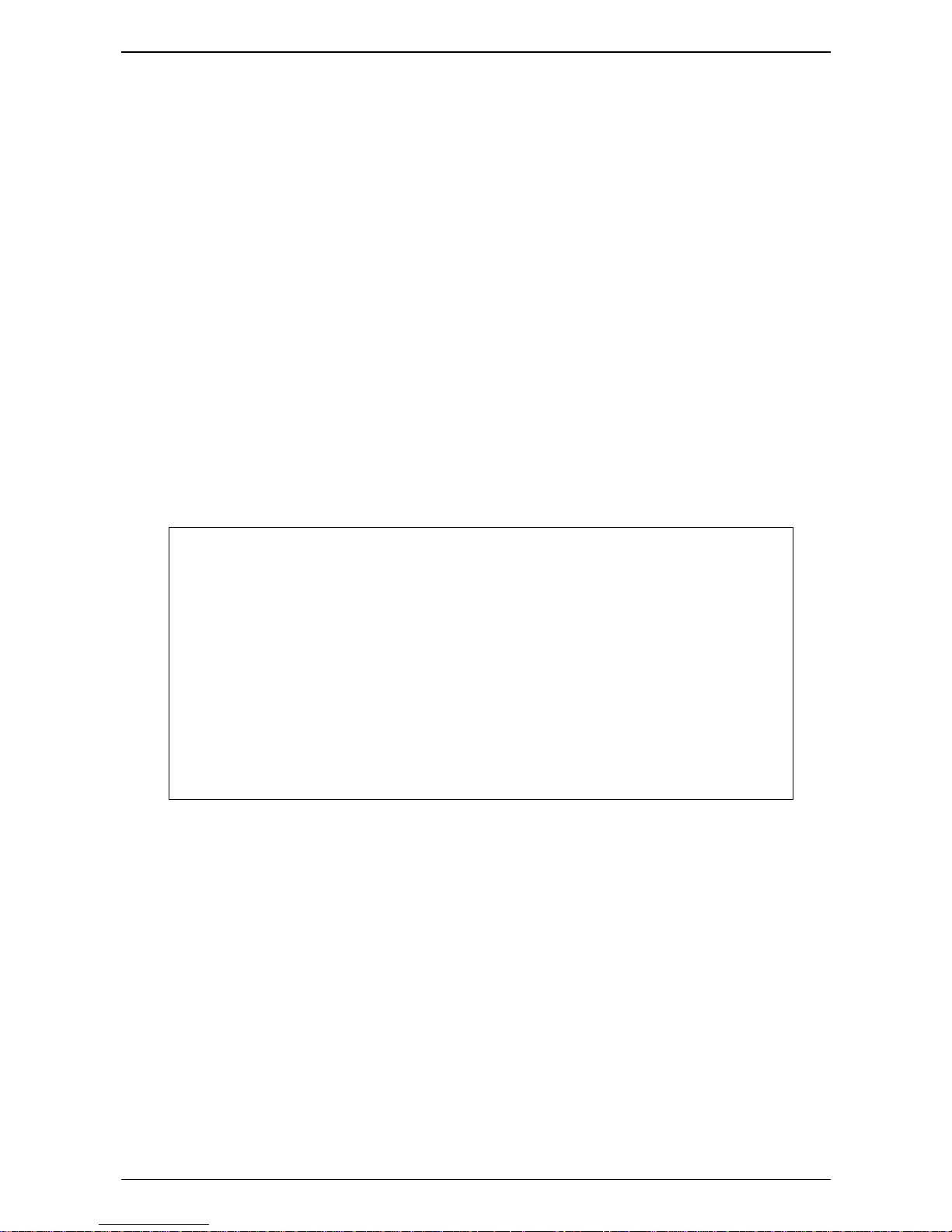

2.1 Front panel layout............................................................................................... 2-1

3.0 Circuit Descriptions

3.1 Mains and Low Voltage power supplies.............................................................. 3-1

3.1.1 Mains Circuit Wiring:................................................................................3-1

3.1.2 Mains Radio Frequency Suppression.........................................................3-2

3.1.3 Neutral - Earth Voltage Detection.............................................................3-2

3.1.4 Low Voltage Transformers....................................................................... 3-3

3.1.5 Control Tone Rejection............................................................................. 3-3

3.1.6 Low Voltage DC Supplies........................................................................3-3

3.1.7 Fan Control...............................................................................................3-4

3.2 Phase control...................................................................................................... 3-4

3.3 SCRs and triggering circuits ................................................................................ 3-4

3.4 Output chokes and filtering ................................................................................. 3-6

Page 4

Equipment Description iv

Revision 2 - 26 April, 2000 HP SERIES DIMMER TECHNICAL MANUAL

3.5 Load & drive indicators.......................................................................................3-6

3.5.1 Drive LEDs ..............................................................................................3-6

3.5.2 Load LEDs............................................................................................... 3-6

3.5.3 Load Detecting.........................................................................................3-7

3.6 CPU card............................................................................................................ 3-8

3.6.1 Microprocessor.........................................................................................3-8

3.6.2 Memory.................................................................................................... 3-8

3.6.3 DMX input / output..................................................................................3-9

3.6.4 Zero crossing detector .............................................................................. 3-9

3.6.5 Analog to digital converter (ADC)............................................................3-9

3.6.6 Optocoupler drive..................................................................................... 3-9

3.6.7 5 volt power supply................................................................................ 3-10

3.6.8 Reset generator....................................................................................... 3-10

3.6.9 Rotary encoder ....................................................................................... 3-10

3.7 Front panel card................................................................................................ 3-11

3.7.1 Switches................................................................................................. 3-11

3.7.2 LEDs ...................................................................................................... 3-11

3.7.3 Encoder.................................................................................................. 3-11

4.0 Dimmer Operation

4.1 Menu structure....................................................................................................4-1

4.1.1 ENTER .................................................................................................... 4-1

4.1.2 NORMAL ................................................................................................ 4-1

4.1.3 CLEAR .................................................................................................... 4-1

4.1.4 MODE menu ............................................................................................ 4-1

4.1.5 DMX CHannel menu ................................................................................ 4-9

4.1.6 DMX BANK menu................................................................................... 4-9

Page 5

Equipment Description v

Revision 2 - 26 April, 2000 HP SERIES DIMMER TECHNICAL MANUAL

4.1.7 BUILD menu.......................................................................................... 4-10

4.1.8 RUN menu.............................................................................................. 4-11

4.1.9 TEST function........................................................................................ 4-14

4.2 Deep clear......................................................................................................... 4-14

4.2.1 Quick deep clear..................................................................................... 4-14

4.3 Channel disable ................................................................................................. 4-15

4.4 Software update................................................................................................ 4-15

5.0 Fault Diagnosis

5.1 Protection........................................................................................................... 5-1

5.1.1 Output protection ..................................................................................... 5-1

5.1.2 Thermal protection....................................................................................5-1

5.1.3 Supply Power fault protection ................................................................... 5-2

5.2 Output faults....................................................................................................... 5-3

5.3 Operating faults...................................................................................................5-3

5.4 DMX faults.........................................................................................................5-3

5.5 Phase fault indication...........................................................................................5-4

5.6 Cold lamp filaments............................................................................................. 5-4

5.7 Memory failure....................................................................................................5-4

5.7 Fault finding guide .............................................................................................. 5-5

6.0 Disassembly

6.1 CPU card removal...............................................................................................6-1

6.2 Front Panel card removal.....................................................................................6-2

6.3 Triac / SCR replacement ..................................................................................... 6-3

6.4 “Engine Block” removal...................................................................................... 6-4

Page 6

Equipment Description vi

Revision 2 - 26 April, 2000 HP SERIES DIMMER TECHNICAL MANUAL

7.0 Test and Configuration Settings

7.1 CPU self-tests..................................................................................................... 7-1

7.2 Output card testing..............................................................................................7-2

7.3 Phase Compensation........................................................................................... 7-2

7.4 Dimmer Re-calib ration ........................................................................................ 7-3

8.0 Technical Data and Specifications

8.1 Multipin output connector pin-outs ..................................................................... 8-3

8.2 DMX connector pin-outs .................................................................................... 8-5

8.3 DMX bank allocations.........................................................................................8-5

8.4 Mains wiring colour codes...................................................................................8-6

Appendix A History of Modifications

Appendix B Connector Pinouts

Appendix C Spare Parts

Appendix D Circuit Diagrams

Page 7

Equipment Description 1-1

Revision 2 - 26 April, 2000 HP SERIES DIMMER TECHNICAL MANUAL

1.0 Introduction

1.1 Mains supply wiring

THREE PHASE OPERATION ("NORMAL"):

In Australia the HP12-TR / HP12-SC is normally fitted with a flexible supply cable and

32 amp Clipsal plug. The cable has 6mm2 (40 amp) conductors for t he three phases, t he

neutral and the earth.

Th e 3 2 a mp Clip s a l p lug s u its the ma jor ity of 3 phase v e n u e outlets in Au s tr a lia , and w ill

provide sufficient power to run twelve pairs of 1000 watt PAR64 lamps, assumimg

normal duty cycles.

The incoming mains supply must be protected at not more than 50 amps. The d imme r s '

circuit breakers are not rat ed t o co rrect ly clear faults if the supply protect ion is in excess

of this. Mains supplies are generally protect ed at lower cur rents (32 amps or 40 amps at

most Australian venues). It is up to the user to ensure that the dimmer is used in a

manner that do es not exceed the available supply capacity.

In Australia the HP6-C is normally fitted with a flexible supply cable and 50 amp Clipsal

plug. The incoming mains supply must be protected at not more than 63 amps. The

dimme r ’ s c ircu it br e a k e rs are not r ate d t o corre c tly cle a r fau lts if t h e s upply protection is

in excess of this.

The power cable is t erminated wit hin the dimmer at a six-way terminal block and an

earthing stud. The six-way terminal block has three poles for t he three live mains phases

(labelled A1, A2, A3), and three poles for the mains neutral (N1, N2, N3). The three

neutral poles are bridged with a copper link, with the mains neutral connected t o terminal

N2.

If the supply cable is damaged, it must be replaced with a cable available from JANDS or

its service agents.

SINGLE PHASE OPERATION:

The dimmers may be configured for single phase operation where three phase mains

supply is unavailable.

The dimme r sho uld be supplied with three same-phase actives and three neutrals. The

three active lines must each be prot ected at not more t han 50 amps [63 amps: HP6-C].

The three neutral conductors must each be rated at t he same current as the actives. The

ea rt h conductor should be similarly rated.

The bridge between the three neutral terminal poles (N1, N2, N3) must be removed

before the three incoming neutral lines are connected.

Although it is possible to supply the dimmer with one large single phase feed, the

dimmers' br eakers ar e not ra ted to clear fault s if the supply is protected at currents of

over 50 amps [63 amps: HP6-C].

Th e ne u t r al- e a r t h d et e c t io n will ac t if all t h r ee ne u t r a ls h av e mo r e t h an 15 v o lt s to e ar t h ,

or if any one neutral has more than 45 volts to earth.

Page 8

Equipment Description 1-2

Revision 2 - 26 April, 2000 HP SERIES DIMMER TECHNICAL MANUAL

DELTA SUPPLY OPERATION (ILLEGAL IN MOST COUNTRI E S !)

The available venue mains supply in some countries (eg. the Philip p ine s ) is in the fo rm o f

three phases (220 volts between phases) with no neutral connection. The dimmer ma y b e

configured for operation from 220V delta supplies.

The bridge between the three neutral terminal poles (N1, N2, N3) must be removed

before the three incoming active lines are connected.

• The first incoming active is connected to terminals A1 and N3.

• The second incoming active is connected to t er minals A2 and N1.

• The third incoming active is connected to terminals A3 and N2.

Note that this connection is ILLEGA L in Australia , Europe and the U.K..

Note that this connection renders the output sockets' neutral pins LIVE.

Note that a dimmer wired in this fashion will be subjected to CONTINUOUS

OVERVOLTAGE if connected to the 415V wye or star three-phase supply of most

countries.

The three active lines must each be protected at not more than 50 amps [63 amps: HP6C]. The dimmers' breakers are not rated to clear faults if the supply is protected at

currents of over 50 amps [63 amps: HP6-C]. The earth conductor must be similarly

rated.

Th e neut ra l-ea rt h volt ag e de tec to r w ill sens e whe the r t he "c ent re" (av era ge) volt ag e of

the three phases deviates more than 15 volts from earth.

Once again DELTA CONNECTION IS ILLEGAL AND DANGEROUS IN MOST COUNTRIE S !

1.2 Phase failure

If o n e p o w e r ph as e s hould fa il, t he d immer w ill t u r n o ff t h e o u t p u t s a ss o c iat e d w it h t ha t

phase. This function can be disabled by the operator. See section 4.1.4.5.

1.3 Circuit breakers

Th e circuit breakers protect the HP dimmers' o ut put devices a nd the user’s o utput wiring

against overloads and short circuits. The breakers have a "type 32" delay characteristic,

which is s imilar to standard switchboard b rea kers.

The delay characteristics of the circuit breaker are a delicate balance between high speed

(required for adequate semiconductor pr o tect ion) and surge tolerance (to pass t he inrush

current demanded by large incandescent lamps).

Each of the twelve output circuits is protected by a 11.5 amp [25 amp: HP6-C] fastacting magnetic circuit breaker. These breakers are designed to pass the rated current,

but will d is c onne c t t h e outpu t circu it fo r a n y overlo a d c ond itio n (th e la rge r th e ove r load ,

the quicker the disconnection).

NOTE: The dimmer outlet sockets are rated at 10 amps [20 amps: HP6-C]. Avoid

loading the dimmer outputs beyond the socket capa city.

The breakers protect the dimmer’s output devices from short-circuit loads and faulty

wiring loo ms, a nd save on expen sive dimmer repairs. A tr ipped circu it breaker indicates a

load fa ult tha t r equ ires immediate atten tion.

Page 9

Equipment Description 1-3

Revision 2 - 26 April, 2000 HP SERIES DIMMER TECHNICAL MANUAL

1.3.1 Overloads and Inrush

Co ld lamp fila me n ts c onsu me con s id e rably mor e p owe r th a n w a rm filame nts. Th is me a n s

that the first time the lamp is turned on to full, the surge current can be several times

greater than the rated cur r ent for the lamp.

This cold surge current may be enough to trip the output circuit breakers. If this

“nu isa nc e - t r ipp in g” o f t he c ir cu it b r ea k er s is a p r o ble m, t h e fila me nt P r e he at fa c ilit y ma y

be utilised . See section 4.1.4 .5 for inst ructions on e nabling the Preheat fac ility.

Lamp filament resistance is roughly propo rt ional to temperatur e. A filament preheated to

900°K (630°C) has a resistance about three times higher than a filament at room

temperature (300°K, 30°C).

Preheat turns on the selected channels a very small amount (around 1% at 240 volts and

4% at 110 volts) which heats the lamp filaments and increases their electrical resistance.

When the lamp is then turned on full, the surge current is much less and the circuit

br eak er will not trip .

Other advantages of using Preheat are an increase in lamp life (due to the reduction of

thermal shock to the filament s), and a reduct ion of lamp heat up t ime (the lamps will

flas h sligh tly quick er).

1.3.2 Short Circuits

The SCRs and triacs are protected by the circuit breakers during shorts produced by

damaged wiring or blown lamp filament fragments across the filament supports.

The stress on SCRs and triacs during short circuits depends on:

• The operating temperature of the devices prior to application of the short

• The impedances of the mains supply, dimmer cho kes and output cables

• The let-through energy of the circuit breaker when breaking the fault

• The moment during the mains wavefor m when the sho rt is ap plied

Th e t r ia c s in t he H P1 2 - T R w ill s u rv ive o u t p ut s ho r t cir c u it s u nd e r mo s t c o nd it io n s. T he

more rugged SCR pairs in the HP12-SC, aided by higher choke impedance, will sur vive

output short s under extreme conditions (high operating temperatures, high supply fault

curr ent ava ilability, zero cable le ngth from dimmer to short ).

1.4 Outdoor Systems

It is recommended that at outdoor shows where the power is locally generated the

following steps be taken to ensure a trouble-free show:

1. Run the console from an extension cord that is plugged into t he same power

so ur ce as t he dimme rs. If t his is n ot po ssible a DMX iso latin g unit sho uld be

inserted between t he ligh ting console and the dimmers.

2. Disable the neutral detect system. Generators often have poor regulation on

their output power and it is very likely that under certain circumstances this can

cause the neutral detect feature t o trip.

Page 10

SELECTSELECT

TR

1 7

6

2

5

3

4

891110

Figure 2.1

Page 11

Equipment Description 2-1

Revision 2 - 26 April, 2000 HP SERIES DIMMER TECHNICAL MANUAL

2.0 Equipment Description

2.1 Front panel layout

(

Figure 2.1

1. Channel output circuit breakers: The circuit breakers are rated at 11.5 amps

continuous, however Jands recommend the maximum load connected to a channel be

limit ed t o 1 0 a mps . T he H P6 - C br e ak e r s a r e r a t e d at 25 a mp s b ut J a nd s r ec o mme nd the

maximum channel lo ad be limited to 20 amps. If nuisance tripping occur s, enable the

Preheat option (see section 4.1.4.5). See also section 5.6 for a full explanation of

nuisance tripping.

2. Display: A r ed four dig it alp ha- numer ic dis play is use d to sh ow dimmer st at us a nd

option menus.

3. LEVEL/FUNCTION encoder wheel: This detent action control knob is used to

select items from the menus, and to select the channel levels or chase rat e (depending on

the operat ing mode).

4. DMX IN/LOOP connectors: A standard five pin AXR connector inputs control

desk DMX-512 signals and outputs them to ot her dimme rs via t he Lo o p c o nne ct o r. S ee

section 8.2 for wiring details.

5. DMX IN LED: A green LED indicates the presence of DMX signals.

6. Keypad: These switches are used to select different opt ions and operating modes. A

red LED is associated with each switch to indicate activation of selected function.

7. PHASE LEDs: T hree green LEDs (one for each phase) indicate that the three phase

mains supply is available.

8. Channel SELECT switch: These select or deselect options for each channel, or

switch a chan nel bet ween “on-line ” and “o ff-line”. I f a cha nnel is “off-line”, it will not

respond to the DMX input signals.

9. Channel STATUS LED: A bi-colour LED indicates channel status, ie.

Red = channel set for 110V o utput

Green = channel set for 240V output

Off = channel disabled

Orange = voltage change selected but not yet confirmed

Flashing = channel selected for changes to be made

10. DRIVE LED: This green LED indicates a contr ol signal is being applied to

that channel.

Page 12

Equipment Description 2-2

Revision 2 - 26 April, 2000 HP SERIES DIMMER TECHNICAL MANUAL

11. LOAD LED: This red LED serves two functions. In normal operation, it

acts as an output mimic. When the channel drive is at zero, it indicates whether that

channel’s load is disconnected (or o pen-circuit).

To check a load, set t he channel drive to zero. The LOAD LE D w ill t u r n O N if t he r e is

no lo a d.

For levels above zero, the LOAD L ED w ill mimic the c ha n n e l outpu t wh e never a load is

connected.

Note that the channel circuit breaker must be ON for the LOAD LED circuitry to work.

BREAKER LOAD CHANNEL DRIVE LOAD LED STATUS

on not connected off ON

on connected off OFF

on connected on OUTPUT MIMIC

off doesn’t matter doesn’t matter OFF

Page 13

Equipment Description 2-3

Revision 2 - 26 April, 2000 HP SERIES DIMMER TECHNICAL MANUAL

[ BLANK PA GE ]

Page 14

1 2 3 4 5 6 78

A

B

C

D

8

7654321

D

C

B

A

1

Jands Electronics P/L

40 Kent Rd

Mascot NSW 2020

Australia

Ph (02) 9582-0909

1

5

20-Apr-2000 16:51:13

H:\Lab\HPCE\CIRCUIT\H

p

tr

p

wr4.sch

Title

Size: Number:

Date:File:

Revision:

Sheet of

Time:

A3

Error : F:\PUBLIC\JANDS.EPS image file not suppor

t

MAINS, FAN CONTROL & POWER SUPPLY

HPTRPWR4

OPTO DRIVE CIRCUIT from CPU:

Open-collector switches (ULN2003 ICs) to common.

FRONTPANEL LED CIRCUITS:

Output mimic (load) LEDs are fed by 470R; LED cathodes

connected to common.

Drive LEDs fed by 470R; LED anodes connected to +5 volts.

C18

4n7-Y

C19

4n7-Y

C17

4n7-Y

C16

4n7-Y

C15

4n7-Y

C14

4n7-Y

TR2

Q6040K7

TR1

Q6040K7

R16

10K

RD2

470R

CF2

100nF

OPDIAC2

BRT11

BR2

DB102

RL2

47K

CS2

100nF

RT2

220R

RS2

100R

L2

CB2

11.5A

OPTRAN2

CNY17

OPTRANS13

CNY17

BR16

DB102

RG3

47K

RG2

47K

RG1

47K

D6

D5

D4

D3

D2

D1

C4

100nF

BR13

DB102

BR15

DB102

BR14

DB102

OPTRAN1

CNY17

CB1

11.5A

PTC3

30mA

PTC2

30mA

PTC1

30mA

C3

1uF

C2

1uF

C1

1uF

FAN-A

12V

TEMP1

LM35

C9

2200uF

TX1 TX2 TX3

L1

RS1

100R

RT1

220R

CS1

100nF

RL1

47K

BR1

DB102

R1

15R

R2

15R

R3

15R

C13

33uF

C11

33uF

C12

33uF

GPO1 GPO2

C7

100uF

OPDIAC1

BRT11

CF1

100nF

OTEMP

90DEG

U1B

LM358

Q2

BC557

R5

470R

R6

470R

R7

22K

R8

10K

U1A

LM358

R13

10K

RD1

470R

C8

10uF

TEMP2

LM35

C5

100nF

C6

100nF

R14

470R

R15

470R

Q1

TIP42

R4

1R

TPD

TPN

FL4

FL3

FL2

FL1

TRACKS

FUSIBLE

THREE

240v:14v

PHASE 3 NEUTRAL to CHANNELS 9 - 12

PHASE 2 NEUTRAL to CHANNELS 5 - 8

(STAR or WYE) OPERATION.

LINKED for NORMAL

NEUTRALS 1-2-3

INPUT WIRING OPTIONS

REFER TO MANUAL for

PHASE 1 NEUTRAL to CHANNELS 1 - 4

NEUT1

NEUT3

NEUT2

ACTIVES to BREAKERS

NEUTRALS to OUTLETS

GROUNDS to OUTLETS

CH3 - CH12

LOAD MIMICS

CHANNEL 2 LOAD MIMIC

CHANNEL 1 LOAD MIMIC

OUTPUT MIMIC (LOAD)

10

11

12

1

2

3

4

5

6

7

8

9

+5V to CH3 - CH12

CHANNEL 2 DRIVE

CHANNEL 1 DRIVE

5

42

1

Two channels of twelve shown.

OP2

LO2

LI2

CB2A2K2 G2

1

2

4

5

1

2

4

6

6

4

2

1

5

4

2

1

LEDs

DRIVE/OUTPUT

FRONTPANEL

TO

CARD

CPU

TO

12

11

10

9

8

7

6

5

4

3

2

1

+5

+5

Temp

V-Faults

COM

+Vs

A

B

C

G1K1 A1

NEUTRAL 3

NEUTRAL 2

CB1

PHASE 1

PHASE 2

CHANNEL DRIVE

EARTH

NEUTRAL 1

PHASE 3

1

2

3

4

5

6

7

8

9

10

11

12

CIRCUIT CARD:

HPCEPWR4

HP-12TR TOURING DIMMER

LI1

LO1

OP1

A

E

NA

E

N

4

8

7

6

5

1

2

3

TP+

TP5

TP-

TPT

Ch.1-4

Ch.5-8

Ch.9-12

Page 15

1 2 3 4 5 6 78

A

B

C

D

8

7654321

D

C

B

A

0

Jands Electronics P/L

40 Kent Rd

Mascot NSW 2020

Australia

Ph (02) 9582-0909

027-Apr-2000 13:15:21

H:\Lab\HPCE\CIRCUIT\Hpscpwr6.s01

Title

Size: Number:

Date:File:

Revision:

Sheet of

Time:

A3

Drawn By:

Error : logo2.jpg file not found.

FRONTPANEL LED CIRCUITS:

Output mimic (load) LEDs are fed by 470R; LED cathodes

connected to common.

Drive LEDs fed by 470R; LED

anodes connected to +5 volts.

OPTO DRIVE CIRCUIT from CPU:

Open-collector switches

(ULN2003 ICs) to common.

CON3

Q1

TIP42

C19

4n7-Y

C18

4n7-Y

C17

4n7-Y

C16

4n7-Y

C15

4n7-Y

C14

4n7-Y

CHASSIS

CHASSIS

CON3

CON3

CON3

CON3

R15 470R

R14 470R

C6

100nF

C5

100nF

TEMP2

LM35

C8

10uF

R13

10K

U1B

R8

10K

R7(A-C)

3x10K

R6

470R

R5(A-D)

4x2K2

Q2

BCX17

U1A

CON3CON3

FAN-B

12V

OTEMP

110DEG

C7

100uF

GPO2GPO1

C12A,B

2x33uF

C11A,B

2x33uF

C13A,B

2x33uF

R3

4R7

R2

4R7

R1

4R7

TX3TX2TX1

C92200uF

TEMP1

LM35

FAN-A

12V

CON3CON3

C1

1uF

C2

1uF

C3

1uF

PTC1

30mA

PTC2

30mA

PTC3

30mA

CB1

11.5A

C4

100nF

D1

D2

D3

D4

D5

D6

RG1

100K

RG2

100K

RG3

100K

OPTRANS13

CNY17

CB2

11.5A

CON3

CON3

CON3

CON3

R16

4K7

CON1CON1 CON1CON1

L1 L2

CON1CON1CON1CON1

D8

D9

D10

D11

C202200uF

D12D13

D14D15

D16

D17 D18

D19D20

D21

D22

D23

C21

2200uF

C22

100uF

LP1

220uH

D24

HER303

R18

470R

R19

1K

ARROW

ARROW

R4

1R

CON3

R17

2K2

R20

10K

R21

470R

R22

470R

C10

2n2

TPD

U2

LM2575-5

FUSIBLE

TRACKS

FL1

FL2

FL3

FL4

EARTH BAR

TPT

TP-

TP5

TP+

3

2

1

5

6

7

8

4

N

E

AN

E

A

TOURING DIMMERHP12-SC

FAN CONTROLMAINS WIRING, and POWER SUPPLY

6.0

HPSCPWR6

12

11

10

9

8

7

6

5

4

3

2

1

PHASE 3

NEUTRAL

EARTH

CHANNEL DRIVE

PHASE 2

PHASE 1

D.FORD

NEUTRAL

NEUTRAL

3

4

567

8

9

101112

1

2

3

C

B

A

+Vs

COM

Temp

+5

+5

1

2

3

4

5

6

7

8

9

10

11

12

TO

CPU

CARD

TO

FRONTPANEL

DRIVE/OUTPUT

LEDs

Two channels oftwelve shown.

1

24

5

CHANNEL 1 DRIVE

CHANNEL 2 DRIVE

+5V to CH3 - CH12

9

8

7

6

5

4

3

2

1

12

11

10

OUTPUT MIMIC (LOAD)

CHANNEL 1 LOAD MIMIC

CHANNEL 2 LOAD MIMIC

GROUNDS to OUTLETS

NEUTRALS to OUTLETS

ACTIVES to BREAKERS

NEUT2

NEUT3

NEUT1

PHASE 1 NEUTRAL to CHANNELS 1 - 4

REFER TO MANUAL for

INPUT WIRING OPTIONS

NEUTRALS 1-2-3 LINKED for

NORMAL (STAR or WYE) OPERATION.

PHASE 2 NEUTRAL to CHANNELS 5 - 8

PHASE 3 NEUTRAL to CHANNELS 9 - 12

240:14V

THREE

NN

OP1

LO1

LI1

CB1

OP2

LO2

LI2

CB2

MIMIC1

DRIVE1

+5V

COMMON

+10V

+10V

COMMON

+5V

DRIVE2

MIMIC2

+7.6V to CH3-CH12

COMMON to CH3-CH12

MAINS VOLTAGES

LOW VOLTAGES

THYRISTOR CONTROL CIRCUITS:

REFER TO DIAGRAM HPSCHDF4

Refer to diagramHPSCHDF5

for thyristor firing circuits.

TPN

3

4

567

8

9

101112

3

4

567

8

9

101112

+Vs

+7.6V

Neutral

Detect

Page 16

1 2 34

A

B

C

D

4

321

D

C

B

A

Title

Number RevisionSize

A4

Date: 20-Apr-2000 Sheet of

File: D:\R_&_D\HPDIMMER\CIRCUIT\Hpschdf3.s01Drawn By:

ARROWARROW

ARROW

ARROW

ARROW

ARROW

ARROW

ARROW

OPTRAN1

CNY17

DP1

DN1 DM1

DL1

RL1

47K

RS1

100R

CS1

47nF

CF1

47nF

SCRB1

SCRA1

L1

CON1

CON1

CON1

CON1

RY1

2R7

RX1

68R

RW1

68R

RP1

10K

RA1

10K

RB1

4K7

RC1

2K2

QA1

BCX19

QB1

BCX19

QC1

BCX19

QE1

BCX19

QG1

BCX19

QD1

BCX17

QH1

BCX17

CA1

100uF

CB1

1uF

TX1

DA1

DB1

DC1

DD1

DE1

DF1

DG1

DH1

DJ1

DK1

RD1

100K

RE1

100K

RF1

100K

RH1

4K7

RJ1

4K7

CC1

2n2

RK1

4K7

RM1

4K7

RN1

4K7

RQ1

2K2

RR1

4K7

ARROW

CD1

100nF

CE1

100nF

RU1

68R

RV1

68R

3

D.FORD

HPSCHDF3

LOW VOLTAGES MAINS VOLTAGES

LEDs

MIMIC

LOAD

to

SUPPLY

+5V

SUPPLY

+10V

NEUTRAL

MAINS

LOAD

to

OUTPUT

BREAKER

POWER

MAINS

from

NEUT1 OP1 LO1 LI1 CB1

HP12-SC SCR FIRING & OUTPUT

CHANNEL 1 SHOWN

from

ULN2003

on CPU

CARD

One of twelve circuits per unit shown.

This diagram is a part of diagram

2W

3W

Q6035K

Q6035K

All diodes BAV103.

All resistors 1/16W

SMT unless stated.

HPSCPWR3.

Page 17

Equipment Description 3-1

Revision 2 - 26 April, 2000 HP SERIES DIMMER TECHNICAL MANUAL

3.0 Circuit Descriptions

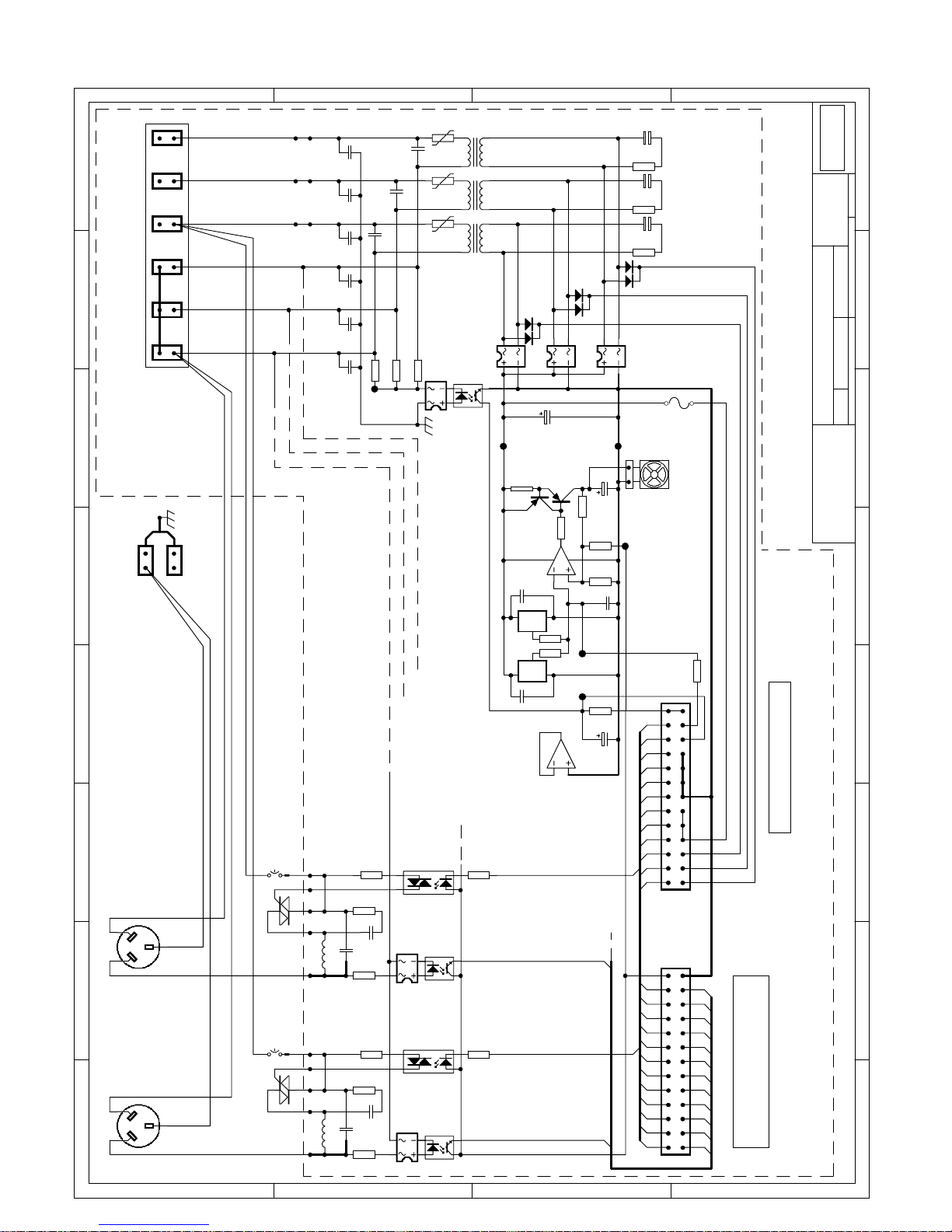

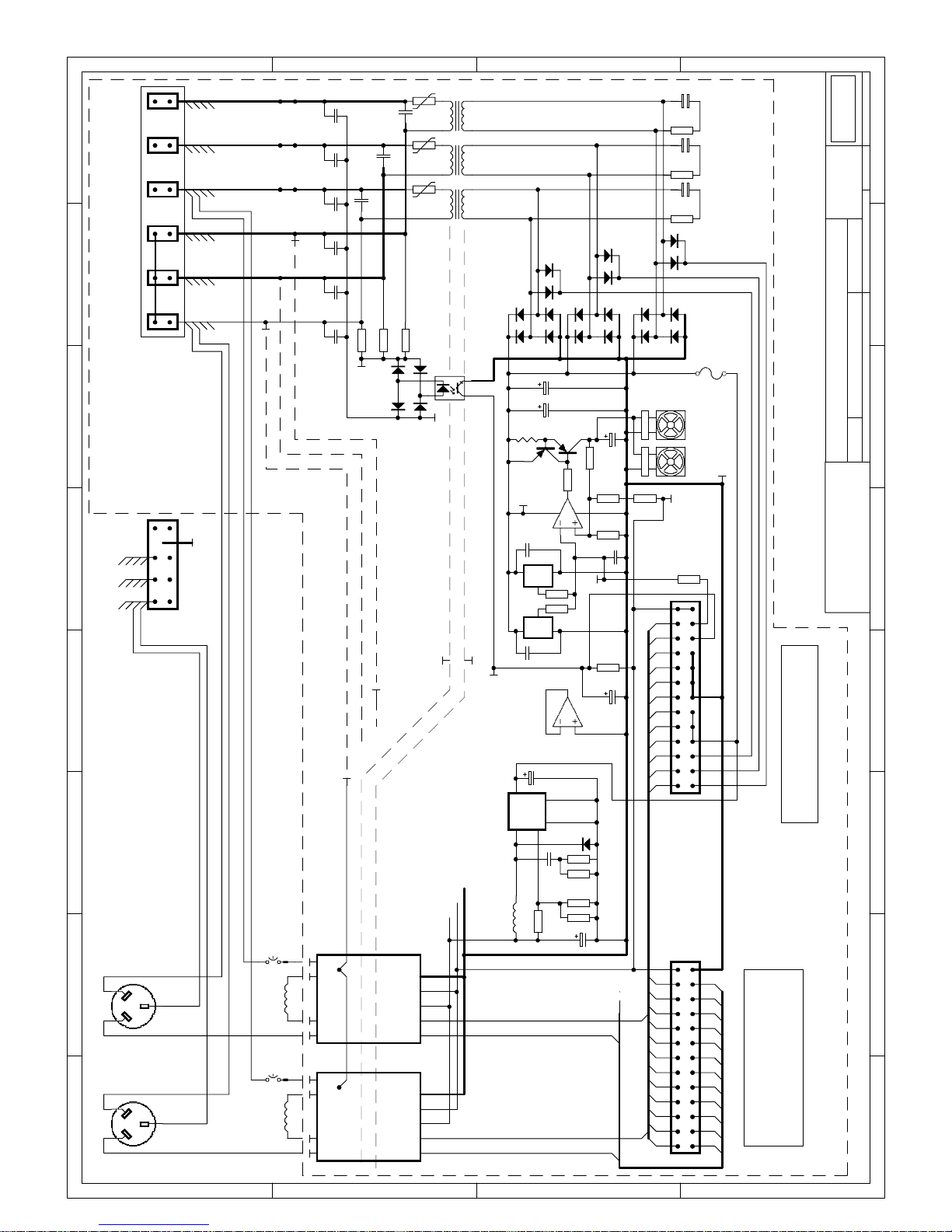

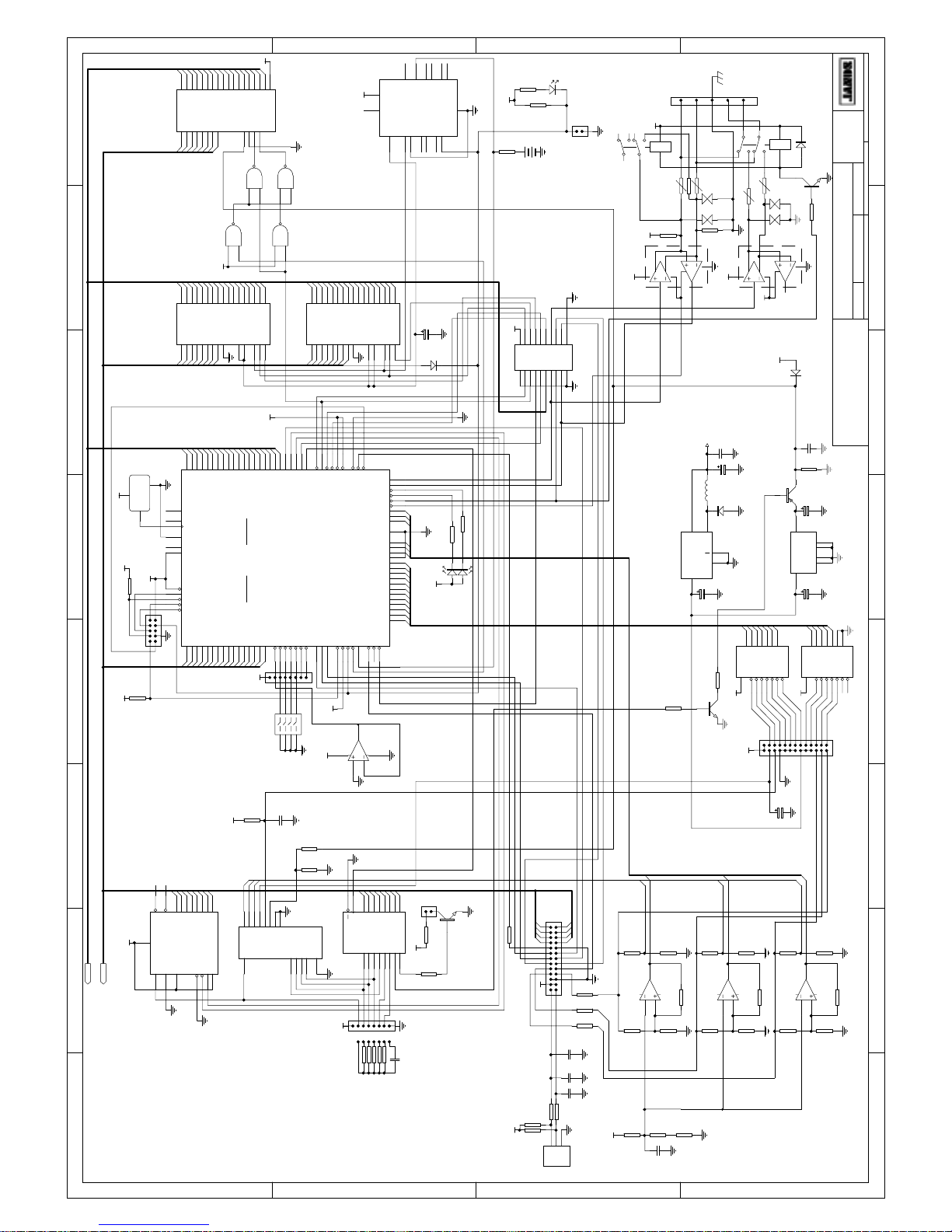

(

Figure 3.1

The Output PCB contains the circuitry for the output devices (triacs in the HP12-TR and

SCRs in the HP12-SC and HP6-C), the temperature-controlled fan, and the 15 volt

power supply.

3.1 Mains and Low Voltage power supplies

Th e d imme r ele c t r o nic s us e s lo w volt a ge d c p o w e r at 15 volt s (u n re g u lated ) a nd 5 v o lt s

(regulated). The HP12-SC also uses a 10V regulated supply for the gate drive

os cillators. The unregu la ted DC p owe r is s upplied by three transformers mounted on the

output PCB.

3.1.1 Mains Circuit Wiring:

The mains circuits of the HP dimmers are co nfigur ed as three separate phase circuits,

with four channels per circuit. The three active mains inputs and three separat e mains

neutral inputs appear at a terminal block, labelled A1, A2, A3 and N1, N2, N3

respectively. The ground ter minal is an adjacent M4 stud.

This wiring allows the dimmer to be configured for three-phase star (wye) mains

supplies, three-phase delta supplies or single-phase supplies.

THREE PHASE OPERATION ("NORMAL"):

Th e r ac k mo u nt HP dimme rs ar e no rma lly supplied with a three-phase power cable and

plug attached, suiting the vast majority of available mains supplies (ie. three phase and

neutral). The three live mains phases are connected to terminals A1, A2, A3. The three

neutral poles are bridged with a copper link, with the mains neutral connected t o terminal

A2.

SINGLE PHASE OPERATION:

The dimmers may be configured for single phase operation where three phase mains

supply is unavailable.

The dimme r sho uld be supplied with three same-phase actives and three neutrals. The

three active lines must each be prot ected at not more t han 50 amps [63 amps: HP6-C].

The three neutral conductors must each be rated at t he same current as the actives. The

ea rt h conductor should be similarly rated.

The bridge between the three neutral terminal poles (N1, N2, N3) must be removed

before the three incoming neutral lines are connected to these terminals. The three

incoming actives are connected t o A1, A2, A3.

Page 18

Equipment Description 3-2

Revision 2 - 26 April, 2000 HP SERIES DIMMER TECHNICAL MANUAL

DELTA SUPPLY OPERATION (ILLEGAL IN MOST COUNTRI E S !)

The available venue mains supply in some countries (eg. the Phillip in es ) is in t he fo r m o f

three phases (220 volts between phases) with no neutral connection. The dimmer ma y b e

configured for operation from 220V delta supplies.

The bridge between the three neutral terminal poles (N1, N2, N3) must be removed

before the three incoming active lines are connected.

• The first incoming active is connected to terminals A1 and N3.

• The second incoming active is connected to t er minals A2 and N1.

• The third incoming active is connected to terminals A3 and N2.

Note that this connection is ILLEGAL in Australia, Europe and the U.K. since this

connection renders the out put sockets' neutral pins LIVE.

No te t hat a dimme r wire d in this fas hion w ill be sub jected t o CONT INUOUS OVERVOLTAGE if connected to the 415V wye or star three-phase supply of most countries.

3.1.2 Mains Radio Frequency Suppression

Radio-frequency interference generated by phase-controlled dimming is heavily

attenuat ed before it can contaminate the mains supply.

Capacitors C1, C2 and C3 (1uF 275VAC X2 rated) are connected from each incoming

active (A1, A2, A3) to the corresponding neutral (N1, N2, N3).

Capacitors C14 thru C19 (4700pF 275VAC Y2 rated) are co nnected from each incoming

active and neutral to ground.

The mains circuits are protected from (improbable) catastrophic failure of these

capacitors by fusible PCB track links (labelled FL1 thru FL4). Failure of these links will

remove power from the low-voltage transformer associated with that phase. The links

may be re new ed du ring rep airs by wir e links (a s ingle s tr and o f flexib le wir e, n ot mor e

than 0.2mm dia).

3.1.3 Neutral - Earth Voltage Detection

Voltages of more than 15V (AC average) between neutral and earth are a strong

indicator of mains supply problems (eg missing or weak neutral connection, or missing

earth).

Th e vo ltage from the dimmer s' ea rt h to each of the three neutrals is sensed by three 100K

resistors (RG1, RG2, RG3), full-wave rectified and fed to the input LED of an

optoisolator.

When the dimmer is configured for normal three-phase star connection, the three

incoming neutrals are bridged, yielding an impedance of 33K from neutral to gro und and

a sensitivity of 15V AC average.

If t h e d imme r is c o nf igu r e d fo r t h r ee s ame - p ha se inp u t s, each neutral has a sensitivity of

45V (or 15V for all three neutrals).

If the d imme r is c onfig u r ed for d e lta ope ratio n (with no incoming neutra l) th e c ircu it will

detect when the "centre average" of the three phases deviates more than 15V from earth.

Page 19

Equipment Description 3-3

Revision 2 - 26 April, 2000 HP SERIES DIMMER TECHNICAL MANUAL

3.1.4 Low Voltage Transformers

HP12-TR: The transformers are nominally rated at 375V (primary), 23V (secondary).

Th e p rima ry w ind ings o f t hes e t r an sfo rme r s w ill to le ra t e 415 vo lts without o verheating.

They are protected against secondary-side overloads by card-mounted 30mA PTC

thermistors. These thermistors are sized NOT to trip during mains overvoltages, but

WIL L tr ip if a lo w vo lta ge fa ult o cc urs . T hermis to r c uto ut will t ur n off the fro ntp anel

PHASE LED.

HP12-SC, HP6-C: The transformers are nominally rated at 240V (primary), 15V

(secondary). The primary windings are protected against secondary-side overloads by

card-mounted 30mA PTC thermistors. These thermistors will trip during continuous

mains overvoltages of more than 340V. Thermistor cutout will turn off the frontpanel

PHASE LED.

If t her mist or c ut ou t o ccu rs, the y may be r ese t by t ur ning off p owe r t o the dimmer for

five seconds. However, since thermistor cutout will never occur during normal

operat ion, t he cause o f cutout should be investigated.

3.1.5 Control Tone Rejection

Control to nes are superimposed on mains voltages by supply authorities to co ntrol offpeak heaters etc. Tone frequencies of 750 Hz and 1050 Hz are common, although

frequencies from 167 Hz to 1750 Hz are in use. Amplitudes are typically less than 5

volts, although higher levels have been reported at some locations.

These tones may cause flicker in dimmed lamps, due to jitter in the detected zerocrossing position.

Th e e ffe c t o f c ontrol t ones is min imis e d b y filter in g a t t h e s e c ondary w in d in g s o f the low

voltage transformers. Resistor-capacitor networks (R1-CF3, R2-CF4, R3-CF5), in

conjunction with inherent transformer inductances, form a 12 dB/oct filter at 400 Hz.

Control tones at levels up to 15 volts at 750 Hz, or 25 volts at 1050 Hz, have little effect

on performance.

3.1.6 Low Voltage DC Supplies

Each of the three tr ansformers has two asso ciated rect ifiers. One set o f rectifiers feeds

the common DC supply filter capacitors, while the other provides full-wave rectified

waveforms to the zero- crossing detect ors and three phase indicator LEDs via the Front

Panel PCB.

Th e dimme rs’ u nre gula ted supply is filtered by C9 (2200uF) and directly feeds the fan

controller, the overvoltage detector and the temperature sensors. All other circuits are

supplied via the OTEMP overtemperature cut out.

Th e dimme r w ill shut d ow n und er so ftw are co nt ro l at 8 5°C. If t he d immer ma nag es t o

reach higher temperatures than this, the OTEMP cutout will remove power from all

cir cu it s e xce p t t h e fa n c o ntroller a nd a ss o cia t e d cir c u it s. T he fa n s pe e d w ill in cr e a se d u e

to lighter supply loading.

The unregulated dc voltage at the common supply filter capacitor (C9) is normally

ar oun d 1 4 ~ 1 5 v olt s b u t may drop a s low a s 1 1 vo lts w ith lo w mains v olta ges , or rise in

excess of 20V during severe mains overvoltages.

Mains overvoltages are sensed as high unregulated DC voltages by op-amp U1b. Since

the DC supply voltage is dependent on dimme r lo a d ing as w ell a s main s v o lt a ge , t h e t r ip

point of this circuit may vary from 260V to 280V AC mains voltage.

Page 20

Equipment Description 3-4

Revision 2 - 26 April, 2000 HP SERIES DIMMER TECHNICAL MANUAL

3.1.7 Fan Control

Temperatures are sensed by LM35DZ sensors mounted at the exhaust ("hot") ends of the

heatsinks. These sensors have an output voltage of 10mV per degree Celsius (ie. 300mV

at 30°C). Their output voltage is summed and fed to the frontpanel CPU card for

temperature display, and to the 12 volt dc fan control.

The fan speed controller is a DC amplifier formed by op-amp U1a and transistor Q1. The

fan is "held off" until sensor temperatures reach 30°C by resistor R16 from the 5V rail.

The fan voltage reaches 12V at t emperatur es of 50°C.

The circuit is protected against shorts in the fan or its wires by transistor Q2, which

clamps the out put current at 0.6 amps.

3.2 Phase control

Th e p ow er a pp lied t o a lo ad is va r ied by co nt r o lling t h e p oin t o f t hyr ist o r firin g in each

mains half-cycle.

The convention used here is that firing angles of 0° (0 radians) occurs at t he end of each

half cycle, and give zero output. Firing angles of 180° (π radians) occurs at the beginning

of each half cycle, giving maximum (unity) output.

The traditional method of achieving phase control (ie. firing position control) has been to

generate a "ramp" voltage in each half-cycle, which is then compared t o t he dc contro l

signal.

Key elements in this technique are:

• The ramp begins just after the st art of the half cycle, at a voltage equal to the

maximum control voltage.

• The ramp ends just before the finish of the half cycle, at a voltage equal to the

minimum control v oltage.

• The beginning and end of the ramp are determined by zero crossings of the

mains wav eform.

• The shape of the ramp determines the control law (CV to P law).

No t e t h at the finit e wid t h o f t he z er o - c r o s sing p u lse c au s es t he d immer t o jump fr om no

firing to some small firing angle as soon as contro l voltage is applied. The snap-on firing

angle is defined by the zero cro ssing pulse width.

This is actually a ver y mino r pr oblem since zero c rossing puls es o f 2.2 ms (±1100 µs

around tr ue zero crossing) give a snap-on power o f less than 1%. The HP has a zerocrossing pulse width less than 2 ms.

The HP micropro cessor (µP) generat es its "ramp" digitally, and specifically shapes the

ramp to pro vide linear control-to-power characteristics. The µP then compares the DMX

channel information with the generated ramp information and turns on the appro priate

output device at the required point on each mains half-cycle.

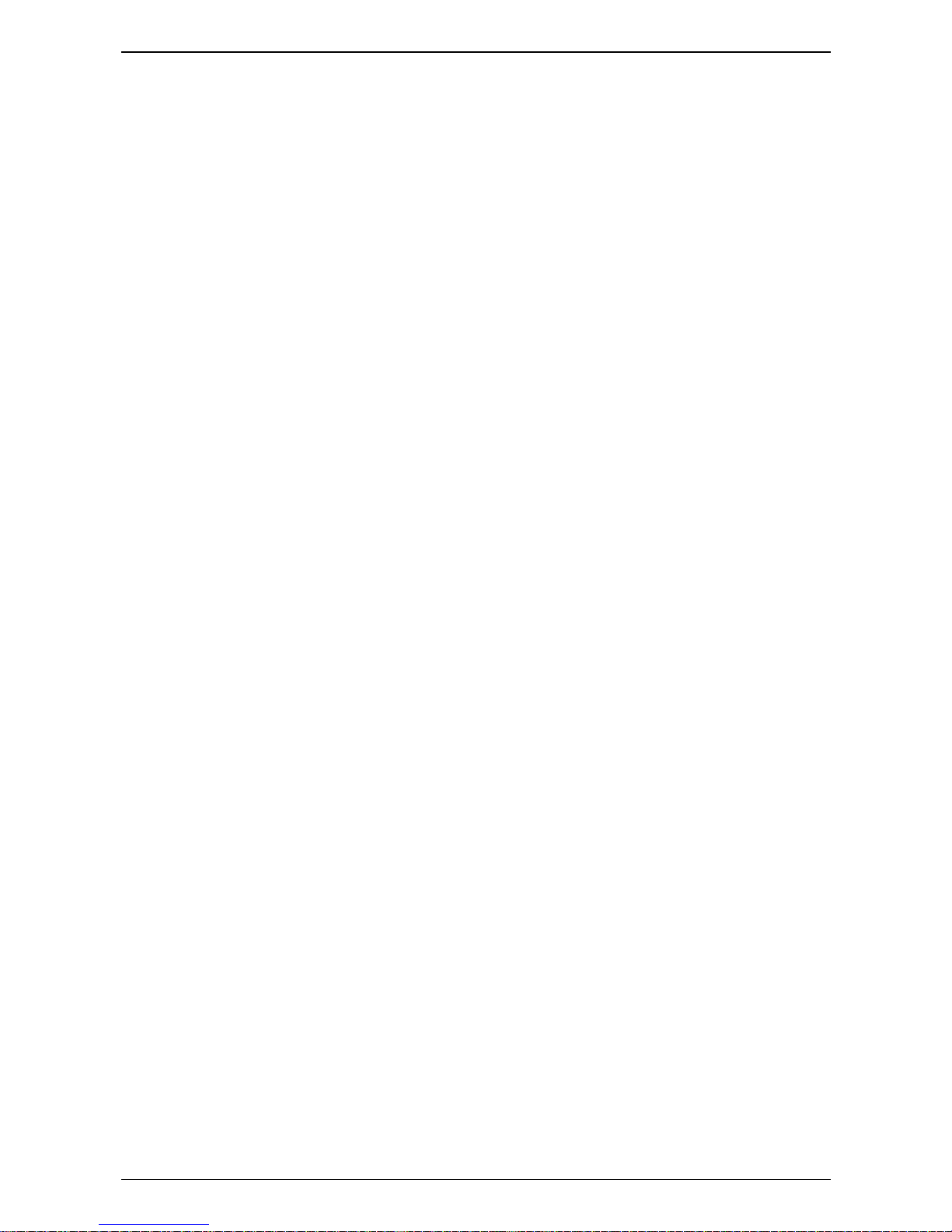

3.3 SCRs and triggering circuits

HP12-TR:

The triacs used in the HP12-TR are 40 amp, 600 volt devices (type Q6040K) with 2500

volt isolation to t he mounting tab. They have a surge current rat ing of 335 amps for 10

millise cond s. The d immer w ill func tio n wit h re placement triacs of lower ratings but its

ability to s urv ive shor t circuits and ove rvoltages will be jeopardised.

Page 21

Equipment Description 3-5

Revision 2 - 26 April, 2000 HP SERIES DIMMER TECHNICAL MANUAL

The output devices are triggered with Siemens BRT12 opto-isolators. These are

optically triggered SCRs rated at 600 volts.

Opto-triggered dimmers have a lower ability to correctly drive low-power inductive

loads than DC-fired SCR dimmers. Although this is true of the HP12-TR, careful

snu bber des ign and comp one nt se lect ion guar ant ees tha t it will co rr ect ly dr ive a ll load s

from rated maximum down to 25 watt transformer pinspots.

When the lamp blows in a transformer-driven pinspot, the unloaded t ransformer primary

pr es ent s a ve ry s mall, hig hly ind uc t ive lo a d. T he H P1 2 -T R d immer may mis be hav e w ith

such a lo ad. However, if two o r mor e pins pot s are connec ted to a dimmer channel, a

lamp failure in one pinspot will have n o adverse effects.

HP12-SC/HP6-C:

The SCRs used in the HP12-SC are 35 amp, 600 volt devices (type S6035K) with 2500

volt isolation to t he mounting tab. They have a surge current rat ing of 425 amps for 10

millise cond s. The d immer w ill func tio n wit h rep lacement SCRs of lower rat ings but its

ability to s urv ive shor t circuits and ove rvoltages will be jeopardised.

The SCRs used in the HP6-C are 65 amp, 600 volt devices (type S6065) with 2500 volt

isolation to the mounting tab. They have a surge current rating of 800 amps for 10

millise cond s. The d immer w ill func tio n wit h rep lacement SCRs of lower rat ings but its

ability to s urv ive shor t circuits and ove rvoltages will be jeopardised.

The SCRs are connected in back-to-back pairs, such that during each mains half-cycle

one SCR is b locking (re verse biased) and the oth er will co nduct if trigge red.

HP12-SC: The SCR gates are triggered with continuous DC (as opposed to trains of

pulses), which forces the SCRs to conduct even if the load current is lower than the SCR

latchin g curr ent. This a llows exc ellent control over small an d highly inductive load s.

The DC gate firing current for the twelve SCR pairs is provided by twelve power

os cilla to rs . T he 40kHz po wer oscillat or s o pe rat e fr o m a 1 0V reg ula te d supply, and are

contro lled by phase-control signals from the CPU.

The oscillator outputs drive pulse transformers. The two secondary (mains-side)

windings of the pulse transformers are full-wave rectified and fed to the SCR gates.

Sufficient gate current is generated to correctly trigger the SCRs at very low

temperatures (minus 10°C).

Ea ch o f the tw elve osc illat or s is pro t ec te d by a 2R7 supply resistor, such that failure in

an o s cilla t o r fu se s t he r es isto r witho u t d isr u p t ing o t h er o s c illat or s. E a ch o sc illa t o r d ra w s

8mA when inactive, and around 80mA when that channel is driven to full.

HP6-C: The SCR gates are triggered with Siemens BRT12 opto-isolators. These are

optically triggered SCRs rated at 600 volts.

Op to - tr ig g e red S C R dimme rs ha ve a low e r ab ility to correc tly drive low-powe r in d u ctiv e

loa ds tha n DC -fir ed SCR dimme rs. Alt ho ugh th is is t ru e o f t he H P6- C, ca refu l snu bbe r

design and compon ent sele ction g uarantee s th at it will correctly drive a ll loads fr om rated

maximum down to 40 watt pinspot tr ansformers.

When the lamp blows in a transformer-driven pinspot, the unloaded t ransformer primary

presents a very small, highly induct ive load. The HP6-C dimmer may misbehave with

such a lo ad. However, if two o r mor e pins pot s are connec ted to a dimmer channel, a

lamp failure in one pinspot will have n o adverse effects.

Page 22

Equipment Description 3-6

Revision 2 - 26 April, 2000 HP SERIES DIMMER TECHNICAL MANUAL

3.4 Output chokes and filtering

Th e chokes and filters minimise the emission of high frequen cy interference radiated from

dimme r outpu t wires. Th e fa s t ris ing wa ve forms produ c e d b y p h a s e - c ont ro lle d tria c s a nd

SCRs have large amounts of high frequency energy, which would be radiated as

electromagnetic interference (EMI) without the chokes.

The degree of suppression at low frequencies (150Hz - 150kHz) is indicated by the

output voltage risetime. Longer risetimes indicate superior suppression, lower acoustic

noise in lamp fila ment s and less "buzz" co upled into audio wiring.

The HP12-SC chokes have a risetime of over 500 microseconds, measured from 10% to

90% of the rising waveform edge, when driving a 2500 watt incandescent load at 90°

firing angle. The HP12-TR chokes have a risetime of 280 microseconds when measured

in the same fa shion.

The suppression at frequencies above 150kHz must meet Australian and international

standards; the HP6-C, HP12-TR and HP12-SC provide suppression superior to statut o ry

requirements.

High frequency output filtering in the dimmers is provided by capacitors (CF1 thru

CF12) connected from the SCR/triac hot input to t he choke out put. I n addition, snubber

components RS1 thru RS12 and CS1 thru CS12 serve to reduce the amplitude of

commutation transients.

NOTES: HP12-TR / HP12-SC / HP6-C

Dimme r cha nnels not dr iven o n will " leak " 50 Hz AC cur ren t t hro ugh the RF-f ilter and

snubber capacitors to their loads. The HP12-TR uses 100nF snubber and filter

ca p a c ito rs, an d w ill pass u p to 15mA to the load; t h e H P 12- SC u s e s 4 7 n F c a p a citor s a nd

will p as s up t o 7mA . T he HP 6 - C u s es 100nF snubber and filter capacitors, and will pa ss

up to 22mA to the load.

Th is c a p a c ito r c urr ent w ill h a ve n o sig nific ant e ffe c t o n load s g r eat er t h a n 20 [40 ] wa tt s ,

but may c aus e a g low (simila r to p rehe a ting ) in ve r y s ma ll pilot lamps o r slo w rot a tio n in

sma ll mo t o r s an d fa ns . S mall d imma ble flu o r es c en t a nd ne o n la mp s may no t d im t o z er o

due to this leakage.

Pr oblems cause d by capac itor cu rre nt may be lar gely e liminate d by co nnec ting a s mall

resistive or incan des cent lo ad in parallel with the des ired load.

3.5 Load & drive indicators

3.5.1 Drive LEDs

Each channel's Drive LED is connected to t he same phase-contr ol signals (generated by

the CPU) which trigger the HP12-TR's / HP6-C's opto-isolators or the HP12-SC's power

os cillat ors . The Dr ive LE D mimics t he p hase-co ntr ol drive to the tr iacs o r SC R pa irs.

The LED intensity is linearly contro lled by the duty cycle of the drive, but visually does

not appear t o be linear.

3.5.2 Load LEDs

Ea c h c h a nn e l’ s L oad L E D is c onne c ted a s a n outpu t volt a g e mimic. T he Load L E D s a re

op to -is olat ed fro m th e dimme r ou tp ut s. T he o pto -is olat o rs ar e d riven from t he o ut put s

via a 47K resistor and bridge rectifier. The "neutral retur n" from each channels' bridge

rectifier ret ur ns t o the neutral associated with that channels' phase (N1, N2 or N3).

Page 23

Equipment Description 3-7

Revision 2 - 26 April, 2000 HP SERIES DIMMER TECHNICAL MANUAL

The opto -isolators' output drives the Load LEDs via 470R resistors from the 5 vo lt rail

at up to 6mA. Although the LED current is vaguely proportional to output voltage,

visually it is not linear due to L ED and percep tual non-lin ear ities.

3.5.3 Load Detecting

Whe n no loa d is c on nec te d, the Lo ad LED will lig ht . T he snu bber a nd filt er c apa cit or s

(100nF for HP12-TR and HP6-C, 47nF for HP12-SC) will p as s a n ac c ur r e nt of 7mA t o

22mA, which is sensed by the Load LED as an output voltage.

The Load LED may be used to indicate the presence of a load only when no drive is

present, and the channel’s breaker is on. In this case, NO LOAD = LED ON;

CHANNEL LOADED = LED OFF.

When the channel is driven (as indicated by the Drive LED) the Load LED will act

simp ly as an output mimic.

Page 24

1 2 3 4 5 6 7 8

A

B

C

D

87654321

D

C

B

A

1

Jands Electronics P/L

40 Kent Rd

Mascot NSW 2020

Australia

Ph (02) 9582-0909

127-Apr-2000 11:57:37

H:\Lab\HPCE\CIRCUIT\Dimc

p

u8.sch

Title

Size: Number:

Date:File:

Revision:

Sheet of

Time:

A2

Drawn By:

CIRCUIT COMMENTS

- The DMX-512 input can be used in loop back or party line mode.

- Mains fluctuations can be compensated.

- FLASH ROM program storage.

CE1

1nF

RE5

4k7

RE4

10k

RE3

18k

RE2

39k

RE1

82k

R45

10k

Q4

BCX19

R44

10k

R42

100k

R43

100k

Q3

BCX19

1

2

3

IC15A

74HC00

C5-10,C12-14

100nF

+5

C1

10nF

C2

10nF

COM

9

1B

1

1C

16

2B

2

2C

15

3B

3

3C

14

4B

4

4C

13

5B

5

5C

12

6B

6

6C

11

7B

7

7C

10

IC9

ULN2003

R36

100R

+5

+5

C15

100nF

R12

10k

R27

4K7

+5

3

2

1

411

IC14A

LM324

+5

R38

2k2

A012A111A210A39A48A57A66A75A827A9

26

A1023A1125A124A1328A1429A15

3

CE22OE

24

D013D114D215D317D418D519D620D7

21

A162A17

30

VPP

1

IC10

27020

+5

R2

1K

R1

1K

R4

10k

R3

10k

+5

C17

10uF

+5

R26

1k

LED3

RESET

R18

22k

R16

1M

+5

RLY1

MR62

RLY2

MR62

R5

100R

+5

+5

R17

10k

10

9

8

IC14C

LM324

D0

111

A1

20

D1

110

A2

21

D2

109

A3

22

D3

108

A4

23

D4

105

A5

24

D5

104

A6

25

D6

103

A7

26

D7

102

A8

27

D8

100

A9

30

D9

99

A10

31

D10

98

A11

32

D11

97

A12

33

D12

94

A13

35

D13

93

A14

35

D14

92

A15

37

D15

91

A1638A1741A1842A19

121

A20

122

A21

123

A22

124

A23

125AS82

R/W79SIZ081SIZ1

80

BERR

70

DSACK0

89

HALT69RESET68BR

113BG114

XTAL

60

BGACK

115

IRQ177IRQ276IRQ375IRQ474IRQ573IRQ672IRQ7

71

A0

90

TP0

16

TP1

16

TP2

14

TP3

13

TP4

12

TP5

11

TP6

10

TP7

9

TP8

6

TP9

5

TP10

4

TP11

3

TP12

132

TP13

131

TP14

130

TP15

129

T2CLK

128

FC2

120

FC1

119

FC0

118

DSACK1

88

CSBOOT

112

AVEC

87

RMC

86DS85

MODCLK

78

IFETCH

55

IPIPE

54

BKPT

56

FREEZE

58

TSTME

57

EXTAL

62

XFC

64

CLKOUT

66

VDDSYN

61

MISO

43

MOSI

44

SCK

45

PCSO

46

PCS1

47

PCS2

48

PCS3

49

TXD

52

RXD

53

VSTBY

19

IC1

68332

+5

Vcc

20

Vin

1

INT

9

Vrf(-)

11

OFL

18

Vrf(+)

12

DB02DB13DB24DB3

5

CS

13

DB4

14

RD

8

DB5

15

WR/RDY

6

DB6

16

MODE

7

DB7

17

IC4

ADC0820

X013X114X215X312X41X55X62X7

4

INH6A11B10C9VEE

7

X

3

IC6

4051

+5

BATT

CR2032

+5

123

45

678

SW1

LED1

Red

LED2

Green

R24

1k

R23

1k

+5

OC

1

CLK

111D22D33D44D55D66D77D88D9

1Q192Q183Q174Q165Q156Q147Q138Q

12

IC5

74HC574

R25

1k

R37

1k

Q1

BCX19

+5

+5

CEO12CEI13VOUT

2

VCC

3

VBATT

1

RES16WDI

11

GND

4

OSC17OSC2

8

LOW

6

PFI

9

PFO

10

BAT-ON

5

/RES

15

WDO

14

IC8

MAX691

+5

R10

10k

+5

+5

A012A111A210A39A48A57A66A75A827A9

26

A1023A1125A124A1328A143A15

31

CE22OE

24

D013D114D215D317D418D519D620D7

21

A16

2

WE29CS30VCC

32

IC2

62010

A012A111A210A39A48A57A66A75A827A9

26

A1023A1125A124A1328A143A15

31

CE22OE

24

D013D114D215D317D418D519D620D7

21

A16

2

WE29CS30VCC

32

IC3

62010

R9

10k

R30

22k

R33

4k7

+5

C18

10uF

D1

HER303

L1

220mH

C3

220uF

C4

220uF

R11

10k

+5

D2

BAV21

R39

100k

+5

C11

100nF

+5

R40

2k2

R41

2k2

+5

4

5

6

IC15B

74HC00

8

9

10

IC15C

74HC00

11

12

13

IC15D

74HC00

Vin

8

GND

2

GND

3

GND

6

GND

7

Vout

1

REG2

MC78L12CG

C22

10uF

C21

10uF

Q2

BCX17

R6

1k

R8

1k

C20

100nF

D3

BAV21

+5

IC11

75176

IC12

75176

IC7

GAL16V8

+5

D4

SM4936

+5

8

(For test only)

External DAC

16,19,23,25,27

5

4

6

1

8

5

6

7

A

B

C

DXO

SZ1

SZ0

LWR

HWR

RRD

HCLCnc

RXD

CON

TXDA0RAM

COLRWAS

nc

Mux Expansion

100k

RN1

Zero cross gens

Encoder

RST

3

4(-)

5(+)

2(-)

Input

Output

DMX

1(+)

1265.82/B2

HP6/12 Dimmer CPU

Drive to Optos

BDM

CN1

Spkr

+5

Temp

gnd

Unreg

HSinA

HSinB

HSinC

Ch1

Ch2

Ch3

Ch4

Ch5

Ch6

Ch7

Ch8

Ch9

Ch10

Ch11

Ch12

Power Supply

To Power PCB

D0

C

B

A

ABC

Sns

(View from solder side)

TO FRONT PANEL CARD

WE

31

Flash Control

/28F020

4

8

231

3

2

R19

22k

R13

1M

R20

10k

12

13

14

IC14D

LM324

R29

22k

R32

4k7

R22

22k

R15

1M

R21

10k

5

6

7

IC14B

LM324

R28

22k

R31

4k7

COM

9

1B

1

1C

16

2B

2

2C

15

3B

3

3C

14

4B

4

4C

13

5B

5

5C

12

6B

6

6C

11

7B

7

7C

10

IC13

ULN2003

C24

10nF

+5

+5

R48

1k

R46

22k

R47

10k

Vin

1

Vout

2

GND

3

FB

4

ON

5

REG1

LM7526-5

+5

7

TH1

C870

TH2

C870

MOV1

1.5KE

MOV2

1.5KE

TH3

C870

TH4

C870

MOV3

1.5KE

MOV4

1.5KE

D(0..15)

A(0..18)

29-32

R7

2K2

123456789

10 11

121314151617181920

GND

2

Vcc

4

OUT

3

OSC1

16MHz

CONN5

1

1

CONN4

1

15

CONN1

C

B

A

D8D9D10

D11

D12

D13

D14

D15

D8D9D10

D11

D12

D13

D14

D15

D8

D9D10

D11D12

D13D14

D15

D0D1D2D3D4D5D6

D7

D8D9D10

D11

D12

D13

D14

D15

D8D9D10

D11

D12

D13

D14

D15

A0A1A2A3A4A5A6A7A8A9A10

A11

A12

A13

A14

A15

A16

A1A2A3A4A5A6A7A8A9

A10

A11

A12

A13

A14

A15

A16

A17

A1A2A3A4A5A6A7A8A9

A10

A11

A12

A13

A14

A15

A16

A17

GND PINS VCC PINS

2817293440515967838795101

106

117

127

128

132

171828395061576365698496

107

116

1268889

78

TP0

TP1

TP2

TP3

TP4

TP5

TP6

TP7

TP8

TP9

TP10

TP11

1

## 36

CONN2

Page 25

Equipment Description 3-8

Revision 2 - 26 April, 2000 HP SERIES DIMMER TECHNICAL MANUAL

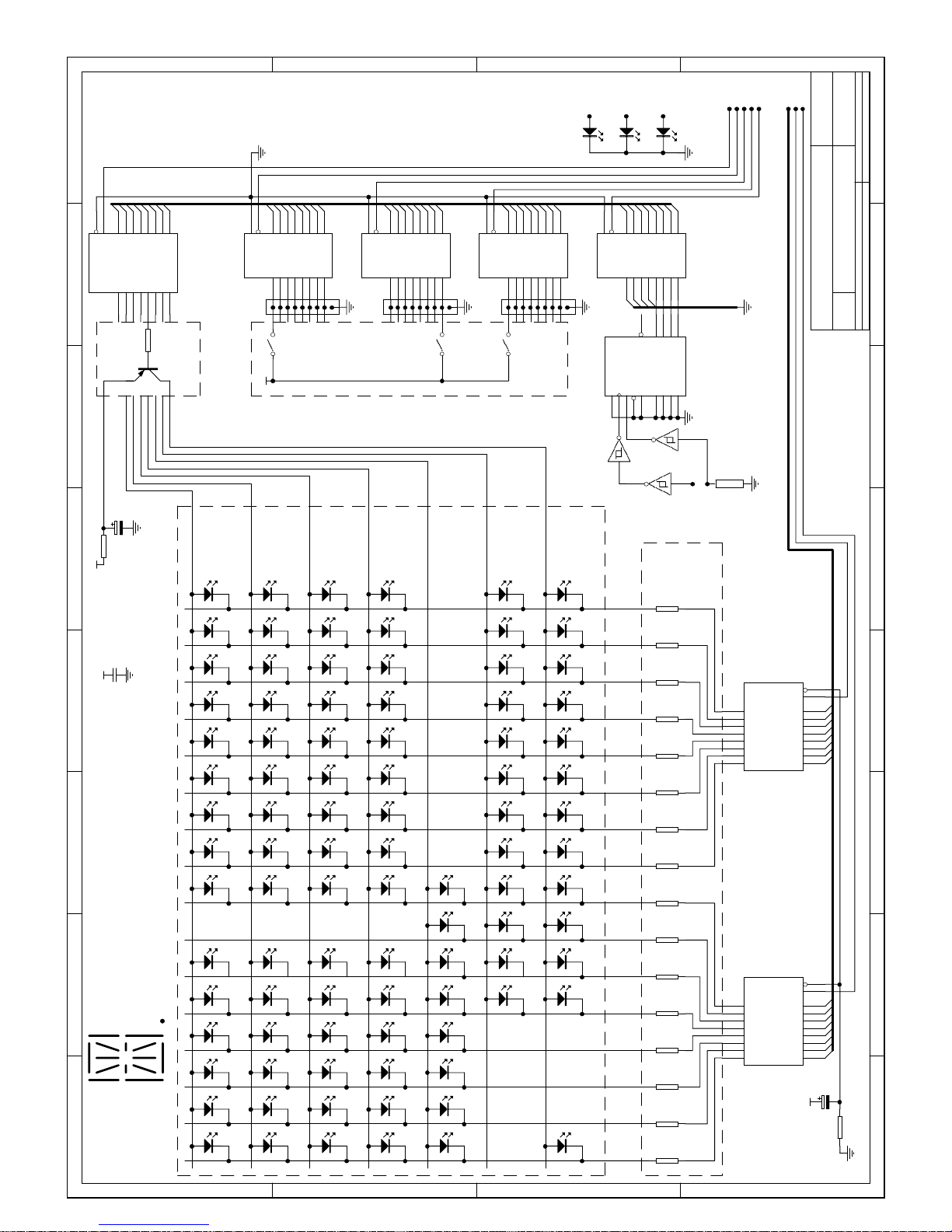

3.6 CPU card

(

Figure 3.2

The HP Series dimmers are fully digital. The CPU reads all inputs and generates all

output s. The one exception to this is the fan control system which is intended to oper ate

without CPU intervention - if the CPU were to stop operating the cooling system will

continue to op er ate normally.

Many of the components on the CPU card ar e Surface Mount, and will r eq uir e e xt r eme

care if components are t o be replaced at any stage.

The CPU is required to read the following inputs:

• the temperature sensor

• three phase voltages

• all switches

• the rotar y encoder

• the DMX input

• mains zero crossin g points

The CPU also drives the following outputs:

• all LEDs

• the DMX output

• twelve dimmer channe l opto-isolators

3.6.1 M icroprocessor

The micropro cessor (µP) is a Motoro la 68332 (IC1) housed in a 132 pin QFP surface

mount package. This is a highly integrat ed par t consisting of a 68020 core surrounded by

serial ports, a system integration module, and a time processing unit which is used to

contro l the triacs via the opt o-isolators. T he system integration module is configured to

generate chip select lines which are used to select the peripherals. The µP’s internal clock

is d erived from an external 16 M Hz c rystal oscillator (OSC1 ).

The four DIP switches (SW1) are connected directly to the unused CPU interrupt pins.

During normal operation all DIP switches should be off.

3.6.2 M em or y

The CPU memory consists of a 256Kx8 program EPROM (IC10) and two 128Kx8 static

RAMs (IC2, IC3). Program is copied from EPROM into RAM at boo t and subsequently

executed from RAM to improve execution speed. As of September 1995, the current

software version is “V1.1F”.

The EPROM may in the future be substituted with a FLASH device to allow for in-field

software upgrades. Read and Write control signals are created by a 74HC00 (IC15);

during normal operat ion the write pulses are not generated as they are only used when

the software is being uploaded into a FLASH device. Diode D2 configures the CPU at

reset to have an 8 bit boot EPROM.

Page 26

Equipment Description 3-9

Revision 2 - 26 April, 2000 HP SERIES DIMMER TECHNICAL MANUAL

Read and Write control lines for the SRAM are generated by the GAL16V8 (IC7). A

MAX691 “watchdog“ chip (IC8) supplies power to t he RAM ICs from the 5V supply

rail, but changes over to t he 3V Lithium backup battery when the 5V supply drops below

a s et level.

CAUTION

Danger of explosion if battery is incorrectly replaced.

Replace only with the same or equivalent type

recommended by the manufacturer. Dispose of used

batteri es accordin g to the ma nufac turer’s ins truct ions.

3.6.3 DMX input / output

DMX signal is received via switching relays (RLY1, RLY2) that allow the DMX t o be

t erminated or looped thro ugh. Whe n terminated, the CPU has the ability t o drive the data

output for future readback systems, however in normal operation the incoming data is

connected directly to the LOOP output.

The balanced DMX input signals are buffered and unbalanced by a 75176 (IC12) before

passing to the serial port of the µP.

3.6.4 Zero crossing detector

The zero crossing detectors synchronise CPU ramp generation to the mains supply. Each

phase transformer output is rectified, divided, and compared (IC14) with a reference

voltage generated from the +5 volt rail. The three comparator outputs should be lowgoing pulses roughly centred around t he mains zero-cr ossing point, with a 10 ms cycle

t ime.

3.6.5 Analog to digital converter (ADC)

As well as being used to generat e zero-cr ossing pulses, the three transformer secondar y

voltages are resistively divided and multiplexed into t he 8 bit A-D co nverter ADC0820

(IC4) via the 4051 analog switch (IC6). This mux is controlled by a latch 74HC574 (IC5

pins 14-19). The temperature sensor and a spare input from the Output PCB are also

connected to the mux inputs.

The ADC is read approximately every 2ms in software V1.1F, however this may change

with later software versions.

The phase voltages are compared in the µP to obtain “bad neutral” information. The

temperature sensor voltage is converted to degrees and can be displayed on the front

panel PCB.

3.6.6 Optocoupler drive

The µP directly drives 12 ULN2003 inverter buffers (IC9, IC13) which in turn drive the

BR T12 op to co up ler s or po wer os cillat o rs ( o n th e Ou tp ut PC B) to fire the t riac s/S CR s.

These signals pass down the Output card flat cable, along with the power supplies.

Page 27

Equipment Description 3-10

Revision 2 - 26 April, 2000 HP SERIES DIMMER TECHNICAL MANUAL

3.6.7 5 volt power supply

All electronic circuits other than the fan controller are run from a 5 volt supply, regulated

from the 15 V supply with a LM2576-5 switching regulator (REG1) operating as a

continuous-mode buck converter at approx 52kHz..

The demand on the 5 V rail is around 750 mA. A conventional linear regulator would

need to dissipate around 7 watts. This loss is reduced to less than 0.5 watts by using a

sw itc hing re gu lat o r . . This cir cu it is r elia ble in op er a tio n but it ma y be d ama ge d b y lon g

periods of very high mains voltage, eg. over 300Vac.

If not working, check the regulator or flyback diode D1. Note that D1 should only be

replaced with a suitable high speed flyback diode designed for use in switchmode power

supplies. Also check inductor L1 for mechanical failure.

An MC78L12CG 12 volt regulator (REG2) pro vides a supply rail for programming th e

FLASH devices. A two tr ansistor switch (Q2, Q4) controlled by IC5 pin 13 connects this

12 volt ra il to t he FL ASH de vice whe n pr og ra mming is req uir ed . I n ge ner al t his c ircu it

should not be active - it is only active during software upgrades to FLASH.

3.6.8 Reset generator

The reset generator is based around a MAX691 (IC8). This IC monitors t he +5 volt rail

and pu ts th e CP U int o re set if t he vo lt age is be low 4. 6 vo lt s. The RES ET LE D s hou ld

flash briefly when power is applied and removed, and when the RST terminals are

shorted together. IC8 also disables the SRAM via the CE pins and switches SRAM

power from the main supply to t he backup battery during power up and down. Capacitor

C17 maintains the supply to t he SRAMs during changeover - if a dimmer is d r o p p ing it s

memory and the battery is OK this capacitor may be faulty.

Th e Lit hiu m bat te ry s hou ld la st ap pr oxima t ely 5 yea rs from the date the battery was

made - note that a 4 year life from date of product sale would not be unexpected when

deliver y and manufacturing times are allowed for .

CAUTION

Danger of explosion if battery is incorrectly replaced.

Replace only with the same or equivalent type

recommended by the manufacturer. Dispose of used

batteri es accordin g to the ma nufac turer’s ins truct ions.

3.6.9 Rotary encoder

While the encoder mounts on the CPU card, most of it’s active circuitry is contained on

the front panel card. A pair of 220R/10K/10nF RC networks filter the encoder signals on

the CPU card before they are routed t o t he front panel card via the flat cable. The value

of these parts is quite critical to correct encoder operation.

Page 28

1 2 3 4 5 6 78

A

B

C

D

8

7654321

D

C

B

A

Title

Number RevisionSize

A3

Date: 27-Apr-2000 Sheet of

File: D:\R_&_D\HPDIMMER\CIRCUIT\Ledmtrx6.s01Drawn By:

C1,2,3,4,6

100nF

+5

SIG

LED24

LED23

LED22

C11

10uF

R25

1R

R18

100R

R16

100R

R15

100R

R14

100R

R11

100R

R10

100R

P04P112P213P33PE1CIN5U/D10CLK15RST

9

Q06Q111Q214Q3

2

COUT

7

IC9

4516

1213

IC8F

40106

+5

C5

10uF

R24

10k

R17

100R

Q1-Q7

BCX17

C8GC12G C11G C9G C7G C6G C5G C4G C3G C2G C1G

C8RC12R C11R C9R C7R C6R C5R C4R C3R C2R C1R

RUNCHAN MODE TEST

C10R

C10G

BLD CLR NORMBANK

N4 C4F4G4H4J4P4A4DP4M4L4K4D4E4 B4

N3 C3F3G3H3J3P3A3DP3M3L3K3D3E3 B3

N2 C2F2G2H2J2P2A2DP2M2L2K2D2E2 B2

B1E1 D1 K1 L1 M1 DP1 A1 P1 J1 H1 G1 F1 C1

1 2

IC8A

40106

R1-R7

100R

+5

+5

S1-S8

S9-S12

A02A13A24A35A46A57A68A7

9

B018B117B216B315B414B513B612B7

11

E

19

DIR

1

IC4

74HC245

A02A13A24A35A46A57A68A7

9

B018B117B216B315B414B513B612B7

11

E

19

DIR

1

IC5

74HC245

A02A13A24A35A46A57A68A7

9

B018B117B216B315B414B513B612B7

11

E

19

DIR

1

IC6

74HC245

OC

1

C

11

1D22D33D44D55D66D77D88D

9

1Q192Q183Q174Q165Q156Q147Q138Q

12

IC1

74HC574

OC

1

C

11

1D

2

2D

3

3D

4

4D

5

5D

6

6D

7

7D

8

8D

9

1Q

19

2Q

18

3Q

17

4Q

16

5Q

15

6Q

14

7Q

13

8Q

12

IC3

74HC574

OC

1

C

11

1D

2

2D

3

3D

4

4D

5

5D

6

6D

7

7D

8

8D

9

1Q

19

2Q

18

3Q

17

4Q

16

5Q

15

6Q

14

7Q

13

8Q

12

IC2

74HC574

N1

S13-S20

A02A13A24A35A46A57A68A7

9

B018B117B216B315B414B513B612B7

11

E

19

DIR

1

IC7

74HC245

3 4

IC8B

40106

R19

100R

R20

100R

R21

100R

R22

100R

R9

100R

R8

100R

R12

100R

R13

100R

R23

100R

R26

100K

Segment Layout

dp

p

n

m

l

k

j

h

gf

e

d

c

b

a

8,9,10

PHASEC

PHASEB

PHASEA

ENCB

ENCA

LCHCDATA

FC2

FC1

FC0

A19

BGACK

10K

10K

RN3

RN2

RN1

S21

22

HP Dimmer Front PCB

Channel

Channel

Normal

Clear

Run

Build

Test

Mode

Chan

Bank

spare

spare

spare

enter

ch12

ch11

ch10

ch9

ch8

ch7

ch6

ch5

ch4

ch3

ch2

ch1

Keypad

Green

Red

Digit 4

Digit 3

Digit 2

Digit 1

Drive

D.Timmins

1265.82/B4.2

JANDS

10K

6

Page 29

Equipment Description 3-11

Revision 2 - 26 April, 2000 HP SERIES DIMMER TECHNICAL MANUAL

3.7 Front panel card

(

Figure 3.4

The front panel PCB holds all front panel switches and LEDs, including the LOAD and

DRIVE LEDs which are fed by the Output PCB. Additionally, the control electronics for

the switches and LEDs and the encoder circuitry are also on the front panel PCB. To

minimise flat cable size, the CPU da ta bus and req uired CPU selec t lines are connected to

the front panel card to control the latches for the LEDs and buffers for the

switches/encoder circuitry. The majority of components on t his card are Surface Mo unt

devices.

3.7.1 Switches

The switches are read individually via tri-state 74HC245 buffers (IC4, IC5, IC6). E ach

switch when pressed (closed) pulls the buffer input high, ot herwise a 10K resistor (RN1,

RN2, RN3) pulls it to ground.

Note that switch faults will most likely be caused through wear in the switches

themselves.

3.7.2 LEDs

Due to t he large number of front panel LEDs (including the four 15 segment displays),

all except the Phase LEDs and Drive/Load LEDs are driven in a matrix, the seven rows

of which are driven by a 74HC574 latch and BCX17 transistors (IC1/Q1-7/R1-R7). T he

16 columns are driven by two 74HC574 latches (IC2-3/R8-23). T he matrix is driven with

only one row o n at any time, each row being on for approximately 2ms out of 14ms. A