Page 1

User Manual

Spark Series

SP-5000M-PMCL

SP-5000C-PMCL

5M CMOS Digital Progressive Scan

Monochrome and Color Camera

Document Version: Ver.1.1

SP-5000-PMCL_Ver.1.1_Oct2013

1046E-1305

Page 2

SP-5000M-PMCL / SP-5000C-PMCL

Notice

The material contained in this manual consists of information that is proprietary to JAI Ltd., Japan and

may only be used by the purchasers of the product. JAI Ltd., Japan makes no warranty for the use of its

product and assumes no responsibility for any errors which may appear or for damages resulting from the

use of the information contained herein. JAI Ltd., Japan reserves the right to make changes without

notice.

Company and product names mentioned in this manual are trademarks or registered trademarks of their

respective owners.

Warranty

For information about the warranty, please contact your factory representative.

Certifications

CE compliance

As defined by the Directive 2004/108/EC of the European Parliament and of the Council, EMC

(Electromagnetic compatibility), JAI Ltd., Japan declares that SP-5000M-PMCL and SP-5000C-PMCL

comply with the following provisions applying to its standards.

EN 61000-6-3 (Generic emission standard part 1)

EN 61000-6-2 (Generic immunity standard part 1)

FCC

This equipment has been tested and found to comply with the limits for a Class B digital device, pursuant

to Part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful

interference in a residential installation. This equipment generates, uses and can radiate radio

frequency energy and, if not installed and used in accordance with the instructions, may cause harmful

interference to radio communications. However, there is no guarantee that interference will not occu r

in a particular installation. If this equipment does cause harmful interference to radio or television

reception, which can be determined by turning the equipment off and on, the user is encouraged to try

to correct the interference by one or more of the following measures:

- Reorient or relocate the receiving antenna.

- Increase the separation between the equipment and receiver.

- Connect the equipment into an outlet on a circuit different from that to which the receiver is

connected.

- Consult the dealer or an experienced radio/TV technician for help.

Warning

Changes or modifications to this unit not expressly approved by the party

responsible for FCC compliance could void the user’s authority to operate the

equipment.

- 2 -

Page 3

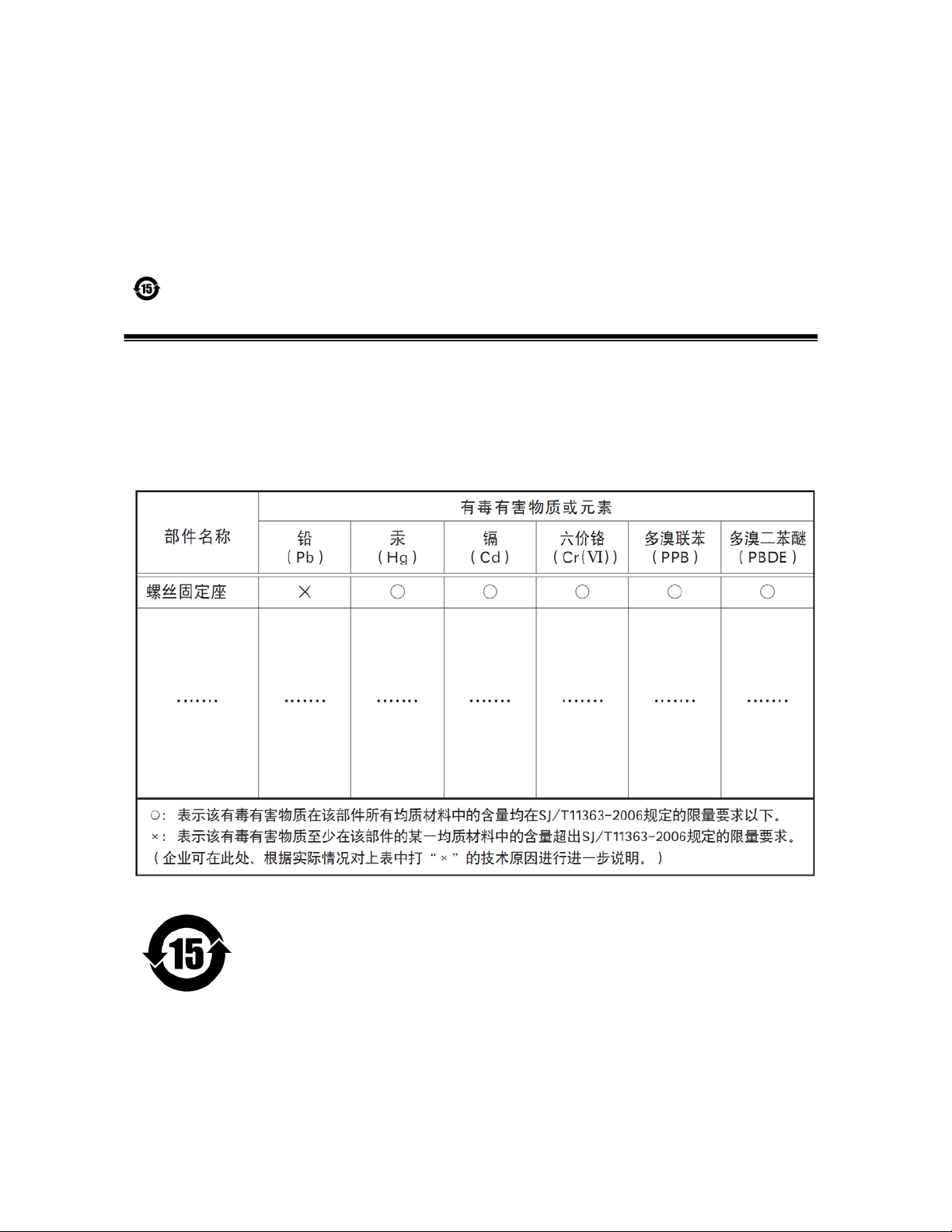

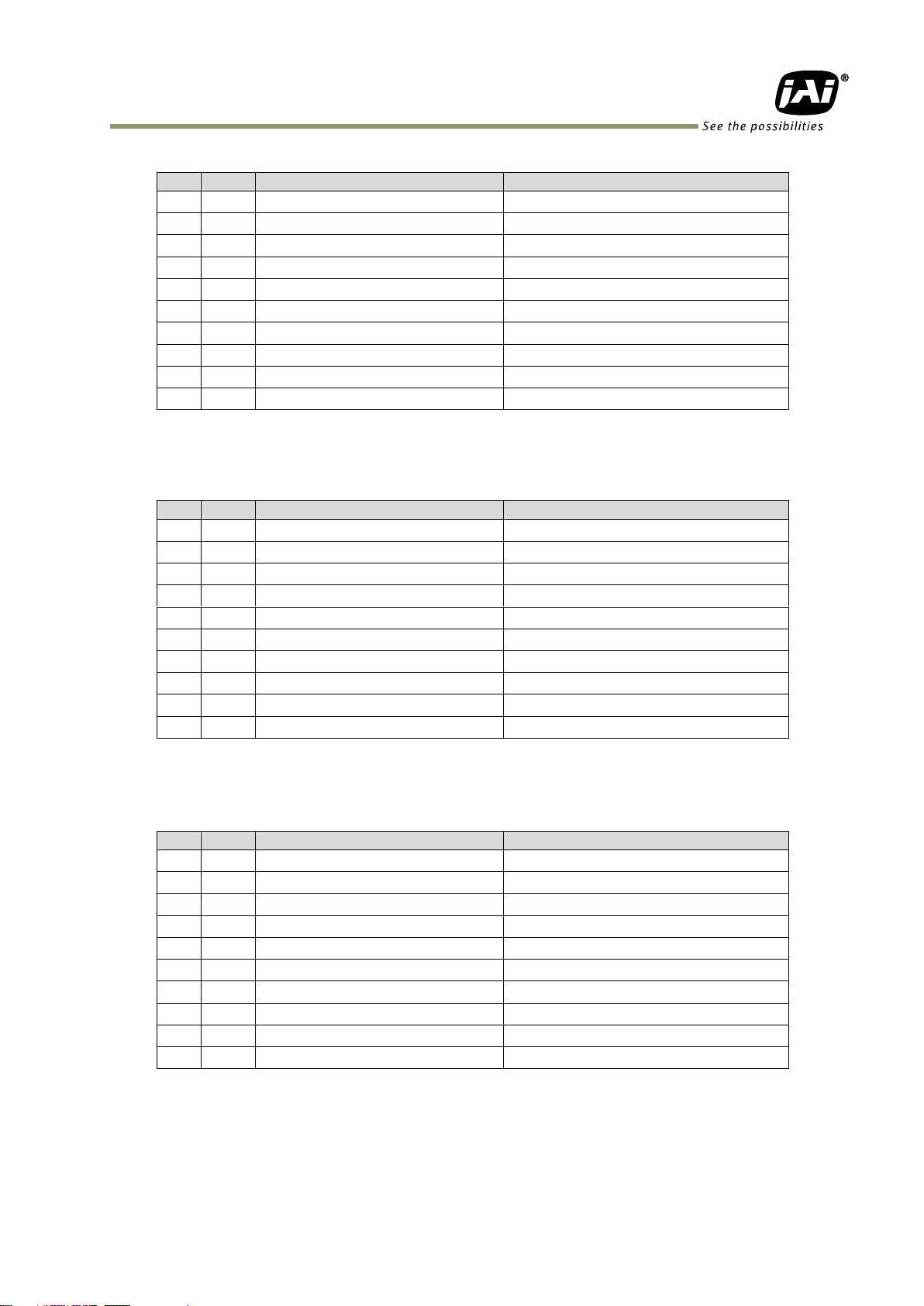

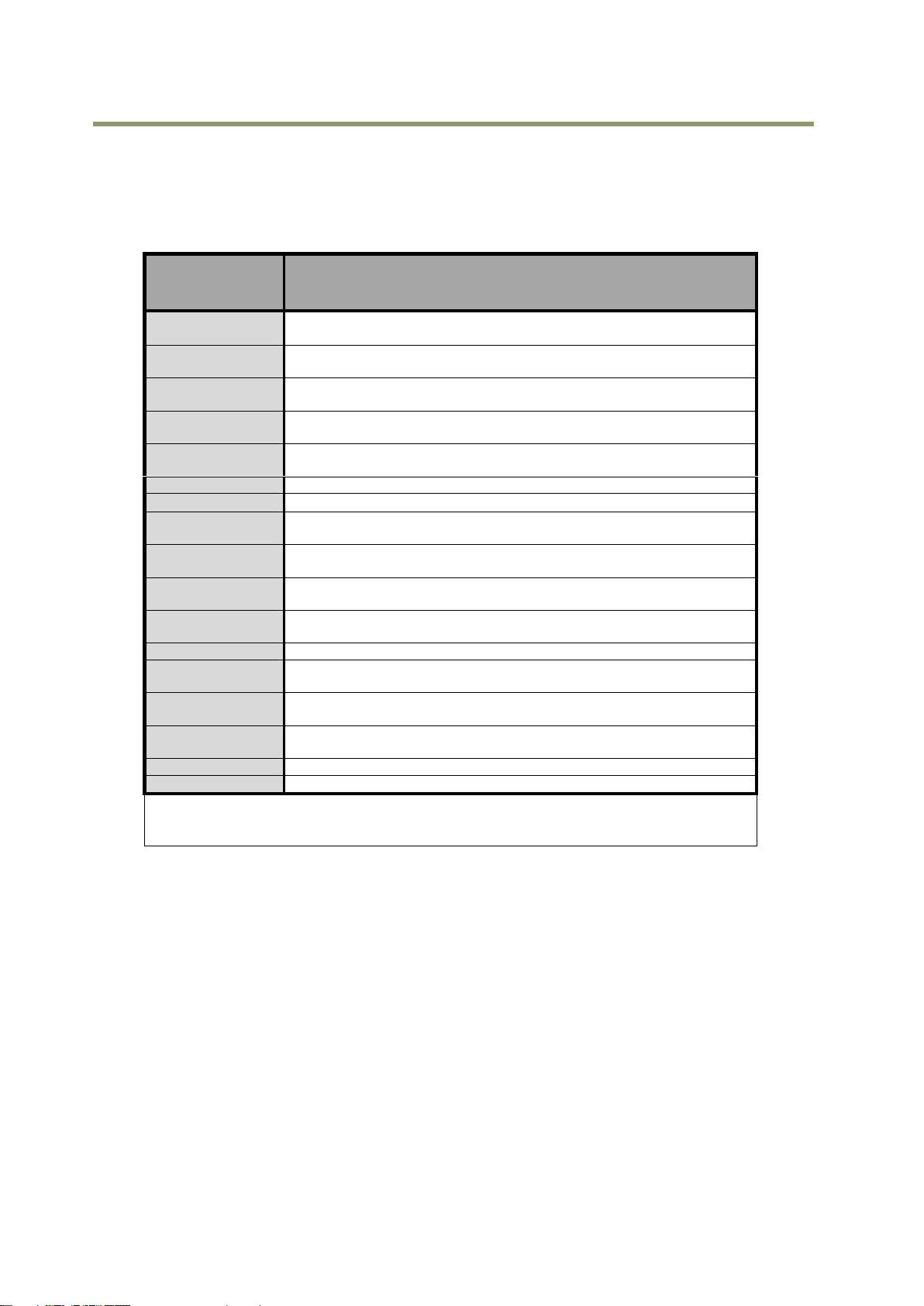

SP-5000M-PMCL

Supplement

The following statement is related to the regulation on “ Measures for the Administration

of the control of Pollution by Electronic Information Products “ , known as “ China RoHS “.

The table shows contained Hazardous Substances in this camera.

mark shows that the environment-friendly use period of contained Hazardous

Substances is 15 years.

嶷勣廣吭並㍻

嗤蕎嗤墾麗嵎賜圷殆兆各式根楚燕

功象嶄鯖繁酎慌才忽佚連恢匍何〆窮徨佚連恢瞳麟半陣崙砿尖一隈〇云恢瞳ゞ 嗤蕎嗤

墾麗嵎賜圷殆兆各式根楚燕 〃泌和

桟隠聞喘豚㍉

窮徨佚連恢瞳嶄根嗤議嗤蕎嗤墾麗嵎賜圷殆壓屎械聞喘議訳周和音氏窟伏翌

亶賜融延、窮徨佚連恢瞳喘薩聞喘乎窮徨佚連恢瞳音氏斤桟廠夛撹冢嶷麟半

賜斤児繁附、夏恢夛撹冢嶷鱒墾議豚㍉。

方忖仝15々葎豚㍉15定。

Page 4

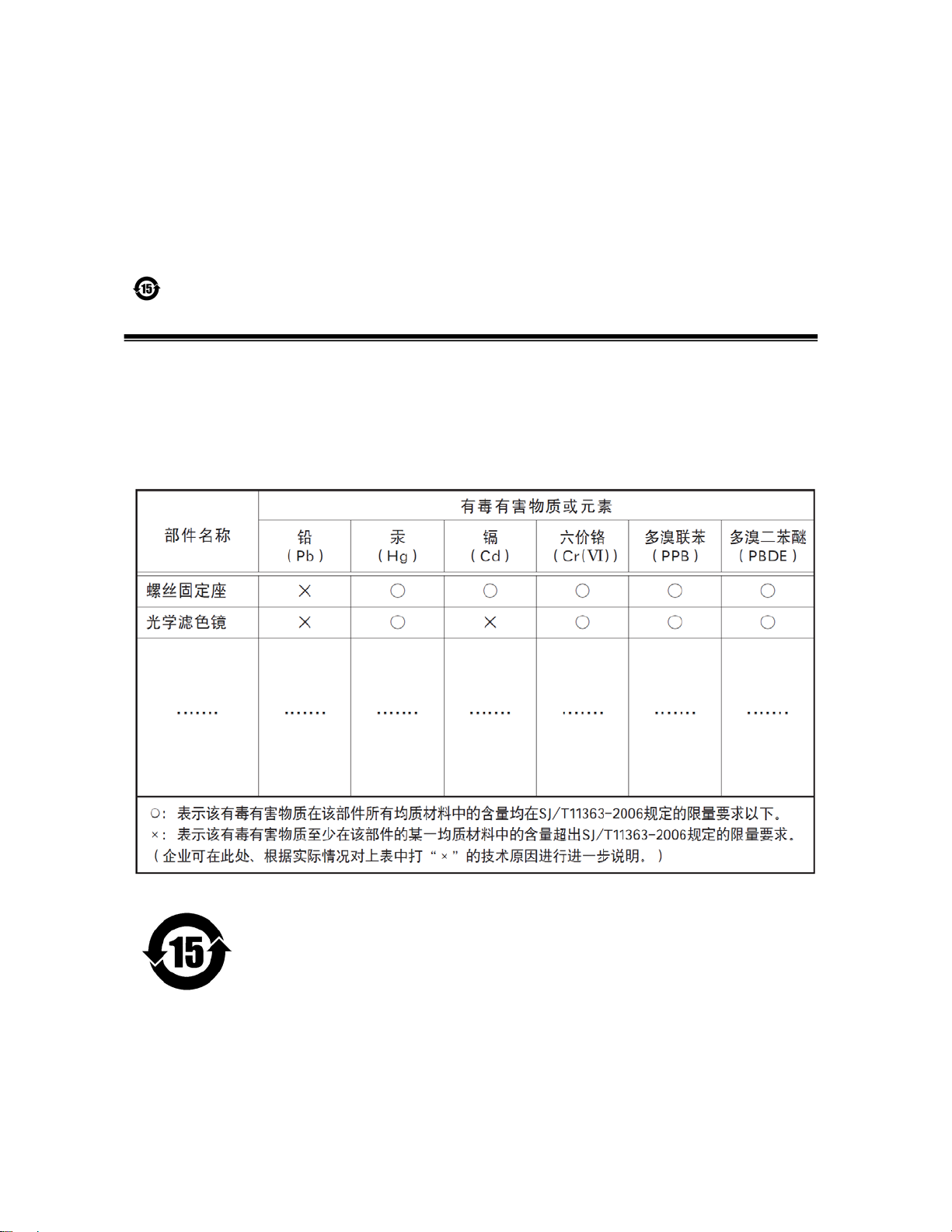

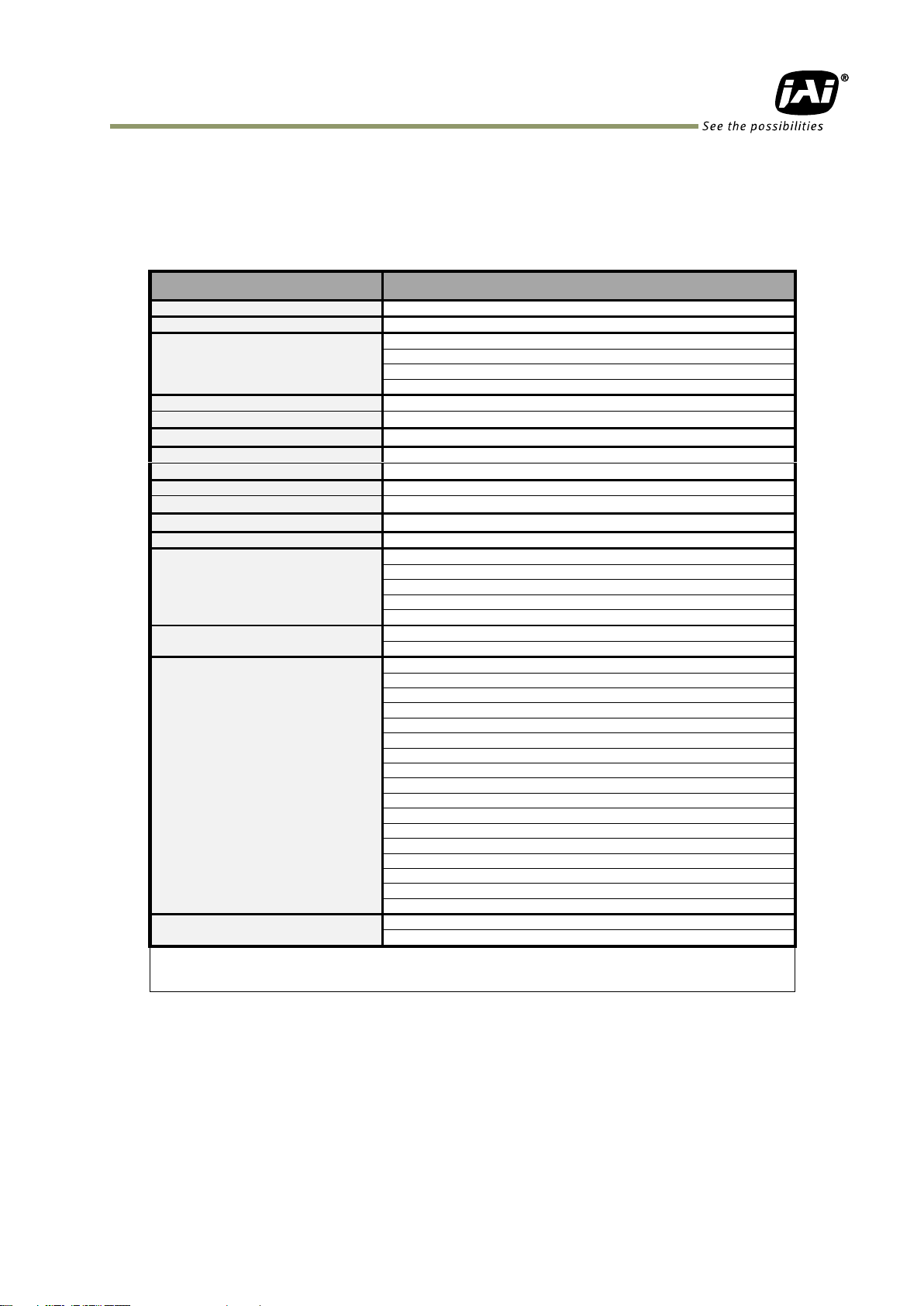

SP-5000C-PMCL

Supplement

The following statement is related to the regulation on “ Measures for the Administration

of the control of Pollution by Electronic Information Products “ , known as “ China RoHS “.

The table shows contained Hazardous Substances in this camera.

mark shows that the environment-friendly use period of contained Hazardous

Substances is 15 years.

嶷勣廣吭並㍻

嗤蕎嗤墾麗嵎賜圷殆兆各式根楚燕

功象嶄鯖繁酎慌才忽佚連恢匍何〆窮徨佚連恢瞳麟半陣崙砿尖一隈〇云恢瞳ゞ 嗤蕎嗤

墾麗嵎賜圷殆兆各式根楚燕 〃泌和

桟隠聞喘豚㍉

窮徨佚連恢瞳嶄根嗤議嗤蕎嗤墾麗嵎賜圷殆壓屎械聞喘議訳周和音氏窟伏翌

亶賜融延、窮徨佚連恢瞳喘薩聞喘乎窮徨佚連恢瞳音氏斤桟廠夛撹冢嶷麟半

賜斤児繁附、夏恢夛撹冢嶷鱒墾議豚㍉。

方忖仝15々葎豚㍉15定。

Page 5

SP-5000M-PMCL / SP-5000C-PMCL

- Contents -

Before using this camera ....................................................................- 6 -

1. General ...................................................................................- 7 -

2. Camera composition ...................................................................- 7 -

3. Key features ..............................................................................- 8 -

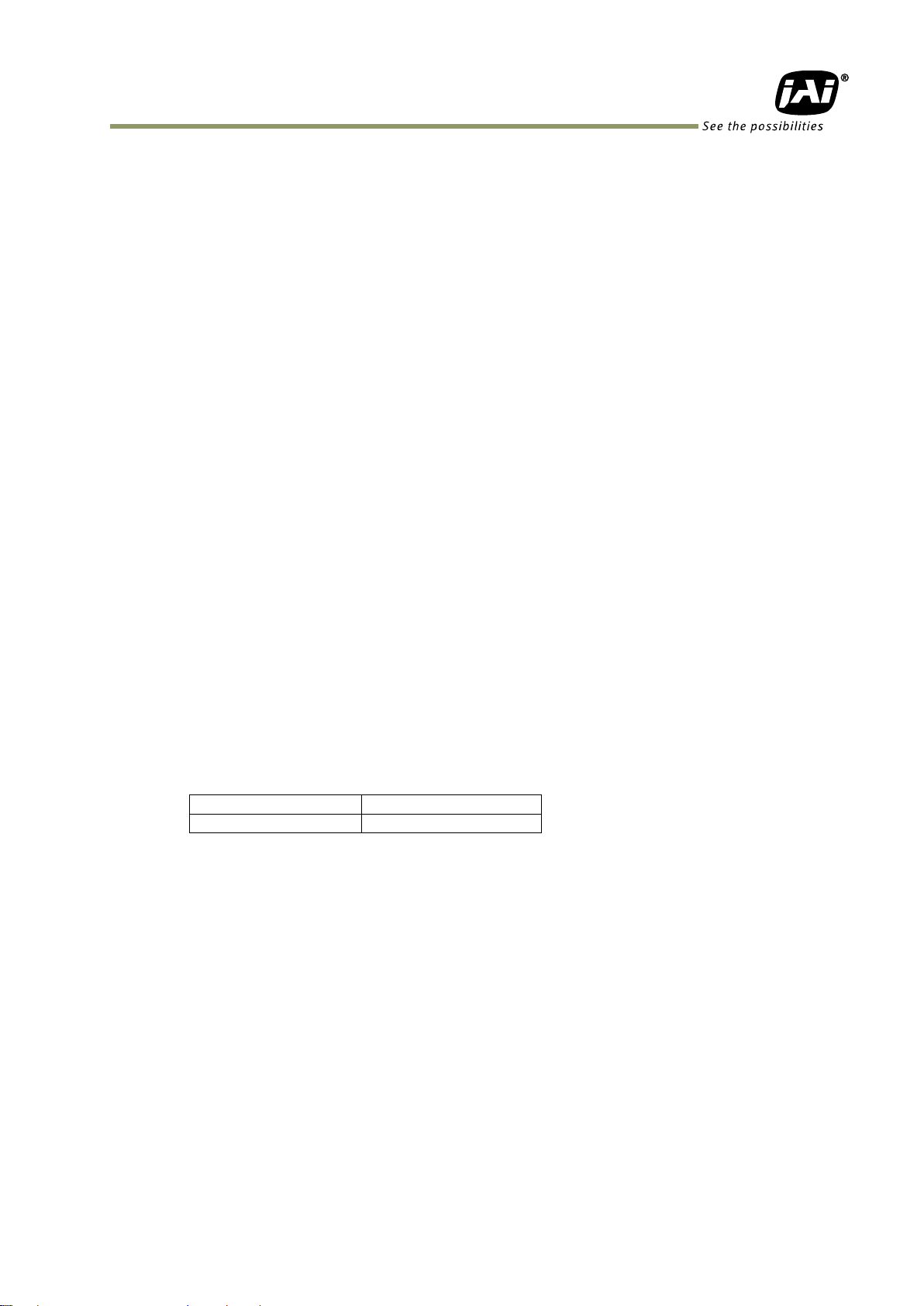

4. Parts locations and their functions ...................................................- 9 -

4.1 Parts locations and their functions ....................................................................... - 9 -

4.2 Rear Panel .................................................................................................. - 10 -

5. Input and output ......................................................................... - 11 -

5.1 Connector and its pin configuration ................................................................... - 11 -

5.1.1 12-Pin connector ..................................................................................... - 11 -

5.1.1.1 Figure ............................................................................................. - 11 -

5.1.1.2 Pin configuration ............................................................................... - 11 -

5.1.2 Camera Link Connector ............................................................................. - 11 -

5.1.2.1 Figure ............................................................................................. - 11 -

5.1.2.2 Pin assignment .................................................................................. - 12 -

5.1.3 AUX Standard Hirose 10-Pin connector ..................................................... - 12 -

5.1.3.1 Figure and pin configuration ................................................................. - 12 -

5.1.4 AUX Type 2 HIROSE 10-Pin connector (factory option) ....................................... - 13 -

5.1.5 AUX Type 3 HIROSE 10-Pin connector (factory option) ..................................... - 13 -

5.2 Camera Link interface ................................................................................... - 14 -

5.2.1 Camera Link Interface .............................................................................. - 14 -

5.2.2 Camera Link pixel clock frequency ............................................................... - 15 -

5.3 Digital IN/OUT interface ................................................................................. - 16 -

5.3.1 Line Selector ......................................................................................... - 16 -

5.3.2 Line Source ........................................................................................... - 16 -

5.3.3 Line Mode ............................................................................................. - 16 -

5.3.4 Line Inverter .......................................................................................... - 16 -

5.3.5 Line Status ............................................................................................ - 16 -

5.3.6 Line Format ........................................................................................... - 17 -

5.3.7 GPIO .................................................................................................... - 17 -

5.3.7.1 Basic block diagram ............................................................................ - 17 -

5.3.7.2 Input and output matrix table ............................................................... - 18 -

5.4 Pulse Generator ........................................................................................... - 18 -

5.4.1 Clock Pre-scaler ...................................................................................... - 19 -

5.4.2 Pulse Generator Selector ........................................................................... - 19 -

5.4.3 Pulse Generator Length ............................................................................ - 20 -

5.4.4 Pulse Generator Start Point ....................................................................... - 20 -

5.4.5 Pulse Generator End Point ......................................................................... - 20 -

5.4.6 Pulse Generator Repeat Count .................................................................... - 20 -

5.4.7 Pulse Generator Clear Activation ................................................................. - 20 -

5.4.8 Pulse Generator Clear Sync Mode ................................................................ - 20 -

5.4.9 Pulse Generator Clear Source ..................................................................... - 22 -

5.4.10 Pulse Generator Inverter ......................................................................... - 23 -

5.4.11 Pulse Generator Setting table ................................................................... - 23 -

6. Sensor layout, output format and timing ........................................ - 24 -

6.1 Sensor layout .............................................................................................. - 24 -

6.1.1 Monochrome sensor ................................................................................. - 24 -

6.1.2 Bayer sensor .......................................................................................... - 24 -

6.2 Camera output format (Tap Geometry) .............................................................. - 25 -

6.2.1 1X2–1Y ................................................................................................. - 25 -

6.2.2 1X4–1Y ................................................................................................. - 26 -

6.2.3 1X8–1Y ................................................................................................. - 26 -

- 3 -

Page 6

SP-5000M-PMCL / SP-5000C-PMCL

6.3 Output timing and output image ....................................................................... - 27 -

6.3.1 Horizontal timing .................................................................................... - 27 -

6.3.2 Vertical timing ....................................................................................... - 35 -

Table 28. Continuous Trigger / Vertical timing 1X4–1Y (2/3) ................................... - 40 -

Camera Settings .................................................................................................. - 40 -

Table 29. Continuous Trigger / Vertical timing 1X2–1Y (3/3) .................................... - 41 -

Camera Settings .................................................................................................. - 41 -

6.3.3 ROI (Region Of Interest) setting .................................................................. - 41 -

6.4 Digital output bit allocation ............................................................................ - 42 -

7. Operating modes ...................................................................... - 43 -

7.1. Acquisition control (change the frame rate) ........................................................ - 43 -

7.1.1 Acquisition control .................................................................................. - 43 -

7.2. Exposure setting ......................................................................................... - 47 -

7.2.1 Mode ................................................................................................... - 47 -

7.2.2 ExposureTime ........................................................................................ - 47 -

7.2.3 ExposureAuto ......................................................................................... - 48 -

7.3. Trigger control ........................................................................................... - 48 -

7.3.1 Trigger Selector ...................................................................................... - 48 -

7.3.2 Trigger Mode ......................................................................................... - 48 -

7.3.3 TriggerSource ........................................................................................ - 48 -

7.3.4 TriggerActivation .................................................................................... - 49 -

7.3.5 Triggeroverlap ....................................................................................... - 49 -

7.4. Normal continuous operation (Timed Exposure Mode/Trigger Mode OFF)..................... - 49 -

7.5. Timed mode (EPS operation) .......................................................................... - 49 -

7.5.1 If Overlap setting is OFF ............................................................................ - 50 -

7.5.2 If Overlap setting is Readout ...................................................................... - 50 -

7.6 Trigger width mode (PWC) .............................................................................. - 51 -

7.6.1 If Overlap setting is OFF ............................................................................ - 51 -

7.6.2 If Overlap setting is Readout ...................................................................... - 52 -

7.7. RCT mode ................................................................................................. - 53 -

7.8 PIV (Particle Image Velocimetry) ...................................................................... - 54 -

7.9 Sequence Mode ............................................................................................ - 55 -

7.9.1 Video send mode .................................................................................... - 55 -

7.9.2 Sequence mode ...................................................................................... - 55 -

7.9.3 Sequence mode timing ............................................................................. - 55 -

7.9.4 Sequence ROI setting parameters ................................................................ - 56 -

7.10 Multi ROI function ....................................................................................... - 58 -

7.10.1 Multi ROI setting parameters .................................................................... - 58 -

7.11. Operation and function matrix ....................................................................... - 61 -

Exposure ...................................................................................................... - 61 -

8. Other functions ....................................................................... - 62 -

8.1 Black level control ........................................................................................ - 62 -

8.1.1 Black Level Selector ................................................................................ - 62 -

8.1.2 Black Level ............................................................................................ - 62 -

8.2 Gain control ................................................................................................ - 62 -

8.2.1 Gain Selector ......................................................................................... - 63 -

8.2.2 Gain .................................................................................................... - 63 -

8.2.3 Gain Raw .............................................................................................. - 63 -

8.2.4 Gain Auto ............................................................................................. - 63 -

8.3. LUT ......................................................................................................... - 64 -

8.3.1 LUT Enable ............................................................................................ - 64 -

8.3.2 LUT Index ............................................................................................. - 64 -

8.3.3 LUT Value ............................................................................................. - 64 -

8.4 Gamma...................................................................................................... - 65 -

8.5 Shading Correction ....................................................................................... - 65 -

8.6 Blemish compensation ................................................................................... - 66 -

- 4 -

Page 7

SP-5000M-PMCL / SP-5000C-PMCL

8.7 ALC .......................................................................................................... - 67 -

8.8 HDR (High Dynamic Range) (SP-5000M-PMCL only).................................................. - 67 -

8.9. Lens ........................................................................................................ - 68 -

8.9.1 About P-Iris ........................................................................................ - 69 -

8.9.2 Setting for P-iris lens being used ................................................................. - 69 -

8.9.2.1 P-Iris lens select ................................................................................ - 69 -

8.9.2.2 Step max. ........................................................................................ - 69 -

8.9.2.3 Position ........................................................................................... - 69 -

8.9.2.4 Current F value ................................................................................. - 69 -

8.9.2.5 P-Iris Auto min. / P-Iris Auto max. .......................................................... - 69 -

8.9.3 Motorized lens ........................................................................................ - 69 -

8.9.3.1 Iris ................................................................................................. - 69 -

8.9.3.2 Zoom .............................................................................................. - 70 -

8.9.3.3 Focus+ ............................................................................................ - 70 -

9. Camera control ......................................................................... - 71 -

10. External appearance and dimensions ......................................... - 72 -

11. Specifications ........................................................................ - 73 -

11.1. Camera spectral response ............................................................................ - 73 -

11.2. Specification table ..................................................................................... - 74 -

Appendix 1 Short ASCII Command Communication Protocol ................ - 77 -

1 Communication setting ................................................................ - 77 -

2 Protocol(Short ASCII Command) ............................................... - 77 -

2.1 Transmit the setting command to camera ........................................................... - 77 -

2.2 Transmit the request command to camera .......................................................... - 77 -

2.3 Switching baud rate between PC and camera ....................................................... - 77 -

2.4 Command list (Short ASCII command) ................................................................. - 78 -

2.4.1 GenCP Bootstrap Register .......................................................................... - 78 -

2.4.2 Technology Specific Bootstra Register ........................................................... - 78 -

2.4.3 Device Control ....................................................................................... - 79 -

2.4.4 Image Format Control .............................................................................. - 79 -

2.4.5 Acquisition Control .................................................................................. - 80 -

2.4.6 Digital I/O Control ................................................................................... - 81 -

2.4.7 Analogue Control .................................................................................... - 82 -

2.4.8 LUT Control ........................................................................................... - 82 -

2.4.9 Transport Layer Control ............................................................................ - 83 -

2.4.10 User Set Control .................................................................................... - 83 -

2.4.11 JAI-Custom .......................................................................................... - 83 -

Appendix 2 ................................................................................. - 101 -

1. Precautions .................................................................................................. - 101 -

2. Typical Sensor Characteristics............................................................................ - 101 -

3. Caution when mounting a lens on the camera ........................................................ - 101 -

4. Caution when mounting the camera .................................................................... - 101 -

5. Exportation .................................................................................................. - 102 -

6. References ................................................................................................... - 102 -

Manual change history ................................................................... - 103 -

User's Record .............................................................................. - 104 -

- 5 -

Page 8

SP-5000M-PMCL / SP-5000C-PMCL

Before using this camera

EMVA 1288

With regard to signal to noise ratio in this manual, specifications measured by EMVA 1288 are used

together with specifications by a traditional measurement method.

EMVA 1288 is a more complete measurement that considers multiple noise sources, including random

noise, pattern noise, and shading. Additionally, EMVA 1288 incorporates temporal variances in pixel

output by capturing 100 frames of data and computing the RMS variations over the captured frames.

Because of the comprehensive nature of the noise analysis and the additional consideration for RMS

variances over time, EMVA 1288 SNR measurements are inherently lower than the traditional SNR

measurements given by manufacturers. However, the comprehensive nature combined with rigid test

parameters, means that all manufacturers’ are measuring their products equally and EMVA 1288 tested

parameters can be compared among different manufacturers’ products.

In order to learn more about EMVA 1288, please visit http://www.emva.org

Frame grabber board

The SP-5000M-PMCL and SP-5000C-PMCL comply with “Power over Camera Link” which enables power to

be supplied to the camera through the Camera Link cable(s). Because the power requirements of the

camera exceed the amount of power which can be provided over a single PoCL connection, power must

be supplied via both Camera Link cables in order to utilize the PoCL capabilities. If you plan to use this

function, please be sure that the frame grabber board you are using also complies with this specification.

Alternatively, the camera can be powered via a separate power supply connected to the 12-pin Hirose

connector.

The SP-5000M-PMCL and SP-5000C-PMCL employ output formats which comply with the GenICam

standard. They are 1X10–1Y (10-Tap output), 1X8-1Y (8-Tap output), 1X4–1Y (4-Tap output) and 1X2–1Y

(2-Tap output). 1X10–1Y is available for 8-bit output, 1X8–1Y is available for 8-bit and 10-bit output,

and 1X4-1Y and 1X2–1Y are available for 8-bit, 10-bit and 12-bit output. Please check if the frame

grabber used in the system complies with the mentioned formats.

Ⓡ

Camera control tool

The SP-5000M-PMCL and SP-5000C-PMCL are designed to use the JAI SDK and Control Tool software to

control camera functions. All controllable functions are stored in the camera’s XML file. The JAI SDK can

be downloaded from www.jai.com .

A camera control tool for using the Short ASCII command protocol is not available on the JAI website.

Please contact your local JAI representative if this is required.

- 6 -

Page 9

SP-5000M-PMCL / SP-5000C-PMCL

Tripod base

MP-42

Power supply unit

PD-12 series

1. General

The SP-5000M-PMCL and SP-5000C-PMCL are among the first new “Spark Series” cameras to be

introduced. They provide both high resolution and a high frame rate with excellent image quality for

machine vision applications. The SP-5000M-PMCL is a monochrome progressive scan COMS camera and

the SP-5000C-PMCL is the equivalent Bayer mosaic progressive scan CMOS camera. Both are equipped

with CMOS sensors offering a 1-inch image format, a resolution of 5 million pixels, and a 5:4 aspect ratio.

They provide a maximum of 134 frames per second for continuous scanning with 2560 x 2048 full pixel

resolution in 1x10–1Y output format.

8-bit, 10-bit or 12-bit output can be selected for both monochrome and raw Bayer formats. The new

cameras feature a Mini Camera Link interface supporting a “Power over Camera Link” capability. A full

pixel readout or partial scan readout mode can be selected depending on applications. The readout

format is available for 10-tap, 8-tap, 4-tap or 2-tap output.

The SP-5000M-PMCL and SP-5000C-PMCL have various comprehensive functions needed for automated

optical inspection applications, such as solid state device inspection or material surface inspection. They

incorporate video processing functions such as a look-up table, flat field shading compensation and

blemish compensation in addition to fundamental functions such as trigger, exposure setting and video

level control.

The latest version of this manual can be downloaded from: www.jai.com

The latest version of the JAI SDK for the SP-5000M-PMCL and SP-5000C-PMCL can be downloaded from:

www.jai.com

For camera revision history, please contact your local JAI distributor.

2. Camera composition

The standard camera composition is as follows.

Camera body 1

Sensor protection cap 1

Dear Customer (sheet) 1

The following optional accessories are available.

- 7 -

Page 10

SP-5000M-PMCL / SP-5000C-PMCL

3. Key features

New Spark Series 1-inch CMOS 5-megapixel progressive scan camera

Utilizes Mini Camera Link interface in Medium or Full configurations

Aspect ratio 5:4, 2560 (H) x 2048 (V) - 5 million effective pixels

5 μm square pixels

S/N 55dB for monochrome and 53dB for color (traditional measurement method)

8-bit, 10-bit or 12-bit output for monochrome and Bayer

134 frames/second with full resolution in continuous operation for 10-tap output,

120 frames/second for 8-tap output

Supports ROI (Region Of Interest) modes for faster frame rate

0dB to +24dB gain control for both SP-5000M-PMCL and SP-5000C-PMCL

10 μs (1/100,000) to 8 seconds exposure control in 1 μs step

Auto exposure control

Timed and trigger width exposure control

RCT and PIV trigger modes for specific applications

ALC control with combined function of AGC, Auto Shutter and Auto Iris

Various pre-processing circuits are provided

Programmable LUT

Gamma correction from 0.45 to 1.0

Shading correction

Bayer white balance with manual or one-push auto (SP-5000C-PMCL only)

Blemish compensation

HDR (High Dynamic Range) function (SP-5000M-PMCL only)

Auto iris lens video output with H-sync

New Hirose 10P connector for motorized lenses and P-iris lens control as standard and video/DC

iris or TTL IN and OUT and LVDS IN interfaces as options

C-mount for lens mount

Accepts power over Mini Camera Link or via 12-pin connector

Setup by Windows XP/Vista/7/8 via serial communication

- 8 -

Page 11

SP-5000M-PMCL / SP-5000C-PMCL

4. Parts locations and their functions

4.1 Parts locations and their functions

Lens mount C-mount (Note *1)

10-pin connector AUX interface connector

LED Indication for power and trigger input

12-pin connector DC+12V and trigger input

Camera Link Connector 2 Digital video output (Medium and Full configuration) (Note *2)

Camera Link Connector 1 Digital video output (Base, Medium and Full config.) (Note *2)

Mounting holes M3 depth 5mm for fixing the camera to the tripod base or

direct installation (Note *3)

*1) Note: Rear protrusion on C-mount lens must be less than 10.0 mm.

*2) Note: When a Camera Link cable is connected to the camera, please do not excessively tighten

screws by using a driver. The Camera Link receptacle on the camera might be damaged.

For security, the strength to tighten screws is less than 0.147 Newton meter (Nm).

Tightening by hand is sufficient in order to achieve this.

*3) Note: The part number for the tripod adapter plate (with 1/4"-20 thread) is MP-42 (option).

Fig. 1 Locations

- 9 -

Page 12

SP-5000M-PMCL / SP-5000C-PMCL

4.2 Rear Panel

The rear panel mounted LED provides the following information:

Amber: Power connected – initiating

This light goes OFF after initiating.

Steady green: Camera is operating in Continuous mode

Flashing green: The camera is receiving external triggering

Note: The interval of flashing does not correspond with external

trigger duration.

Fig. 2 Rear panel

- 10 -

Page 13

SP-5000M-PMCL / SP-5000C-PMCL

1

14

13

26

Pin no.

Signal

Remarks 1 GND

2

DC input

+12V ~ +24V (note 3)

3

GND

4

Video Iris

Video signal output for lens auto iris

5

NC

6

NC

7

NC

8

NC

9

TTL out 1

Line1 (note 1)

10

TTL In 1

Line4 (note 2)

11

DC input

+12V ~ +24V (note 3)

12

GND

Fig.3 Hirose 12-pin connector

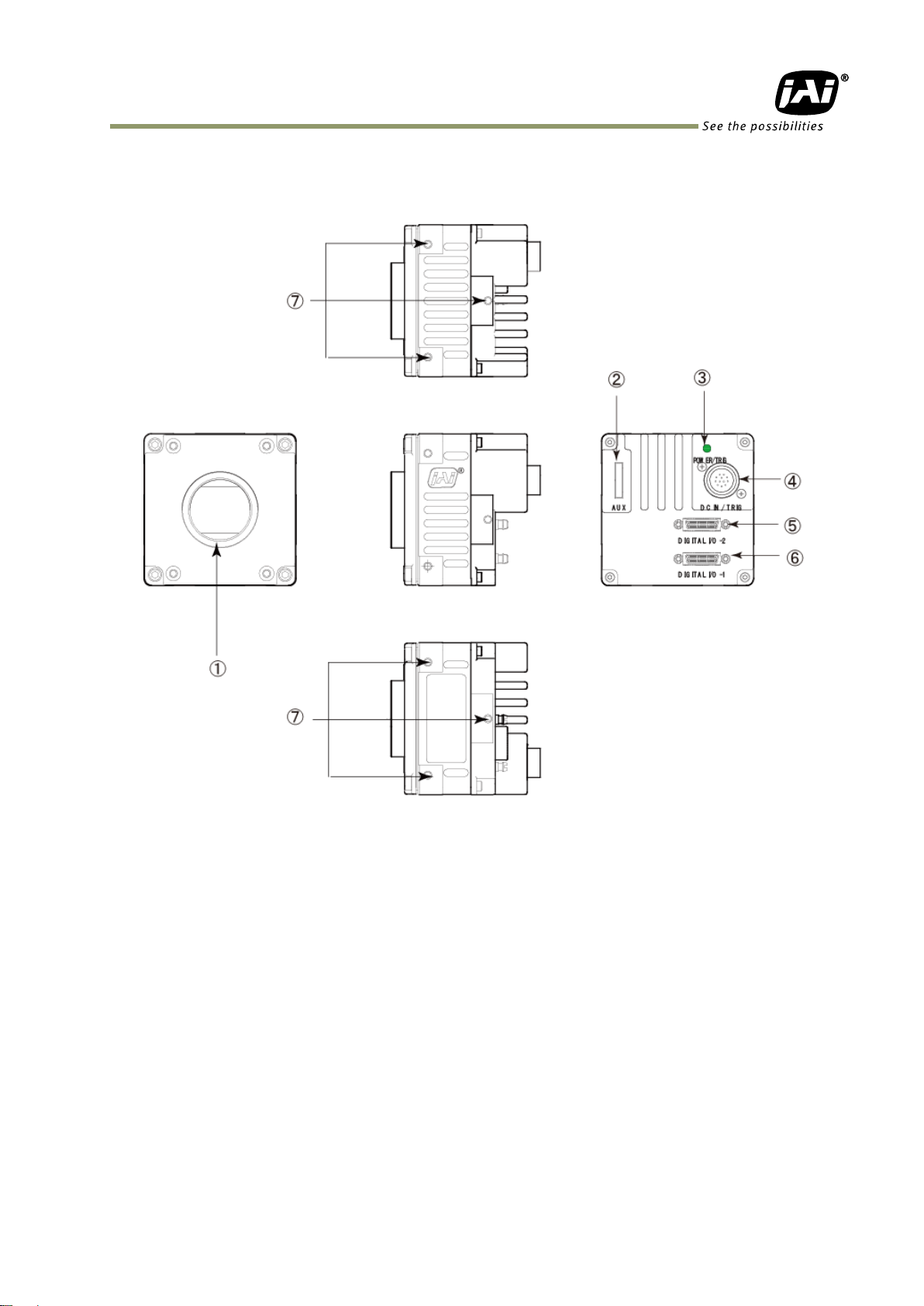

5. Input and output

5.1 Connector and its pin configuration

5.1.1 12-Pin connector

5.1.1.1 Figure

Type: HR-10A-10R-12PB(72) Hirose male or equivalent

5.1.1.2 Pin configuration

Table 1 12-pin configuration

Note 1) Factory default setting is Exposure Active and negative

Exposure Active inside the camera is positive but for the output, it is inverted to negative.

Note 2) Factory default setting is trigger input.

Note 3) See page 6 for notes about power options for these cameras

5.1.2 Camera Link Connector

5.1.2.1 Figure

Type: 26-pin Mini Camera Link connector (Honda HDR-EC26FYTG2-SL+) See page 6 for notes about Power

over Camera Link (PoCL) options for this camera.

Fig.4 Camera Link connector

- 11 -

Page 14

SP-5000M-PMCL / SP-5000C-PMCL

Pin No

In/Out

Name

Note

1,26 Power

Power

2(-),15(+)

O

X_OUT0

Data output

3(-),16(+)

O

X_OUT1

4(-),17(+)

O

X_OUT2

5(-),18(+)

O

X_Clk

Clock for CL

6(-),19(+)

O

X_OUT3

Data output

7(+),20(-)

I

SerTC (RxD)

LVDS serial control

8(-),21(+)

O

SerTFG (TxD)

9(-),22(+)

I

CC1 (Trigger)

Trigger input

10(+),23(-)

CC1 (Reserved)

11,24 N.C

12,25 N.C

13,14

Shield

Power Return

Pin No

In/Out

Name

Note

1,26 Power

Power

2(-),15(+)

O

Y_OUT0

Data output

3(-),16(+)

O

Y_OUT1

4(-),17(+)

O

Y_OUT2

5(-),18(+)

O

Y_Clk

Clock for CL

6(-),19(+)

O

Y_OUT3

Data output

7(+),20(-)

I

N.C

8(-),21(+)

O

Z_OUT0

Data output

9(-),22(+)

I

Z_OUT1

10(+),23(-)

Z_OUT2

11,24

Z_Clk

Clock for CL

12,25

Z_OUT3

Data output

13,14

Shield

Power Return

1

8

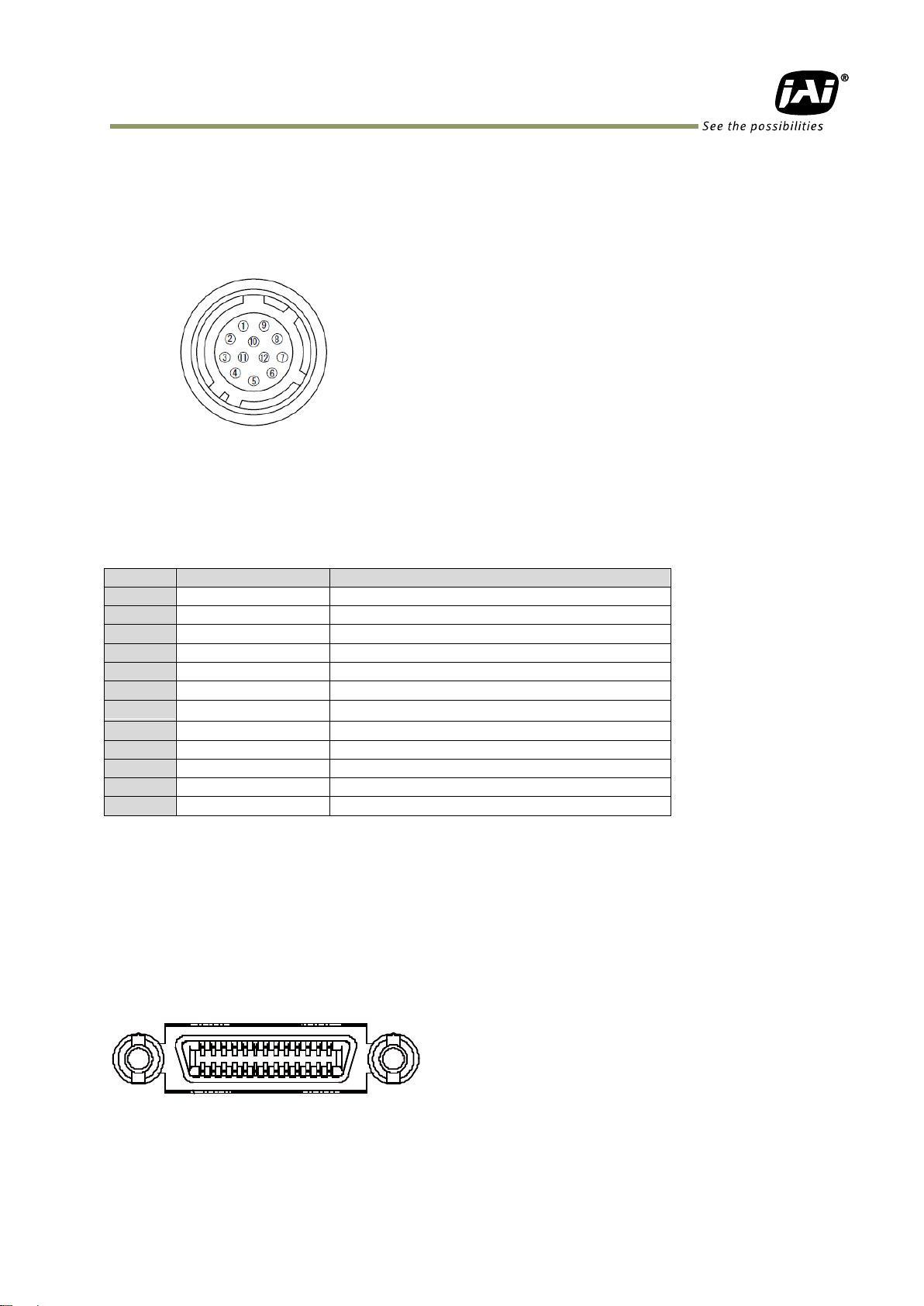

5.1.2.2 Pin assignment

Table-2 Camera link pin configuration – connector 1

Camera Link connector 2

5.1.3 AUX Standard Hirose 10-Pin connector

5.1.3.1 Figure and pin configuration

Type : HIROSE 10-Pin Connector 3260-10S3(55)

Fig.5 Hirose 10-pin connector

- 12 -

Page 15

SP-5000M-PMCL / SP-5000C-PMCL

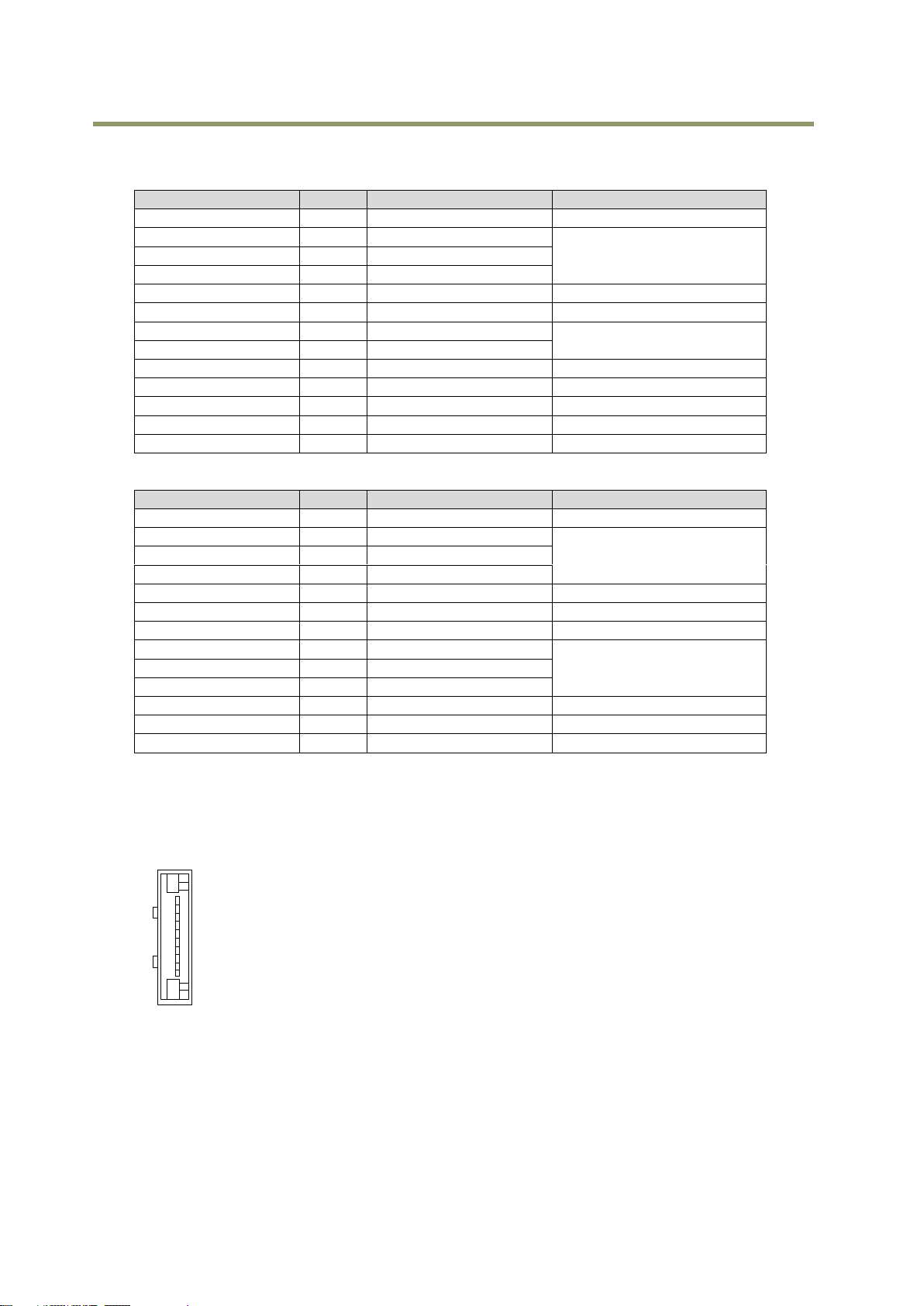

No

I/O

Name

Note

1

O

DRIVE IRIS+

Motorized Lens

2

O

DRIVE FOCUS+

Motorized Lens

3

O

DRIVE ZOOM+

Motorized Lens

4

O

COMMON

Motorized Lens

5

GND

6 O

P-IRIS OUT1A

P-Iris Lens

7

O

P-IRIS OUT1B

P-Iris Lens

8

O

P-IRIS OUT2A

P-Iris Lens

9

O

P-IRIS OUT2B

P-Iris Lens

10

O

GND

No

I/O

Name

Note

1

O

Video Signal

Video Iris Lens

2

O

Power DC+12V

Video Iris Lens

3

NC

4

NC

5

GND

6

O

DC IRIS DAMP-

DC Iris

7

O

DC IRIS DAMP+

DC Iris

8

O

DC IRIS DRIVE+

DC Iris

9

O

DC IRIS DRIVE-

DC Iris

10

GND

No

I/O

Name

Note

1

O

TTL OUT2

Line8 2 O

TTL OUT3

Line9

3

I

TTL_IN2

Line10

4

NC

5

GND

6 I

LVDS_IN1+

Line11

7

I

LVDS_IN1-

8

NC

9

GND

10

GND

Table -3 AUX Standard Hirose 10-pin connector pin assignment

5.1.4 AUX Type 2 HIROSE 10-Pin connector (factory option)

Type: HIROSE 10-Pin Connector 3260-10S3(55)

Table-4 10-pin pin configuration (option)

5.1.5 AUX Type 3 HIROSE 10-Pin connector (factory option)

HIROSE 10-Pin Connector 3260-10S3(55)

Table – 5 10-pin pin configuration (option)

- 13 -

Page 16

SP-5000M-PMCL / SP-5000C-PMCL

Base Medium Full 80bit Full

2Tap / 12bit 4Tap / 12bit 8 Tap / 8b it 8 Tap / 10b it 10 Tap / 8 bit

1X2 - 1Y 1X4 - 1Y 1x8 - 1Y 1X 8 - 1Y 1X10 - 1Y

Port A0 TxIN 0 Tap1 D0 Tap 1 D0 Tap 1 D0 Tap 1 D2 Tap 1 D0

Port A1 TxIN 1 Tap1 D1 Tap 1 D1 Tap 1 D1 Tap 1 D3 Tap 1 D1

Port A2 TxIN 2 Tap1 D2 Tap 1 D2 Tap 1 D2 Tap 1 D4 Tap 1 D2

Port A3 TxIN 3 Tap1 D3 Tap 1 D3 Tap 1 D3 Tap 1 D5 Tap 1 D3

Port A4 TxIN 4 Tap1 D4 Tap 1 D4 Tap 1 D4 Tap 1 D6 Tap 1 D4

Port A5 TxIN 6 Tap1 D5 Tap 1 D5 Tap 1 D5 Tap 1 D7 Tap 1 D6

Port A6 TxIN 27 Tap1 D6 Tap 1 D6 Tap 1 D6 Tap 1 D8 T ap 4 D1

Port A7 TxIN 5 Tap1 D7 Tap 1 D7 Tap 1 D7 Tap 1 D9 Tap 1 D5

Port B0 TxIN 7 Tap1 D8 Tap 1 D8 Tap 2 D0 Tap 2 D2 T ap 1 D7

Port B1 TxIN 8 Tap1 D9 Tap 1 D9 Tap 2 D1 Tap 2 D3 T ap 2 D0

Port B2 TxIN 9 Tap1 D10 Tap 1 D10 T ap 2 D2 Tap 2 D4 Tap 2 D1

Port B3 TxIN 12 Tap1 D11 Tap 1 D11 Tap 2 D3 T ap 2 D5 Tap 2 D4

Port B4 TxIN 13 Tap2 D8 T ap 2 D8 Tap 2 D4 Tap 2 D6 Tap 2 D5

Port B5 TxIN 14 Tap2 D9 T ap 2 D9 Tap 2 D5 Tap 2 D7 Tap 2 D6

Port B6 TxIN 10 Tap2 D10 Tap 2 D10 Tap 2 D6 T ap 2 D8 Tap 2 D2

Port B7 TxIN 11 Tap2 D11 Tap 2 D11 Tap 2 D7 T ap 2 D9 Tap 2 D3

Port C0 TxIN 15 Tap2 D0 Tap 2 D0 Tap 3 D0 Tap 3 D2 T ap 2 D7

Port C1 TxIN 18 Tap2 D1 Tap 2 D1 Tap 3 D1 Tap 3 D3 T ap 3 D2

Port C2 TxIN 19 Tap2 D2 Tap 2 D2 Tap 3 D2 Tap 3 D4 T ap 3 D3

Port C3 TxIN 20 Tap2 D3 Tap 2 D3 Tap 3 D3 Tap 3 D5 T ap 3 D4

Port C4 TxIN 21 Tap2 D4 Tap 2 D4 Tap 3 D4 Tap 3 D6 T ap 3 D5

Port C5 TxIN 22 Tap2 D5 Tap 2 D5 Tap 3 D5 Tap 3 D7 T ap 3 D6

Port C6 TxIN 16 Tap2 D6 Tap 2 D6 Tap 3 D6 Tap 3 D8 T ap 3 D0

Port C7 TxIN 17 Tap2 D7 Tap 2 D7 Tap 3 D7 Tap 3 D9 T ap 3 D1

- TxIN 24 LVAL LVAL LVAL LVAL L VAL

- TxIN 25 FVAL FVAL FVAL FVAL FVAL

(Port I0) TxIN 26 DVAL DVAL DVAL T ap 1 D0 Tap 4 D0

(Port I1) TxIN 23 Exposure Active Exposure Active Ex posure Active Tap 1 D1 Tap 3 D7

SP-5000M/C-PMCL

Camera Link Configuration

Camera Link port/bit

GenICam Tap Geometry

D

i

g

i

t

a

l

I

/

O

-

1

Port

Base Medium Full 80bit Full

2Tap / 12bit 4Tap / 12bit 8 Tap / 8b it 8 Tap / 10b it 10 Tap / 8 bit

1X2 - 1Y 1X4 - 1Y 1x8 - 1Y 1X 8 - 1Y 1X10 - 1Y

Port D0 TxIN 0 — Tap 4 D0 Tap 4 D0 T ap 4 D2 Tap 4 D2

Port D1 TxIN 1 — Tap 4 D1 Tap 4 D1 T ap 4 D3 Tap 4 D3

Port D2 TxIN 2 — Tap 4 D2 Tap 4 D2 T ap 4 D4 Tap 4 D4

Port D3 TxIN 3 — Tap 4 D3 Tap 4 D3 T ap 4 D5 Tap 4 D5

Port D4 TxIN 4 — Tap 4 D4 Tap 4 D4 T ap 4 D6 Tap 4 D6

Port D5 TxIN 6 — Tap 4 D5 Tap 4 D5 T ap 4 D7 Tap 5 D0

Port D6 TxI N 27 — Tap 4 D6 Tap 4 D6 T ap 4 D8 LVAL

Port D7 TxIN 5 — Tap 4 D7 Tap 4 D7 T ap 4 D9 Tap 4 D7

Port E0 TxIN 7 — Tap 3 D0 Tap 5 D0 Tap 5 D2 Tap 5 D1

Port E1 TxIN 8 — Tap 3 D1 Tap 5 D1 Tap 5 D3 Tap 5 D2

Port E2 TxIN 9 — Tap 3 D2 Tap 5 D2 Tap 5 D4 Tap 5 D3

Port E3 TxI N 12 — Tap 3 D3 Tap 5 D3 Tap 5 D5 Tap 5 D6

Port E4 TxI N 13 — Tap 3 D4 Tap 5 D4 Tap 5 D6 Tap 5 D7

Port E5 TxI N 14 — Tap 3 D5 Tap 5 D5 Tap 5 D7 Tap6 D0

Port E6 TxI N 10 — Tap 3 D6 Tap 5 D6 Tap 5 D8 Tap 5 D4

Port E7 TxI N 11 — Tap 3 D7 Tap 5 D7 Tap 5 D9 Tap 5 D5

Port F0 TxIN 15 — Tap 3 D8 Tap6 D0 Tap 6 D2 Tap6 D1

Port F1 TxIN 18 — Tap 3 D9 Tap6 D1 Tap 6 D3 Tap6 D4

Port F2 TxIN 19 — Tap 3 D10 Tap6 D2 Tap 6 D4 Tap6 D5

Port F3 TxIN 20 — Tap 3 D11 Tap6 D3 Tap 6 D5 Tap6 D6

Port F4 TxIN 21 — Tap 4 D8 Tap6 D4 Tap 6 D6 Tap6 D7

Port F5 TxIN 22 — Tap 4 D9 Tap6 D5 Tap 6 D7 Tap7 D0

Port F6 TxIN 16 — Tap 4 D10 Tap6 D6 Tap 6 D8 Tap6 D2

Port F7 TxIN 17 — Tap 4 D11 Tap6 D7 Tap 6 D9 Tap6 D3

- TxIN 24 — LVAL LVAL LVAL Tap7 D2

(Port I2) TxIN 25 — FVAL FVAL Tap 2 D0 Tap7 D3

(Port I3) TxIN 26 — DVAL DVAL Tap 2 D1 Tap7 D4

(Port I4) TxIN 23 — Exposure Active Exposure Active Tap 3 D0 T ap7 D1

SP-5000M/C-PMCL

D

i

g

i

t

a

l

I

/

O

-

2

(

1

/

2

)

Port

Camera Link Configuration

Camera Link port/bit

GenICam Tap Geometry

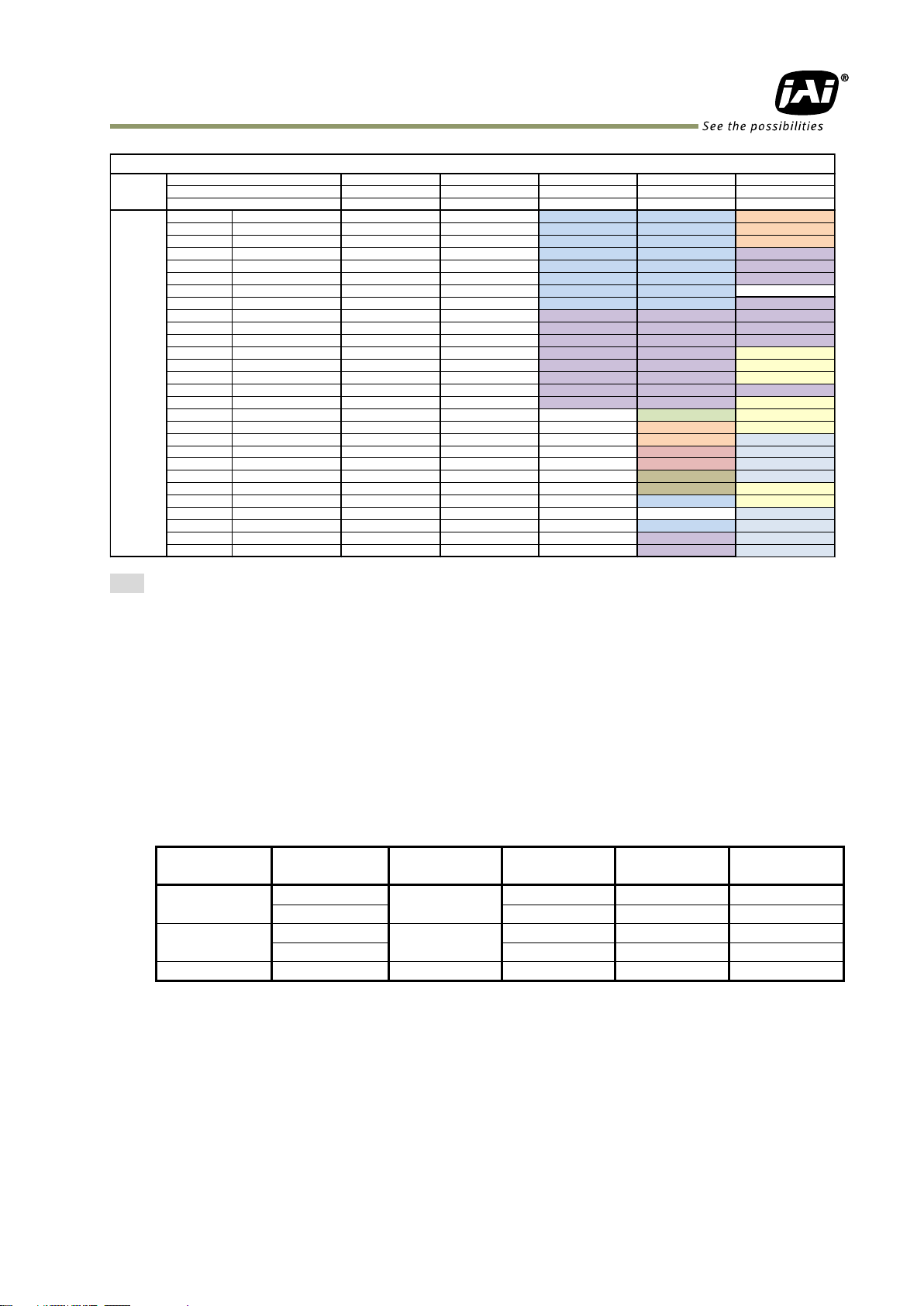

5.2 Camera Link interface

5.2.1 Camera Link Interface

Table-6 Camera Link interface

- 14 -

Page 17

SP-5000M-PMCL / SP-5000C-PMCL

Base Medium Full 80bit Full

2Tap / 12bit 4Tap / 12bit 8 Tap / 8b it 8 Tap / 10b it 10 Tap / 8 bit

1X2 - 1Y 1X4 - 1Y 1x8 - 1Y 1X 8 - 1Y 1X10 - 1Y

Port G0 TxIN 0 — ― Tap 7 D0 Tap 7 D2 Tap7 D5

Port G1 TxIN 1 — ― Tap 7 D1 Tap 7 D3 Tap7 D6

Port G2 TxIN 2 — ― Tap 7 D2 Tap 7 D4 Tap7 D7

Port G3 TxIN 3 — ― Tap 7 D3 Tap 7 D5 Tap8 D0

Port G4 TxIN 4 — ― Tap 7 D4 Tap 7 D6 Tap8 D1

Port G5 TxIN 6 — ― Tap 7 D5 Tap 7 D7 Tap8 D3

Port G6 TxIN 27 — ― Tap 7 D6 Tap 7 D8 LVAL

Port G7 TxIN 5 — ― Tap 7 D7 Tap 7 D9 Tap8 D2

Port H0 TxIN 7 — ― Tap 8 D0 Tap 8 D2 Tap8 D4

Port H1 TxIN 8 — ― Tap 8 D1 Tap 8 D3 Tap8 D5

Port H2 TxIN 9 — ― Tap 8 D2 Tap 8 D4 Tap8 D6

Port H3 TxIN 12 — ― Tap 8 D3 Tap 8 D5 Tap 9 D1

Port H4 TxIN 13 — ― Tap 8 D4 Tap 8 D6 Tap 9 D2

Port H5 TxIN 14 — ― Tap 8 D5 Tap 8 D7 Tap 9 D3

Port H6 TxIN 10 — ― Tap 8 D6 Tap 8 D8 Tap8 D7

Port H7 TxIN 11 — ― Tap 8 D7 Tap 8 D9 Tap 9 D0

(Port I5) TxIN 15 — ― Tap 3 D1 Tap 9 D4

(Port I6) TxIN 18 — ― Tap 4 D0 Tap 9 D7

(Port I7) TxIN 19 — ― Tap 4 D1 Tap10 D0

(Port K0) TxIN 20 — ― Tap 5 D0 Tap10 D1

(Port K1) TxIN 21 — ― Tap 5 D1 Tap10 D2

(Port K2) TxIN 22 — ― Tap 6 D0 Tap10 D3

(Port K3) TxIN 16 — ― Tap 6 D1 Tap 9 D5

(Port K4) TxIN 17 — ― Tap 7 D0 Tap 9 D6

- TxIN 24 — ― LVAL LVAL Tap10 D5

(Port K5) TxIN 25 — ― FVAL Tap 7 D1 Tap10 D6

(Port K6) TxIN 26 — ― DVAL Tap 8 D0 T ap10 D7

(Port K7) TxIN 23 — ― Exposure Active Tap 8 D1 Tap10 D4

SP-5000M/C-PMCL

D

i

g

i

t

a

l

I

/

O

-

2

(

2

/

2

)

Port

Camera Link Configuration

Camera Link port/bit

GenICam Tap Geometry

Camera Link

Pixel Clock

Maximum

length

1X2–1Y

1X4–1Y

1X8-1Y

1X10–1Y

61.7 MHz

10 m

23 fps

— — —

7 m

46 fps

93 fps

115 fps

75.4 MHz

7 m

28 fps

56 fps

112 fps

—

5 m

134 fps

82.3 MHz

5 m

30 fps

61 fps

120 fps

134 fps

Note

1. In this table, not all tap geometry items are described. For instance, 1X4–1Y shows only 12-bit.

In case of 10-bit, upper 2 bits (D10 and D11) are not used and in case of 8-bit, upper 4 bits

(D8 through D11) are not used.

2. Please check whether the frame grabber complies with those formats if you use 80-bit (8-tap/10-bit)

camera configuration.

3. If you use 80-bit (8-tap/10-bit) camera configuration, DVAL and Exposure Active (JAI custom) are

not output through the Camera Link interface. FVAL is only output via Digital I/O-1 connector.

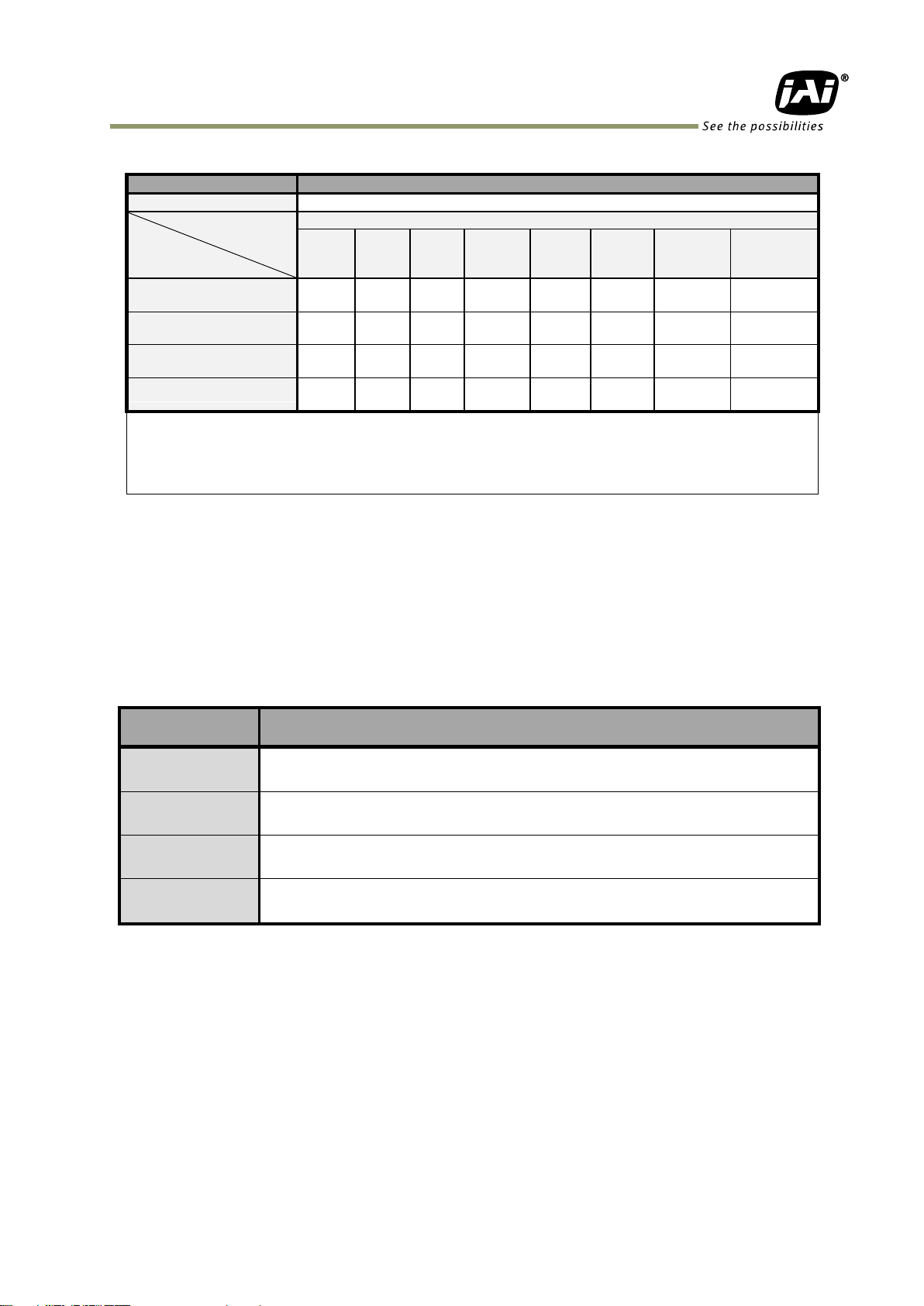

5.2.2 Camera Link pixel clock frequency

In the SP-5000M-PMCL and SP-5000C-PMCL, the Camera Link pixel clock can be selected from

82.3 MHz, 75.4 MHz and 61.7 MHz. If the 61.7 MHz clock is used, the transfer length through

the camera link cable will be extended to 10m. On the other hand, the frame rate will be

reduced. The default setting is 82.3 MHz.

Note: The maximum lengths shown in the above table are guidelines. Operating at these lengths

may generate bit noise, depending on the cable used.

- 15 -

Page 18

SP-5000M-PMCL / SP-5000C-PMCL

Line Selector item

Description

Line 1 TTL 1 Out

TTL 1 output from Hirose 12P #9 pin

Line 8 TTL 2 OUT

TTL 2 output from AUX Hirose 10P #1 pin

Line 10 TTL 3 OUT

TTL 3 output from AUX Hirose 10P #2 pin

NAND 0 IN 1

No. 1 input to the first NAND gate

NAND 0 IN 2

No. 2 input to the first NAND gate

NAND 1 IN 1

No. 1 input to the second NAND gate

NAND 1 IN 2

No. 2 input to the second NAND gate

Line Source item

Description

Low

Connect Low Level signal to line item selected in Line Selector, Default setting

High

Connect High Level signal to line item selected in Line Selector

Frame Trigger Wait

Connect Frame Trigger Wait signal to line item selected in Line Selector

Frame Active

Connect Frame Active signal to line item selected in Line Selector

Exposure Active

Connect Exposure Active signal to line item selected in Line Selector

FVAL

Connect FVAL signal to line item selected in Line Selector

LVAL

Connect LVAL signal to line item selected in Line Selector

PulseGenerator0 Out

Connect Pulse Generator 0 signal to line item selected in Line Selector

PulseGenerator1 Out

Connect Pulse Generator 1 signal to line item selected in Line Selector

PulseGenerator2 Out

Connect Pulse Generator 2 signal to line item selected in Line Selector

PulseGenerator3 Out

Connect Pulse Generator 3 signal to line item selected in Line Selector

TTL 1 In

Connect TTL 1 IN signal to line item selected in Line Selector

CL CC1 In

Connect CL CC1 IN signal to line item selected in Line Selector

NAND 0 Out

Connect NAND 0 signal to line item selected in Line Selector

NAND 1 Out

Connect NAND 1 signal to line item selected in Line Selector

Line 10 TTL 2 In

Connect TTL 2 IN signal to Line 10 (Option)

Line 11 LVDS 1 In

Connect LVDS 1 IN signal to Line 11 (Option)

Note]

As for LVAL, some line items cannot be connected. Refer to “5.3.7.2 GPIO matrix table”

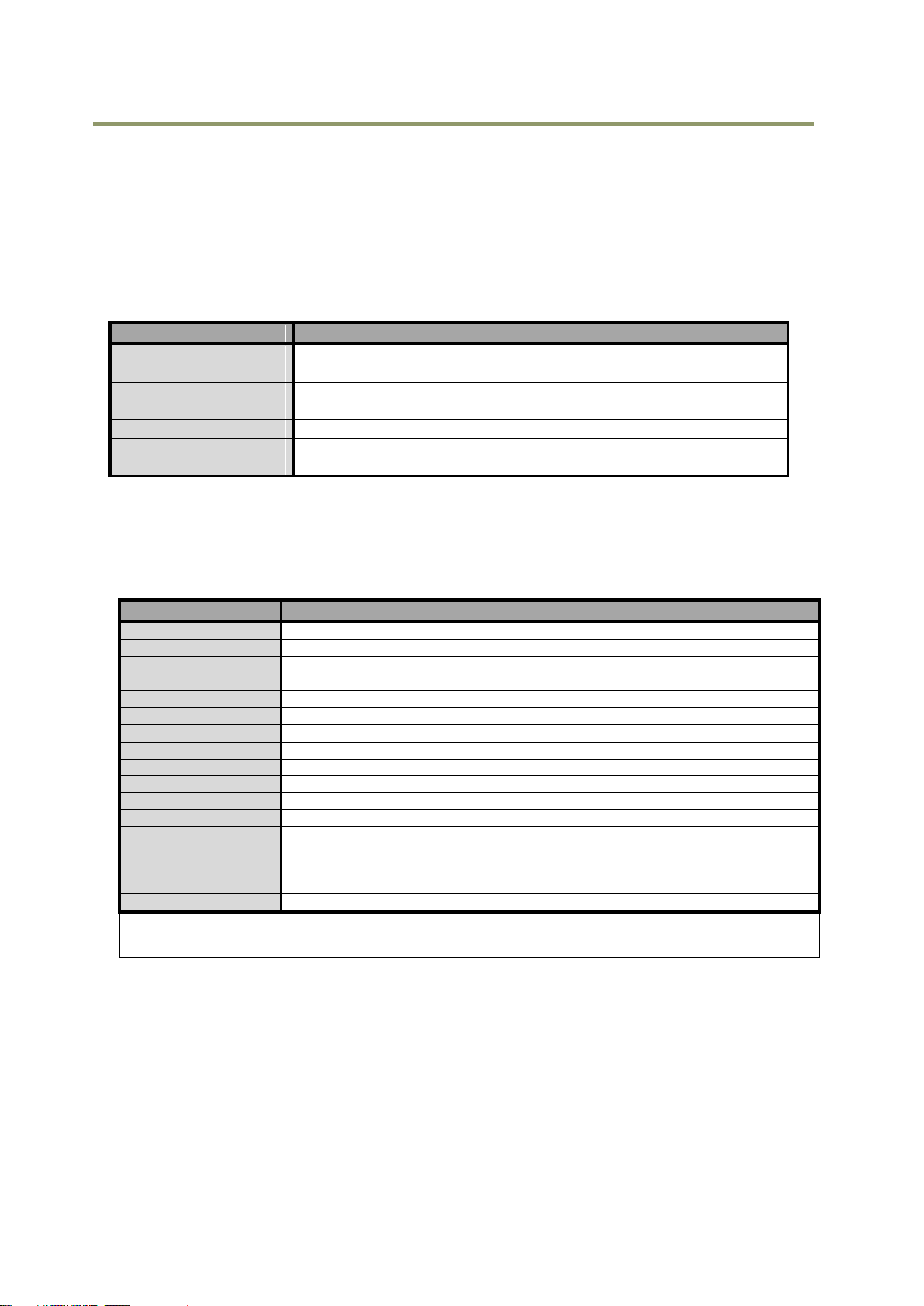

5.3 Digital IN/OUT interface

In the SP-5000M-PMCL and SP-5000C-PMCL, the software control tool can assign the necessary

signals used in the system to digital inputs and outputs (see Section 5.3.7.1 for block diagram).

5.3.1 Line Selector

In the Line Selector, the following input and output signals can be assigned.

Table-7 Line selector

5.3.2 Line Source

Line source signal can be selected from the following table to connect it to the line item which

is selected in the line selector.

Table-8 Line Source

5.3.3 Line Mode

Indicates the status of the item selected in Line Selector. (INPUT or OUTPUT)

5.3.4 Line Inverter

Inverts the signal polarity for the item selected in Line Selector.

(False=Positive, True=Negative)

5.3.5 Line Status

Indicates the status of the selected signal (input or output) (True=High,

False=Low)

- 16 -

Page 19

SP-5000M-PMCL / SP-5000C-PMCL

Soft Trigger

LVAL IN

FVAL IN

Exposure Active

Frame Trigger Wait

Frame Active

GPIO 4 (TTL IN 1)

GPIO 7 (CL CC1)

GPIO 10 (TTL IN2)

GPIO 11 (LVDS IN)

Pixel Clock

Cross Pont

Switch

12 bit Counter

INV

INV

INV N

NAND

INV

Non INV

Pulse Generator

20 bit counter x 4

CLR

Sel Bit (5,0) Sel Bit (7)

Sel Bit (7)

Pulse Generator 0

Pulse Generator 1

Pulse Generator 2

Pulse Generator 3

Trigger 2 (Frame Start)

GPIO 1 (TTL OUT 1)

GPIO 8 (TL OUT 2)

GPIO 9 (TTL OUT 3)

Sel Bit (7)

Clock IN

Clear IN

Gate 1

Gate 2

5.3.6 Line Format

Indicates the interface information of the input and output lines.

Not connected, TTL, LVDS or Opto-coupled

Note: In the SP-5000-PMCL, Opto-coupled interface is not available.

5.3.7 GPIO

GPIO is a general interface for input and output and controls the I/O for trigger signals and

other valid signals and pulse generators. By using this interface you can control an external light

source, make a delay function for an external trigger signal, or make a precise exposure setting

together with a PWC trigger.

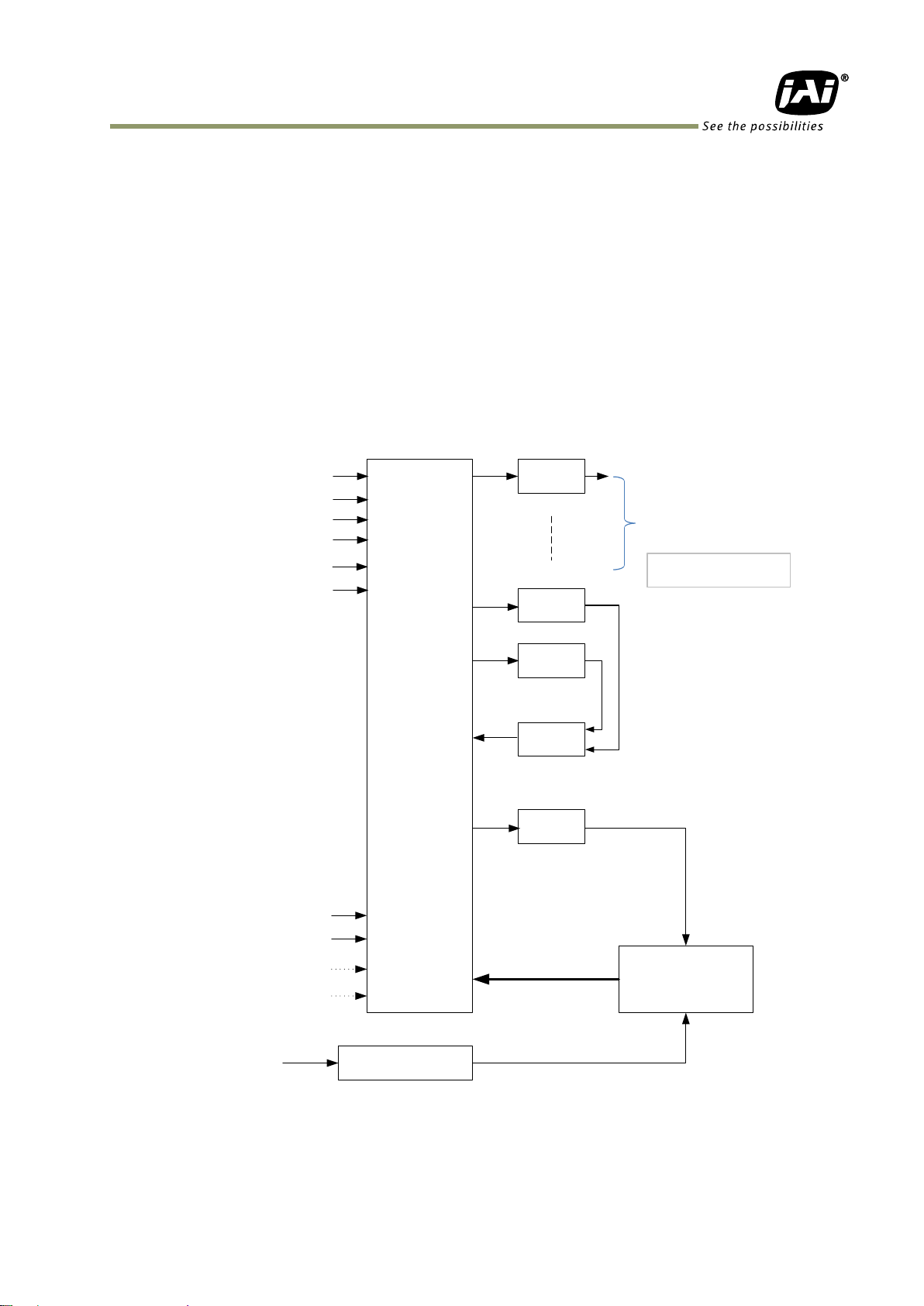

5.3.7.1 Basic block diagram

The basic block diagram is as follows.

In the SP-5000-PMCL, the pixel clock is 48 MHz.

Note: Items written in blue letters are available if the AUX Type 3 option is selected.

Fig.6 GPIO interface

- 17 -

Page 20

SP-5000M-PMCL / SP-5000C-PMCL

Selector (Cross

point switch output)

Source signal

(Cross point switch input)

Low

High

Soft Trigger

Exposure Active

Frame Trigger Wait

Frame Active

FVAL

LVAL

Pulse Generator 0

Pulse Generator 1

Pulse Generator 2

Pulse Generator 3

Line 4 - TTL In1

Line 7 - CL CC1 in

NAND 0 Out

NAND 1 Out 1

Line 10 - TTL 2 In

Line 11 - LVDS 1 In

Trigger Source

Line Selector

Pulse Generator

Selector

Trigger Source

(Frame Start )

Line 1 - 12P TTL Out

Line 8 - TTL 2 Out

Trigger Selector

Pulse Generator

Clear Source

Line Source

Line 9 - TTL 3 Out

NAND 1 In 1

NAND 1 In 2

NAND 2 In 1

NAND 2 In 2

Pulse Generator 0

Pulse Generator 1

Pulse Generator 2

Pulse Generator 3

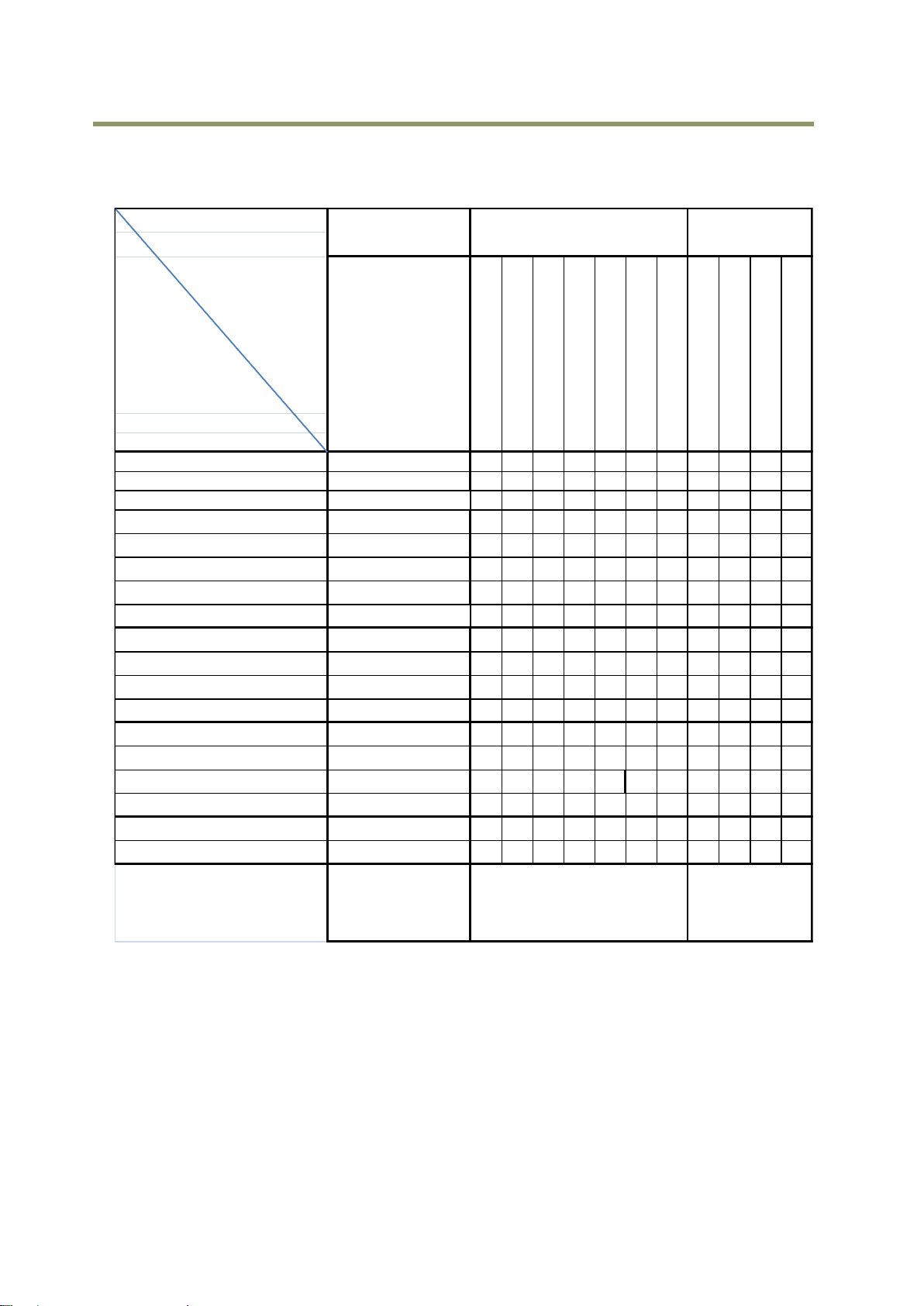

5.3.7.2 Input and output matrix table

The relation between input and output is as follows.

Table-9 GPIO matrix table

Note: In the above table, TTL 2 IN, LVDS IN, TTL 2 Out and TTL 3 Out are available only if AUX Type

3 option is used.

5.4 Pulse Generator

The SP-5000-PMCL has a frequency divider using the sensor clock as the basic clock and four pulse

generators. In each Pulse Generator, various Clear settings are connected to GPIO.

The following shows Pulse Generator default settings.

- 18 -

Page 21

SP-5000M-PMCL / SP-5000C-PMCL

Display Name

Value

Clock Pre-scaler

1

Pulse Generator

Selector

Pulse Generator

Length

Start

Point

End

Point

Repeat

Count

Clear

Source

Clear

Inverter

Clear

Activation

Clear

Sync

Mode

-

Pulse Generator 0

1 0 1 0 Off

True

Off

Async

Mode

-

Pulse Generator 1

1 0 1 0 Off

True

Off

Async

Mode

-

Pulse Generator 2

1 0 1 0 Off

True

Off

Async

Mode

-

Pulse Generator 3

1 0 1 0 Off

True

Off

Async

Mode

Note:]

When Pulse Generator Repeat Count is set to “0”, the camera is operating in free-running mode.

However, based on the above default settings, Length=1, Start Point=0 and End Point=1, Pulse

Generator stops at High output. Therefore, if Start Point=0 and End Point=1 are configured, Length should

be “2” as the minimum active width.

Trigger Selector

item

Description

Pulse Generator

0

If Pulse Generator 0 is selected, Length, Start Point, End Point, Repeat Count, Clear Source, Clear

Inverter, Clear Activation and Clear Sync Mode of Pulse Generator 0 are displayed under the

selector.

Pulse Generator

1

If Pulse Generator 1 is selected, Length, Start Point, End Point, Repeat Count, Clear Source, Clear

Inverter, Clear Activation and Clear Sync Mode of Pulse Generator 1 are displayed under the

selector.

Pulse Generator

2

If Pulse Generator 2 is selected, Length, Start Point, End Point, Repeat Count, Clear Source, Clear

Inverter, Clear Activation and Clear Sync Mode of Pulse Generator 2 are displayed under the

selector.

Pulse Generator

3

If Pulse Generator 3 is selected, Length, Start Point, End Point, Repeat Count, Clear Source, Clear

Inverter, Clear Activation and Clear Sync Mode of Pulse Generator 3 are displayed under the

selector.

Table - 10 Pulse Generator default settings

5.4.1 Clock Pre-scaler

Clock pre-scaler (Divide Value) can set the dividing value of the frequency divider (12-bit

length) and the sensor clock is used for this. Four built-in pulse generators work by the

same clock. In the SP-5000-PMCL, the sensor clock is 48 MHz.

5.4.2 Pulse Generator Selector

This is where you select one of the 4 pulse generators in order to set or modify its

parameters.

Table - 11 Pulse Generator setting

- 19 -

Page 22

SP-5000M-PMCL / SP-5000C-PMCL

Pulse generator

length

Pulse generator Start point

Pulse generator End point

Pulse generator repeat count = N

(Pulse generator length x N)

Pulse generator

Clear source IN

(Clear activation

= Rising edge

Clear SYNC mode

= Async)

Pulse generator

Output

Pulse generator

length

Pulse generator

length

000

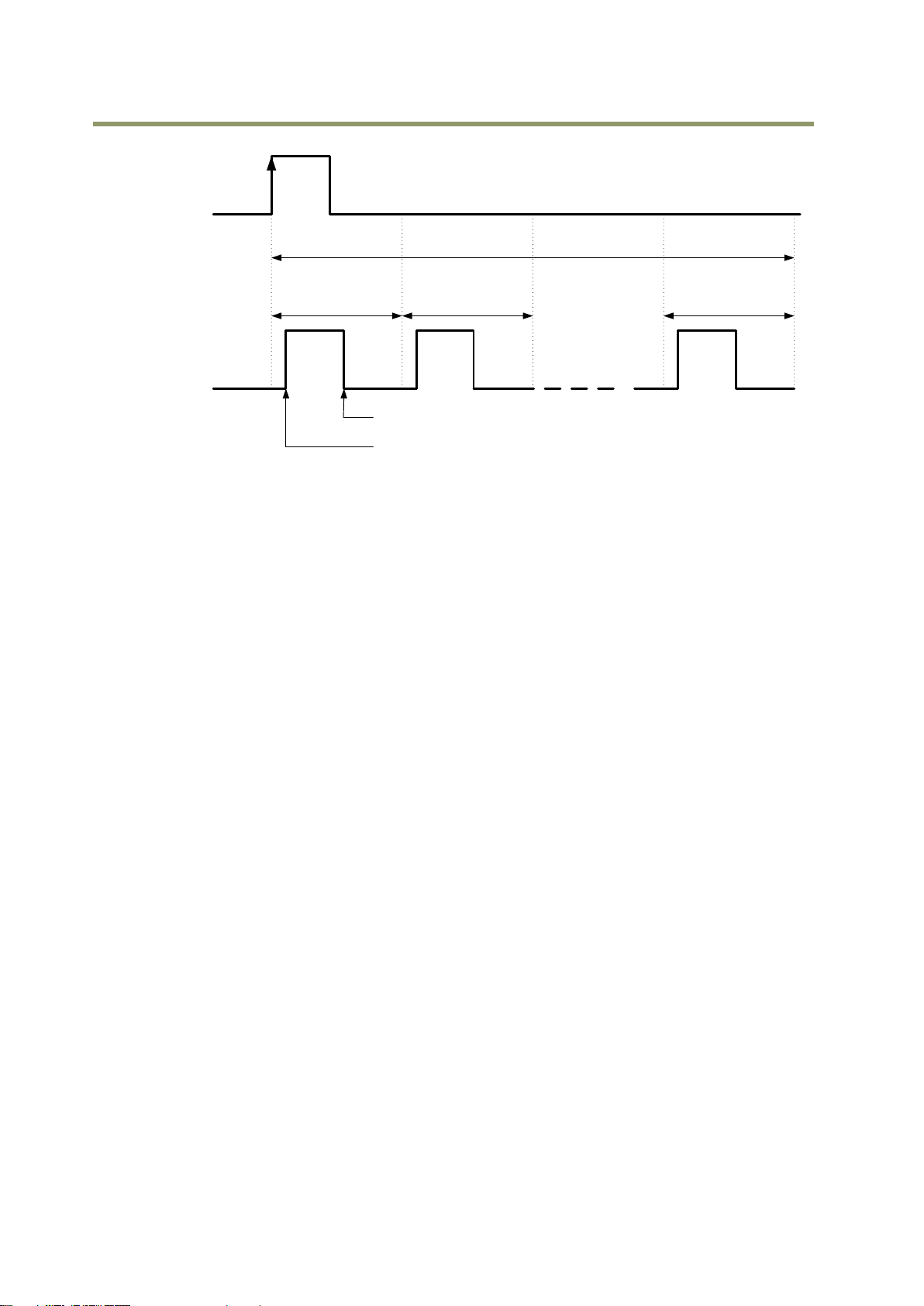

Fig.7 Pulse Generator pulse construction

5.4.3 Pulse Generator Length

Set the counter up value for the selected pulse generator. If Repeat Count value is “0” and

if Pulse Generator Clear signal is not input, the pulse generator generates the pulse

repeatedly until reaching this counter up value.

5.4.4 Pulse Generator Start Point

Set the active output start count value for the selected pulse generator.

However, please note that a maximum 1 clock jitter for the clock which is divided in the clock

pre-scaler can occur.

5.4.5 Pulse Generator End Point

Set the active output ending count value for the selected pulse generator.

5.4.6 Pulse Generator Repeat Count

Set the repeating number of the pulse for the selected pulse generator. After Trigger Clear

signal is input, the pulse generator starts the count set in Repeat Count. Accordingly, an

active pulse which has a start point and end point can be output repeatedly.

However, if Repeat Count is set to“0”, it works as free-running counter.

5.4.7 Pulse Generator Clear Activation

Set the clear conditions of clear count pulse for the selected pulse generator.

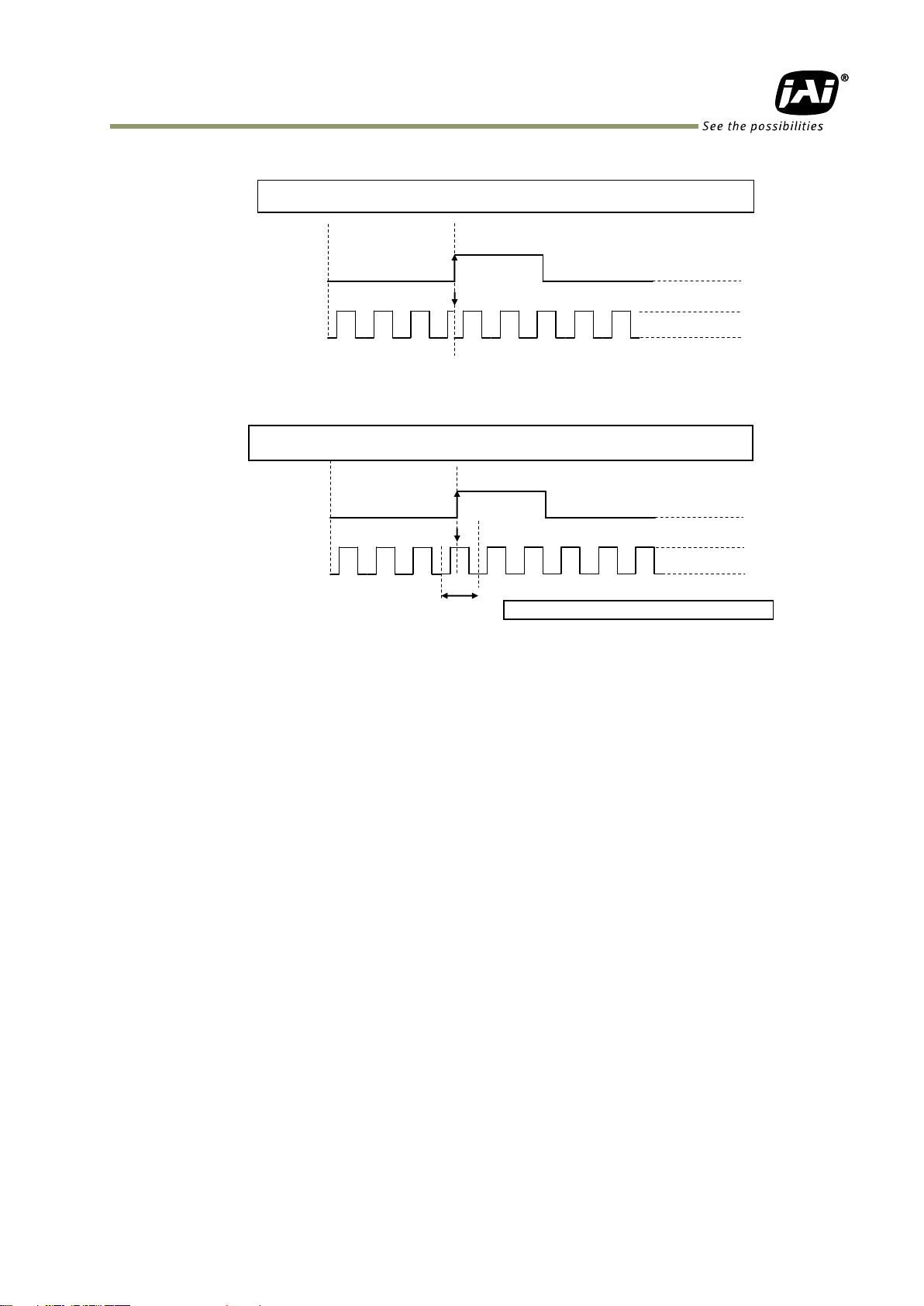

5.4.8 Pulse Generator Clear Sync Mode

Set the count clear method for the selected pulse generator.

In case of Async Mode, if the clear signal is input during the length setting value, the counter

will stop counting according to the clear signal input.

In case of Sync Mode, if the clear signal is input during the length setting value, the counter

will continue to count until the end of the length setting value and then clear the count.

Both modes clear the repeat count when the counter is cleared.

- 20 -

Page 23

SP-5000M-PMCL / SP-5000C-PMCL

0

Clear

↓

Pulse

Generator

Output

Pulse

Generator

Clear Source In

(Example 1) Clear Activation = Rising Edge, Clear Sync Mode = Async Mode,

Clear Inverter = False

(Example 2) Clear Activation = Rising Edge, Clear Sync Mode = Sync Mode,

Clear Inverter = False

Pulse

Generator

Output

Pulse

Generator

Clear Source In

0

Pulse

Generator

Length

0

Clear

↓

Note: Repeat Count is also reset.

Fig.8 Counter clear in Async mode

Fig.9 Counter clear in Sync mode

- 21 -

Page 24

SP-5000M-PMCL / SP-5000C-PMCL

Pulse Generator

Clear Source

item

Description

Low

Connect Low level signal to Clear Source for the selected pulse generator.

Default setting

High

Connect High level signal to Clear Source for the selected pulse

generator.

Frame Trigger Wait

Connect Frame Trigger Wait signal to Clear Source for the selected pulse

generator.

Frame Active

Connect Frame Active signal to Clear Source for the selected pulse

generator.

Exposure Active

Connect Exposure Active signal to Clear Source for the selected pulse

generator.

FVAL

Connect FVAL signal to Clear Source for the selected pulse generator.

LVAL

Connect LVAL signal to Clear Source for the selected pulse generator.

PulseGenerator0

Out

Connect Pulse Generator 0 output to Clear Source for the selected pulse

generator.

PulseGenerator1

Out

Connect Pulse Generator 1 output to Clear Source for the selected pulse

generator.

PulseGenerator2

Out

Connect Pulse Generator 2 output to Clear Source for the selected pulse

generator.

PulseGenerator3

Out

Connect Pulse Generator 3 output to Clear Source for the selected pulse

generator.

TTL 1 In

Connect TTL 1 IN signal to Clear Source for the selected pulse generator.

CL CC1 In

Connect CL CC1 IN signal to Clear Source for the selected pulse

generator.

Nand0 Out

Connect NAND 0 output signal to Clear Source for the selected pulse

generator.

Nand1 Out

Connect NAND 1 output signal to Clear Source for the selected pulse

generator.

Line 10 TTL 2 In

Connect TTL 2 IN signal to Line 10.

Line 11 LVDS 1 In

Connect LVDS 1 IN signal to Line 11.

Note:

The pulse generator output cannot be used as the clear input to the same pulse generator.

Refer to “5.3.7.2.GPIO matrix table”.

5.4.9 Pulse Generator Clear Source

The following clear sources can be selected as the pulse generator clear signal.

Table - 12 Pulse generator clear source

- 22 -

Page 25

SP-5000M-PMCL / SP-5000C-PMCL

Display Name

Value

Clock Pre-scaler

1 to 4096

Pulse Generator Clock (MHZ)

[Pixel Clock:48MHz]÷[Clock Pre-scaler]

Pulse Generator Selector

- Pulse Generator 0

- Pulse Generator 1

- Pulse Generator 2

- Pulse Generator 3

- Pulse Generator Length

1 to 1048575

- Pulse Generator Length (ms)

([Clock Source]÷[Clock Pre-scaler])-1 x [Pulse Generator Length]

- Pulse Generator Frequency (Hz)

[ Pulse Generator Length (ms)]-1

- Pulse Generator Start Point

0 to 1048574

- Pulse Generator Start Point (ms)

([Clock Source]÷[Clock Pre-scaler])-1 x [Pulse Generator Start Point]

- Pulse Generator End Point

1 to 1048575

- Pulse Generator End Point (ms)

([Clock Source]÷[Clock Pre-scaler])-1 x [Pulse Generator End Point]

- Pulse Generator pulse-width (ms)

[ Pulse Generator End Point (ms)]-[ Pulse Generator Start Point (ms)]

- Pulse Generator Repeat Count

0 to 255

- Pulse Generator Clear Activation

Clear Mode for the Pulse Generators

- Off

- High Level

- Low level

- Rising Edge

- Falling Edge

- Pulse Generator Clear Sync Mode

- Async mode

- Sync mode

- Pulse Generator Clear Source

- Low

- High

- Frame Trigger Wait

- Frame Active

- Exposure Active

- Fval

- Lval

- PulseGenerator0

- PulseGenerator1

- PulseGenerator2

- PulseGenerator3

- TTL_In1

- CL_CC1_In

- Nand0 Out

- Nand1 Out

- Line 10 - TTL 2 In

- Line 11 - LVDS 1 In

- Pulse Generator Inverter(Polarity)

Pulse Generator Clear Inverter

- False

- True

Note:

1. If Pulse Generator Repeat Count is set to “0”, the pulse generator works in free-running mode.

2. The output of the same pulse generator cannot be connected to Clear input.

5.4.10 Pulse Generator Inverter

Clear Source Signal can be have polarity inverted.

5.4.11 Pulse Generator Setting table

Table - 13 Pulse Generator setting parameters

- 23 -

Page 26

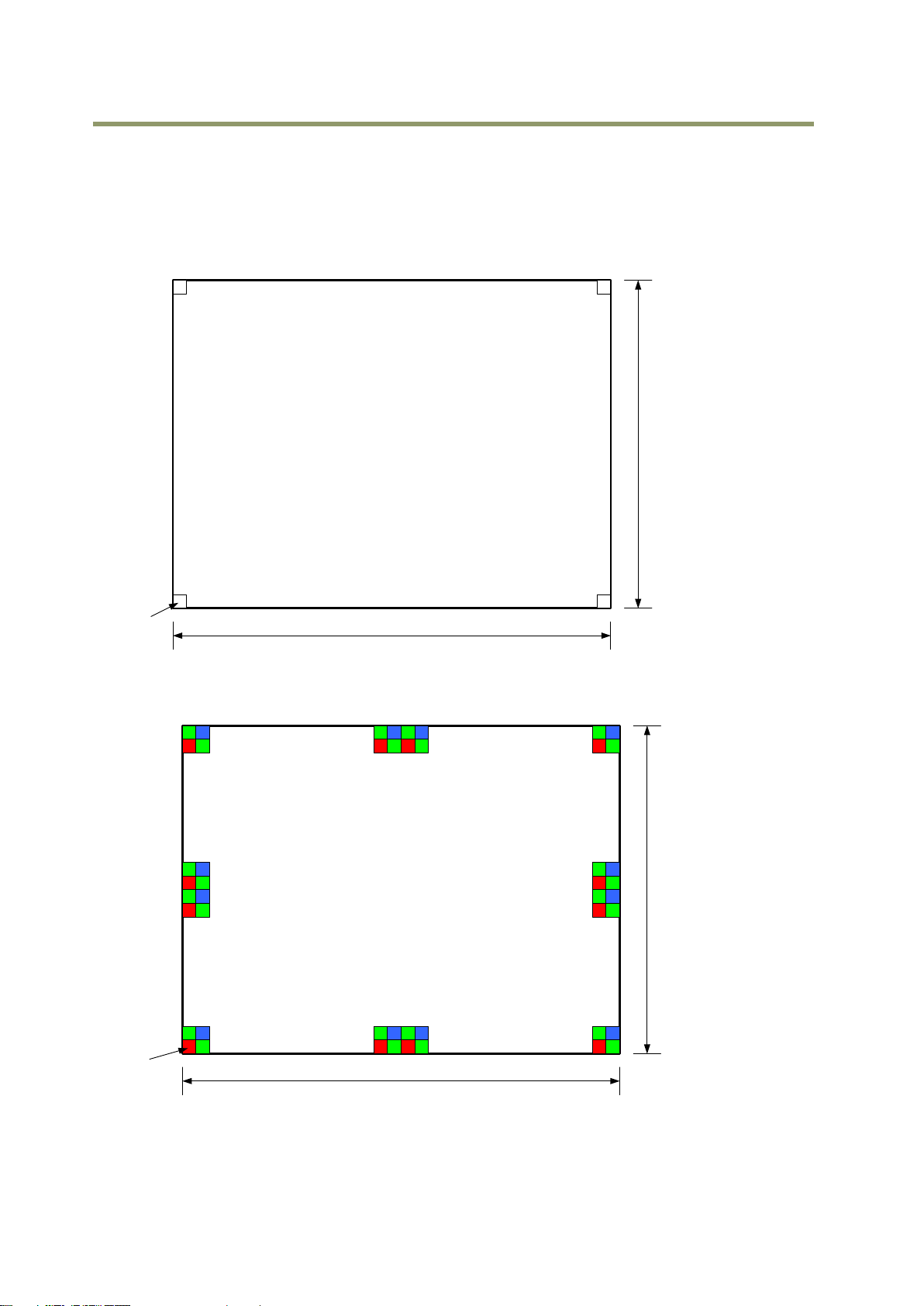

SP-5000M-PMCL / SP-5000C-PMCL

2560 Pixels

2048 Pixels

F

Pixel (0,0)

2560 Pixels

2048 Pixels

F

Pixel (0,0)

6. Sensor layout, output format and timing

6.1 Sensor layout

The CMOS sensors used in the SP-5000M-PMCL and SP-5000C-PMCL have the following pixel layout.

6.1.1 Monochrome sensor

Fig. 10 Monochrome sensor layout

6.1.2 Bayer sensor

Fig. 11 Color sensor layout

- 24 -

Page 27

SP-5000M-PMCL / SP-5000C-PMCL

Camera output format

Bit assignment

Refer to drawing

1X2–1Y

8-bit, 10-bit, 12-bit

6.2.1

1X4–1Y

8-bit, 10-bit, 12-bit

6.2.2

1X8–1Y

8-bit, 10-bit

6.2.3

1X10–1Y

8-bit

6.2.4

Width = 2560 Pixel 1280 Pixel x 2 Taps

Height = 2048 Pixel

X5120

Y1

X5120

Y3840

X4

Y1

X4

Y2048

X3

Y1

X3

Y2048

X2

Y1

X2

Y2048

X5

Y1

X5

Y2048

X6

Y1

X6

Y2048

X7

Y1

X7

Y2048

X8

Y1

X8

Y2048

X2053

Y1

X2553

Y2048

X2054

Y1

X2554

Y2048

X2055

Y1

X2555

Y2048

X2056

Y1

X2556

Y2048

X2057

Y1

X2557

Y2048

X2058

Y1

X2558

Y2048

X2059

Y1

X2559

Y2048

X2056

Y1

X2056

Y2

X2560

Y2047

X2560

Y2048

X1

Y1

X1

Y2

X1

Y2047

X1

Y2048

Tap 1

Tap 2

Pixel(0,0)

Step Y = 1

Step X = 2

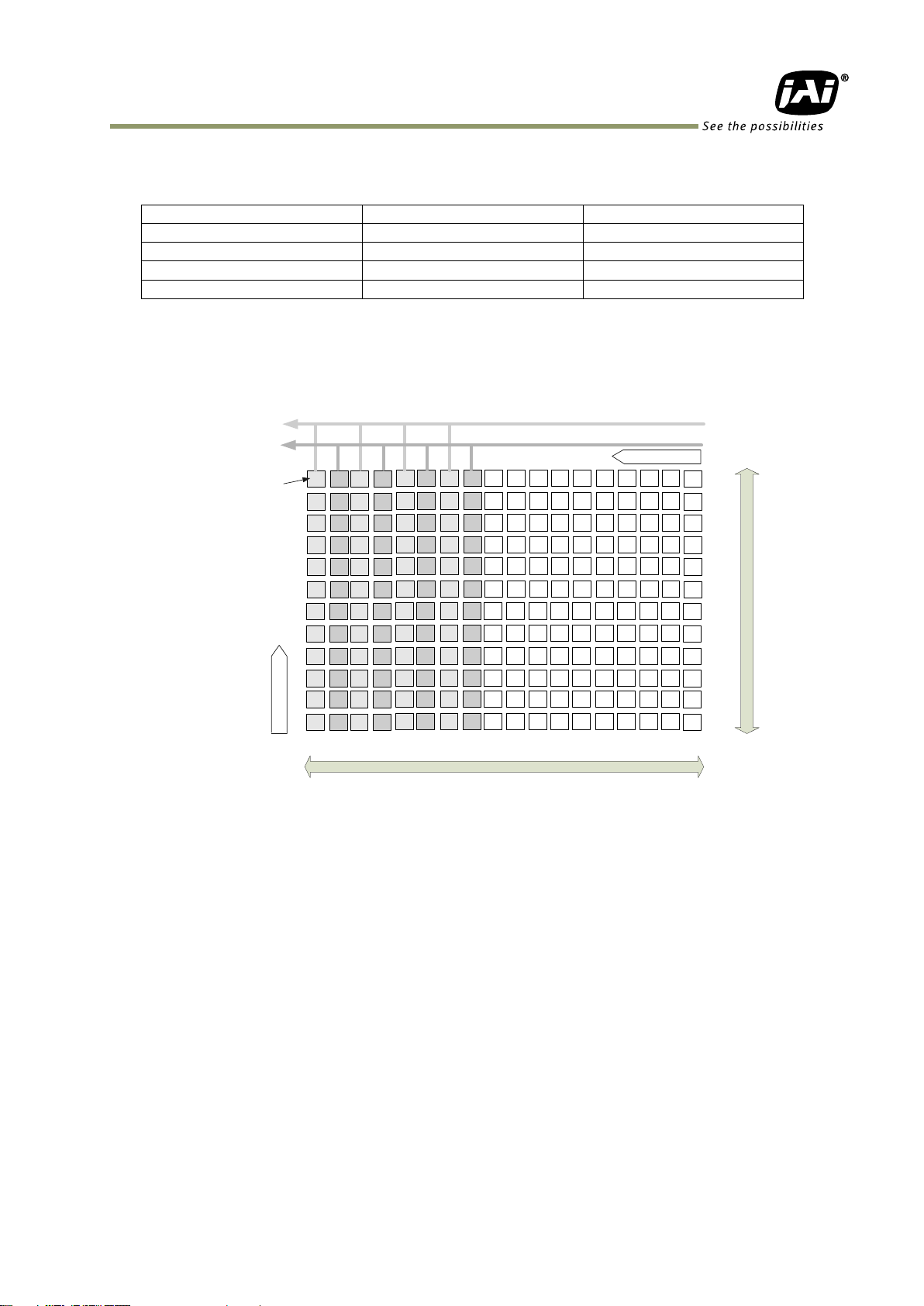

6.2 Camera output format (Tap Geometry)

Table - 14 Output format

Note: The camera output description is based on GenICam SFNC Ver.1.5.1.

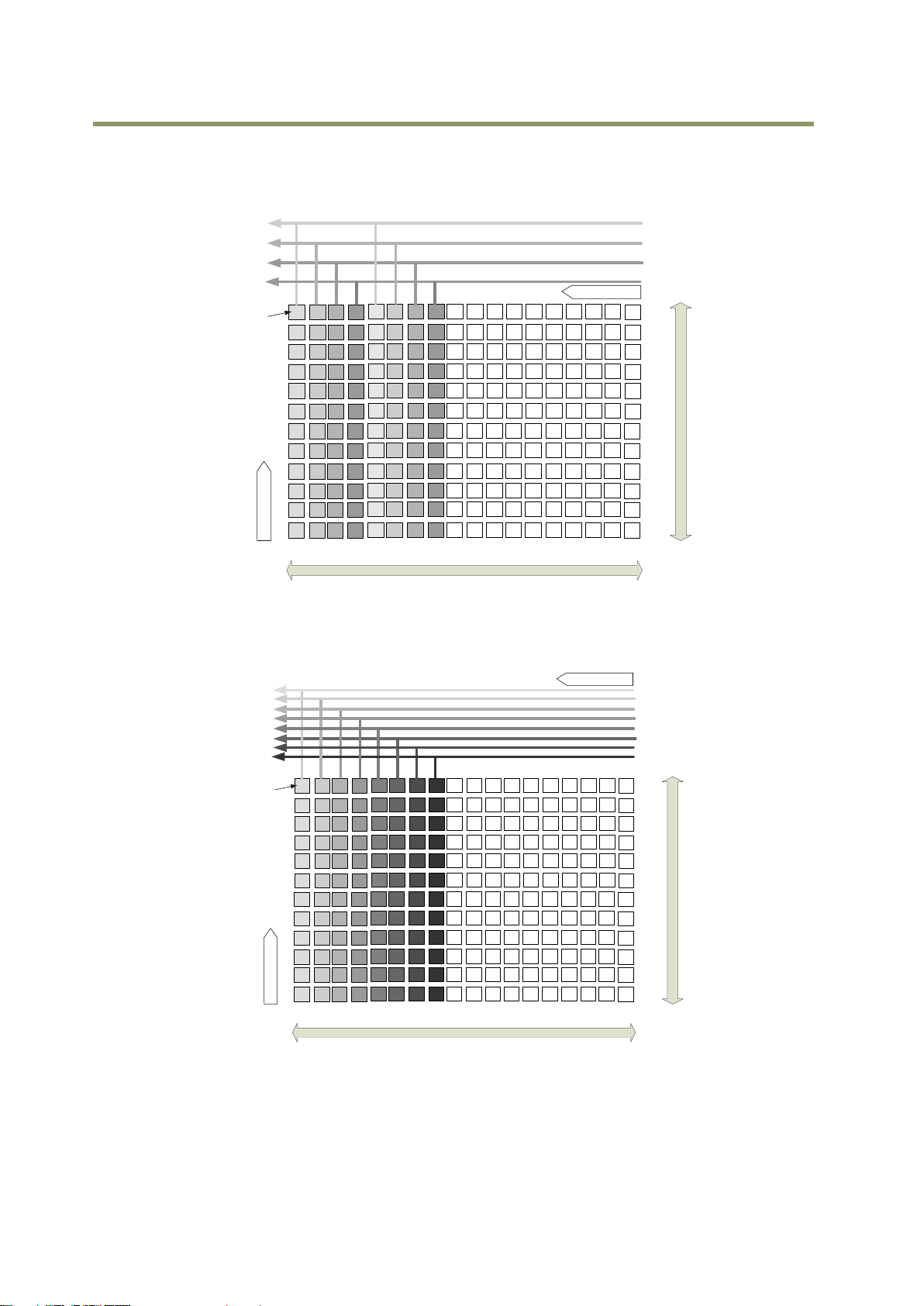

6.2.1 1X2–1Y

1X2–1Y is a 2-tap readout system specified in GenICam Tap Geometry and it outputs as the

following.

Fig.12 1X2–1Y output format

- 25 -

Page 28

SP-5000M-PMCL / SP-5000C-PMCL

Width = 2560 Pixel 1280 Pixel x 2 Taps

Height = 2048 Pixel

X5120

Y1

X5120

Y3840

X4

Y1

X4

Y2048

X3

Y1

X3

Y2048

X2

Y1

X2

Y2048

X5

Y1

X5

Y2048

X6

Y1

X6

Y2048

X7

Y1

X7

Y2048

X8

Y1

X8

Y2048

X2053

Y1

X2553

Y2048

X2054

Y1

X2554

Y2048

X2055

Y1

X2555

Y2048

X2056

Y1

X2556

Y2048

X2057

Y1

X2557

Y2048

X2058

Y1

X2558

Y2048

X2059

Y1

X2559

Y2048

X2056

Y1

X2056

Y2

X2560

Y2047

X2560

Y2048

X1

Y1

X1

Y2

X1

Y2047

X1

Y2048

Tap 1

Tap 2

Pixel(0,0)

Step Y = 1

Step X = 4

Tap 2

Tap 2

Width = 2560 Pixel 1280 Pixel x 2 Taps

Height = 2048 Pixel

X5120

Y1

X5120

Y3840

X4

Y1

X4

Y2048

X3

Y1

X3

Y2048

X2

Y1

X2

Y2048

X5

Y1

X5

Y2048

X6

Y1

X6

Y2048

X7

Y1

X7

Y2048

X8

Y1

X8

Y2048

X2053

Y1

X2553

Y2048

X2054

Y1

X2554

Y2048

X2055

Y1

X2555

Y2048

X2056

Y1

X2556

Y2048

X2057

Y1

X2557

Y2048

X2058

Y1

X2558

Y2048

X2059

Y1

X2559

Y2048

X2056

Y1

X2056

Y2

X2560

Y2047

X2560

Y2048

X1

Y1

X1

Y2

X1

Y2047

X1

Y2048

Tap 1

Tap 4

Pixel(0,0)

Step Y = 1

Step X = 8

Tap 6

Tap 8

Tap 2

Tap 5

Tap 3

Tap 7

6.2.2 1X4–1Y

1X4–1Y is a 4-tap readout system specified in GenICam Tap Geometry and it outputs as the

following.

Fig. 13 1X4–1Y output format

6.2.3 1X8–1Y

1X8–1Y is an 8-tap readout system and outputs as follows.

Fig. 14. 1X8–1Y output format

- 26 -

Page 29

SP-5000M-PMCL / SP-5000C-PMCL

Width = 2560 Pixel 256 Pixel x 10 Taps

Height = 2048 Pixel

X5120

Y1

X5120

Y3840

X4

Y1

X4

Y2048

X3

Y1

X3

Y2048

X2

Y1

X2

Y2048

X5

Y1

X5

Y2048

X6

Y1

X6

Y2048

X7

Y1

X7

Y2048

X8

Y1

X8

Y2048

X2053

Y1

X2553

Y2048

X2054

Y1

X2554

Y2048

X2055

Y1

X2555

Y2048

X2056

Y1

X2556

Y2048

X2057

Y1

X2557

Y2048

X2058

Y1

X2558

Y2048

X2059

Y1

X2559

Y2048

X2056

Y1

X2056

Y2

X2560

Y2047

X2560

Y2048

X1

Y1

X1

Y2

X1

Y2047

X1

Y2048

Tap 1

Tap 4

Pixel(0,0)

Step Y = 1

Step X = 10

Tap 6

Tap 8

Tap 2

Tap 5

Tap 3

Tap 7

Tap 9

Tap 10

FVAL Active

(a) LVAL Active (b)

(c) H-Offset

FVAL

LVAL

DVAL

DATA

DVAL Active

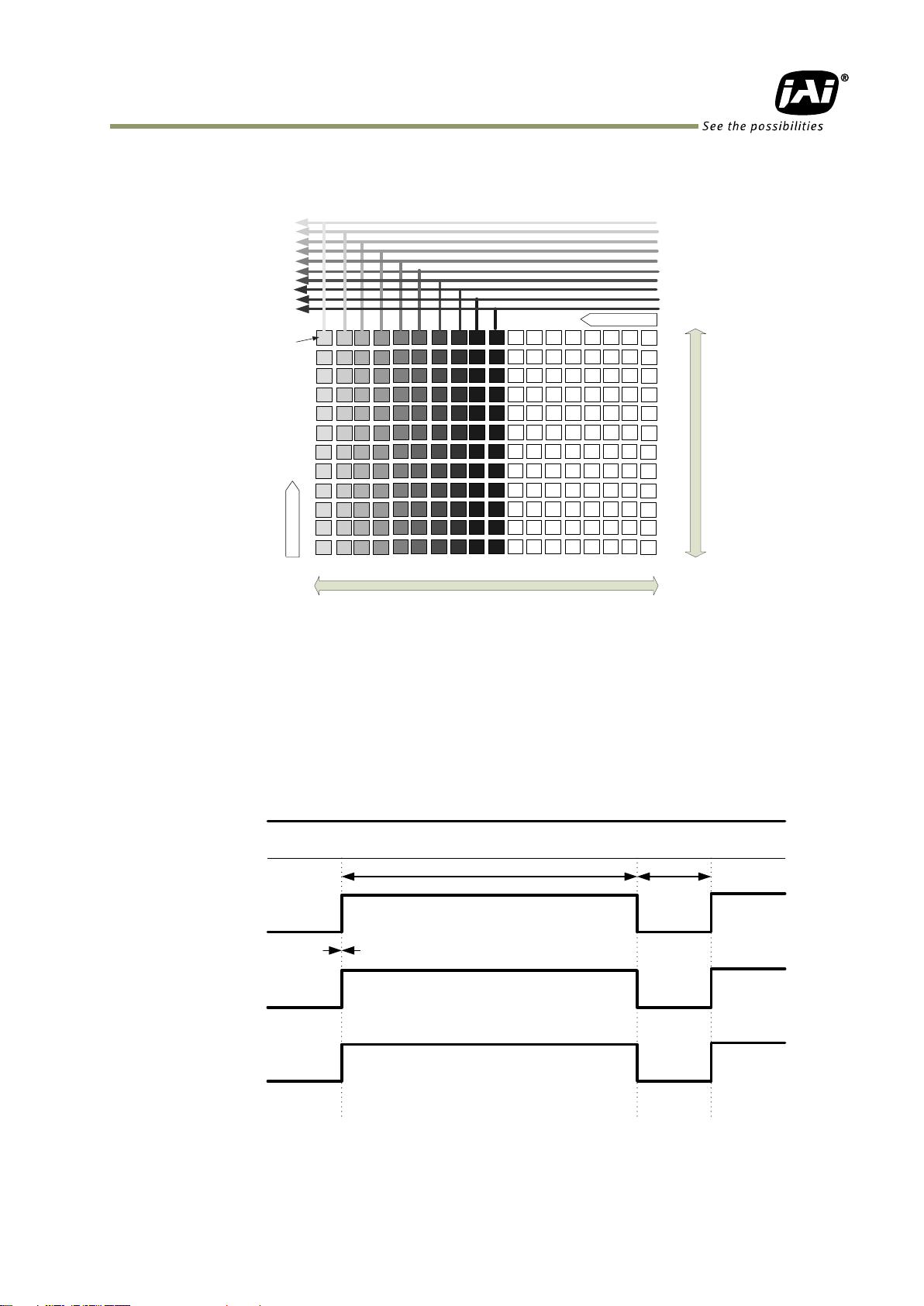

6.2.4 1X10–1Y

1X10-1Y is a 10-tap readout system and outputs as follows.

Fig.15 1X10–1Y Output format

6.3 Output timing and output image

6.3.1 Horizontal timing

The horizontal frequency is changed by setting the Tap Geometry.

In the SP-5000M-PMCL and SP-5000C-PMCL, H-binning is available but the horizontal frequency

is not changed. Therefore, the frame rate is not increased in H-Binning mode.

Fig. 16 Horizontal timing per 1 tap in Camera Link output

- 27 -

Page 30

SP-5000M-PMCL / SP-5000C-PMCL

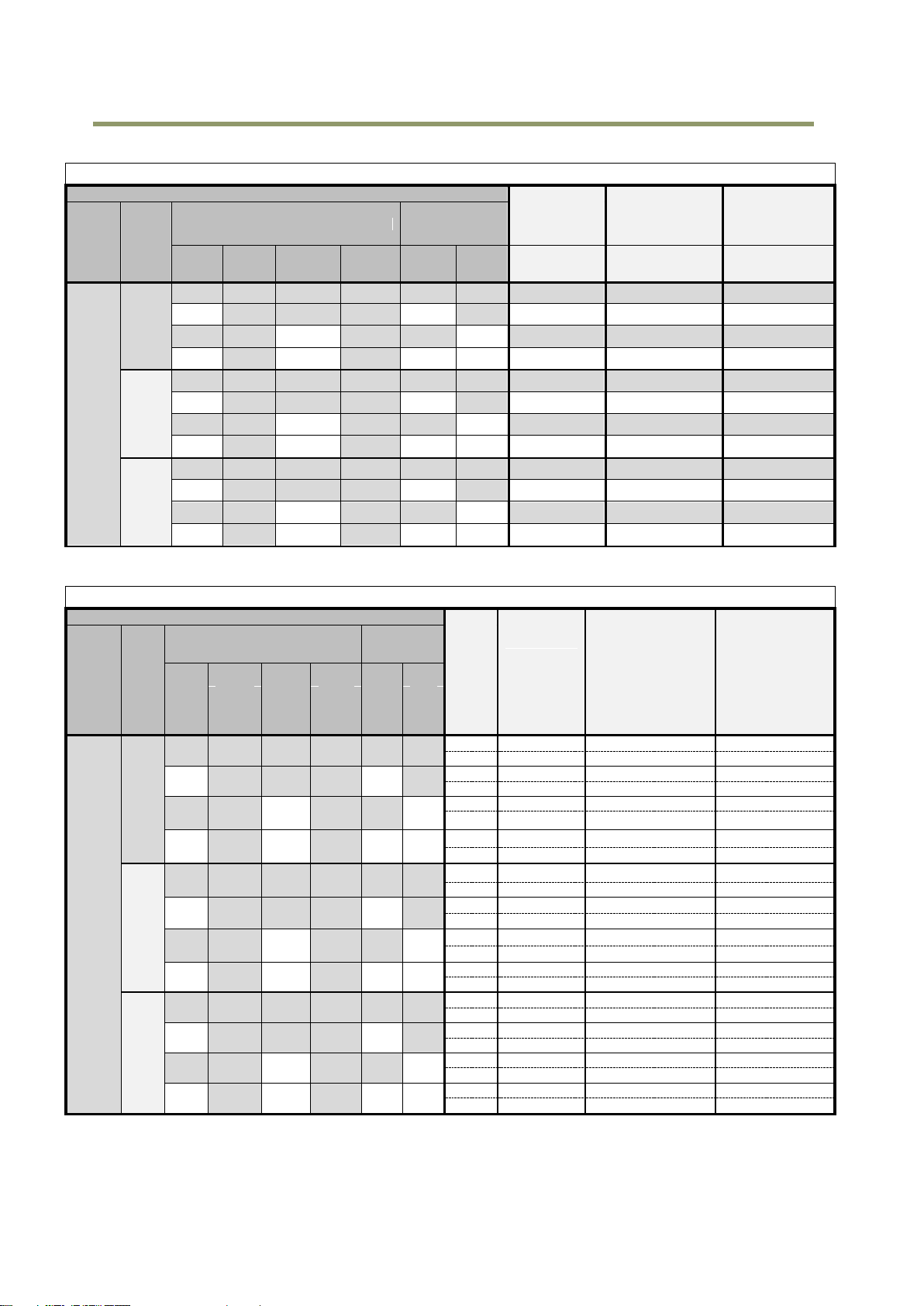

Table 15. Continuous Trigger / Horizontal timing 1X10–1Y (1/2)

Camera Settings

(a)

(b)

(c)

Tap

Geometry

Camera

Link

Pixel

Clock

AOI

Binning 1: OFF

2* ON

LVAL

Active

LVAL

Non-Active

H-Offset

Width

Offset

X

Height

Offset

Y

Horizont

al

Vertical

[Unit:

Clock]

[Unit:

Clock]

[Unit:

Clock]

1X10

-1Y

82.3

MHz

2560 0 2048 0 1 1 256

27 to 30

0

1280 0 2048

0

2

1

128

155 to 158

0

2560 0 1024

0

1

2

256

27 to 30

0

1280 0 1024

0

2

2

128

155 to 158

0

75.4

MHz

2560 0 2048

0

1

1

256

4 to 6

0

1280 0 2048

0

2

1

128

132 to 134

0

2560 0 1024

0

1

2

256

4 to 6

0

1280 0 1024

0

2

2

128

132 to 134

0

61.7

MHz

2560 0 2048

0

1

1

256

4 to 6

0

1280 0 2048

0

2

1

128

132 to 134

0

2560 0 1024

0

1

2

258

4 to 6

0

1280 0 1024

0

2

2

128

132 to 134

0

Table 16. Continuous Trigger / Horizontal timing 1X10–1Y (2/2)

Camera Settings

Tap

Geometry

Camera

Link

Pixel Clock

AOI

Binning

1: OFF

2: ON

1Line

Total

Clock

Horizontal

Frequency

Horizontal

Period

Width

Offset

X

Height

Offset

Y

Hori

zont

al

Verti

cal

[Unit: Clock]

[Unit: kHz]

[Unit: us]

1X10

-1Y

82.3

MHz

2560 0 2048 0 1

1

a

283 to 286

290.763 to 287.713

3.439 to 3.476

b

284.56

289.169

3.458

1280 0 2048 0 2

1

a

283 to 286

290.763 to 287.713

3.439 to 3.476

b

284.56

289.169

3.458

2560 0 1024 0 1

2

a

283 to 286

290.763 to 287.713

3.439 to 3.476

b

284.56

289.169

3.458

1280 0 1024 0 2

2

a

283 to 286

290.763 to 287.713

3.439 to 3.476

b

284.56

289.169

3.458

75.4

MHz

2560 0 2048 0 1

1

a

260 to 262

290.112 to 287.897

3.447 to 3.473

b

260.86

289.155

3.458

1280 0 2048 0 2

1

a

260 to 262

290.112 to 287.897

3.447 to 3.473

b

260.86

289.155

3.458

2560 0 1024 0 1

2

a

260 to 262

290.112 to 287.897

3.447 to 3.473

b

260.86

289.155

3.458

1280 0 1024 0 2

2

a

260 to 262

290.112 to 287.897

3.447 to 3.473

b

260.86

289.155

3.458

61.7

MHz

2560 0 2048 0 1

1

a

260 to 262

237.362 to 235.550

4.213 to 4.245

b

261.00

236.452

4.229

1280 0 2048 0 2

1

a

260 to 262

237.362 to 235.550

4.213 to 4.245

b

261.00

236.452

4.229

2560 0 1024 0 1

2

a

260 to 262

237.362 to 235.550

4.213 to 4.245

b

261.00

236.452

4.229

1280 0 1024 0 2

2

a

260 to 262

237.362 to 235.550

4.213 to 4.245

b

261.00

236.452

4.229

Note: a: Actual operating value b: Calculation value

- 28 -

Page 31

SP-5000M-PMCL / SP-5000C-PMCL

Table 17. Continuous Trigger / Horizontal timing 1X8-1Y (1/2)

Camera Settings

(a)

(b)

(c)

Tap

Geometry

Camera

Link

Pixel Clock

AOI

Binning

LVAL

Active

LVAL

Non-Active

H-Offset

Width

Offset

X

Height

Offset

Y

Horizont

al

Vertical

[Unit:

Clock]

[Unit:

Clock]

[Unit:

Clock]

1X8

-1Y

82.3

MHz

2560 0 2048

0

1

(Off) 1 (Off)

320

4 to 7

0

1280 0 2048

0

2

(On) 1 (Off)

160

164 to 167

0

2560 0 1024

0

1

(Off) 2 (On)

320

4 to7

0

1280 0 1024

0

2

(On) 2 (On)

160

164 to167

0

75.4

MHz

2560 0 2048

0

1

(Off) 1 (Off)

320

4 to 7

0

1280 0 2048

0

2

(On) 1 (Off)

160

164 to 167

0

2560 0 1024

0

1

(Off) 2 (On)

320

4 to 7

0

1280 0 1024

0

2

(On) 2 (On)

160

164 to 167

0

61.7

MHz

2560 0 2048

0

1

(Off) 1 (Off)

320

3 to 5

0

1280 0 2048

0

2

(On) 1 (Off)

164

164

0

2560 0 1024

0

1

(Off) 2 (On)

320

3 to 5

0

1280 0 1024

0

2

(On) 2 (On)

160

164

0

- 29 -

Page 32

SP-5000M-PMCL / SP-5000C-PMCL

Table 18. Continuous Trigger / Horizontal timing 1X8–1Y (2/2)

Camera Settings

Tap

Geometry

Camera

Link

Pixel Clock

AOI

Binning

1Line

Total

Clock

Horizontal

Frequency

Horizontal

Period

Width

Offset

X

Height

Offset

Y

Horiz

ontal

Verti

cal

[Unit: Clock]

[Unit: kHz]

[Unit: us]

1X8

-1Y

82.3

MHz

2560

0

a

b

0

1

(Off) 1 (Off)

a

324 to 327

253.969 to

3.937 to 3.974

b

325.71

252.639

3.958

1280

0

a

b

0

2

(On) 1 (Off)

a

324 to 327

253.969 to

3.937 to 3.974

b

325.71

252.639

3.958

2560

0

a

b

0

1

(Off) 2 (On)

a

324 to 327

253.969 to

3.937 to 3.974

b

325.71

252.639

3.958

1280

0

a

b

0

2

(On) 2 (On)

a

324 to 327

253.969 to

3.937 to 3.974

b

325.71

252.639

3.958

75.4

MHz

2560

0

a

b

0

1

(Off) 1 (Off)

a

324 to 327

232.806 to 230.670

4.295 to 4.335

b

325.29

231.882

4.313

1280

0

a

b

0

2

(On) 1 (Off)

a

324 to 327

232.806 to 230.670

4.295 to 4.335

b

325.29

231.882

4.313

2560

0

a

b

0

1

(Off) 2 (On)

a

324 to 327

232.806 to 230.670

4.295 to 4.335

b

325.29

231.882

4.313

1280

0

a

b

0

2

(On) 2 (On)

a

324 to 327

232.806 to 230.670

4.295 to 4.335

b

325.29

231.882

4.313

61.7

MHz

2560

0

a

b

0

1

(Off) 1 (Off)

a

323 to 325

191.065 to 189.889

5.234 to 5.266

b

324.00

190.475

5.250

1280

0

a

b

0

2

(On) 1 (Off)

a

328

188.152

5.315

b

324.00

190.475

5.250

2560

0

a

b

0

1

(Off) 2 (On)

a

323 to 325

191.065 to 189.889

5.234 to 5.266

b

324.00

190.475

5.250

1280 0 a

0

2

(On) 2 (On)

a

328

188.152

5.315

b

324.00

190.475

5.250

Note: a: Actual operating value b: Calculation value

- 30 -

Page 33

SP-5000M-PMCL / SP-5000C-PMCL

Table 19. Continuous Trigger / Horizontal timing 1X4–1Y (1/2)

Camera Settings

(a)

(b)

(c)

Tap

Geometry

Camera Link

Pixel Clock

AOI

Binning

LVAL

Active

LVAL

Non-Active

H-Offset

Width

Offset

X

Height

Offset

Y

Horizont

al

Vertical

[Unit:

Clock]

[Unit:

Clock]

[Unit:

Clock]

1X4

-1Y

82.3

MHz

2560 0 2048

0

1

(Off) 1 (Off)

640

3 to 6

0

1280 0 2048

0

2

(On) 1 (Off)

320

323 to 326

0

2560 0 1024

0

1

(Off) 2 (On)

640

3 to 6

0

1280 0 1024

0

2

(On) 2 (On)

320

323 to 326

0

75.4

MHz

2560 0 2048

0

1

(Off) 1 (Off)

640

3 to 6

0

1280 0 2048

0

2

(On) 1 (Off)

320

323 to 326

0

2560 0 1024

0

1

(Off) 2 (On)

640

3 to 6

0

1280 0 1024

0

2

(On) 2 (On)

320

323 to 326

0

61.7

MHz

2560 0 2048

0

1

(Off) 1 (Off)

640

4 to 7

0

1280 0 2048

0

2

(On) 1 (Off)

320

324 to 327

0

2560 0 1024

0

1

(Off) 2 (On)

640

4 to 7

0

1280 0 1024

0

2

(On) 2 (On)

320

324 to 327

0

- 31 -

Page 34

SP-5000M-PMCL / SP-5000C-PMCL

Table 20. Continuous Trigger / Horizontal timing 1X4–1Y (2/2)

Camera Settings

Tap

Geometry

Camera

Link

Pixel Clock

AOI

Binning

1Line

Total

Clock

Horizontal

Frequency

Horizontal

Period

Width

Offset

X

Height

Offset

Y

Horiz

ontal

Verti

cal

[Unit: Clock]

[Unit: kHz]

[Unit: us]

1X4

-1Y

82.3

MHz

2560 0 2048

0

1

(Off) 1 (Off)

a

643 to 646

127.972 to 127.378

7.814 to 7.851

b

644.57

127.632

7.835

1280 0 2048

0

2

(On) 1 (Off)

a

643 to 646

127.972 to 127.378

7.814 to 7.851

b

644.57

127.632

7.835

2560 0 1024

0

1

(Off) 2 (On)

a

643 to 646

127.972 to 127.378

7.814 to 7.851

b

644.57

127.632

7.835

1280 0 1024

0

2

(On) 2 (On)

a

643 to 646

127.972 to 127.378

7.814 to 7.851

b

644.57

127.632

7.835

75.4

MHz

2560 0 2048

0

1

(Off) 1 (Off)

a

643 to 646

117.308 to 116.861

8.525 to 8.557

b

644.29

117.073

8.542

1280 0 2048

0

2

(On) 1 (Off)

a

643 to 646

117.308 to 116.861

8.525 to 8.557

b

644.29

117.073

8.542

2560 0 1024

0

1

(Off) 2 (On)

a

643 to 646

117.308 to 116.861

8.525 to 8.557

b

644.29

117.073

8.542

1280 0 1024

0

2

(On) 2 (On)

a

643 to 646

117.308 to 116.861

8.525 to 8.557

b

644.29

117.073

8.542

61.7

MHz

2560 0 2048

0

1

(Off) 1 (Off)

a

644 to 647

95.829 to 95.385

10.435 to 10.484

b

645.43

95.617

10.458

1280 0 2048

0

2

(On) 1 (Off)

a

644 to 647

95.829 to 95.385

10.435 to 10.484

b

645.43

95.617

10.458

2560 0 1024

0

1

(Off) 2 (On)

a

644 to 647

95.829 to 95.385

10.435 to 10.484

b

645.43

95.617

10.458

1280 0 1024

0