IXYS IXFN80N50, IXFN75N50 Datasheet

HiPerFET

TM

V

DSS

I

D25

R

DS(on)

Power MOSFETs

Single Die MOSFET

IXFN 80N50 500 V 80 A 50 m

IXFN 75N50 500 V 75 A 55

D

N-Channel Enhancement Mode

Avalanche Rated, High dv/dt, Low t

rr

Symbol Test Conditions Maximum Ratings

V

DSS

V

DGR

V

GS

V

GSM

I

D25

I

DM

I

AR

E

AR

E

AS

dv/dt I

P

D

T

J

T

JM

T

stg

V

ISOL

M

d

T

= 25°C to 150°C 500 V

J

T

= 25°C to 150°C; RGS = 1 MΩ 500 V

J

Continuous ±20 V

Transient ±30 V

T

= 25°C, Chip capability 75N50 75 A

C

T

= 25°C, pulse width limited by T

C

T

= 25°C

C

T

= 25°C64mJ

C

T

= 25°C6J

C

≤ IDM, di/dt ≤ 100 A/µs, VDD ≤ V

S

T

≤ 150°C, RG = 2 Ω

J

T

= 25°C 700 W

C

DSS

80N50 80 A

75N50 300 A

JM

80N50 320 A

, 5 V/ns

-55 ... +150 °C

50/60 Hz, RMS t = 1 min 2500 V~

I

≤ 1 mA t = 1 s 3000 V~

ISOL

Mounting torque 1.5/13 Nm/lb.in.

Terminal connection torque 1.5/13 Nm/lb.in.

Weight 30 g

Symbol Test Conditions Characteristic Values

(T

= 25°C, unless otherwise specified)

V

V

I

I

R

GSS

DSS

DSS

GH(th)

DS(on)

J

VGS= 0 V, ID = 3 mA 500 V

VDS= VGS, ID = 8 mA 2 4 V

V

= ±20 V

GS

VDS= V

VGS= 0 V T

VGS= 10 V, ID = 0.5 I

Pulse test, t ≤ 300 µs, 75N50 55 mΩ

DSS

, V

= 0 ±200 nA

DC

DS

T

= 25°C 100 µA

J

= 125°C2mA

J

80N50 50 mΩ

D25

min. typ. max.

duty cycle d ≤ 2 %

G

S

S

80 A

150 °C

-55 ... +150 °C

ΩΩ

Ω

ΩΩ

ΩΩ

Ω

m

ΩΩ

miniBLOC, SOT-227 B (IXFN)

E153432

S

G

S

D

G = Gate D = Drain

S = Source

Either Source terminal of miniBLOC can be used

as Main or Kelvin Source

Features

•International standard packages

•miniBLOC, with Aluminium nitride

isolation

•Low R

HDMOSTM process

DS (on)

•Rugged polysilicon gate cell structure

•Unclamped Inductive Switching (UIS)

rated

•Low package inductance

•Fast intrinsic Rectifier

Applications

• DC-DC converters

• Battery chargers

• Switched-mode and resonant-mode

power supplies

• DC choppers

• Temperature and lighting controls

Advantages

• Easy to mount

• Space savings

• High power density

© 2002 IXYS All rights reserved

98538C (02/02)

IXFN 75N50

IXFN 80N50

Symbol Test Conditions Characteristic Values

= 25°C, unless otherwise specified)

(T

g

C

C

C

t

t

t

t

Q

Q

Q

R

R

fs

iss

oss

rss

d(on)

r

d(off)

f

g(on)

gs

gd

thJC

thCK

J

VDS = 15 V; ID = 0.5 • I

, pulse test 50 70 S

D25

VGS = 0 V, VDS = 25 V , f = 1 MH z 1750 pF

VGS = 10 V, VDS = 0.5 • V

, ID = 0.5 • I

DSS

RG = 1 Ω (External), 102 ns

VGS = 10 V, VDS = 0.5 • V

, ID = 0.5 • I

DSS

min. typ. max.

9890 pF

460 pF

61 ns

D25

70 ns

27 ns

380 nC

D25

80 nC

173 nC

0.18 K/W

0.05 K/W

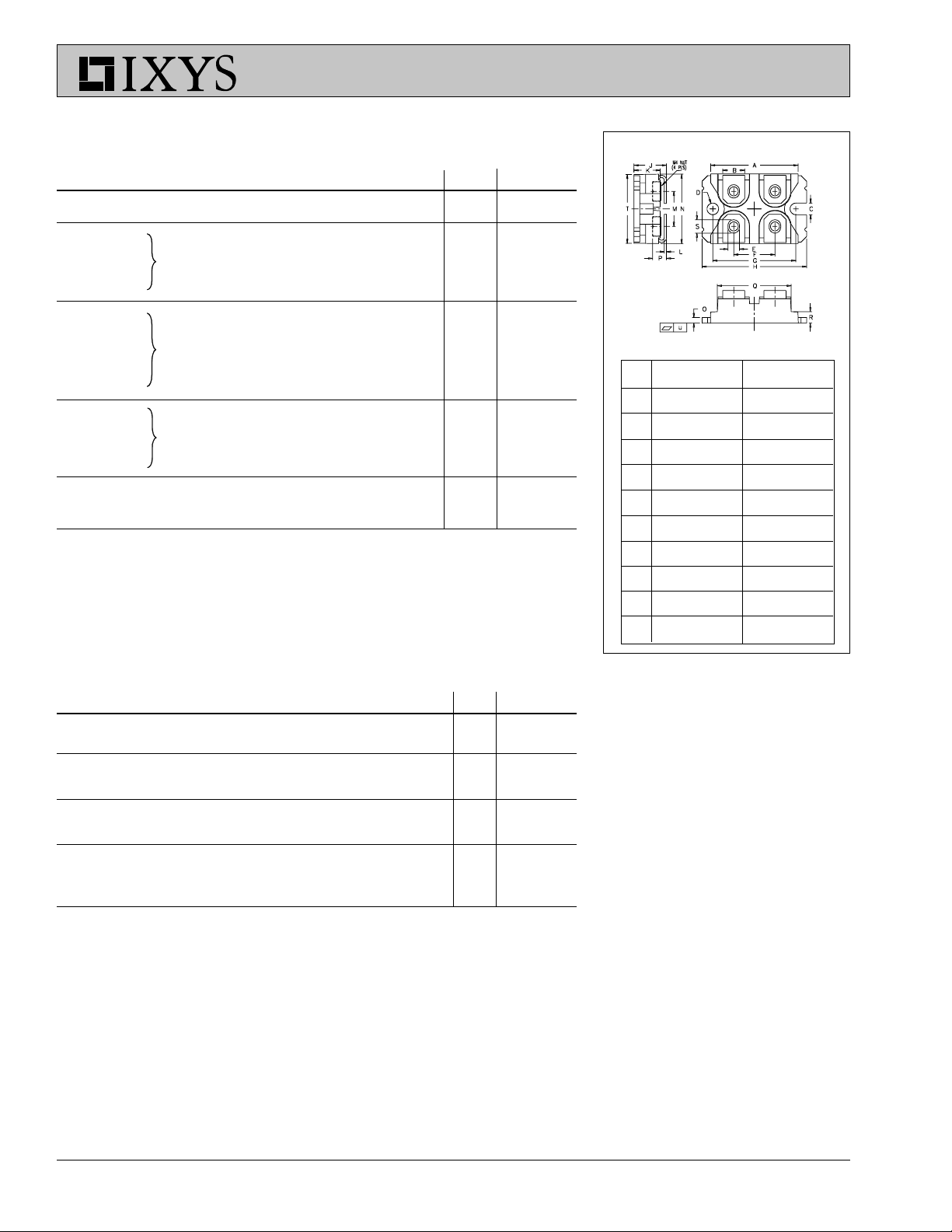

miniBLOC, SOT-227 B

M4 screws (4x) supplied

Dim. Millimeter Inches

Min. Max. Min. Max.

A 31.50 31.88 1.240 1.255

B 7.80 8.20 0.307 0.323

C 4.09 4.29 0.161 0.169

D 4.09 4.29 0.161 0.169

E 4.09 4.29 0.161 0.169

F 14.91 15.11 0.587 0.595

G 30.12 30.30 1.186 1.193

H 38.00 38.23 1.496 1.505

J 11.68 12.22 0.460 0.481

K 8.92 9.60 0.351 0.378

L 0.76 0.84 0.030 0.033

M 12.60 12.85 0.496 0.506

N 25.15 25.42 0.990 1.001

O 1.98 2.13 0.078 0.084

P 4.95 5.97 0.195 0.235

Q 26.54 26.90 1.045 1.059

R 3.94 4.42 0.155 0.174

S 4.72 4.85 0.186 0.191

T 24.59 25.07 0.968 0.987

U -0.05 0.1 -0.002 0.004

Source-Drain Diode Characteristic Values

(TJ = 25°C, unless otherwise specified)

Symbol Test Conditions min. typ. max.

I

S

I

SM

V

SD

VGS= 0 V 75N50 75 A

80N50 80 A

Repetitive; 75N50 300 A

pulse width limited by TJM80N50 320 A

IF = IS, VGS = 0 V, 1.3 V

Pulse test, t ≤ 300 µs, duty cycle d ≤ 2 %

t

rr

Q

RM

I

RM

IF = 30A, -di/dt = 100 A/µs, VR = 100 V 250 ns

1.2 µC

8A

IXYS reserves the right to change limits, test conditions, and dimensions.

IXYS MOSFETS and IGBTs are covered by one or more of the following U.S. patents: 4,835,592 4,881,106 5,017,508 5,049,961 5,187,117 5,486,715 6,306,728B1

4,850,072 4,931,844 5,034,796 5,063,307 5,237,481 5,381,025

Loading...

Loading...