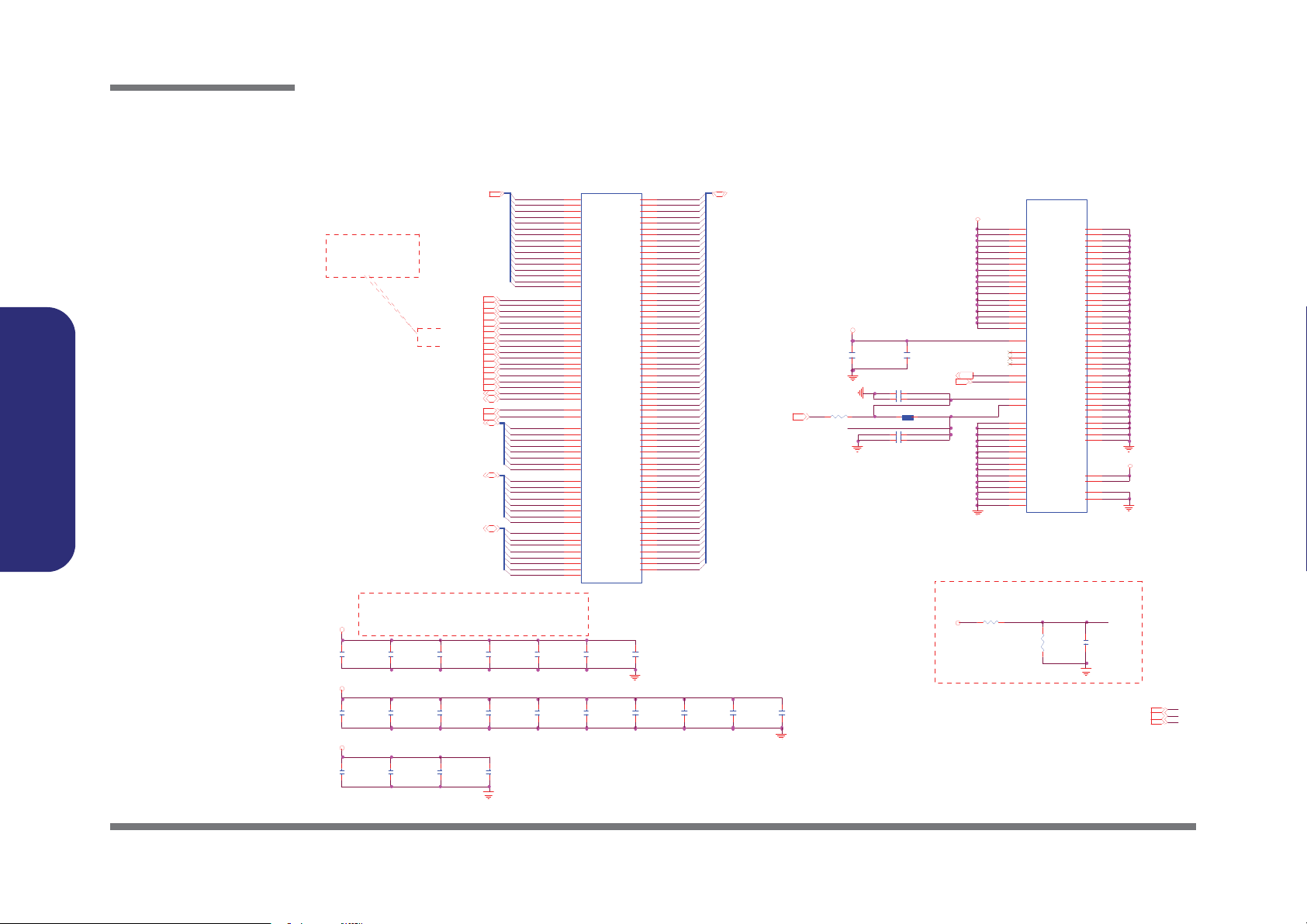

ITAUTEC W7425 Schematics

Schematic Diagrams

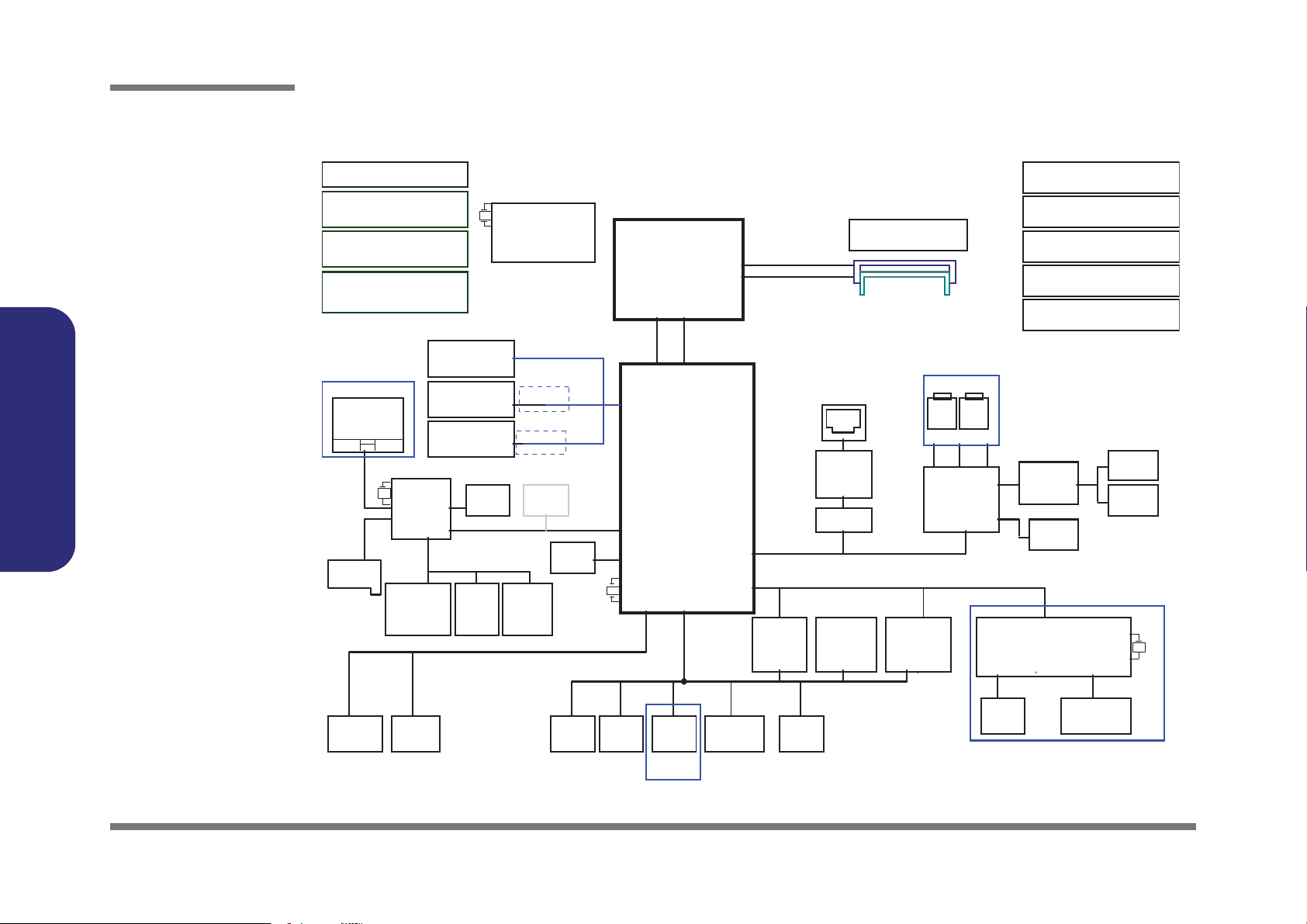

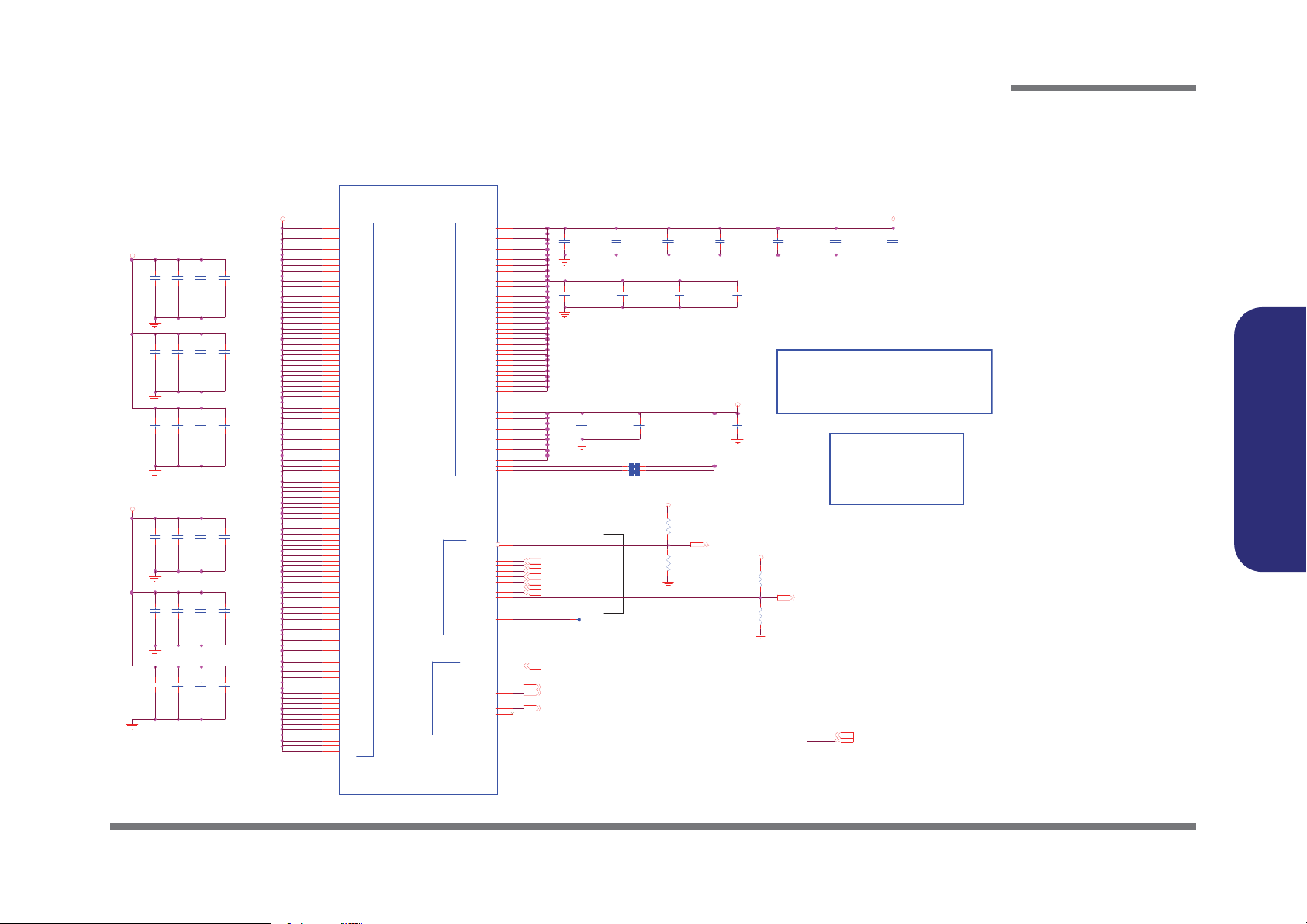

Ca l pe l la System Blo ck Diagram

POWER SWIT CH +H OTKEY X 3

(USB2)

Clock Generato r

New Card

(USB11)

LCD CONNEC TO R, <8"

TO UC H PA D

CR T CO NN EC TO R

LPC

CAR D READER

P OWE R GP U

SMART

BATTERY

SO-DIMM1

INT SPK R

CLICK BOARD

SOCKET

<=8"

Memory Termination

PCIE

27x27mm

1071 Ball FCBGA

480 Mbps

DDRIII

Synaptic

Mini PCIE

RTM875N-632-VB -GRT

14.318 MHz

7IN1

SPI

0.5"~6.5"

1"~16"

DDRIII

INT MIC

25

MHz

Arrandale

USB0 Bluetooth

24 MHz

<12"

FDI

HDMI

AZALIA

MDC

MODULE

SHEET 11

INT SPK L

128pins LQFP

SO-DIMM0

32.768KHz

MDC CON

SYSTEM SM BUS

BIOS

SPI

LAN

IT E 85 02 E

<12"

SATA HDD

Ibex Peak-M

Platform

Controller

H ub (P CH)

SATA ODD

INT. K/B

CLICK BOA RD

Azalia CodecEC

0.5"~11"

RJ-11

SOCKET

<15"

5V,3V,5VS,3VS,1.5VS,

USB2.0

CR T SWITCH

LVDS SWITCH

RJ-45

USB1

VDD3,VDD5

DMI*4

810602-1703

SMART

FAN

(USB5)

JMC251 C

AUDIO

BOARD

B.Schematic Diagrams

B - 2 System Block Diagram

Sheet 1 of 42

System Block

Diagram

System Block Diagram

6-71-E51 Q2 -D 01A

POWER SWITCH BOARD

6-71-E51 QS -D 01A

AUDIO BOA RD

USB+EARP HO NE +EXT.MIC

6-71-C45 08 -D 02A

EXTERNA L ODD BOARD

EXT. ODD

6-71-E51 QN -D 01

32.768 KHz

14*14*1.6mm

EC SMBUS

THERMAL

SENSOR

W83L771AWG

SA TA I/ II 3 .0G b/ s

TPM

http://hobi-elektronika.net

INTERNAL

GRAPHICS

INTERNAL

GRAPHICS

33 MHz

PROCESSOR

rPGA989/988

USB4

800/1067 MHz

DDR3 / 1.5V

0.1"~13

AZALIA LINK

SOCKET

(USB3)

CCD

100 MHz

3G CA RD

(USB9)

AU DI O BO AR D

HP

MI C

OUT

IN

VI A VT 18 12

1.8VS

1.5V,0.75VS(VTT_MEM)

VCORE 1.1VS_VTT

AMP

N7101

JMICRO

Clock Generator

C LO CK GE NE RA TO R

100MHz100MHz1(0.7V-1.5V)

0(default)

PIN_30 CPU_1CPU_0

133MHz133MHz

R137 10K_04

CP U_SEL_During CK_P EWGD Latch Pinl

CLK_ SDATA

CLK_ SCL K

CLK_PW RG D

SMBu s

CLK_ SDATA

CLK_ SCL K

3.3VS

SMB_DATA15

SMB_CLK15

CLK_SDATA 10 ,11

CLK_SCLK 1 0,11

L15 *15m il_short_06

L14 *15mil_short_06

3.3V 3,4,12,14,15,16,18,19,20,21,23,24,25,29,30, 31,33,34,35

REF _ 0 /CP U_ S EL

5VS

S

D

G

Q1 1A

MT D N 70 0 2Z H S6 R

2

6

1

S

D

G

Q1 1B

MT D N 70 0 2Z H S6 R

5

3

4

RE F_0/CPU _ S EL

0.1uF near the every power pin

CLKG EN POWER

0.1uF near the every power pin

VDD_I/O can be

ranging from

1.05V to 3.3V

5V S 1 3 , 17 , 2 0, 2 1 , 2 6 ,2 7 , 3 0, 3 1 , 35 , 3 6

EMI Capactior

EMI

XIN

Slego SLG8SP585 6-02-08585-EQ0

Realtek RTM875N-632-VB-GRT

C20 5

0.1u_16V_Y5V_04

R149

10K_1% _04

C207

1u_6.3V_X5R _04

X1 HSX530G_1 4.31 818 M Hz

12

C199

33 p _5 0 V _ N P O _ 0 4

R146

1M_04

C202

33p_50V_N PO_04

Q1 2

MTN7002ZHS3

G

DS

C206

0.1u_16V_Y5V_04

C19 6

1u_6.3V_X5R_04

C197

0.1u_16V_Y 5V_04

CPU _STO P #

REF_0/CPU_SEL C 194 *10p_50V _NPO_06

U7

SLG 8SP585

VD D_ DO T

1

VD D_ 2 7

5

VD D_ SRC

17

VD D_ CPU

24

VD D_ REF

29

VSS _DOT

2

XTAL _O UT

27

XTAL _IN

28

R EF_ 0/C PU_SEL

30

SD A

31

SC L

32

VSS _27

8

VSS _SATA

9

VSS _SRC

12

VSS _CPU

21

VSS _REF

26

V DD_ SR C_ I/O

15

V DD_ CP U_ I/O

18

DOT_96

3

DO T_96#

4

27M

6

27M_SS

7

SRC _1 /SATA

10

S RC_1 #/S ATA#

11

SRC _2

13

SR C_2#

14

CPU_ ST OP#

16

CPU _1

20

CP U_ 1#

19

CPU _0

23

CP U_ 0#

22

CK P W RGD /PD#

25

GND

33

3.3VS

CLK _ V CC 2CLK_VCC 1

CLK_VCC2

3.3VS

CLK_ VCC1

1.1VS_V TT

3.3VS

3.3VS

CLK_BUF_DOT96_N 15

CLK_ BUF_R EF1415

CLK _BUF_DOT96_P 15

CLK_BUF_BCLK_N 15

CLK_BUF_BCLK_P 15

1.1 VS _ VT T 4 ,6 ,7 ,14,1 5 ,16,19, 20,2 1,34, 3 5,36

3.3 VS 10 ,11,1 2,13,1 4,15 ,1 6,17 ,18,19 ,20,2 1 ,23,2 4,25,2 6,27 ,2 8,29,30,3 1 ,35,3 6

CLK _SATA 15

CLK _PCIE_ICH# 15

CLK _PCIE_ICH 15

CLKE N #36

CLK _SATA# 15

XO U T

XI N

R134 33_04

RN 15

2.2K_4P2R_04

1 4

2 3

R 1 48 2. 2 1 K _1 % _ 04

6-22-14R31-1B7

6-22-14R31-1B6

XOUT

R136 *4.7K_04

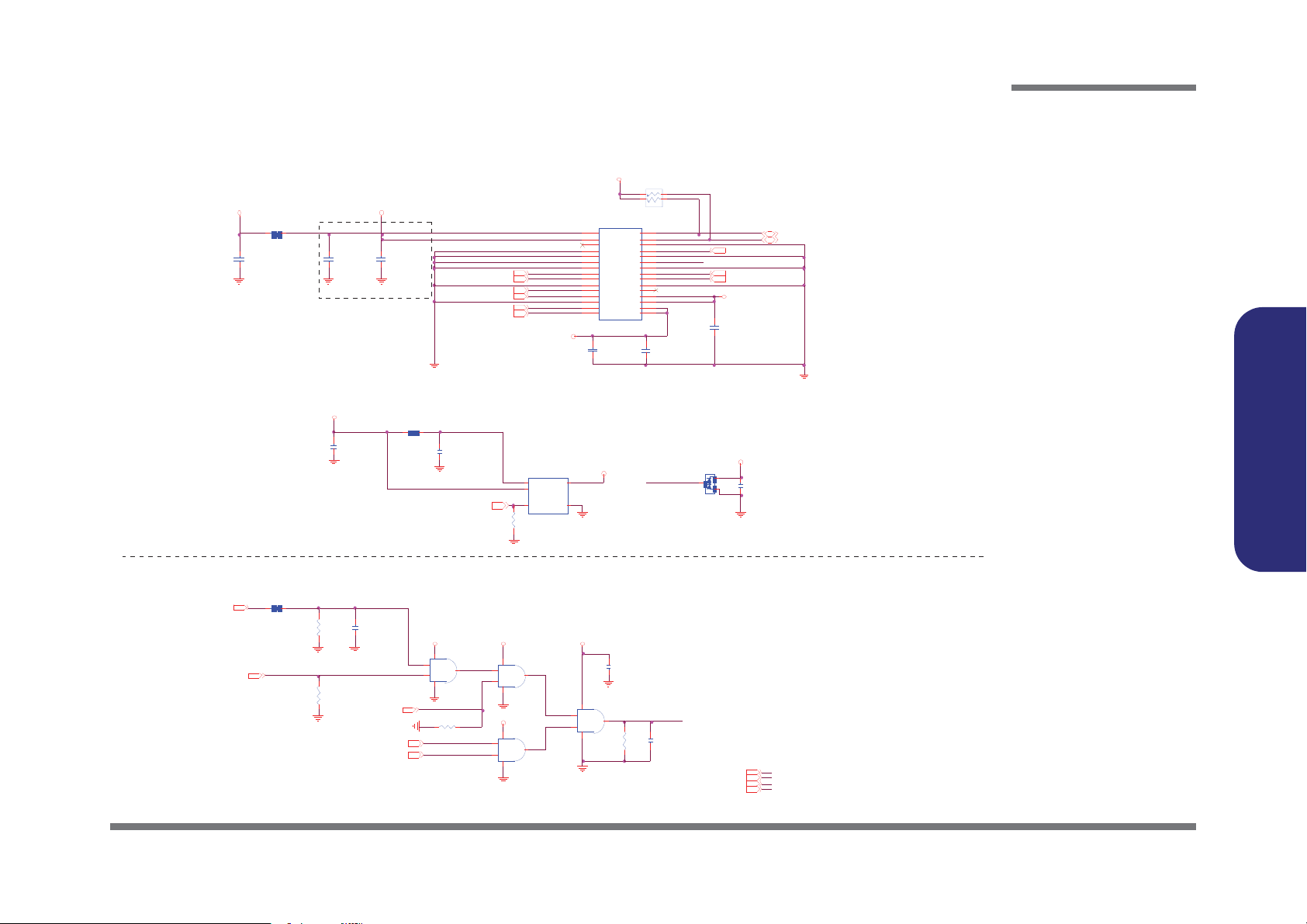

Sheet 2 of 42

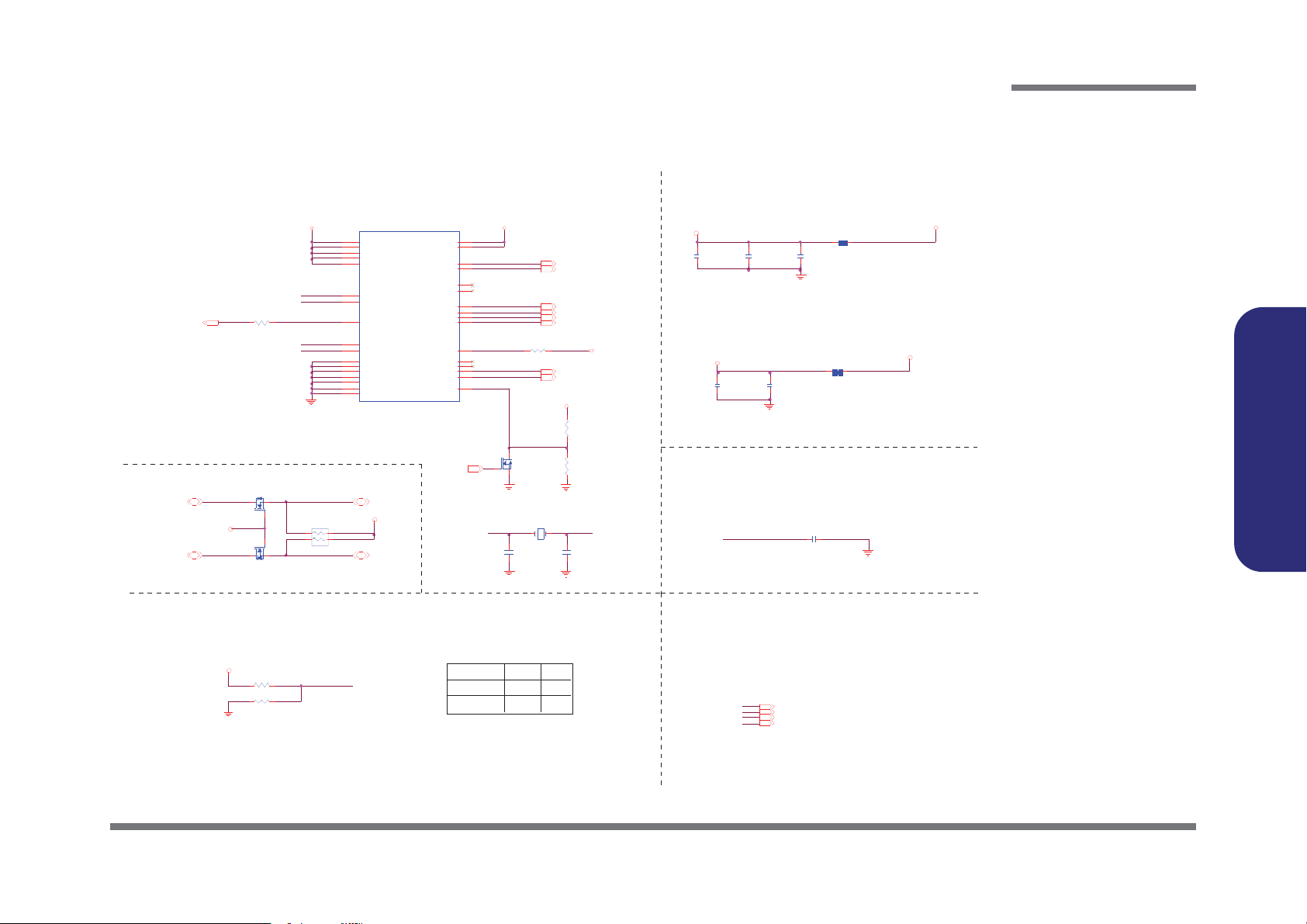

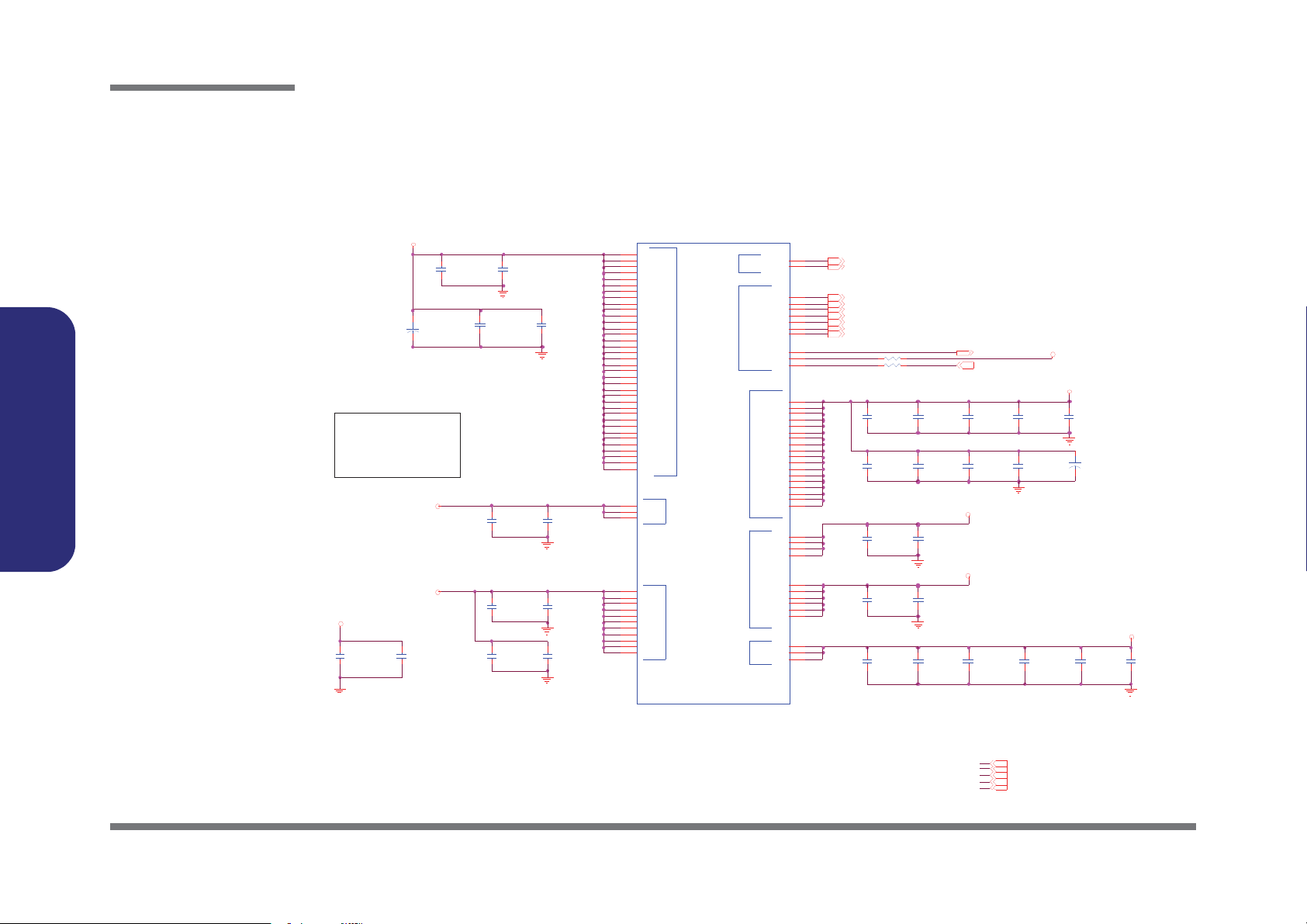

Clock Generator

Schematic Diagrams

B.Schematic Diagrams

http://hobi-elektronika.net

Clock Generator B - 3

Schematic Diagrams

Sheet 3 of 42

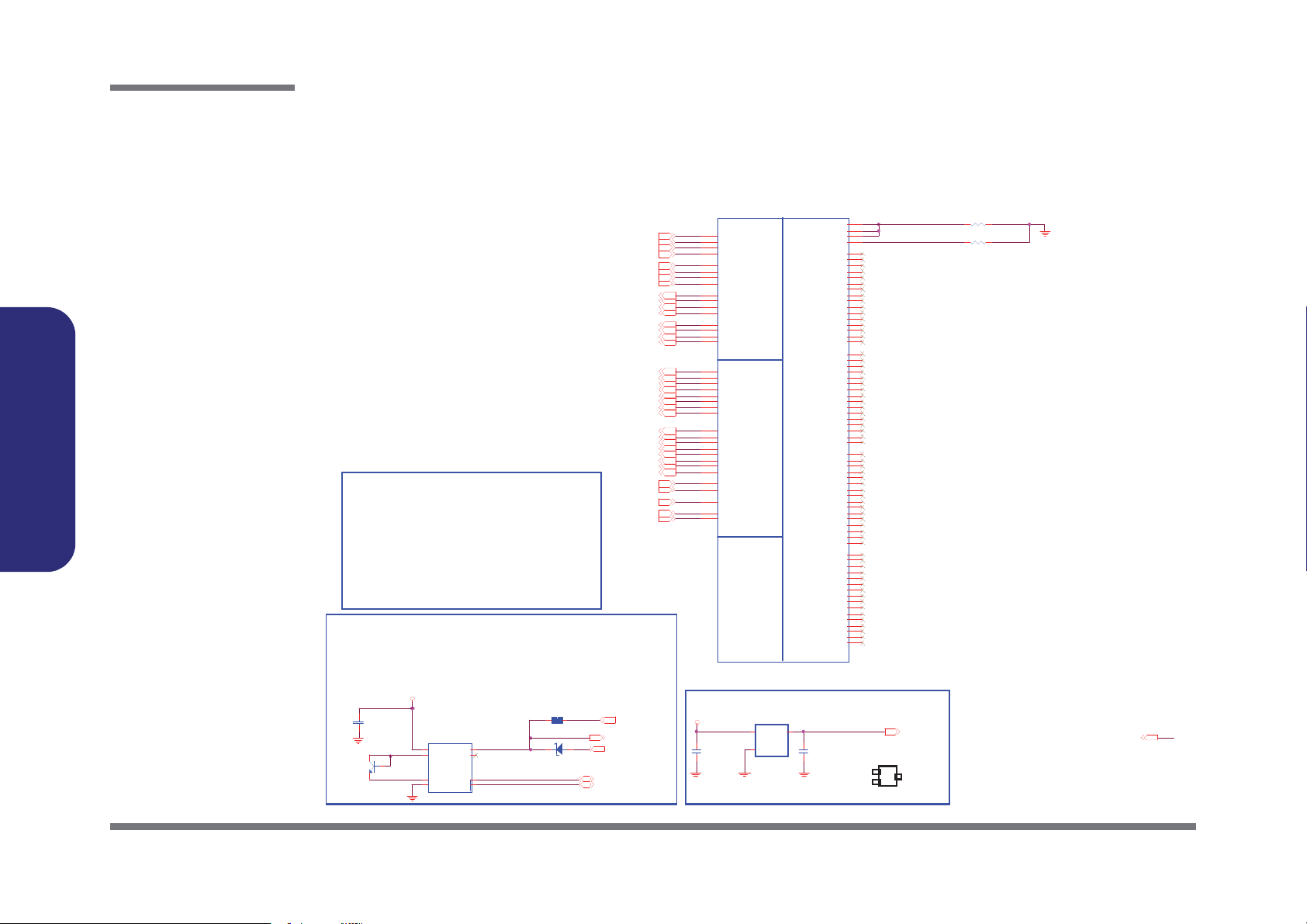

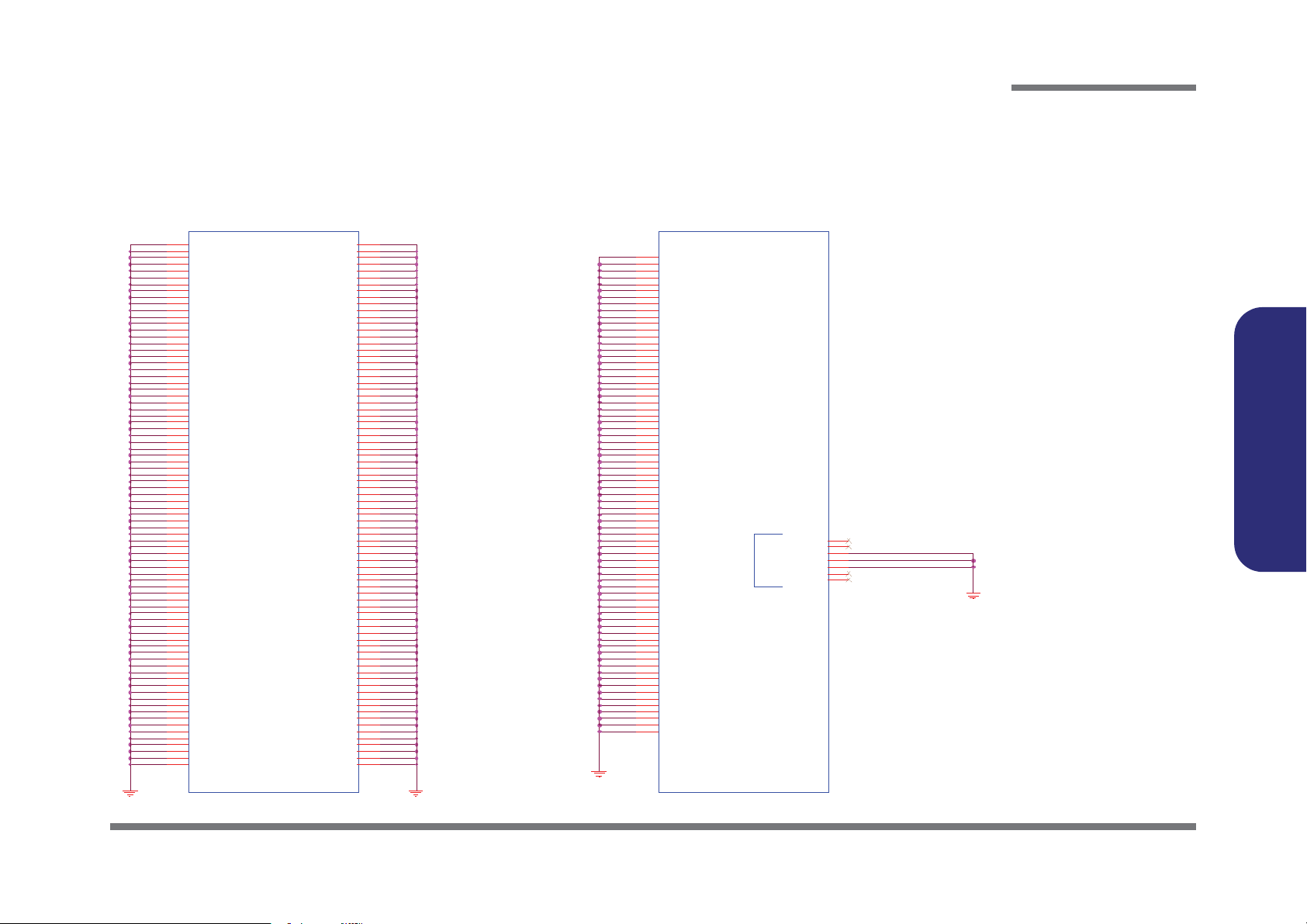

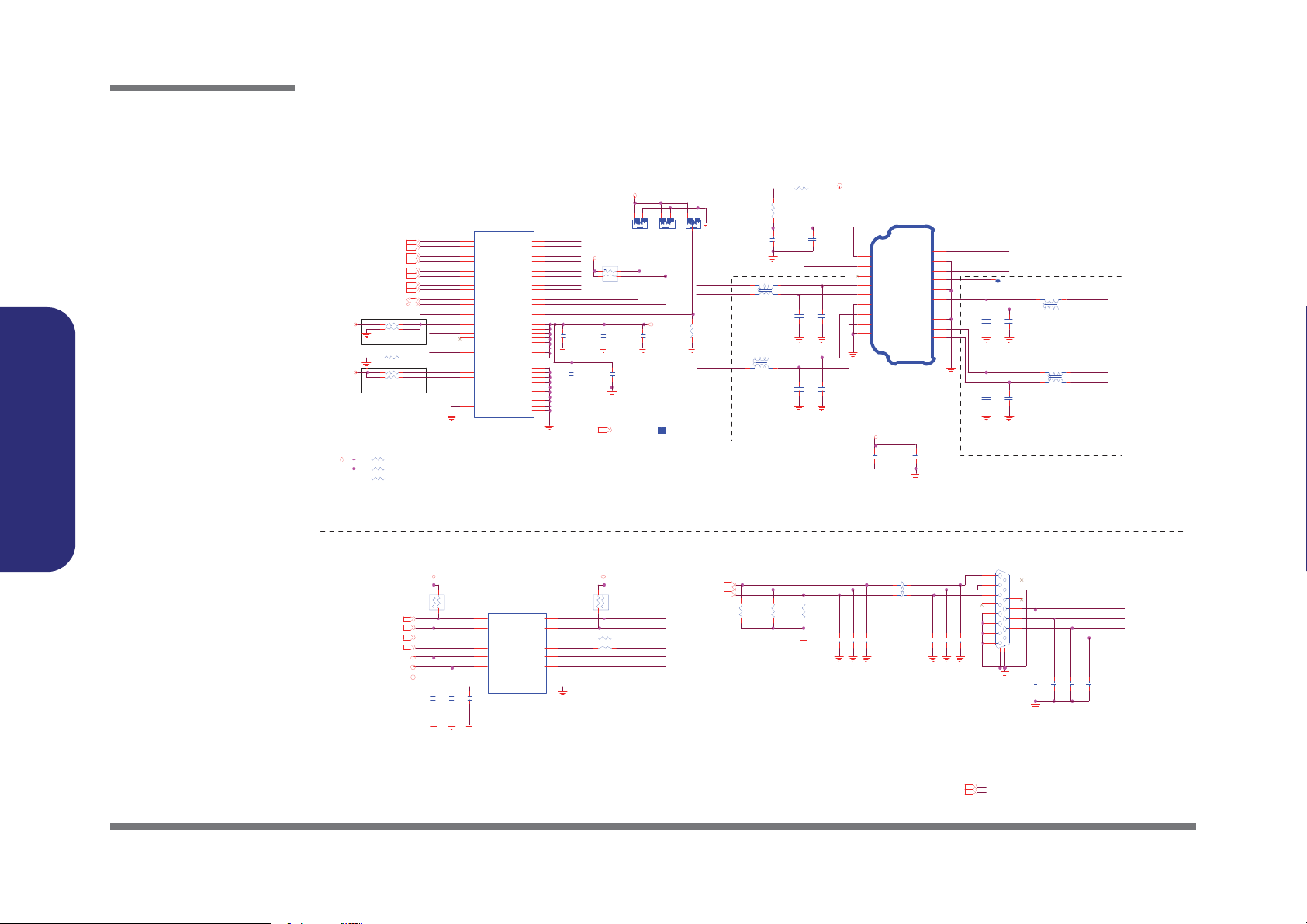

CPU 1/7

(DMI, PEG, FDI)

PR OCESSOR 1/7 ( DMI,PEG,FDI )

It applies to Auburndale and Clarksfield discrete graphic designs.

If discrete graphic chip is used for Aub urndale, VAXG (GFX core) rail can be conne cted

to GND if motherboard only supports discrete gr aphics and also in a common

motherboard design if GFX VR is not stuffed. On the other han d, if the VR is stuffed,

VAXG can be left floating in a common motherboard design (Gfx VR keeps VAXG from

floating).

In addition, FDI_RXN_[7:0] and FDI_RXP_

[7:0] ca

n be left floa ting on the PCH.

FDI_TX[7:0] and FDI_TX#[7 :0] can be left floating on the Auburndale.

The GFX_IMON, FDI_FSYNC[0], FDI _FSYNC[1], FDI_LSYNC[0], FDI_LSYNC[1], and

FDI_INT signals should be tied to GND (through 1K ? % resistors) in the common

motherboard design case. Please not that if these signals are left floating, there are no

functional impacts but a small amount of power (~15 mW) maybe wasted. VAXG_SENSE

and VSS

AXG_SE

NSE on

Auburndale can be left as no connect.

DPLL_REF_SSCLK and DPLL_REF_SSCLK# can be connected to GND on Auburndale

directly if motherboard only supports discrete graphics. In a common motherboard

design, these pins are driven via PCH (even if Graphics is dis abled by BIOS) thus no

external termination is required.

CPU 1/7 (DMI, PEG, FDI)

B.Schematic Diagrams

The rmal Sensor near U16

3.3V

C357

*0.1u_16V_Y5V_04

Q10

*2 N3 9 0 4

E C

U18

1

VDD

2

B

D+

3

D-

5

GN D

*W 8 3L 7 71 A W G

THE RM

ALER T

SDA TA

SC LK

U16A

A24

C23

DM I_TXN016

DM I_TXN116

DM I_TXN216

DM I_TXN316

DM I_TXP016

DM I_TXP116

DM I_TXP216

DM I_TXP316

DMI_RXN016

DMI_RXN116

DMI_RXN216

DMI_RXN316

DMI_RXP 016

DMI_RXP 116

DMI_RXP 216

DMI_RXP 316

FD I_TXN 016

FD I_TXN 116

FD I_TXN 216

FD I_TXN 316

FD I_TXN 416

FD I_TXN 516

FD I_TXN 616

FD I_TXN 716

FD I_TXP016

FD I_TXP116

FD I_TXP216

FD I_TXP316

FD I_TXP416

FD I_TXP516

FD I_TXP616

FD I_TXP716

FDI_FSY NC 016

FDI_FSY NC 116

FDI_ IN T16

FDI_LSYN C016

FDI_LSYN C116

R 228 * 10m il_short_04

4

6

7

8

AC

D16 *C DBU 0 03 4 0

CRIT_TEMP_REP# 19

THER M_AL ER T # 28

PM _EXT TS# _EC 4

SM D_CPU _T HER M 1 5,28

SM C_CPU _T HER M 1 5,28

DM I _ RX# [ 0 ]

DM I _ RX# [ 1 ]

B22

DM I _ RX# [ 2 ]

A21

DM I _ RX# [ 3 ]

B24

D23

DM I _ RX[0 ]

DM I _ RX[1 ]

B23

DM I _ RX[2 ]

A22

DM I _ RX[3 ]

D24

DM I _ T X# [0 ]

G24

DM I _ T X# [1 ]

F23

H23

DM I _ T X# [2 ]

DM I _ T X# [3 ]

D25

DM I_ T X[0 ]

F24

DM I_ T X[1 ]

E23

DM I_ T X[2 ]

G23

DM I_ T X[3 ]

E22

FD I_TX#[0]

D21

FD I_TX#[1]

D19

FD I_TX#[2]

D18

G21

FD I_TX#[3]

FD I_TX#[4]

E19

F21

FD I_TX#[5]

FD I_TX#[6]

G18

FD I_TX#[7]

D22

C21

FD I_TX [0 ]

FD I_TX [1 ]

D20

C18

FD I_TX [2 ]

FD I_TX [3 ]

G22

E20

FD I_TX [4 ]

FD I_TX [5 ]

F20

FD I_TX [6 ]

G19

FD I_TX [7 ]

F17

FD I_F SYN C[0]

E17

FD I_F SYN C[1]

C17

FD I_IN T

F18

FD I_LSY NC [0]

D17

FD I_LSY NC [1]

PZ98927-3641-01F

An alo g Th erm al Sen sor

3.3V

C359

0.1u_16V_Y 5V _04

Q14

2

3

GN D

G711ST9U

PLACE NEAR U16

PEG_IC OM PI

PEG_ICOMPO

PEG_R CO MPO

PE G_RBI AS

PE G_RX# [0]

PE G_RX# [1]

PE G_RX# [2]

DMI Intel(R) FDI

PE G_RX# [3]

PE G_RX# [4]

PE G_RX# [5]

PE G_RX# [6]

PE G_RX# [7]

PE G_RX# [8]

PE G_RX# [9]

PEG_R X#[1 0]

PEG_R X#[1 1]

PEG_R X#[1 2]

PEG_R X#[1 3]

PEG_R X#[1 4]

PEG_R X#[1 5]

PEG _RX[0]

PEG _RX[1]

PEG _RX[2]

PEG _RX[3]

PEG _RX[4]

PEG _RX[5]

PEG _RX[6]

PEG _RX[7]

PEG _RX[8]

PEG _RX[9]

PE G_RX[10 ]

PE G_RX[11 ]

PE G_RX[12 ]

PE G_RX[13 ]

PE G_RX[14 ]

PE G_RX[15 ]

PEG _ TX# [0]

PEG _ TX# [1]

PEG _ TX# [2]

PEG _ TX# [3]

PEG _ TX# [4]

PEG _ TX# [5]

PEG _ TX# [6]

PEG _ TX# [7]

PEG _ TX# [8]

PEG _ TX# [9]

PE G_TX# [10 ]

PE G_TX# [11 ]

PE G_TX# [12 ]

PE G_TX# [13 ]

PE G_TX# [14 ]

PE G_TX# [15 ]

PCI EXPRESS -- GRAPHICS

PEG _TX[0]

PEG _TX[1]

PEG _TX[2]

PEG _TX[3]

PEG _TX[4]

PEG _TX[5]

PEG _TX[6]

PEG _TX[7]

PEG _TX[8]

PEG _TX[9]

PEG _ TX[10 ]

PEG _ TX[11 ]

PEG _ TX[12 ]

PEG _ TX[13 ]

PEG _ TX[14 ]

PEG _ TX[15 ]

1:2 (4mils:8mils)

OU T1VCC

C36 0

0. 1u _ 1 6V _Y 5 V _ 04

20 mil

B26

A26

B27

A25

K35

J34

J33

G35

G32

F34

F31

D35

E33

C33

D32

B32

C31

B28

B30

A31

J35

H34

H33

F35

G33

E34

F32

D34

F33

B33

D31

A32

C30

A28

B29

A30

L33

M35

M33

M30

L31

K32

M29

J31

K29

H30

H29

F29

E28

D29

D27

C26

L34

M34

M32

L30

M31

K31

M28

H31

K28

G30

G29

F28

E27

D28

C27

C25

PEG_IR CO MP_R

EXP _R BIAS

THERM_VOLT 28

1

3

R209 49.9_1 %_04

R208 750_1%_04

3. 3 V4,12,14,15,16,18,19,20,21,23,24,25,29,30,31,33,34,35

2

B - 4 CPU 1/7 (DMI, PEG, FDI)

http://hobi-elektronika.net

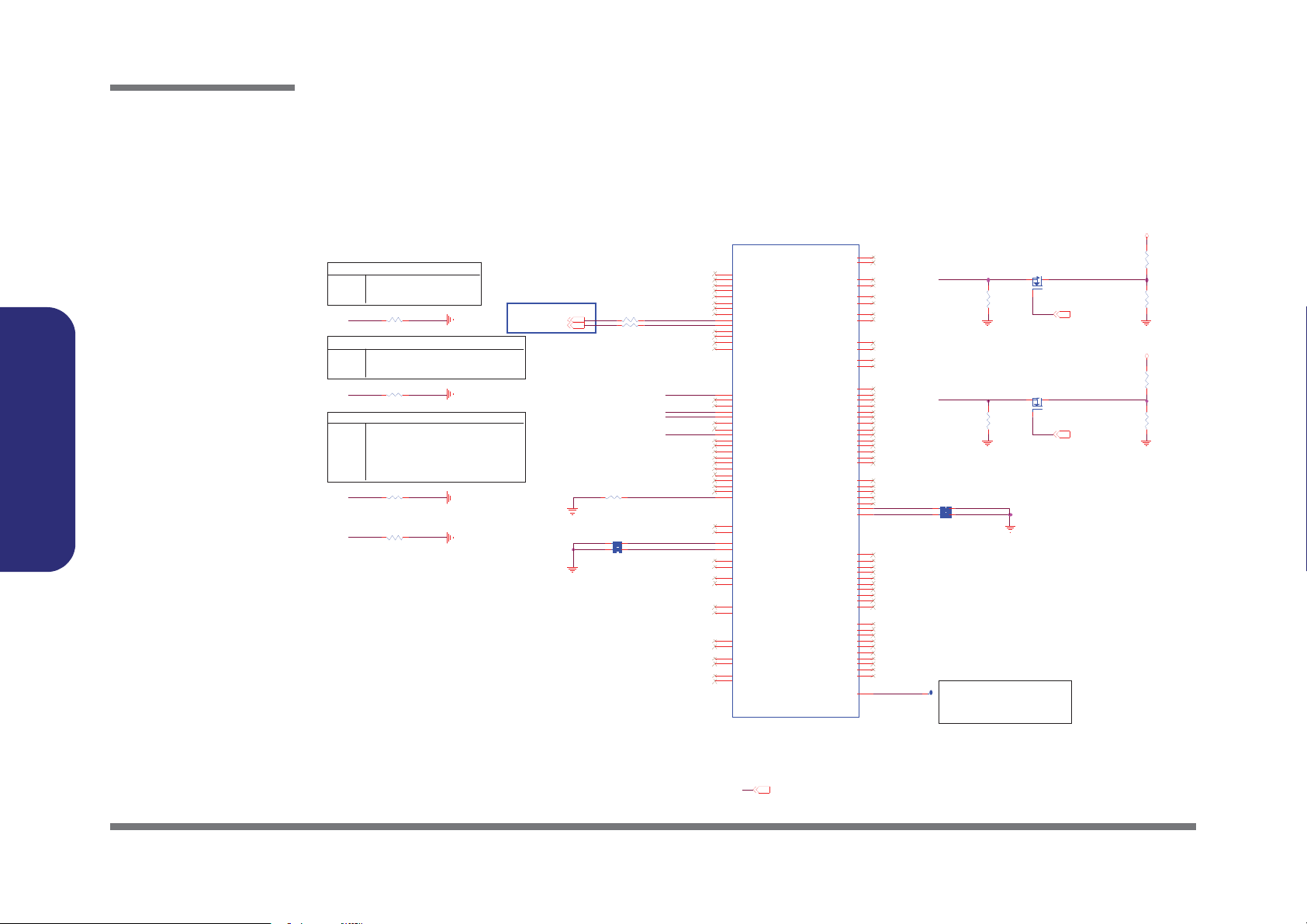

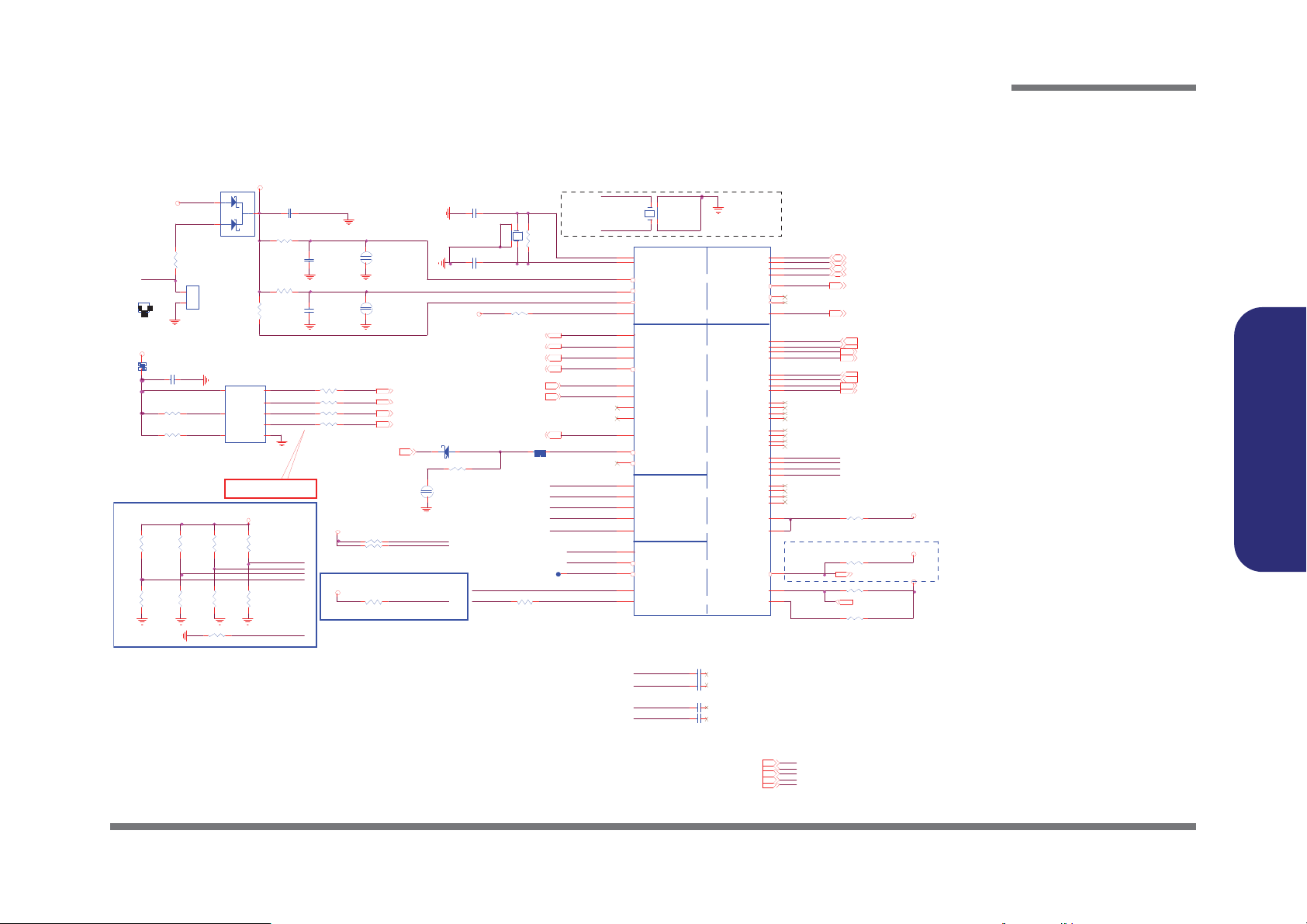

CPU 2/7 (CLK, MISC, JTAG)

H_CP UR ST#

H_CO MP 2

H_CO MP 3

H_CO MP 1

H_CO MP 0

P M_EXTTS#[0]

H_PR OC HO T#_D

XD P _TD O_M

H_C PUR ST#

H_P W RG D_X DP

PLT_R ST# _R

XD P _PREQ #

XD P _TC L K

XD P _TR ST #

XD P _TM S

H_C OM P 3

SY S_ AGEN T_ PW RO K

H_C OM P 2

P M_EXTTS#[1]

H_C OM P 1

SM_DRAMRST#

S M_RCOMP_0

XD P _ T D O _ M

XD P _ T D I _ R

S M_RCOMP_1

VD DP W R GO OD _ R

S M_RCOMP_2

H_C AT ERR #

XD P_ PRE Q#

XD P _ T C L K

XD P _TD I_ R

H_C OM P 0

XD P _TD I_ M

XD P _ T M S

SM _R CO MP_2

SM _R CO MP_1

SM _R CO MP_0

XD P _ T D O _ M

H_P RO CH OT# _ D

XD P_ TRST#

SM_DR AMR ST#

XD P _ T D O _ R

XD P _TD O_R

XDP_TDI_M

DRA MPWRGD_CPU

R24 2 *51_ 0 4

IN 3 .3V

R25 1 *51_ 0 4

R24 9 * 0 _04

R 237 20_1% _04

R250 *10m il_short_04

C31 1

*47n_50V_04

R 236 20_1% _04

R229 100_1%_04

R53 *0_0 4

R207

*100K _1%_04

CLOCKS

MISC THERMAL PWR MANAGEMENT

DDR3

MISC

JTAG & BPM

U16B

PZ 98927-3641-01F

SM_RC OM P[1]

AM 1

SM_RC OM P[2]

AN 1

SM_D RAM RST#

F6

SM_RC OM P[0]

AL1

BCLK#

B16

BC L K

A16

BCLK_ ITP#

AT30

BCLK_ITP

AR 30

PEG _ CLK#

D16

PEG _C L K

E16

DP LL_RE F_S SCL K#

A17

DPLL_REF_SSC LK

A18

CATERR#

AK14

COMP3

AT23

PEC I

AT15

PR OC HO T#

AN26

THER MTR IP#

AK15

R ESE T_O BS#

AP26

VC CP W R GO OD _ 1

AN14

VC CP W R GO OD _ 0

AN27

SM _D RA MPWR OK

AK13

VTTPW R GOO D

AM15

RSTIN#

AL14

PM_EXT_TS#[0]

AN 15

PM_EXT_TS#[1]

AP15

PRDY#

AT28

PRE Q#

AP27

TC K

AN 28

TM S

AP28

TRST#

AT27

TD I

AT29

TDO

AR 27

TDI _M

AR 29

TDO_M

AP29

DB R#

AN 25

BPM#[0]

AJ2 2

BPM#[1]

AK22

BPM#[2]

AK24

BPM#[3]

AJ2 4

BPM#[4]

AJ2 5

BPM#[5]

AH 22

BPM#[6]

AK23

BPM#[7]

AH 23

COMP2

AT24

PM _S YN C

AL15

TAPPW R GO OD

AM26

COMP1

G1 6

COMP0

AT26

SKTO CC #

AH24

R25 2 *51_ 0 4

R54 10 K_ 04

R235 *8.2K_04

R230 24.9_1% _04

R24 5 *51_ 0 4

R203

*1K_1%_04

R244 51_04

R 247 * 68_04

R52 *10m il_short_04

R23 3 10 K_ 04

R60 1.5K_1%_04

R206 *10m il_short_04

R243 *10m il_short_04

R23 2 *0_0 4

R248 *10m il_short_04

R 2 13 4 9 . 9 _1 % _ 0 4

R231 130_1%_04

R61

750_1%_04

Q1 3

*R JU003N 03T106

G

DS

U17

*MC74VHC1G08DFT1G

1

2

5

4

3

R24 1 *51_ 0 4

R62

3K_1% _04

R23 4 *12. 4K _ 1 % _ 04

R240 51_04

R50

1.1K_1% _04

R246 *1.5K_1%_04

R 2 19 4 9 . 9 _1 % _ 0 4

R239 68_04

R 2 38 4 9 . 9 _1 % _ 0 4

1.1VS_VTT

1.1VS_ VTT

1.1VS_ VTT

H_CPUPWRGD19

3. 3 V

1. 5 V

1.5 VS_CPU

H_VTTPWRGD16

BCLK_CP U_N 19

BCLK_CP U_P 19

CLK_ DP_ P 15

CLK_DP_N 15

TS#_D IMM0_1 1 0,11

H_THRMTR IP#19

CLK_ EXP_N 1 5

CLK_ EXP_P 1 5

B UF_PLT_R ST#18,23,25,28

PM_D RAM _ PW RG D16

DELA Y_PWRGD16,36

H_PM _ SYN C16

H_PE C I19 , 2 8

1.1V S_V TT 2,6,7,14,15,16, 19,20,21,34,35, 36

PM _EXT TS#_E C 3

1.1V S_VTT _P WRG D 16 ,33 ,34

3.3V 3,12,14,15,16,18,19,20,21,23,24,25,29,30,31,33,34,35

DRAMRST_CTRL 9,19

DD R3_ DR AM RST # 10,11

1.5V 9,10,11,21,23,27,29,31,33,36

DDR3 Compensation Signals

Proces so r Co mp ensation

Signals

Proces so r Pu ll ups

Signal from PCH to Processor

Connect to PC H (PLT_RST#)

(needs to be level translated

from 3.3 V to 1.1 V).

Connect to the Processor (VTTPWRGOOD) VTT_1.1 VR pow er

good signal to processor. Signal voltage level is 1.1 V.

If PROCHOT# is not used, then it must be terminated

with a 50-O pull-up re sistor to VTT_1.1 rail.

PROCES SOR 2/7 ( CLK,MISC,J TAG )

H_P RO CH OT#36

1.5V S_C PU 7,31

BSS138 ( VGS 1.5V )

?? IBEX CONTROL

Intel change

4.75K -->1.1K

12K -->3K

TRACE WIDTH 10MIL, LENGTH <500MILS

VD DP W R GO OD _ R

H_CA TER R#

Sheet 4 of 42

CPU 2/7

(CLK, MISC, JTAG)

Schematic Diagrams

http://hobi-elektronika.net

B.Schematic Diagrams

CPU 2/7 (CLK, MISC, JTAG) B - 5

Schematic Diagrams

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_A6

M_A_A5

M_A_A7

M_A_A8

M_A_A9

M_A_DQ29

M_A_DQ4

M_A_A4

M_A_DQ32

M_A_DQ31

M_A_DQ30

M_A_DQ37

M_A_DQ36

M_A_DQ35

M_A_DQ34

M_A_DQ33

M_A_DQ42

M_A_DQ41

M_A_DQ40

M_A_DQ39

M_A_DQ47

M_A_DQ46

M_A_DQ45

M_A_DQ44

M_A_DQ43

M_A_DQ51

M_A_DQ28

M_A_DQ50

M_A_DQ49

M_A_DQ38

M_A_DQ48

M_A_DQ55

M_A_DQ54

M_A_DQ53

M_A_DQ52

M_A_A3

M_A_DQ5

M_A_A0

M_A_DQS 7

M_A_A1

M_A_A2

M_A_A15

M_A_DQS 6

M_A_DQ58

M_A_DQ57

M_A_DQ56

M_A_DQ6

M_A_DQ59

M_A_DQ63

M_A_DQ62

M_A_DQ61

M_A_DQ60

M_A_DQS 4

M_A_DQS 5

M_A_DQS 0

M_A_DQS 2

M_A_DQS 1

M_A_DQS 3

M_A_DQ7

M_A_A14

M_A_A13

M_A_DQ8

M_A_DQ9

M_A_DQ13

M_A_DQ12

M_A_DQ11

M_A_A11

M_A_DQ19

M_A_DQ18

M_A_DQ17

M_A_DQ16

M_A_DQ15

M_A_DQ14

M_A_DQS #5

M_A_DQS #6

M_A_DQS #7

M_A_DQ10

M_A_DQS #2

M_A_DQS #1

M_A_DQS #3

M_A_DQS #4

M_A_DQS #0

M_A_DQ22

M_A_DQ21

M_A_DQ26

M_A_DQ25

M_A_DQ24

M_A_DQ23

M_A_DQ0

M_A_A12

M_A_DQ20

M_A_DQ27

M_A_DM4

M_A_DM5

M_A_DM6

M_A_DM7

M_A_DM0

M_A_DM2

M_A_DM1

M_A_DM3

M_A_A10

DDR SYSTE M ME MORY A

U16C

PZ 98927-3641-01F

SA _BS[0 ]

AC3

SA _BS[1 ]

AB2

SA _BS[2 ]

U7

SA _CAS#

AE1

SA _RAS#

AB3

SA _WE#

AE9

SA _CK[0]

AA6

SA _CK[1]

Y6

SA_ CK# [0]

AA7

SA_ CK# [1]

Y5

SA_C KE[ 0]

P7

SA_C KE[ 1]

P6

SA_ CS# [0]

AE2

SA_ CS# [1]

AE8

SA_OD T[0 ]

AD8

SA_OD T[1 ]

AF9

SA_D M[0 ]

B9

SA_D M[1 ]

D7

SA_D M[2 ]

H7

SA_D M[3 ]

M7

SA_D M[4 ]

AG6

SA_D M[5 ]

AM7

SA_D M[6 ]

AN10

SA_D M[7 ]

AN13

SA_DQS[0]

C8

SA_DQS#[0]

C9

SA_DQS[1]

F9

SA_DQS#[1]

F8

SA_DQS[2]

H9

SA_DQS#[2]

J9

SA_DQS[3]

M9

SA_DQS#[3]

N9

SA_DQS[4]

AH8

SA_DQS#[4]

AH7

SA_DQS[5]

AK10

SA_DQS#[5]

AK9

SA_DQS[6]

AN11

SA_DQS#[6]

AP11

SA_DQS[7]

AR13

SA_DQS#[7]

AT13

SA _MA[0]

Y3

SA _MA[1]

W1

SA _MA[2]

AA8

SA _MA[3]

AA3

SA _MA[4]

V1

SA _MA[5]

AA9

SA _MA[6]

V8

SA _MA[7]

T1

SA _MA[8]

Y9

SA _MA[9]

U6

SA_ M A[10]

AD4

SA_ M A[11]

T2

SA_ M A[12]

U3

SA_ M A[13]

AG8

SA_ M A[14]

T3

SA_ M A[15]

V9

SA _DQ[0]

A10

SA _DQ[1]

C1 0

SA _DQ[2]

C7

SA _DQ[3]

A7

SA _DQ[4]

B10

SA _DQ[5]

D1 0

SA _DQ[6]

E10

SA _DQ[7]

A8

SA _DQ[8]

D8

SA _DQ[9]

F10

SA _DQ[10]

E6

SA _DQ[11]

F7

SA _DQ[12]

E9

SA _DQ[13]

B7

SA _DQ[14]

E7

SA _DQ[15]

C6

SA _DQ[16]

H1 0

SA _DQ[17]

G8

SA _DQ[18]

K7

SA _DQ[19]

J8

SA _DQ[20]

G7

SA _DQ[21]

G10

SA _DQ[22]

J7

SA _DQ[23]

J1 0

SA _DQ[24]

L7

SA _DQ[25]

M6

SA _DQ[26]

M8

SA _DQ[27]

L9

SA _DQ[28]

L6

SA _DQ[29]

K8

SA _DQ[30]

N8

SA _DQ[31]

P9

SA _DQ[32]

AH5

SA _DQ[33]

AF5

SA _DQ[34]

AK6

SA _DQ[35]

AK7

SA _DQ[36]

AF6

SA _DQ[37]

AG5

SA _DQ[38]

AJ7

SA _DQ[39]

AJ6

SA _DQ[40]

AJ10

SA _DQ[41]

AJ9

SA _DQ[42]

AL10

SA _DQ[43]

AK 1 2

SA _DQ[44]

AK8

SA _DQ[45]

AL7

SA _DQ[46]

AK 1 1

SA _DQ[47]

AL8

SA _DQ[48]

AN8

SA _DQ[49]

AM10

SA _DQ[50]

AR11

SA _DQ[51]

AL11

SA _DQ[52]

AM9

SA _DQ[53]

AN9

SA _DQ[54]

AT11

SA _DQ[55]

AP 1 2

SA _DQ[56]

AM12

SA _DQ[57]

AN12

SA _DQ[58]

AM13

SA _DQ[59]

AT14

SA _DQ[60]

AT12

SA _DQ[61]

AL13

SA _DQ[62]

AR14

SA _DQ[63]

AP 1 4

DDR SYSTE M ME MORY - B

U16D

PZ98927-3641-01F

SB_B S[0]

AB1

SB_B S[1]

W5

SB_B S[2]

R7

SB_C AS#

AC5

SB_R AS#

Y7

SB_W E#

AC6

SB_C K[ 0]

W8

SB_C K[ 1]

V7

SB_C K#[ 0]

W9

SB_C K#[ 1]

V6

SB_CKE[0]

M3

SB_CKE[1]

M2

SB_C S#[ 0]

AB8

SB_C S#[ 1]

AD6

SB_ODT[ 0]

AC7

SB_ODT[ 1]

AD1

SB_DM[0]

D4

SB_DM[1]

E1

SB_DM[2]

H3

SB_DM[3]

K1

SB_DM[4]

AH1

SB_DM[5]

AL2

SB_DM[6]

AR4

SB_DM[7]

AT8

SB _DQS[4]

AG2

SB_ DQS #[4]

AH2

SB _DQS[5]

AL5

SB_ DQS #[5]

AL4

SB _DQS[6]

AP5

SB_ DQS #[6]

AR5

SB _DQS[7]

AR7

SB_ DQS #[7]

AR8

SB _DQS[0]

C5

SB_ DQS #[0]

D5

SB _DQS[1]

E3

SB_ DQS #[1]

F4

SB _DQS[2]

H4

SB_ DQS #[2]

J4

SB _DQS[3]

M5

SB_ DQS #[3]

L4

SB_MA[ 0]

U5

SB_MA[ 1]

V2

SB_MA[ 2]

T5

SB_MA[ 3]

V3

SB_MA[ 4]

R1

SB_MA[ 5]

T8

SB_MA[ 6]

R2

SB_MA[ 7]

R6

SB_MA[ 8]

R4

SB_MA[ 9]

R5

SB_MA[ 1 0 ]

AB5

SB_MA[ 1 1 ]

P3

SB_MA[ 1 2 ]

R3

SB_MA[ 1 3 ]

AF7

SB_MA[ 1 4 ]

P5

SB_MA[ 1 5 ]

N1

SB_D Q[0 ]

B5

SB_D Q[1 ]

A5

SB_D Q[2 ]

C3

SB_D Q[3 ]

B3

SB_D Q[4 ]

E4

SB_D Q[5 ]

A6

SB_D Q[6 ]

A4

SB_D Q[7 ]

C4

SB_D Q[8 ]

D1

SB_D Q[9 ]

D2

SB_D Q[1 0]

F2

SB_D Q[1 1]

F1

SB_D Q[1 2]

C2

SB_D Q[1 3]

F5

SB_D Q[1 4]

F3

SB_D Q[1 5]

G4

SB_D Q[1 6]

H6

SB_D Q[1 7]

G2

SB_D Q[1 8]

J6

SB_D Q[1 9]

J3

SB_D Q[2 0]

G1

SB_D Q[2 1]

G5

SB_D Q[2 2]

J2

SB_D Q[2 3]

J1

SB_D Q[2 4]

J5

SB_D Q[2 5]

K2

SB_D Q[2 6]

L3

SB_D Q[2 7]

M1

SB_D Q[2 8]

K5

SB_D Q[2 9]

K4

SB_D Q[3 0]

M4

SB_D Q[3 1]

N5

SB_D Q[3 2]

AF3

SB_D Q[3 3]

AG1

SB_D Q[3 4]

AJ3

SB_D Q[3 5]

AK1

SB_D Q[3 6]

AG4

SB_D Q[3 7]

AG3

SB_D Q[3 8]

AJ4

SB_D Q[3 9]

AH4

SB_D Q[4 0]

AK3

SB_D Q[4 1]

AK4

SB_D Q[4 2]

AM6

SB_D Q[4 3]

AN2

SB_D Q[4 4]

AK5

SB_D Q[4 5]

AK2

SB_D Q[4 6]

AM4

SB_D Q[4 7]

AM3

SB_D Q[4 8]

AP3

SB_D Q[4 9]

AN5

SB_D Q[5 0]

AT4

SB_D Q[5 1]

AN6

SB_D Q[5 2]

AN4

SB_D Q[5 3]

AN3

SB_D Q[5 4]

AT5

SB_D Q[5 5]

AT6

SB_D Q[5 6]

AN7

SB_D Q[5 7]

AP6

SB_D Q[5 8]

AP8

SB_D Q[5 9]

AT9

SB_D Q[6 0]

AT7

SB_D Q[6 1]

AP9

SB_D Q[6 2]

AR10

SB_D Q[6 3]

AT10

M_CKE0 10

M_CL K_DDR110

M_CKE1 10

M_A_BS110

M_CS#0 10

M_A_BS210

M_CL K_DDR# 110

M_A_CAS#10

M_ODT010

M_ODT110

M_CS#1 10

M_A_A[15 :0] 1 0

M_A_RAS#10

M_A_DM[7:0]10

M_A_DQ[63:0]10

M_CL K_DDR010

M_A_WE#10

M_B_B S011

M_CL K_DDR# 010

M_A_BS010

M_B_WE#11

M_B_RAS #11

M_B_B S111

M_C KE2 1 1

M_B_CAS #11

M_B_DQ[63:0]11

M_B_B S211

M_CLK_DDR#3 11

M_CLK_DDR3 11

M_C KE3 1 1

M_ODT3 11

M_CS#3 11

M_CS#2 11

M_CLK_DDR#2 11

M_CLK_DDR2 11

M_ODT2 11

M_B_DQS#[7:0] 11

M_B_A[15:0] 11

M_B_DM[7:0] 11

M_A_DQS[7: 0] 10

M_A_DQS#[7:0] 10

M_B_DQS[7:0]11

P ROCESSOR 3/ 7 ( DDR3 )

M_B_DQ48

M_B_DQ47

M_B_DQ54

M_B_DQ53

M_B_DQ52

M_B_DQ51

M_B_DQ50

M_B_DQ49

M_B_DQS5

M_B_DQ58

M_B_DQ57

M_B_DQ56

M_B_DQ55 M_B_DQS7

M_B_DQS0

M_B_DQS1

M_B_DQS2

M_B_DQS3

M_B_DQS4

M_B_DQS6

M_B_DQ61

M_B_DQ60

M_B_DQ59

M_B_DQS#4

M_B_DQS#6

M_B_DQS#5

M_B_DQ11

M_B_DQ63

M_B_DQ62

M_B_DM6

M_B_DM5

M_B_DQ12

M_B_DQS#7

M_B_DQS#0

M_B_DQS#1

M_B_DQS#2

M_B_DQS#3

M_B_DM7

M_B_DM0

M_B_DM1

M_B_DM2

M_B_DM3

M_B_DM4

M_B_DQ3

M_B_DQ2

M_B_DQ1

M_B_DQ4

M_B_DQ6

M_B_DQ5

M_B_DQ9

M_B_DQ8

M_B_DQ7

M_B_DQ0

M_B_DQ10

M_B_DQ13

M_B_A2

M_B_A3

M_B_A4

M_B_A6

M_B_A5

M_B_A0

M_B_A1

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A13

M_B_A12

M_B_DQ14

M_B_DQ18

M_B_DQ17

M_B_DQ16

M_B_A14

M_B_A15

M_B_DQ15

M_B_A7

M_B_DQ23

M_B_DQ22

M_B_DQ21

M_B_DQ20

M_B_DQ19

M_B_DQ28

M_B_DQ27

M_B_DQ26

M_B_DQ25

M_B_DQ24

M_B_DQ34

M_B_DQ33

M_B_DQ32

M_B_DQ31

M_B_DQ30

M_B_DQ29

M_B_DQ39

M_B_DQ38

M_B_DQ37

M_B_DQ36

M_B_DQ35

M_B_DQ44

M_B_DQ43

M_B_DQ42

M_B_DQ41

M_B_DQ40

M_B_DQ46

M_B_DQ45

Sheet 5 of 42

CPU 3/7

(DDR3)

CPU 3/7 (DDR3)

B.Schematic Diagrams

B - 6 CPU 3/7 (DDR3)

http://hobi-elektronika.net

CPU 4/7 (Power)

C36

10u_6. 3V _X5R _06

C303

10u_6.3V_X5R _06

PSI# 36

1K PU to VTT and 1K PD to GND

for PO C

1.1VS_VTT

ICCMAX_VTT Max Current

for VTT Rail

SV 18

The decoupling capacitors, filter

recommendations and sense resistors on the

CPU/PCH Rails are specific to the CRB

Implementation. Customers need to follow the

recommendations in the Calpella Platform

Design Guide

VCORE

Please note that the

VTT Rail Values are

Auburndale VTT=1.05V

C34 0

0. 1u _ 1 0 V _ X 7 R _ 04

C34

10u_6.3V_X5R_06

PROCES SOR 4/7 ( POWER )

C32 8

*1 0 u _6 .3 V_ X5R _ 0 6

C338

0.01u_50V_X7R_04

PSI #

C301

22u_6.3V _X5R _08

+VTT_44

TO VCORE POWER CONTROL

PROCESSOR UNCORE POWERPROCESSOR CORE POW ER

H_VTTVID1

+VTT_43

C355

*22u_6.3V_X 5R_08

C327

*10u_6.3V_X 5R_06

C34 2

*22u_6.3V_X5R_08

C344

10u_6.3V_X5R_06

C324

10u_6. 3V _X5R _06

C 352

22u_6.3V_X5R_08

C329

*22u_6.3V_X 5R_08

C30

*10u_6.3V _X5R _06

POWER

CPU CORE SUPPLY

1.1V RAIL POWER

SENSE LINES

CPU VIDS

U16F

P Z 98 9 2 7 - 3 6 4 1- 01 F

ISENSE

AN35

VTT_SENSE

B15

PSI#

AN33

VID [0]

AK35

VID [1]

AK33

VID [2]

AK34

VID [3]

AL35

VID [4]

AL33

VID [5]

AM33

VID [6]

AM35

PR O C_D PR SL PVR

AM34

VTT_ SELEC T

G15

VC C_ SE NS E

AJ34

VSS _S EN SE_ VTT

A15

VC C1

AG 3 5

VC C2

AG 3 4

VC C3

AG 3 3

VC C4

AG 3 2

VC C5

AG 3 1

VC C6

AG 3 0

VC C7

AG 2 9

VC C8

AG 2 8

VC C9

AG 2 7

VC C10

AG 2 6

VC C11

AF35

VC C12

AF34

VC C13

AF33

VC C14

AF32

VC C15

AF31

VC C16

AF30

VC C17

AF29

VC C18

AF28

VC C19

AF27

VC C20

AF26

VC C21

AD 3 5

VC C22

AD 3 4

VC C23

AD 3 3

VC C24

AD 3 2

VC C25

AD 3 1

VC C26

AD 3 0

VC C27

AD 2 9

VC C28

AD 2 8

VC C29

AD 2 7

VC C30

AD 2 6

VC C31

AC 3 5

VC C32

AC 3 4

VC C33

AC 3 3

VC C34

AC 3 2

VC C35

AC 3 1

VC C36

AC 3 0

VC C37

AC 2 9

VC C38

AC 2 8

VC C39

AC 2 7

VC C40

AC 2 6

VC C41

AA35

VC C42

AA34

VC C43

AA33

VC C44

AA32

VC C45

AA31

VC C46

AA30

VC C47

AA29

VC C48

AA28

VC C49

AA27

VC C50

AA26

VC C51

Y35

VC C52

Y34

VC C53

Y33

VC C54

Y32

VC C55

Y31

VC C56

Y30

VC C57

Y29

VC C58

Y28

VC C59

Y27

VC C60

Y26

VC C61

V35

VC C62

V34

VC C63

V33

VC C64

V32

VC C65

V31

VC C66

V30

VC C67

V29

VC C68

V28

VC C69

V27

VC C70

V26

VC C71

U35

VC C72

U34

VC C73

U33

VC C74

U32

VC C75

U31

VC C76

U30

VC C77

U29

VC C78

U28

VC C79

U27

VC C80

U26

VC C81

R35

VC C82

R34

VC C83

R33

VC C84

R32

VC C85

R31

VC C86

R30

VC C87

R29

VC C88

R28

VC C89

R27

VC C90

R26

VC C91

P35

VC C92

P34

VC C93

P33

VC C94

P32

VC C95

P31

VC C96

P30

VC C97

P29

VC C98

P28

VC C99

P27

VCC100

P26

VTT0_33

AF10

VTT0_34

AE10

VTT0_35

AC10

VTT0_36

AB10

VTT0_37

Y10

VTT0_38

W10

VTT0_39

U10

VTT0_40

T10

VTT0_41

J12

VTT0_42

J11

VTT0_1

AH14

VTT0_2

AH12

VTT0_3

AH11

VTT0_4

AH10

VTT0_5

J14

VTT0_6

J13

VTT0_7

H14

VTT0_8

H12

VTT0_9

G14

VTT0_10

G13

VTT0_11

G12

VTT0_12

G11

VTT0_13

F14

VTT0_14

F13

VTT0_15

F12

VTT0_16

F11

VTT0_17

E14

VTT0_18

E12

VTT0_19

D14

VTT0_20

D13

VTT0_21

D12

VTT0_22

D11

VTT0_23

C14

VTT0_24

C13

VTT0_25

C12

VTT0_26

C11

VTT0_27

B14

VTT0_28

B12

VTT0_29

A14

VTT0_30

A13

VTT0_31

A12

VTT0_32

A11

VSS_SE NS E

AJ35

VTT0_43

J16

VTT0_44

J15

C32 3

22u_6.3V_X5R_08

C31 2

22u_6.3V_X5R _08

C318

22u_6.3V_X5R_08

C 346

*10u_6.3V_X5R_06

C334

22u_6.3V_X5R_08

C34 8

*10u_6. 3V_X 5R_06

C347

10u_6.3V_X5R_06

C304

22u_6.3V_X5R _08

R22 2

*1 K _1 % _ 04

C305

22u_6.3V_X5R_08

C354

*22u_6.3V_X5R _08

C35

*1 0 u _6. 3V _ X5 R _ 0 6

R22 3

1K_1%_04

C29

10u_6. 3V _X5R _06

R226

1K_1%_04

C345

10u_6.3V_X5R_06

C335

*22u_6.3V_X 5R_08

C 331

22u_6.3V_X5R_08

C33

*10u_6.3V_X5R_06

C337

22u_6.3V_X5R_08

C 339

10u_6.3V_X5R_06

C33 2

22u_6.3V_X5R_08

C32 6

10u_6.3V_X5R_06

R225

*1K_1%_04

C 356

22u_6.3V_X5R_08

C333

10u_6.3V_X5R_06

C 325

*10u_6.3V _X 5R_06

1.1VS_V TTVC O RE

1. 1V S _ V T T

VCORE

1.1VS_VTT

1.1VS_ VTT

VCORE

IM O N 36

VS S _SEN SE 36

VC C _ SEN SE 36

1.1V S_ VT T 2 ,4,7 , 1 4 ,1 5 ,16,19 ,2 0 ,21 ,3 4,3 5,3 6

VCO R E 36

PM_DPRSLPVR 36

H_VID2 36

H_VID5 36

H_VID4 36

H_VID6 36

H_VID3 36

H_VID1 36

VTT_ SEN SE 3 4

H_VID0 36

ICCMA X Maximum Processor SV 48

R 216 *15m il_short_06

R 215 *15m il_short_06

VTT TOTAL 21A

48A

Sheet 6 of 42

CPU 4/7

(Power)

Schematic Diagrams

http://hobi-elektronika.net

CPU 4/7 (Power) B - 7

B.Schematic Diagrams

Schematic Diagrams

C330

22u_6. 3V _X5R _08

R45 100_ 1 % _ 0 4

C37

1u _6 .3V_ X5 R _0 4

C30 8

22u_6.3V_X5R_08

+

C53

100 u _6 .3V_ B_ A

C60

1u_ 6.3V_ X5R_0 4

POWER

GRAPHICS VIDs

GRAPHICS

D DR3 - 1.5V RA ILS

FDI PEG & DMI

SENSE

LINES

1.1V1.8V

U16G

PZ 98927-3641-01F

GF X_ VI D[0 ]

AM22

GF X_ VI D[1 ]

AP22

GF X_ VI D[2 ]

AN22

GF X_ VI D[3 ]

AP23

GF X_ VI D[4 ]

AM23

GF X_ VI D[5 ]

AP24

GF X_ VI D[6 ]

AN24

GFX_VR_EN

AR25

GFX_DPRSLPVR

AT25

GF X_ IM O N

AM24

VAXG _ SEN SE

AR22

VSSAXG _SEN SE

AT22

VAXG 1

AT21

VAXG 2

AT19

VAXG 3

AT18

VAXG 4

AT16

VAXG 5

AR 2 1

VAXG 6

AR 1 9

VAXG 7

AR 1 8

VAXG 8

AR 1 6

VAXG 9

AP21

VAXG 10

AP19

VAXG 11

AP18

VAXG 12

AP16

VAXG 13

AN 2 1

VAXG 14

AN 1 9

VAXG 15

AN 1 8

VAXG 16

AN 1 6

VAXG 17

AM 21

VAXG 18

AM 19

VAXG 19

AM 18

VAXG 20

AM 16

VAXG 21

AL2 1

VAXG 22

AL1 9

VAXG 23

AL1 8

VAXG 24

AL1 6

VAXG 25

AK21

VAXG 26

AK19

VAXG 27

AK18

VAXG 28

AK16

VAXG 29

AJ2 1

VAXG 30

AJ1 9

VAXG 31

AJ1 8

VAXG 32

AJ1 6

VAXG 33

AH 2 1

VAXG 34

AH 1 9

VAXG 35

AH 1 8

VAXG 36

AH 1 6

VTT1_ 45

J24

VTT1_ 46

J23

VTT1_ 47

H25

VTT1_ 48

K26

VTT1_ 49

J27

VTT1_ 50

J26

VTT1_ 51

J25

VTT1_ 52

H27

VTT1_ 53

G28

VTT1_ 54

G27

VTT1_ 55

G26

VTT1_ 56

F26

VTT1_ 57

E26

VTT1_ 58

E25

VDDQ1

AJ1

VDDQ2

AF1

VDDQ3

AE7

VDDQ4

AE4

VDDQ5

AC1

VDDQ6

AB7

VDDQ7

AB4

VDDQ8

Y1

VDDQ9

W7

VDD Q10

W4

VDD Q11

U1

VDD Q12

T7

VDD Q13

T4

VDD Q14

P1

VDD Q15

N7

VDD Q16

N4

VDD Q17

L1

VDD Q18

H1

VTT0_59

P10

VTT0_60

N10

VTT0_61

L1 0

VTT0_62

K10

VC CP LL1

L2 6

VC CP LL2

L2 7

VC CP LL3

M2 6

VTT1_63

J2 2

VTT1_64

J2 0

VTT1_65

J1 8

VTT1_66

H21

VTT1_67

H20

VTT1_68

H19

C38

2.2u_16V _X5R _06

C30 6

22u_6.3V_X5R_08

C364

10u_6. 3V _X5R _06

C64

10u_6.3V_X5R_06

C30 9

22u_6.3V_X5R_08

C32 0

10u_6.3V_X5R_06

C350

2 2 u _ 6. 3V _X 5 R _ 08

C39

1u_6.3V_X5R _04

C31 5

22u_6.3V_X5R_08

C30 2

22u_6.3V_X5R_08

C31 3

22u_6.3V_X5R_08

C52

4.7u_6.3V_X5R _06

C30 7

22u_6.3V_X5R_08

C34 3

1u _6 .3V_ X5 R _0 4

C41

1u_6.3V_X5R_04

C55

1u_6.3V_X5R_04

1.1V S_VT T

1. 5V S _ C P U

VG F X_CO RE

DFGT_VR_EN 35

1.1VS_VTT

1.1VS_VTT

1.8VS

1.1VS_VTT

DFGT_VID _4 35

DFGT_VID _3 35

DFGT_VID _2 35

DFGT_VID _1 35

DFGT_VID _0 35

GP UVC C SE N SE 3 5

1.8VS 20,33

1.5V 4,9,10,11,21,23,27,29,31, 33,36

1.1VS _VTT 2,4, 6, 14,15,16,19,20,21,34,35,36

VGFX_CORE 35

Please note that the

VTT Rail Values are

Auburndale VTT=1.05V

Clarksfield VTT=1.1V

GF X_ IM O N 3 5

1.5VS _CPU 4,31

DFGT_VID _6 35

DFGT_VID _5 35

GP UVS SSEN SE 35

VC CP LL 0. 6A

VD DQ 6 A

PROCESSOR 5/7 ( GRAPHICS POWER )

+

C 371 560u_2. 5V _6.6* 6.6*5.9

C39 6

0.01u_50V_X7R_04

C35 1

0. 01 u _ 5 0 V _ X 7R _ 0 4

1.1VS_VTT

R361 *1K_04

1.1VS_VTT

GFXVR_DPRSLPVR

C54

10u_6.3V_X5R_06

C56

10u_6.3V _X5R _06

C61

10u_6.3V_X5R_06

C58

10u_6.3V_X5R_06

TP_GFX_IMON

C33 6

22u_6.3V_X5R_08

C36 2

22u_6.3V_X5R_08

C31 4

22u_6.3V_X5R_08

C349

10u_6.3V_X5R _06

C34 1

1u_6.3V_X5R_04

Sheet 7 of 42

CPU 5/7

(Graphics Power)

CPU 5/7 (Graphics Power)

B.Schematic Diagrams

B - 8 CPU 5/7 (Graphics Power)

http://hobi-elektronika.net

VSS

NCTF

U16I

PZ9 8927- 364 1- 01F

VSS16 1

K2 7

VSS16 2

K9

VSS16 3

K6

VSS16 4

K3

VSS16 5

J32

VSS16 6

J30

VSS16 7

J21

VSS16 8

J19

VSS16 9

H35

VSS17 0

H32

VSS17 1

H28

VSS17 2

H26

VSS17 3

H24

VSS17 4

H22

VSS17 5

H18

VSS17 6

H15

VSS17 7

H13

VSS17 8

H11

VSS17 9

H8

VSS18 0

H5

VSS18 1

H2

VSS18 2

G3 4

VSS18 3

G3 1

VSS18 4

G2 0

VSS18 5

G9

VSS18 6

G6

VSS18 7

G3

VSS18 8

F3 0

VSS18 9

F2 7

VSS19 0

F2 5

VSS19 1

F2 2

VSS19 2

F1 9

VSS19 3

F1 6

VSS19 4

E3 5

VSS19 5

E3 2

VSS19 6

E2 9

VSS19 7

E2 4

VSS19 8

E2 1

VSS19 9

E1 8

VSS20 0

E1 3

VSS20 1

E1 1

VSS20 2

E8

VSS20 3

E5

VSS20 4

E2

VSS20 5

D33

VSS20 6

D30

VSS20 7

D26

VSS20 8

D9

VSS20 9

D6

VSS21 0

D3

VSS21 1

C34

VSS21 2

C32

VSS21 3

C29

VSS21 4

C28

VSS21 5

C24

VSS21 6

C22

VSS21 7

C20

VSS21 8

C19

VSS21 9

C16

VSS22 0

B3 1

VSS22 1

B2 5

VSS22 2

B2 1

VSS22 3

B1 8

VSS22 4

B1 7

VSS22 5

B1 3

VSS22 6

B1 1

VSS22 7

B8

VSS22 8

B6

VSS22 9

B4

VSS23 0

A2 9

VSS_ NCTF1

AT35

VSS_ NCTF2

AT1

VSS_ NCTF3

AR34

VSS_ NCTF4

B34

VSS_ NCTF5

B2

VSS_ NCTF6

B1

VSS_ NCTF7

A35

VSS23 1

A2 7

VSS23 2

A2 3

VSS23 3

A9

VSS

U16H

PZ 98927 -3 641 -01F

VSS1

AT20

VSS2

AT17

VSS3

AR31

VSS4

AR28

VSS5

AR26

VSS6

AR24

VSS7

AR23

VSS8

AR20

VSS9

AR17

VSS1 0

AR15

VSS1 1

AR12

VSS1 2

AR9

VSS1 3

AR6

VSS1 4

AR3

VSS1 5

AP20

VSS1 6

AP17

VSS1 7

AP13

VSS1 8

AP10

VSS1 9

AP7

VSS2 0

AP4

VSS2 1

AP2

VSS2 2

AN34

VSS2 3

AN31

VSS2 4

AN23

VSS2 5

AN20

VSS2 6

AN17

VSS2 7

AM29

VSS2 8

AM27

VSS2 9

AM25

VSS3 0

AM20

VSS3 1

AM17

VSS3 2

AM14

VSS3 3

AM11

VSS3 4

AM8

VSS3 5

AM5

VSS3 6

AM2

VSS3 7

AL34

VSS3 8

AL31

VSS3 9

AL23

VSS4 0

AL20

VSS4 1

AL17

VSS4 2

AL12

VSS4 3

AL9

VSS4 4

AL6

VSS4 5

AL3

VSS4 6

AK29

VSS4 7

AK27

VSS4 8

AK25

VSS4 9

AK20

VSS5 0

AK17

VSS5 1

AJ31

VSS5 2

AJ23

VSS5 3

AJ20

VSS5 4

AJ17

VSS5 5

AJ14

VSS5 6

AJ11

VSS5 7

AJ8

VSS5 8

AJ5

VSS5 9

AJ2

VSS6 0

AH35

VSS6 1

AH34

VSS6 2

AH33

VSS6 3

AH32

VSS6 4

AH31

VSS6 5

AH30

VSS6 6

AH29

VSS6 7

AH28

VSS6 8

AH27

VSS6 9

AH26

VSS7 0

AH20

VSS7 1

AH17

VSS7 2

AH13

VSS7 3

AH9

VSS7 4

AH6

VSS7 5

AH3

VSS7 6

AG10

VSS7 7

AF8

VSS7 8

AF4

VSS7 9

AF2

VSS8 0

AE35

VSS81

AE 3 4

VSS82

AE 3 3

VSS83

AE 3 2

VSS84

AE 3 1

VSS85

AE 3 0

VSS86

AE 2 9

VSS87

AE 2 8

VSS88

AE 2 7

VSS89

AE 2 6

VSS90

AE 6

VSS91

AD 10

VSS92

AC 8

VSS93

AC 4

VSS94

AC 2

VSS95

AB 3 5

VSS96

AB 3 4

VSS97

AB 3 3

VSS98

AB 3 2

VSS99

AB 3 1

VSS10 0

AB 3 0

VSS10 1

AB 2 9

VSS10 2

AB 2 8

VSS10 3

AB 2 7

VSS10 4

AB 2 6

VSS10 5

AB 6

VSS10 6

AA 1 0

VSS10 7

Y8

VSS10 8

Y4

VSS10 9

Y2

VSS11 0

W35

VSS11 1

W34

VSS11 2

W33

VSS11 3

W32

VSS11 4

W31

VSS11 5

W30

VSS11 6

W29

VSS11 7

W28

VSS11 8

W27

VSS11 9

W26

VSS12 0

W6

VSS12 1

V1 0

VSS12 2

U8

VSS12 3

U4

VSS12 4

U2

VSS12 5

T35

VSS12 6

T34

VSS12 7

T33

VSS12 8

T32

VSS12 9

T31

VSS13 0

T30

VSS13 1

T29

VSS13 2

T28

VSS13 3

T27

VSS13 4

T26

VSS13 5

T6

VSS13 6

R10

VSS13 7

P8

VSS13 8

P4

VSS13 9

P2

VSS14 0

N35

VSS14 1

N34

VSS14 2

N33

VSS14 3

N32

VSS14 4

N31

VSS14 5

N30

VSS14 6

N29

VSS14 7

N28

VSS14 8

N27

VSS14 9

N26

VSS15 0

N6

VSS15 1

M10

VSS15 2

L35

VSS15 3

L32

VSS15 4

L29

VSS15 5

L8

VSS15 6

L5

VSS15 7

L2

VSS15 8

K3 4

VSS15 9

K3 3

VSS16 0

K3 0

PROCESSOR 6/7 ( GND )

Schematic Diagrams

CPU 6/7 (GND)

B.Schematic Diagrams

http://hobi-elektronika.net

Sheet 8 of 42

CPU 6/7 (GND)

CPU 6/7 (GND) B - 9

Schematic Diagrams

TP _R S V D 8 6

VR EF_ CH _A_ DIMM

??IBEX CONTROL

MVR E F_ D Q_ DI M 0

CFG7

R38

*1K_1%_04

R214

*100K_1%_0 4

R 227 * 3.01K_04

Q8

*A O3 4 0 2L

G

DS

R40

*1K_1%_04

R 221 * 3.01K_04

R 224 * 3.01K_04

R 220 * 3.01K_04

RESERVED

U16 E

PZ98927-3641-01F

CFG[0]

AM30

CFG[1]

AM28

CFG[2]

AP31

CFG[3]

AL32

CFG[4]

AL30

CFG[5]

AM31

CFG[6]

AN29

CFG[7]

AM32

CFG[8]

AK32

CFG[9]

AK31

CFG[10]

AK28

CFG[11]

AJ28

CFG[12]

AN30

CFG[13]

AN32

CFG[14]

AJ32

CFG[15]

AJ29

CFG[16]

AJ30

CFG[17]

AK30

RS VD3 4

AH25

RS VD3 5

AK26

RS VD3 8

AJ26

RSVD_NCTF_42

AT3

RS VD3 9

AJ27

RSVD_NCTF_40

AP1

RSVD_NCTF_41

AT2

RSVD_NCTF_43

AR1

RSVD_TP_86

H16

RS VD4 5

AL28

RS VD4 6

AL29

RS VD4 7

AP30

RS VD4 8

AP32

RS VD4 9

AL27

RS VD5 0

AT31

RS VD5 1

AT32

RS VD5 2

AP33

RS VD5 3

AR33

RSVD_NCTF_54

AT33

RSVD_NCTF_55

AT34

RSVD_NCTF_56

AP35

RSVD_NCTF_57

AR35

RS VD5 8

AR32

RSVD_NCTF_30

C35

RSVD_NCTF_31

B35

RSVD_NCTF_28

A34

RSVD_NCTF_29

A33

RSVD27

J2 8

RSVD26

J2 9

RSVD16

A19

RSVD15

B19

RSVD17

A20

RSVD18

B20

RSVD20

T9

RSVD19

U9

RSVD22

AB9

RSVD21

AC9

RSVD_NCTF_23

C1

RSVD_NCTF_24

A3

RSVD_TP_66

AA5

RSVD_TP_67

AA4

RSVD_TP_68

R8

RSVD_TP_71

AA2

RSVD_TP_72

AA1

RSVD_TP_73

R9

RSVD_TP_69

AD3

RSVD_TP_74

AG7

RSVD_TP_70

AD2

RSVD_TP_75

AE3

RSVD_TP_76

V4

RSVD_TP_77

V5

RSVD_TP_78

N2

RSVD_TP_81

W3

RSVD_TP_82

W2

RSVD_TP_83

N3

RSVD_TP_79

AD5

RSVD_TP_84

AE5

RSVD_TP_80

AD7

RSVD_TP_85

AD9

RS VD3 6

AL26

RSVD_NCTF_37

AR2

RSVD1

AP25

RSVD2

AL25

RSVD3

AL24

RSVD4

AL22

RSVD5

AJ33

RSVD6

AG9

RSVD7

M2 7

RSVD8

L2 8

RSVD9

J1 7

RSVD10

H17

RSVD11

G2 5

RSVD12

G1 7

RSVD13

E31

RSVD14

E30

RS VD3 2

AJ13

RS VD3 3

AJ12

RSVD_TP_59

E15

RSVD_TP_60

F15

KEY

A2

RS VD6 2

D15

RS VD6 3

C15

RS VD6 4

AJ15

RS VD6 5

AH15

VSS

AP34

R212

*100K_1%_0 4

Q9

*A O3 4 0 2L

G

DS

R36

*1K_1%_04

R37

*1K_1%_04

1.5V

MVREF_DQ_DIM111

MVREF_DQ_DIM010

1.5V

1.5V 4,10, 11,21,23,27,29,31,33, 36

DR AMR ST_ CT R L 4,1 9

DR AMR ST_ CT R L 4,1 9

VR EF _C H_A_DI MM

VR EF _C H_B_DI MM

AP2302GN

AP2302GN

CFG3

CFG4

R 205 *15m il_short_06

R 204 *15m il_short_06

R 218 *15m il_short_06

R 217 *15m il_short_06

VSS (AP34) can be left NC is

CRB implementation ; EDS/DG

recommendation to GND

R 211 *0_04

CFG4

CFG3

CFG0

CFG7

Clar ksfield (onl y f or e arly samples

pre- ES1) - Conne ct to G ND with 3.01 K Oh m/5%

resi stor

PROCESSOR 7/7 ( RESERVED )

H _R SVD 17_R

H _R SVD 18_R

RSVD86

Connect to GND

RSV D6 4 _R

RSV D6 5 _R

CFG7

R SVD8 6

CFG0

??IBEX CONTROL

VR EF_ CH _B_ DIMM MVR E F_ D Q_ DI M 1

1 : Single PEG

0 : Bifurcation enable

CFG0

CFG3

PCI-Express Configuration Select

CFG4

CFG3 - PCI-Express Static L ane Rev ersal

1 : Normal Operation

0 : Lane Numbers Reversed

15 -> 0, 14 -> 1, ...

CFG4 - Display Port Presenc e

1 : Disablled; No physical Display Port

a tt ac he d to Em be dd ed D is pl a y Po rt

0 : Enabled; An external Display Port

d evice is conn ected to the Embedded

is pl ay P or t

R39 *0_04

R35 *0_04

CPU 7/7 (RESERVED)

B.Schematic Diagrams

CPU 7/7

(RESERVED)

B - 10 CPU 7/7 (RESERVED)

Sheet 9 of 42

http://hobi-elektronika.net

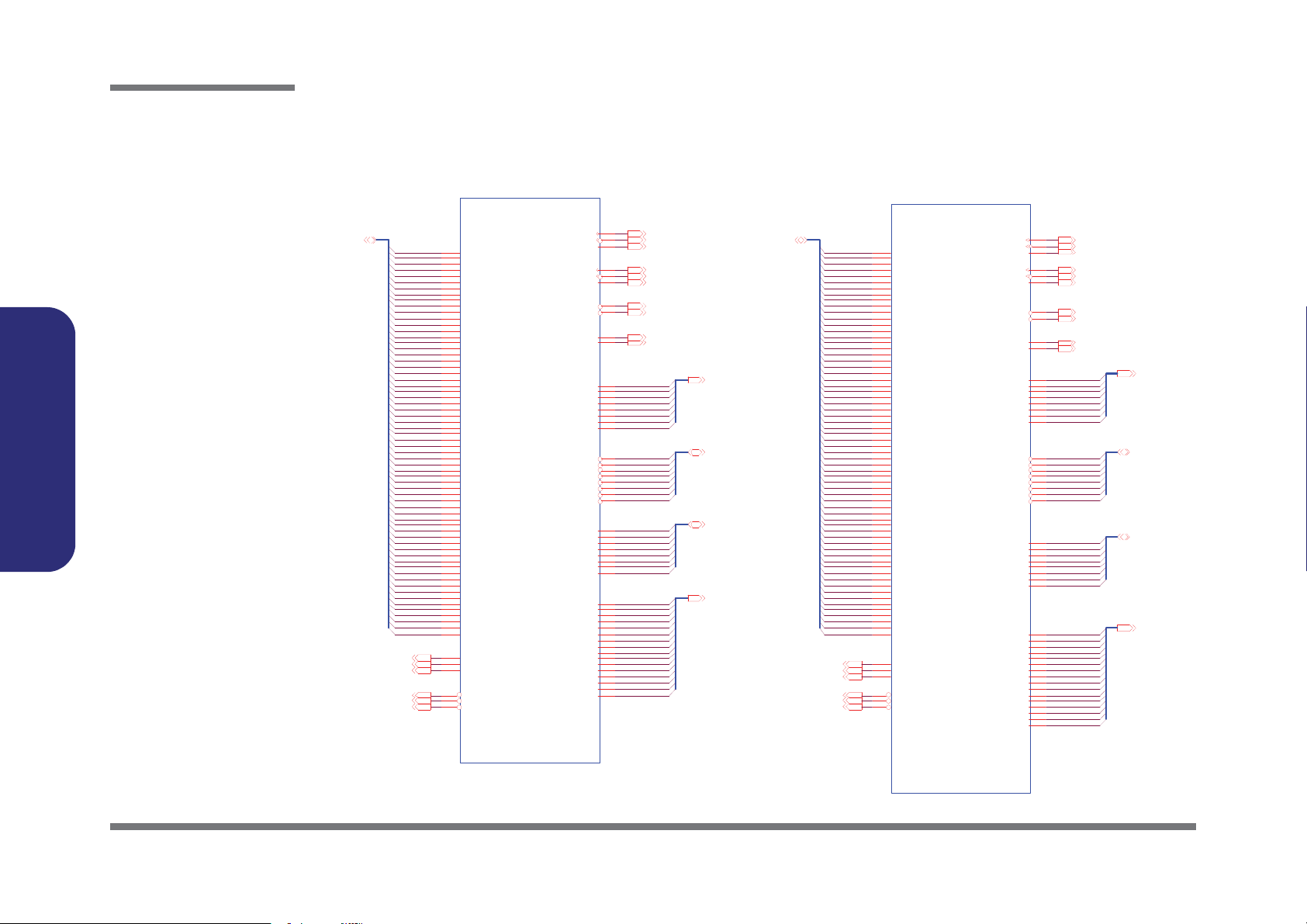

DDR3 SO-DIMM_0

SO- DIM M A

M_A _DQ3

M_A _DQ2

M_A _DQ1

M_A _DQ32

M_A _DQ31

M_A _DQ30

M_A _DQ29

M_A _DQ4

M_A _DQ39

M_A _DQ37

M_A _DQ36

M_A _DQ35

M_A _DQ34

M_A _DQ33

M_A _DQ44

M_A _DQ43

M_A _DQ42

M_A _DQ41

M_A _DQ40

M_A _DQ49

M_A _DQ38

M_A _DQ47

M_A _DQ46

M_A _DQ45

M_A _DQ54

M_A _DQ53

M_A _DQ52

M_A _DQ51

M_A _DQ28

M_A _DQ50

M_A _DQ56

M_A _DQ6

M_A _DQ5

M_A _DQ48

M_A _DQ55

M_A _DQ62

M_A _DQ61

M_A _DQ60

M_A _DQ58

M_A _DQ57

M_A _DQ11

M_A _DQ9

M_A _DQ8

M_A _DQ7

M_A _DQ59

M_A _DQ63

M_A _DQ16

M_A _DQ15

M_A _DQ14

M_A _DQ13

M_A _DQ12

M_A _DQ21

M_A _DQ10

M_A _DQ19

M_A _DQ18

M_A _DQ17

M_A _DQ26

M_A _DQ25

M_A _DQ24

M_A _DQ23

M_A _DQ0

M_A _DQ22

M_A _DQ20

M_A _DQ27

CHANGE TO STANDARD

C104

1u_ 6.3V_ X5R_0 4

C10 1

10u_6.3V_X5R _06

C106

1u_6.3V _X5R_04

VTT_MEM

C10 5

*1u_6.3V _X5R_04

C82 2.2u_6 .3 V_ X5 R _06

C19 0.1u_10V_X7R_04

C 18 2.2u_6.3V_X5R_06

C97

0. 1 u _ 1 0V _X 7 R _ 0 4

R 72 10K_1% _04

R20 *0_04

JDIMM2A

AS0A62 1-U2SN -7F

A0

98

A1

97

A2

96

A3

95

A4

92

A5

91

A6

90

A7

86

A8

89

A9

85

A10/AP

107

A11

84

A12/BC#

83

A13

119

A14

80

A15

78

DQ 0

5

DQ 1

7

DQ 2

15

DQ 3

17

DQ 4

4

DQ 5

6

DQ 6

16

DQ 7

18

DQ 8

21

DQ 9

23

DQ10

33

DQ11

35

DQ12

22

DQ13

24

DQ14

34

DQ15

36

DQ16

39

DQ17

41

DQ18

51

DQ19

53

DQ20

40

DQ21

42

DQ22

50

DQ23

52

DQ24

57

DQ25

59

DQ26

67

DQ27

69

DQ28

56

DQ29

58

DQ30

68

DQ31

70

DQ32

129

DQ33

131

DQ34

141

DQ35

143

DQ36

130

DQ37

132

DQ38

140

DQ39

142

DQ40

147

DQ41

149

DQ42

157

DQ43

159

DQ44

146

DQ45

148

DQ46

158

DQ47

160

DQ48

163

DQ49

165

DQ50

175

DQ51

177

DQ52

164

DQ53

166

DQ54

174

DQ55

176

DQ56

181

DQ57

183

DQ58

191

DQ59

193

DQ60

180

DQ61

182

DQ62

192

DQ63

194

BA0

109

BA1

108

RA S#

110

WE#

113

CA S#

115

S0#

114

S1#

121

CK E0

73

CK E1

74

CK 0

101

CK 0#

103

CK 1

102

CK 1#

104

SD A

200

SC L

202

SA1

201

SA0

197

DM 0

11

DM 1

28

DM 2

46

DM 3

63

DM 4

136

DM 5

153

DM 6

170

DM 7

187

DQ S 0

12

DQ S 1

29

DQ S 2

47

DQ S 3

64

DQ S 4

137

DQ S 5

154

DQ S 6

171

DQ S 7

188

DQ S 0 #

10

DQ S 1 #

27

DQ S 2 #

45

DQ S 3 #

62

DQ S 4 #

135

DQ S 5 #

152

DQ S 6 #

169

DQ S 7 #

186

OD T 0

116

OD T 1

120

BA2

79

C96

1u_6.3V _X5R_04

C81 0 .1u_1 0 V_ X7R _04

C86

0.1u_10V_X7R _04

R65

1K_1%_04

R63 1K _1% _04

JDIMM2B

AS0A62 1-U 2 SN-7F

VDD 1

75

VDD 2

76

VDD 3

81

VDD 4

82

VDD 5

87

VDD 6

88

VDD 7

93

VDD 8

94

VDD 9

99

VDD 10

100

VDD 11

105

VDD 12

106

VDD SPD

199

NC 1

77

NC 2

122

NC TE ST

125

VREF _D Q

1

VSS1

2

VSS2

3

VSS3

8

VSS4

9

VSS5

13

VSS6

14

VSS7

19

VSS8

20

VSS9

25

VSS10

26

VSS11

31

VSS12

32

VSS13

37

VSS14

38

VSS15

43

VS S1 6

44

VS S1 7

48

VS S1 8

49

VS S1 9

54

VS S2 0

55

VS S2 1

60

VS S2 2

61

VS S2 3

65

VS S2 4

66

VS S2 5

71

VS S2 6

72

VS S2 7

12 7

VS S2 8

12 8

VS S2 9

13 3

VS S3 0

13 4

VS S3 1

13 8

VS S3 2

13 9

VS S3 3

14 4

VS S3 4

14 5

VS S3 5

15 0

VS S3 6

15 1

VS S3 7

15 5

VS S3 8

15 6

VS S3 9

16 1

VS S4 0

16 2

VS S4 1

16 7

VS S4 2

16 8

VS S4 3

17 2

VS S4 4

17 3

VS S4 5

17 8

VS S4 6

17 9

VS S4 7

18 4

VS S4 8

18 5

VS S4 9

18 9

VS S5 0

19 0

VS S5 1

19 5

VS S5 2

19 6

G2

GN D2

G1

GN D1

VTT2

20 4

VTT1

20 3

VREF _C A

126

RESE T#

30

EVEN T#

198

VDD 13

111

VDD 14

112

VDD 16

118

VDD 15

117

VDD 17

123

VDD 18

124

3.3VS

3.3VS

VTT_M EM

1. 5 V

1.5V

M_A_BS15

M _ CL K_ DD R15

DDR3_DRAMRST#4, 1 1

M_ O DT 15

M_A _RAS#5

M_A _CAS#5

M _ CL K_ DD R#15

VTT_MEM11,33

M_ O DT 05

M_A_BS05

M_A _W E#5

M_A_BS25

M_ C K E05

M _ CL K_ DD R05

M_ C S #15

M_ A _ DQ [ 6 3 :0] 5

M_ C K E15

M_ C S #05

3.3VS2,11,12,13,14,15,16,17,18,19,20,21,23,24,25,26, 27,28,29,30,31,35,36

M _ CL K_ DD R#05

M_ A_ D Q S [7 :0 ]5

TS#_DIMM0_14, 1 1

MVR EF_DQ_DIM09

M_A_A[15:0]5

M_ A_ D M[ 7 : 0 ]5

M_A_D QS#[7 :0]5

1.5V4,9,11, 21,23,27,29,31,33,36

SA1_D IM 1 1 1

SA1_DIM0

CLOSE TO SO -DI MM_0

SA0_D IM 1 1 1

SA0_DIM1

SA1_DIM1

SA0_DIM0

RN3

10K_8P4R _04

1

2

3

4 5

6

7

8

3.3VS

MVREF_DIM0

20m ils

sig na l /spa ce / sign a l:

Layout Note:

8 / 4 / 8

20m ils

+

C35 3

*220u_2.5V_B_A

R 1 9 * 15 m i l _s h o r t _ 06

MVR EF_DIM0

+

C316

*560u_2. 5V_6.6*6.6*5.9

C57

10u_6.3V_X5R_06

C62

10u_6.3V _X5R_06

C68

1u_ 6. 3V_X5R_04

C78

*10u_6.3V_X5R_06

C47

1u_6.3V_X5R_04

C70

*1u_6.3V_X5R _04

1.5V

CLK_SDATA2, 1 1

CLK_SCLK2,11

SA0_DIM 0

SA1_DIM 0

M_A_DM5

M_A_DM6

M_A_DM7

M_A_DM0

M_A_DM2

M_A_DM1

M_A_DM3

M_A_DM4

M _A_A6

M _A_A5

M _A_A7

M _A_A8

M _A_A9

M _A_A0

M _A_A1

M _A_A2

M _A_A3

M _A_A4

M _A_A1 2

M _A_A1 1

M _A_A1 3

M _A_A1 4

M _A_A1 5

M _A_A1 0

M _A_D QS0

M _A_D QS1

M _A_D QS2

M _A_D QS3

M _A_D QS4

C48

0.1u_1 0V_X7R _04

C73

0.1u_10V_X7R _04

1. 5 V

C67

0.1u_10V_X7R_04

C44

*0.1u_10V _X7R_04

C43

*0.1u_1 0V_ X7R_0 4

C46

0.1u_10V _X7R_04

C75

0.1u_10V_X7R _04

M _A_D QS5

M _A_D QS6

M _A_D QS7

M _A_D QS#0

M _A_D QS#1

M _A_D QS#2

M _A_D QS#3

M _A_D QS#4

M _A_D QS#5

+

C32 1

560u_2.5V _6.6*6.6*5.9

M _A_D QS#6

M _A_D QS#7

Sheet 10 of 42

DDR3 SO-DIMM_0

Schematic Diagrams

http://hobi-elektronika.net

B.Schematic Diagrams

DDR3 SO-DIMM_0 B - 11

Schematic Diagrams

MVR E F_ DI M 1

SO -DI MM B

CHANGE TO STANDARD

Layout Note:

M_ B _ DQ 3 1

M_ B _ DQ 4 6

M_ B _ DQ 1 3

M_ B _ DQ 2 4

M_ B _ DQ 5 6

M_ B _ DQ 2 8

M_ B _ DQ 1 1

M_ B _ DQ 2 3

M_ B _ DQ 6 1

M_ B _ DQ 6 2

M_ B _ DQ 5 8

M_ B _ DQ 5 0

M_ B _ DQ 1

M_ B _ DQ 1 6

M_ B _ DQ 6 0

M_ B _ DQ 2

M_ B _ DQ 4 0

M_ B _ DQ 5 4

M_ B _ DQ 4 1

M_ B _ DQ 5 7

M_ B _ DQ 3 7

M_ B _ DQ 2 5

M_ B _ DQ 3 0

M_ B _ DQ 2 7

M_ B _ DQ 4 4

M_ B _ DQ 3

M_ B _ DQ 7

M_ B _ DQ 9

M_ B _ DQ 3 4

M_ B _ DQ 5

M_ B _ DQ 4 7

M_ B _ DQ 4 3

M_ B _ DQ 3 8

M_ B _ DQ 1 7

M_ B _ DQ 4 2

M_ B _ DQ 8

M_ B _ DQ 5 9

M_ B _ DQ 3 5

M_ B _ DQ 3 6

8 / 4 / 8

M_ B _ DQ 4

M_ B _ DQ 2 6

M_ B _ DQ 6 3

M_ B _ DQ 3 3

M_ B _ DQ 4 5

M_ B _ DQ 4 8

M_ B _ DQ 5 5

M_ B _ DQ 2 9

M_ B _ DQ 1 5

C108

*1u_6.3V _X5R_04

C107

1u_6.3V_X5R _04

M_ B _ DQ 1 0

M_ B _ DQ 5 2

M_ B _ DQ 5 3

C103

1u_6.3V_X5R_04

VTT_MEM

M_ B _ DQ 6

M_ B _ DQ 1 9

M_ B _ DQ 1 8

M_ B _ DQ 0

M_ B _ DQ 1 2

C10 2

10u_6.3V_X5R _06

M_ B _ DQ 2 0

M_ B _ DQ 3 9

M_ B _ DQ 4 9

M_ B _ DQ 5 1

M_ B _ DQ 2 1

M_ B _ DQ 3 2

M_ B _ DQ 1 4

M_ B _ DQ 2 2

M_B_A3

M_B_A4

M_B_A6

M_B_A5

M_B_A9

M_B_A10

M_B_A11

M_B_A13

M_B_A12

M_B_A0

M_B_A1

M_B_A2

M_B_A14

M_B_A7

M_B_A8

20m ils

R23 *0_04

SA1_ D IM1

JDIMM1B

AS0A621-UAS N-7F

VD D1

75

VD D2

76

VD D3

81

VD D4

82

VD D5

87

VD D6

88

VD D7

93

VD D8

94

VD D9

99

VD D10

100

VD D11

105

VD D12

106

VD DSPD

199

NC 1

77

NC 2

122

NC TEST

125

VR EF_ DQ

1

VSS1

2

VSS2

3

VSS3

8

VSS4

9

VSS5

13

VSS6

14

VSS7

19

VSS8

20

VSS9

25

VSS10

26

VSS11

31

VSS12

32

VSS13

37

VSS14

38

VSS15

43

VSS16

44

VSS17

48

VSS18

49

VSS19

54

VSS20

55

VSS21

60

VSS22

61

VSS23

65

VSS24

66

VSS25

71

VSS26

72

VSS27

127

VSS28

128

VSS29

133

VSS30

134

VSS31

138

VSS32

139

VSS33

144

VSS34

145

VSS35

150

VSS36

151

VSS37

155

VSS38

156

VSS39

161

VSS40

162

VSS41

167

VSS42

168

VSS43

172

VSS44

173

VSS45

178

VSS46

179

VSS47

184

VSS48

185

VSS49

189

VSS50

190

VSS51

195

VSS52

196

G2

GN D 2

G1

GN D 1

VTT2

204

VTT1

203

VR EF_ CA

126

RE SET#

30

EVEN T#

198

VD D13

111

VD D14

112

VD D16

118

VD D15

117

VD D17

123

VD D18

124

JDIMM1A

AS0A62 1-UASN -7F

A0

98

A1

97

A2

96

A3

95

A4

92

A5

91

A6

90

A7

86

A8

89

A9

85

A10 /AP

107

A11

84

A12 /BC#

83

A13

119

A14

80

A15

78

DQ 0

5

DQ 1

7

DQ 2

15

DQ 3

17

DQ 4

4

DQ 5

6

DQ 6

16

DQ 7

18

DQ 8

21

DQ 9

23

DQ 1 0

33

DQ 1 1

35

DQ 1 2

22

DQ 1 3

24

DQ 1 4

34

DQ 1 5

36

DQ 1 6

39

DQ 1 7

41

DQ 1 8

51

DQ 1 9

53

DQ 2 0

40

DQ 2 1

42

DQ 2 2

50

DQ 2 3

52

DQ 2 4

57

DQ 2 5

59

DQ 2 6

67

DQ 2 7

69

DQ 2 8

56

DQ 2 9

58

DQ 3 0

68

DQ 3 1

70

DQ 3 2

129

DQ 3 3

131

DQ 3 4

141

DQ 3 5

143

DQ 3 6

130

DQ 3 7

132

DQ 3 8

140

DQ 3 9

142

DQ 4 0

147

DQ 4 1

149

DQ 4 2

157

DQ 4 3

159

DQ 4 4

146

DQ 4 5

148

DQ 4 6

158

DQ 4 7

160

DQ 4 8

163

DQ 4 9

165

DQ 5 0

175

DQ 5 1

177

DQ 5 2

164

DQ 5 3

166

DQ 5 4

174

DQ 5 5

176

DQ 5 6

181

DQ 5 7

183

DQ 5 8

191

DQ 5 9

193

DQ 6 0

180

DQ 6 1

182

DQ 6 2

192

DQ 6 3

194

BA0

109

BA1

108

RA S #

110

WE#

113

CA S #

115

S0#

114

S1#

121

CK E 0

73

CK E 1

74

CK 0

101

CK 0#

103

CK 1

102

CK 1#

104

SD A

200

SC L

202

SA1

201

SA0

197

DM 0

11

DM 1

28

DM 2

46

DM 3

63

DM 4

136

DM 5

153

DM 6

170

DM 7

187

DQ S0

12

DQ S1

29

DQ S2

47

DQ S3

64

DQ S4

137

DQ S5

154

DQ S6

171

DQ S7

188

DQ S0 #

10

DQ S1 #

27

DQ S2 #

45

DQ S3 #

62

DQ S4 #

135

DQ S5 #

152

DQ S6 #

169

DQ S7 #

186

OD T 0

116

OD T 1

120

BA2

79

C84 2.2u_6.3V_X5 R _06

R66

1K_1%_04

C98

1u_6.3V_X5R _04

C87

0.1u_10V_X7R _04

R64 1K_1%_04

C22 2.2u_6.3V_X5 R _06

C99

0.1u_10V_X7R_04

C83 0.1u_10V_X7R _04

si g n al /sp a c e/ signal:

CLOSE TO SO -DIMM_1

C 2 3 0 . 1u _ 1 0 V _X 7 R _0 4

1. 5 V

1.5V

VTT_M EM

3. 3 V S

M_B_A15

3.3VS2,10,12,13,14, 15,16,17,18,19,20,21,23,24,25,26,27,28,29,30,31,35,36

VTT_M EM10 , 3 3

DDR 3 _ DR AMR S T#4,10

M_ B_ A [1 5 :0]5 M_ B_ D Q[ 6 3: 0 ] 5

TS # _ D I M M 0_ 14,10

CLK_SC LK2, 1 0

CLK _ S DA TA2,10

M_ B_ R A S #5

M _B_ BS15

M_CLK_DDR35

M_ B_ W E #5

M_ B_ C A S #5

M_CLK_DDR#35

M _CKE25

M_CLK_DDR25

M _B_ BS05

M_CLK_DDR#25

M_CS#35

M _CKE35

M _B_ BS25

M_OD T25

M_OD T35

M_CS#25

M _B_ DQ S#[7:0 ]5

M_B _D QS [7:0]5

M _B _D M[7:0 ]5

1.5V4,9,10,21,23,27,29,31,33,36

MVREF _DQ_DIM19

M_B _D M5

M_B _D M6

M_B _D M7

M_B _D M0

M_B _D M2

M_B _D M1

M_B _D M3

M_B _D M4

M_B_DQS0

M_B_DQS6

M_B_DQS5

M_B_DQS4

M_B_DQS3

M_B_DQS2

M_B_DQS1

M_B_DQS#3

M_B_DQS#2

M_B_DQS#1

M_B_DQS#0

M_B_DQS7

M_B_DQS#7

M_B_DQS#6

M_B_DQS#5

M_B_DQS#4

Layout Note:

SO-DIMM_1 is pla ced farther from the G M CH than SO -DIMM_0

C51

1u_6.3V_X5R_04

C79

*1u_6.3V_X5R _04

C63

10u_6.3V_X5R _06

C85

*10u_6.3V_X5R_06

C71

1u_6.3V_X5R_04

C76

1u_6.3V_X5R_04

1.5V

C42

10u_6.3V_X5R _06

R22 *15mil_short_06

C69

0.1u_10V_X7R _04

C50

0.1u _10V_X7R_0 4

C10 9

0.1u_10V_X7R _04

C66

0.1u_10V_X7R _04

C72

0.1u_10V_X7R_04

C49

0.1u_10V_X7R _04

C25

0.1u_10V_X7R _04

C228

0.1u_10V_X7R _04

C77

0.1u_10V_X7R_04

C45

0.1u_10V_X7R_04

1.5V

SA1_D IM 110

SA0_D IM 110

2010/01/08

MV RE F _ D I M1

SA0_ D IM1

Sheet 11 of 42

DDR3 SO-DIMM_1

DDR3 SO-DIMM_1

B.Schematic Diagrams

B - 12 DDR3 SO-DIMM_1

http://hobi-elektronika.net

LVDS, Inverter

C15

0.1u_16V_Y 5V_04

2A

3.3V S

C17

*0.01u_50V_X7R _04

R 16 *15mil_short_06

VIN _LCD

LV D S - L 0 P

P_ DD C_ DAT A

LV D S - L 1 P

LV D S - L C L K N

C4

4.7u_6.3V_X5R _06C60.1u_16V_Y5V_04

INV_ BL ON

C291

0.1u_16V_Y5V_04

3. 3 V S

LV D S - L 2N

LV D S - L 1 N

LV D S - L C L K P

BRI GHTN E SS

LV D S - L 0 N

PLVD D

LV D S - L 2P

J_LC D1

87216-3006

1

1

2

2

3

3

4

4

5

5

6

6

7

7

8

8

9910

10

111112

12

131314

14

151516

16

171718

18

191920

20

212122

22

232324

24

252526

26

272728

28

292930

30

VIN

80m ils

BRIGHTNESS 28

LV D S -L C L K N17

LVDS-LCLKP17

LVDS-L1P17

CLOSE TO LVDS CONN.

PIN

LVDS-L1N17

RN6

2.2K_4P2R _04

1 4

2 3

LV D S - L 2N 1 7

EDID Mode

LV D S - L 2P 17

P_ DD C_ CL K

P_DDC_CLK 17

P_DDC_DATA 17

3.3VS

LVDS-L0P17

PANEL CONN ECTOR

LVDS-L0N17

PLVDD

2A

NB_E NAV DD17

U1

APL3512A

VIN

4

VIN

5

EN

3

VO UT

1

GN D

2

R13

100K_1%_04

PANE L POWER

G5243A 6-02- 052 43 -9 C0

APL3512A 6-0 2-0 35 12 -9 C0

3.3VS2,10,11,13,14,15,16,17,18,19,20,21,23,24, 25,26, 27,28,29,30,31,35,36

VIN30, 31,32,33,34,35,36,37

3.3V3,4,14,15,16,18,19,20,21, 23,24, 25,29,30,31,33,34,35

C29 0

*0.1u_16V_Y 5V_04

3.3V

BRIG HTNES S

D15

*BAV99 REC TIF IER

A

C

AC

C30 0

0.1u_50V _Y 5V _06

C29 7

0.1u_50V _Y 5V _06

C29 4

0. 1u_50V_Y5V_06

R68 *10mil_short_04

SY S15V31,32

L25 *15mil_short_06

BLON

IN V_BL O N

BKL_EN_R

Z1201

INVERTER CONNECTOR

R71

1M_04

C93

0 . 1u _ 1 6V _ Y 5V _ 0 4

C89

*0.1u_16V_Y5V_04

U3B

74LVC08PW

4

5

6

147

U3D

74LVC08PW

12

13

11

147

R70 100K_1%_04

U3A

74LVC08PW

1

2

3

147

C90

*0.47u_10V_Y5V_04

U3C

7 4 LV C 0 8P W

9

10

8

147

R69

100K_1%_04

R67

*100K_1%_04

3. 3 V3. 3 V

BLON17

ALL _SY S_ PWRG D16,28

3. 3V

3. 3 V

BKL_E N28

S B _B LO N19

LID_SW#28,30

Z1202

Z1203

Schematic Diagrams

http://hobi-elektronika.net

B.Schematic Diagrams

Sheet 12 of 42

LVDS, Inverter

LVDS, Inverter B - 13

Schematic Diagrams

HDMIB_ CLKBN17

HDMIB_ D0BN17

HDMIB_ D1BN17

HDMIB_ D2BN17

HDMIB_ D2BP17

HDMIB_ D0BP17

HDMIB_ D1BP17

HDMIB_ CLKBP17

L5

* H DM I 201 2F 2 SF -90 0T 04 -short

142

3

R51

*L VA R 0 402 - 24 0E 0R 0 5P - LF

R46

*LVAR0402-240E0R05P-LF

J_ C RT1

10 8A H 1 5F S T04 A 1C C

8

7

6

5

4

3

2

1

9

10

11

12

13

14

15

GND2

GND1

HDMIB_D AT A2 N

RED

HDMIB_D AT A0 N

FOR EMI

DDCLK

FO R EM I

DDCD ATA

HDMIB_DATA1P

24 mil

PORTC_HP D

VSYNC

HDMIB_DATA 1N

HSYNC

HDMIB_DATA0P

GRN

BLUE

HDMIB_EXT1_SCL

HDMI_CEC

HD MIB_EXT1_SDA

HDMIB_EXT1_HPD

C 7 10 00 p_ 50 V_ X 7R _0 4

C292 220p_50V_NPO_04

C 2 95 1 000 p_ 50 V_ X 7R _ 04

C 29 3 22 0p _50 V _N P O _0 4

HDMIB_DATA 1P

C 1 1 1 0p _5 0V _N P O _0 4

C14 10p_50V_NPO_04

H D MI B _E XT 1_ S C L

HDMIB_DATA1N

J_ H DMI 1

C12817-119A5-L

SHIEL D2

2

TMD S D A TA 1 +

4

TMD S D A TA 1 -

6

SHIEL D0

8

TMD S C L O C K+

10

TMD S C L O C K-

12

RESERVED

14

SDA

16

+5 V

18

TM D S D A TA 2+

1

TMDS DAT A2 -

3

SHIELD1

5

TM D S D A TA 0+

7

TMDS DAT A0 -

9

CLK SHIEL D

11

CEC

13

SC L

15

DDC/CEC GND

17

HOT PLUG DET ECT

19

C16 10 p_50V_NPO_04

HDMI PO RT

HDMIB_DATA0P

HDMIB_DATA0N

PIN 4 9=GND

R15 33 _04

IP47 72C Z16 6-02-477 21- B60

TPD7 S01 9 6-02-0701 9-B 20

R14 33 _04

CRT PO RT

HDMIB_EXT 1_ HP D

DDCLK

For ESD

PS 8101 6-03-08101- 032

H D MI B _E XT 1_ S D A

RD3

BAV99 RECT IFIER

A

C

AC

RD1

BAV99 RECT IFIER

A

C

AC

C1

0.1u_16V_Y5V_04

C27

0.1u_16V_Y5V_04

C319

10u_6.3V_X5R_06

C59

*0.1u_16V_Y5V_04

U15

TP D 7S 0 19

VCC_SYNC

1

VCC_VIDEO

2

VI D E O _ 1

3

VI D E O _ 2

4

VI D E O _ 3

5

GND

6

VCC_DDC

7

BYP

8

DDC_OUT1

9

DDC_IN1

10

DDC_IN211DDC_OUT2

12

SYNC_IN113SYNC_OUT 1

14

SYNC_IN215SYNC_OUT 2

16

C29 9

0 . 22 u_ 10V _ Y5 V _04

L7

* H D MI 20 12F 2 SF - 90 0T 04 - sho r t

142

3

C29 8

0.22u_10 V_Y5V_04

C32

0.1u_16V_Y5V_04

C296

0.22u_10V_Y5V_04

R48

20K_1%_04

C310

0.1u_16V_Y5V_04

3.3VS

C40

*0.1u_16V_Y5V_04

5V S

3. 3V S

3.3VS

5V S

C65

0.1u_16V_Y5V_04

RD2

BAV99 RECTIFIER

A

C

AC

U2

PTN3360BBS

IN_D1+

39

IN_D1-

38

IN_D2+

42

IN_D2-

41

IN_D3+

45

IN_D3-

44

IN_D4+

48

IN_D4-

47

SCL

9

SDA

8

HPD

7

OE#

25

DC C_EN#

32

RT_EN#

10

PC0

3

PC1

4

REXT

6

GND[6]

27

QE_ 2

35

OE_ 1

34

OUT _D1+

22

OUT _D1-

23

OUT _D2+

19

OUT _D2-

20

OUT _D3+

16

OUT _D3-

17

OUT _D4+

13

OUT _D4-

14

SCL_SINK

28

SDA_ SINK

29

HPD_S INK

30

VCC[1]

2

VCC[2]

11

VCC[3]

15

VCC[4]

21

VCC[5]

26

VCC[6]

33

VCC[7]

40

VCC[8]

46

GND[1]

1

GND[2]

5

GND[3]

12

GND[4]

18

GND[5]

24

GND[7]

31

GND[8]

36

GND[9]

37

GND[10]

43

GN D

49

CRT_ HSYNC

5V S

3.3VS

DDCDATA

3.3VS

HDMIB_DATA2P

RED

BLUE

GRN

HSYNC

VSYN CCRT_ VSYNC

HDMIB_CLOCKP

RN2

2.2K_4P2R_04

1 4

2 3

5V S

HDMIB_DATA2N

HDMIB_CLOCKN

6-19-31001 -266

PORTC_HPD17

C31 7

22 u_6 . 3V _X 5R _ 08

M_PORTB_ HPD# _R

DAC_HSYNC17

DAC_ VSYNC17

L6

*H D M I2 01 2F 2S F - 90 0T 04- s ho r t

142

3

C 1 0 1 0p _5 0V _N P O _0 4

C12 10p_50V_NPO_04

C13 10 p_50V_NPO_04

R59

*LVAR0402-240E0R05P-LF

R55

*L VA R 0 402 - 24 0E 0R 0 5P - LF

R210

1_0 4

L8

*H D M I2 01 2F 2S F - 90 0T 04- s ho rt

142

3

R44

*LV A R 04 02- 2 40 E0 R 05 P -LF

R43

*L VA R 0 402 - 24 0E 0R 0 5P - LF

HDMIB_CLO CKN

HDMIB_CLO CKP

3. 3V S2,10,1 1, 1 2, 14 , 15 , 16, 1 7, 1 8, 19 , 20 ,21,23,24,25,26,27,28,29,30,3 1, 3 5, 36

5V S2 , 17 , 20, 2 1, 2 6, 27 , 30 ,3 1,3 5, 36

R41

*LVAR04 02-240E0R05P-LF

R42

*L VA R 0 402 - 24 0E 0R 0 5P - LF

RN7

2.2K_4P2R_04

1 4

2 3

5VS

L27

1_04

HDMIB_DATA2P

RN1

2.2K_4P2R_04

1 4

2 3

.

L4 FCM1005MF-6 00T01

.

L2 FCM1005MF-6 00T01

.

L3 FCM1005MF-6 00T01

FOR INTEL GRAPHIC

Z4307

DAC_DDCA CL K17

DAC_DDCA DATA17

Z4304

HDMI_CTRLDATA

PC1

DAC_ RED17

DCC_EN#

HDMI_CTRLCLK

DAC_ BL UE17

DAC_ GREEN17

Z4305

M_PORTB_ HPD# _R

R11

150_1%_04

R10

15 0_ 1% _ 04

R12