ISSI IS80LV31-40WI, IS80LV31-40W, IS80LV31-40PQI, IS80LV31-40PLI, IS80LV31-40PL Datasheet

...

IS80LV51

IS80LV51

IS80LV31

IS80LV31

ISSI

ISSI

®

®

CMOS SINGLE CHIP

LOW VOLTAGE

8-BIT MICROCONTROLLER

FEATURES

• 80C51 based architecture

• 4K x 8 ROM (IS80LV51 only)

• 128 x 8 RAM

• Two 16-bit Timer/Counters

• Full duplex serial channel

• Boolean processor

• Four 8-bit I/O ports, 32 I/O lines

• Memory addressing capability

– 64K ROM and 64K RAM

• Programmable lock

– Lock bits (2)

• Power save modes:

– Idle and power-down

• Six interrupt sources

• Most instructions execute in 0.3 µs

• CMOS and TTL compatible

• Maximum speed: 40 MHz @ Vcc = 3.3V

• Industrial temperature available

• Packages available:

– 40-pin DIP

– 44-pin PLCC

– 44-Pin PQFP

ADVANCE INFORMATION

OCTOBER 1998

GENERAL DESCRIPTION

The ISSI IS80LV51 and IS80LV31 are high-performance

microcontrollers fabricated using high-density CMOS

technology. The CMOS IS80LV51/31 is functionally

compatible with the industry standard 80C51

microcontrollers.

The IS80LV51/31 is designed with 4K x 8 ROM (IS80LV51

only); 128 x 8 RAM; 32 programmable I/O lines; a serial

I/O port for either multiprocessor communications, I/O

expansion or full duplex UART; two 16-bit timer/counters;

a six-source, two-priority-level, nested interrupt structure;

and an on-chip oscillator and clock circuit. The

IS80LV51/31 can be expanded using standard TTL

compatible memory.

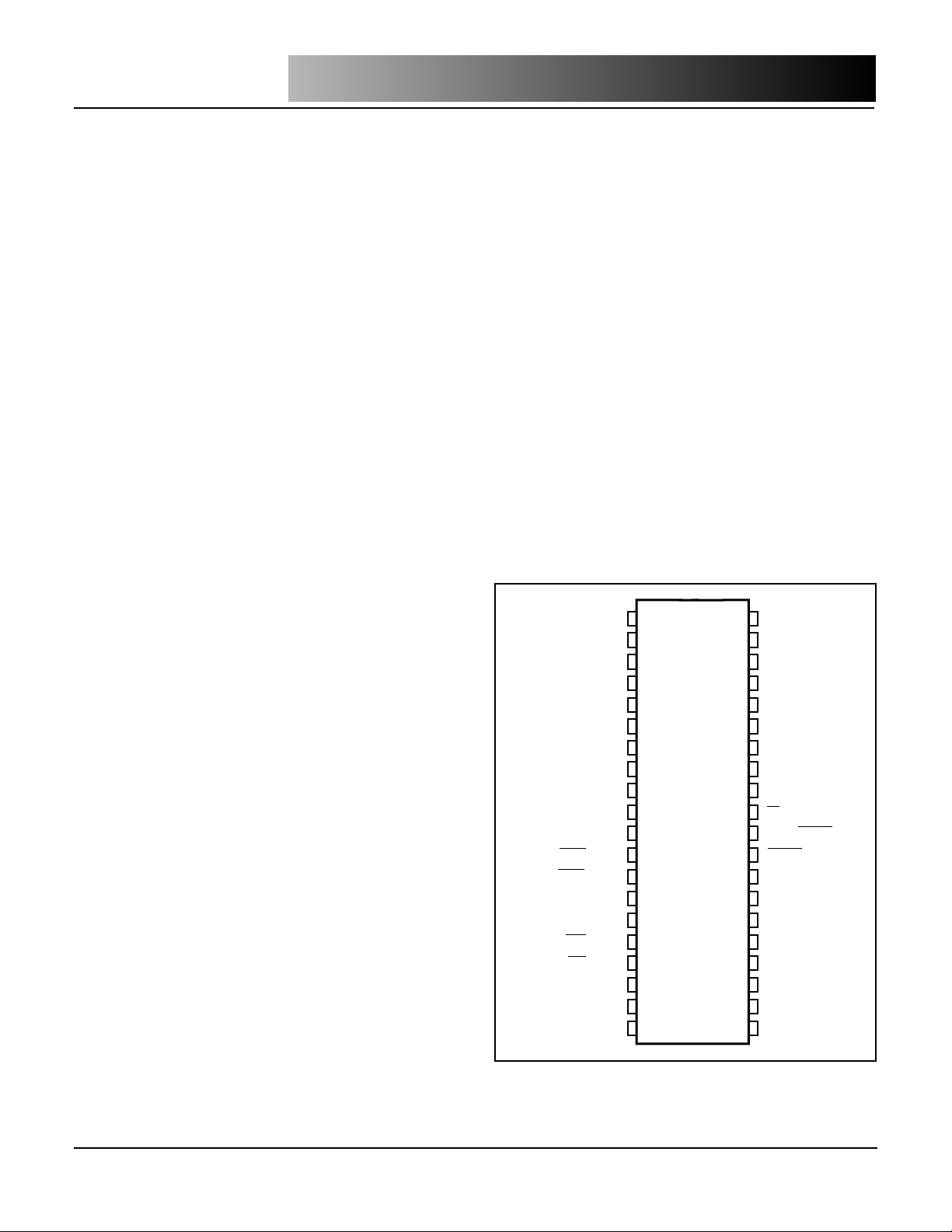

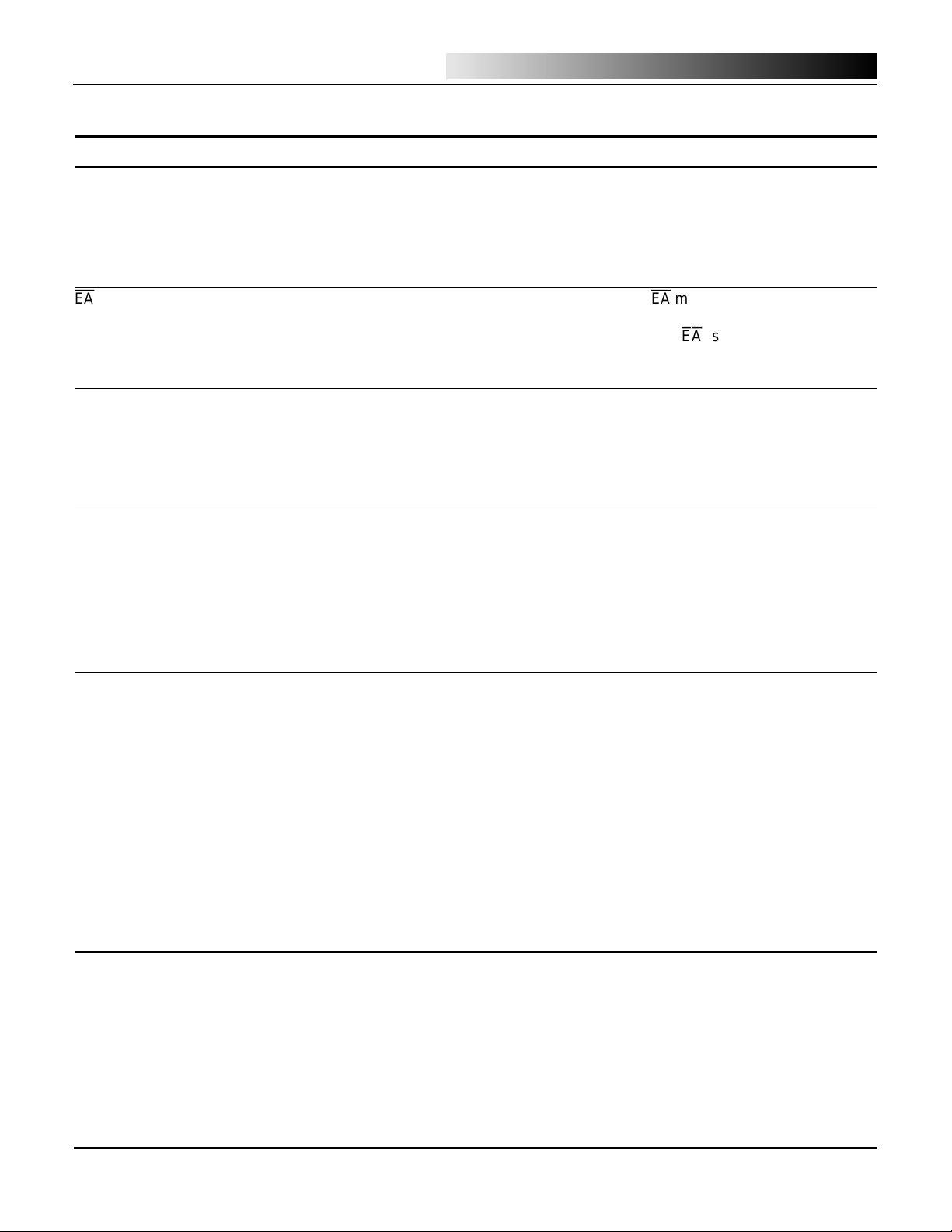

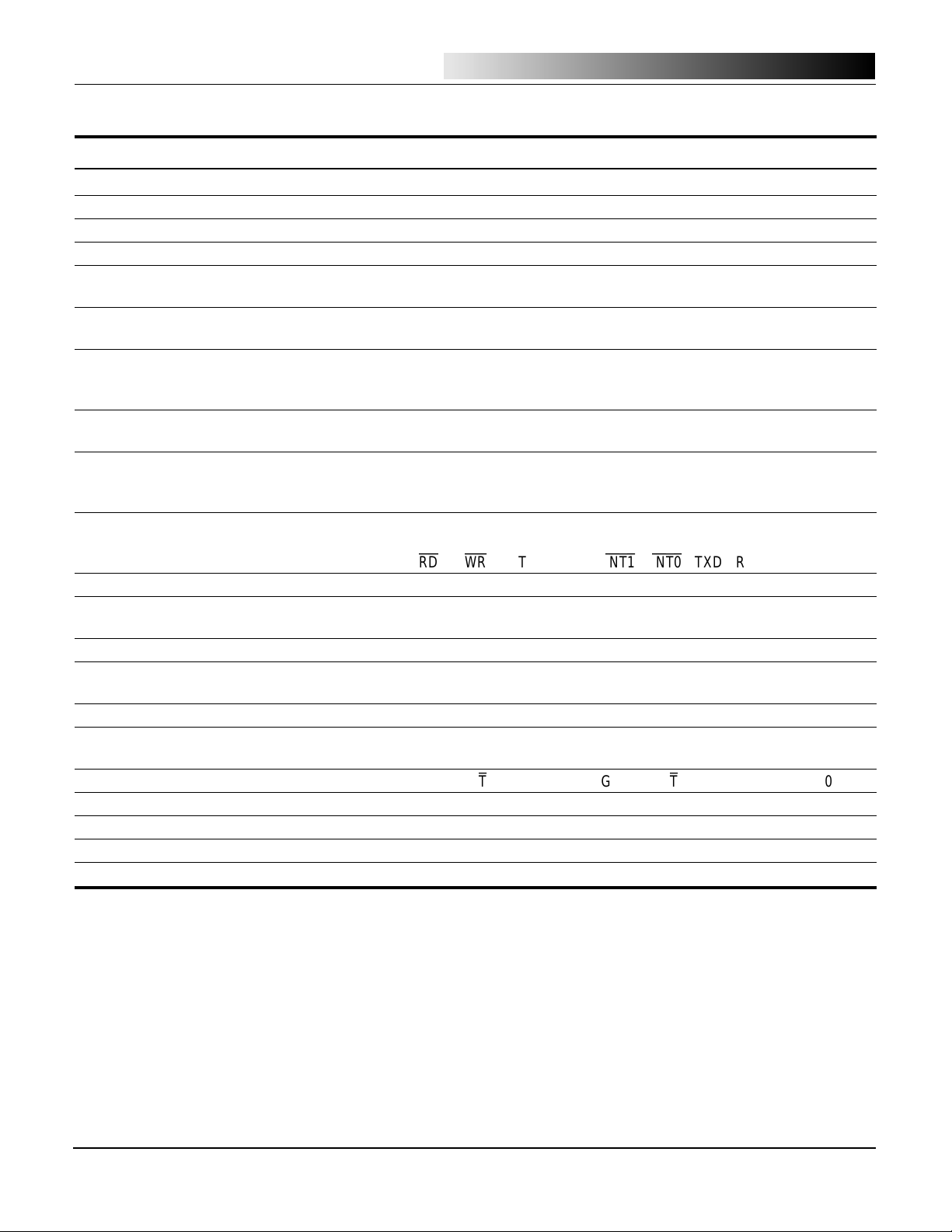

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

VCC

P0.0/AD0

P0.1/AD1

P0.2/AD2

P0.3/AD3

P0.4/AD4

P0.5/AD5

P0.6/AD6

P0.7/AD7

EA/VPP

ALE/PROG

PSEN

P2.7/A15

P2.6/A14

P2.5/A13

P2.4/A12

P2.3/A11

P2.2/A10

P2.1/A9

P2.0/A8

P1.0

P1.1

P1.2

P1.3

P1.4

P1.5

P1.6

P1.7

RST

RxD/P3.0

TxD/P3.1

INT0/P3.2

INT1/P3.3

T0/P3.4

T1/P3.5

WR/P3.6

RD/P3.7

XTAL2

XTAL1

GND

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

Figure 1. IS80LV51/31 Pin Configuration: 40-pin PDIP

This document contains ADVANCE INFORMATION data. ISSI reserves the right to make changes to its products at any time without notice in order to improve design and supply the best possible

product. We assume no responsibility for any errors which may appear in this publication. © Copyright 1998, Integrated Silicon Solution, Inc.

Integrated Silicon Solution, Inc.

ADVANCE INFORMATION MC018-0A

10/01/98

1

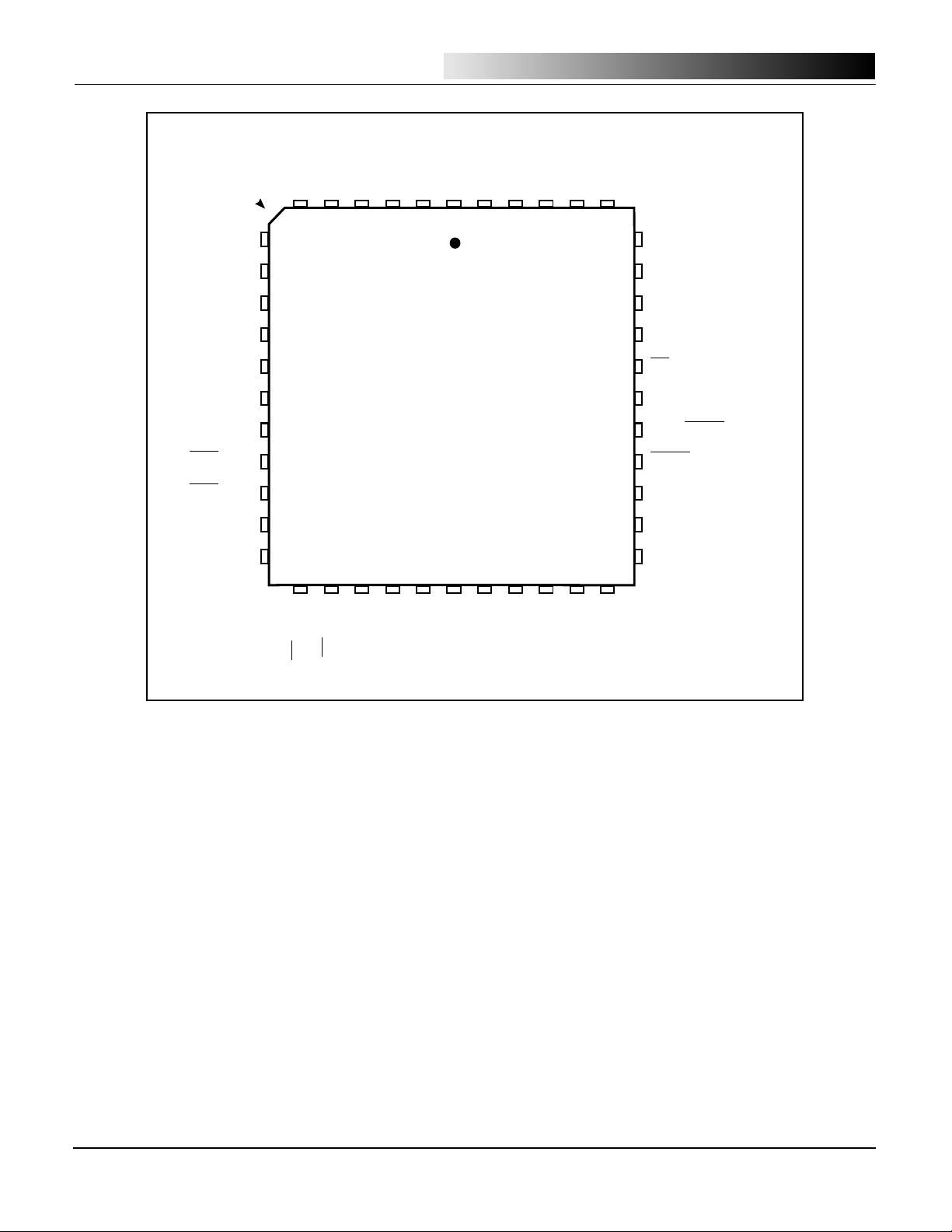

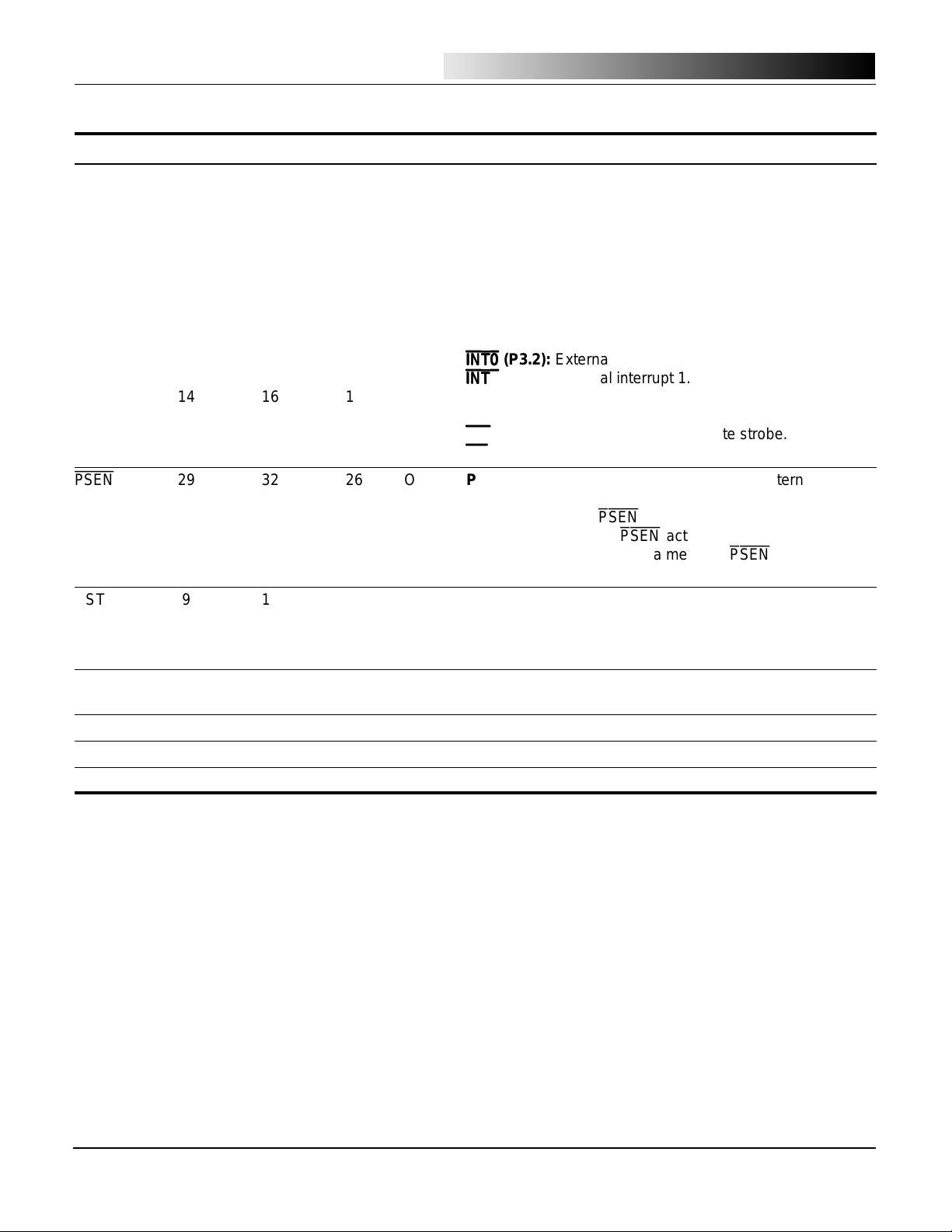

IS80LV51

IS80LV31

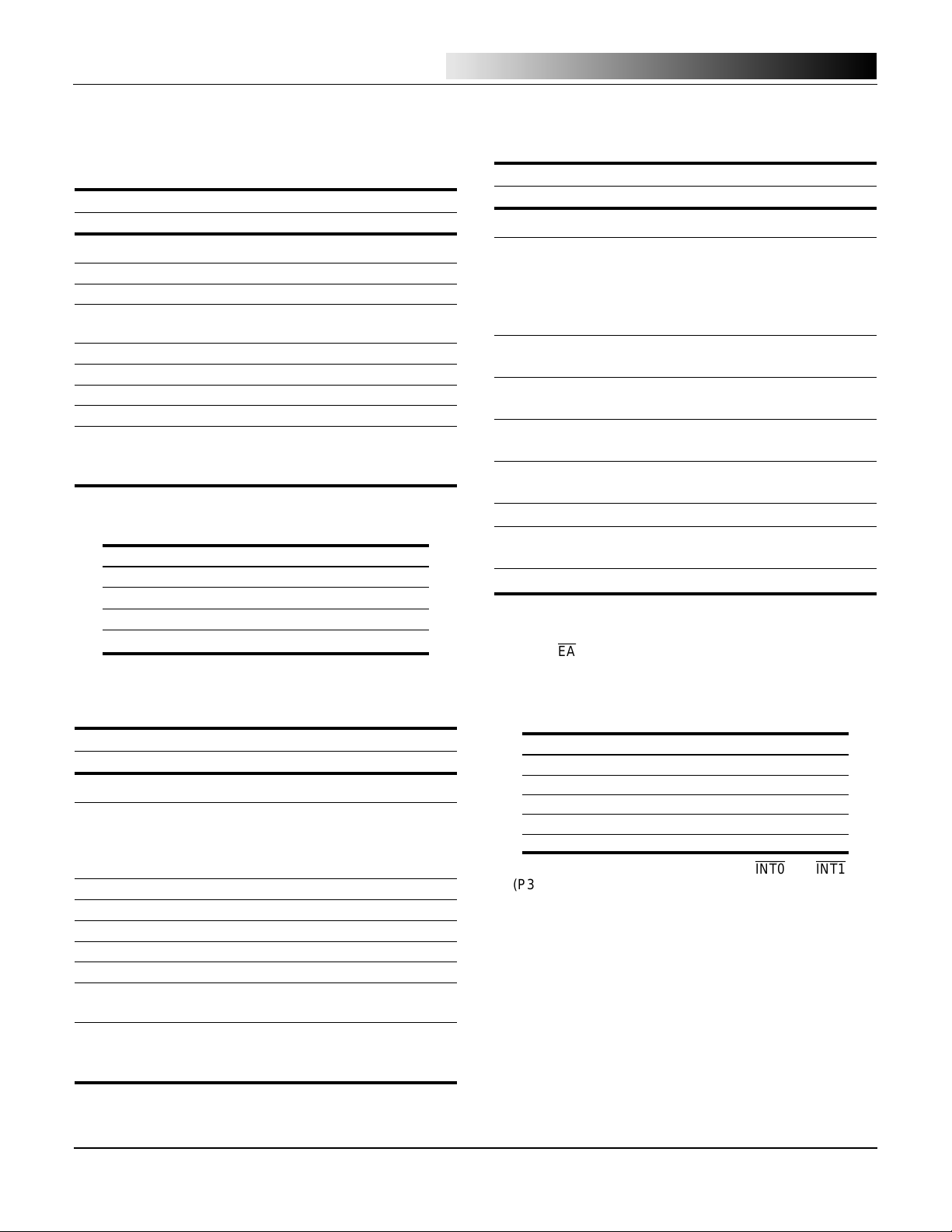

INDEX

P1.4

P1.3

P1.2

P1.1

P1.0NCVCC

P0.0/AD0

P0.1/AD1

P0.2/AD2

P0.3/AD3

®

ISSI

P1.5

P1.6

P1.7

RST

RxD/P3.0

NC

TxD/P3.1

INT0/P3.2

INT1/P3.3

T0/P3.4

T1/P3.5

4365 2144

7

8

9

10

11

12

13

14

15

16

17

18 19 20 21 22 23 24

GND

XTAL1

RD/P3.7

WR/P3.6

XTAL2

NC

43 42 41 40

25 26 27 28

A8/P2.0

A9/P2.1

A10/P2.2

39

38

37

36

35

34

33

32

31

30

29

A11/P2.3

A12/P2.4

P0.4/AD4

P0.5/AD5

P0.6/AD6

P0.7/AD7

EA/VPP

NC

ALE/PROG

PSEN

P2.7/A15

P2.6/A14

P2.5/A13

Figure 2. IS80LV51/31 Pin Configuration: 44-pin PLCC

2

Integrated Silicon Solution, Inc.

ADVANCE INFORMATION MC018-0A

10/01/98

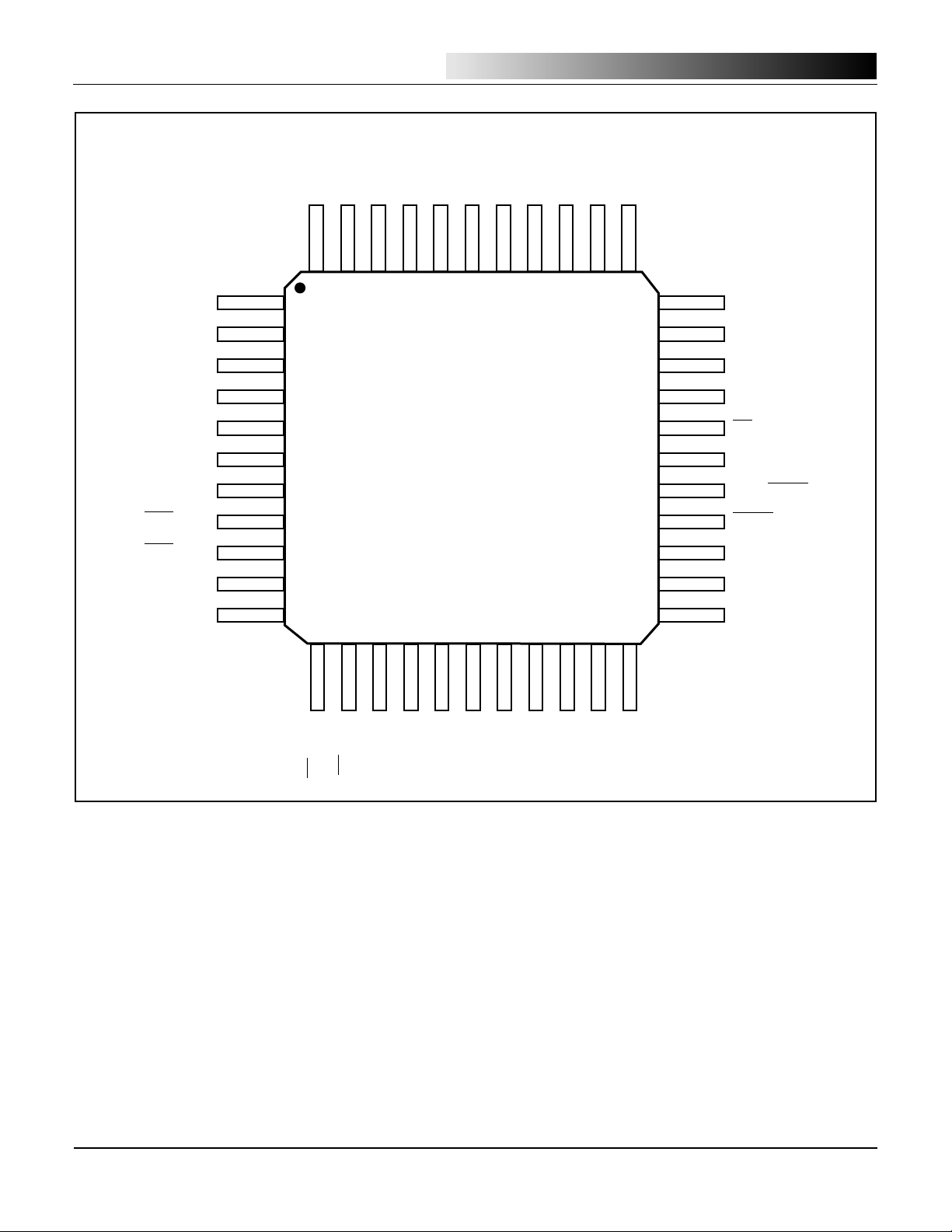

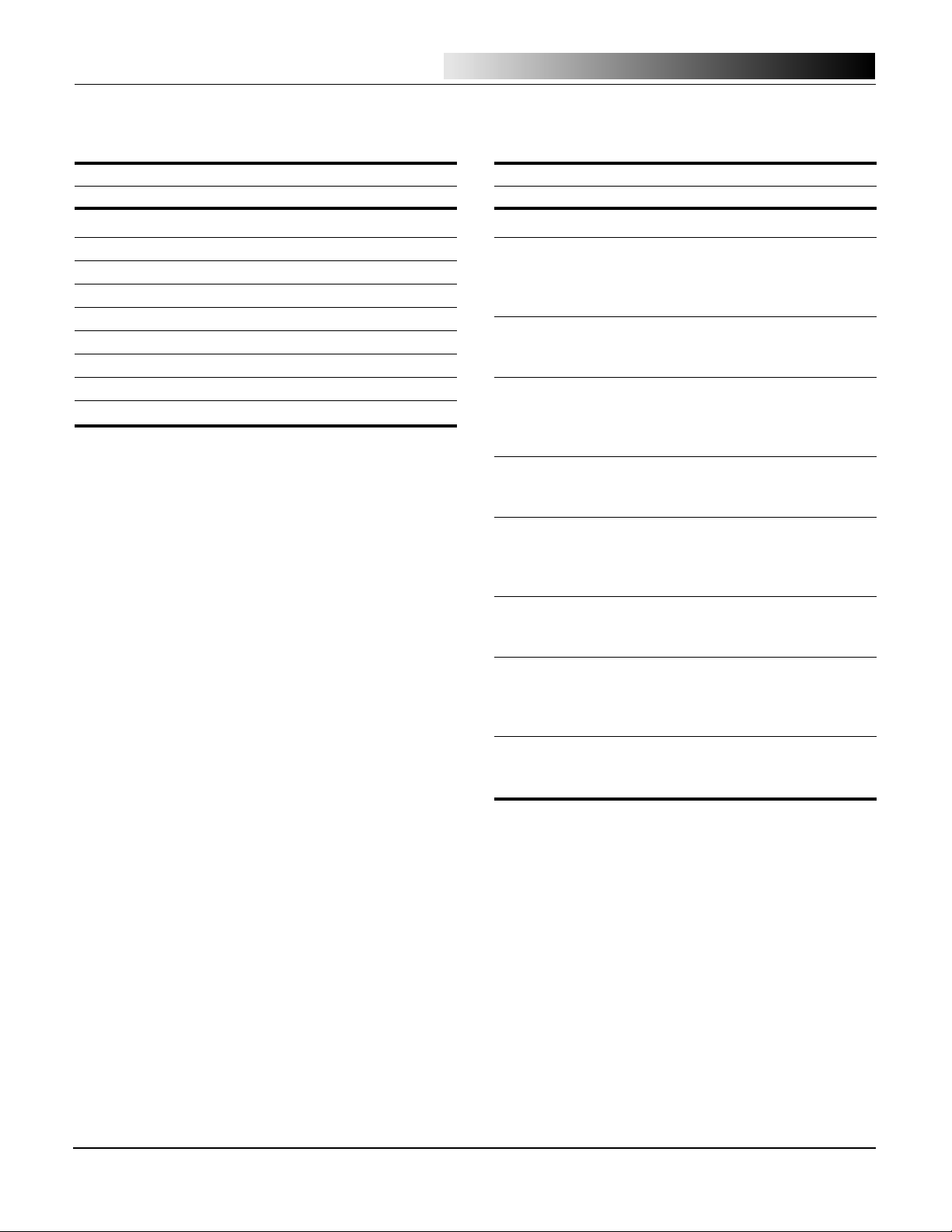

IS80LV51

IS80LV31

P1.4

P1.3

P1.2

P1.1

P1.0NCVCC

P0.0/AD0

P0.1/AD1

P0.2/AD2

P0.3/AD3

®

ISSI

P1.5

P1.6

P1.7

RST

RxD/P3.0

NC

TxD/P3.1

INT0/P3.2

INT1/P3.3

T0/P3.4

T1/P3.5

42 4144 43 40 39 38

1

2

3

4

5

6

7

8

9

10

11

12 13 14 15 16 17 18

GND

XTAL1

RD/P3.7

WR/P3.6

XTAL2

NC

37 36 35 34

19 20 21 22

A8/P2.0

A9/P2.1

A10/P2.2

33

32

31

30

29

28

27

26

25

24

23

A11/P2.3

A12/P2.4

P0.4/AD4

P0.5/AD5

P0.6/AD6

P0.7/AD7

EA/VPP

NC

ALE/PROG

PSEN

P2.7/A15

P2.6/A14

P2.5/A13

Figure 3. IS80LV51/31 Pin Configuration: 44-pin PQFP

Integrated Silicon Solution, Inc.

ADVANCE INFORMATION MC018-0A

10/01/98

3

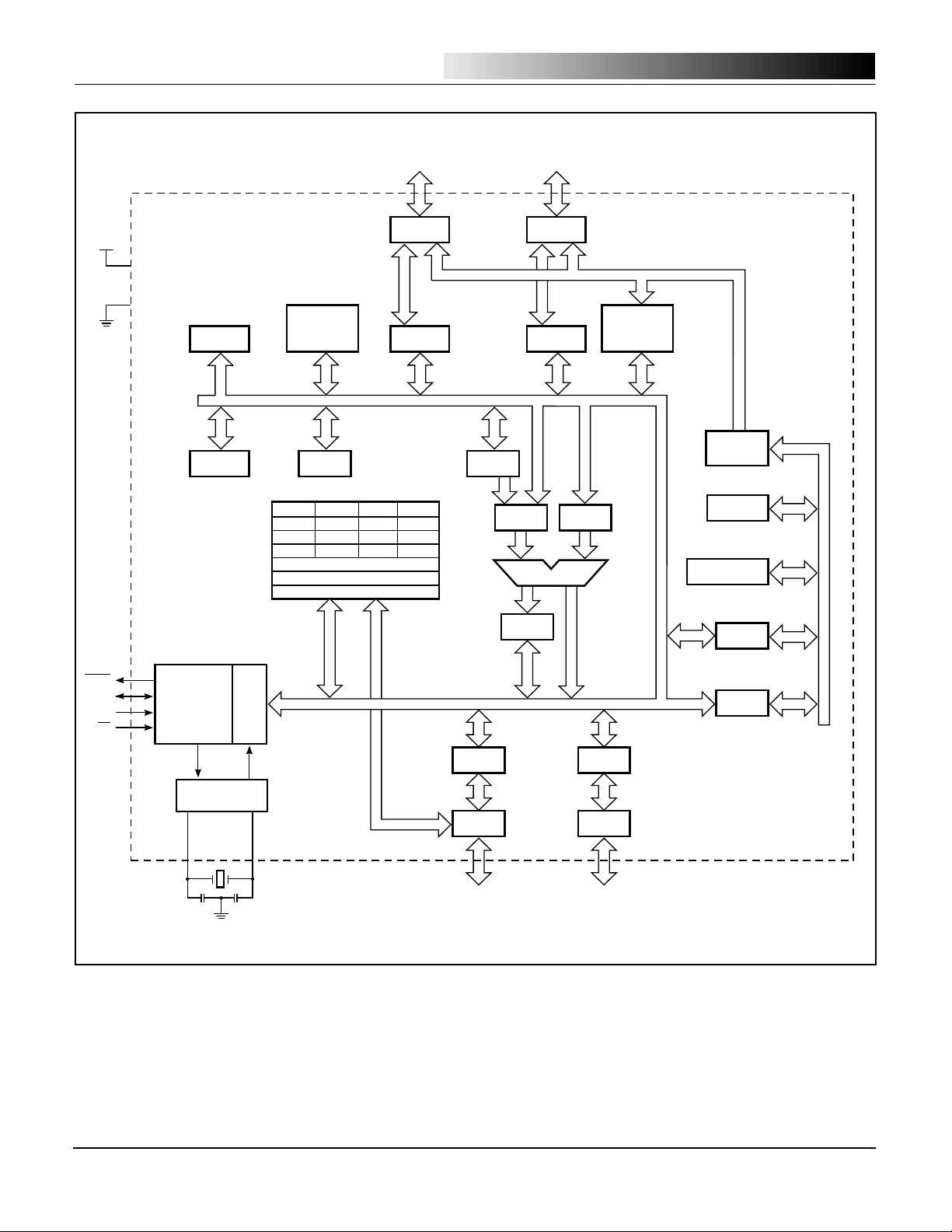

IS80LV51

IS80LV31

®

ISSI

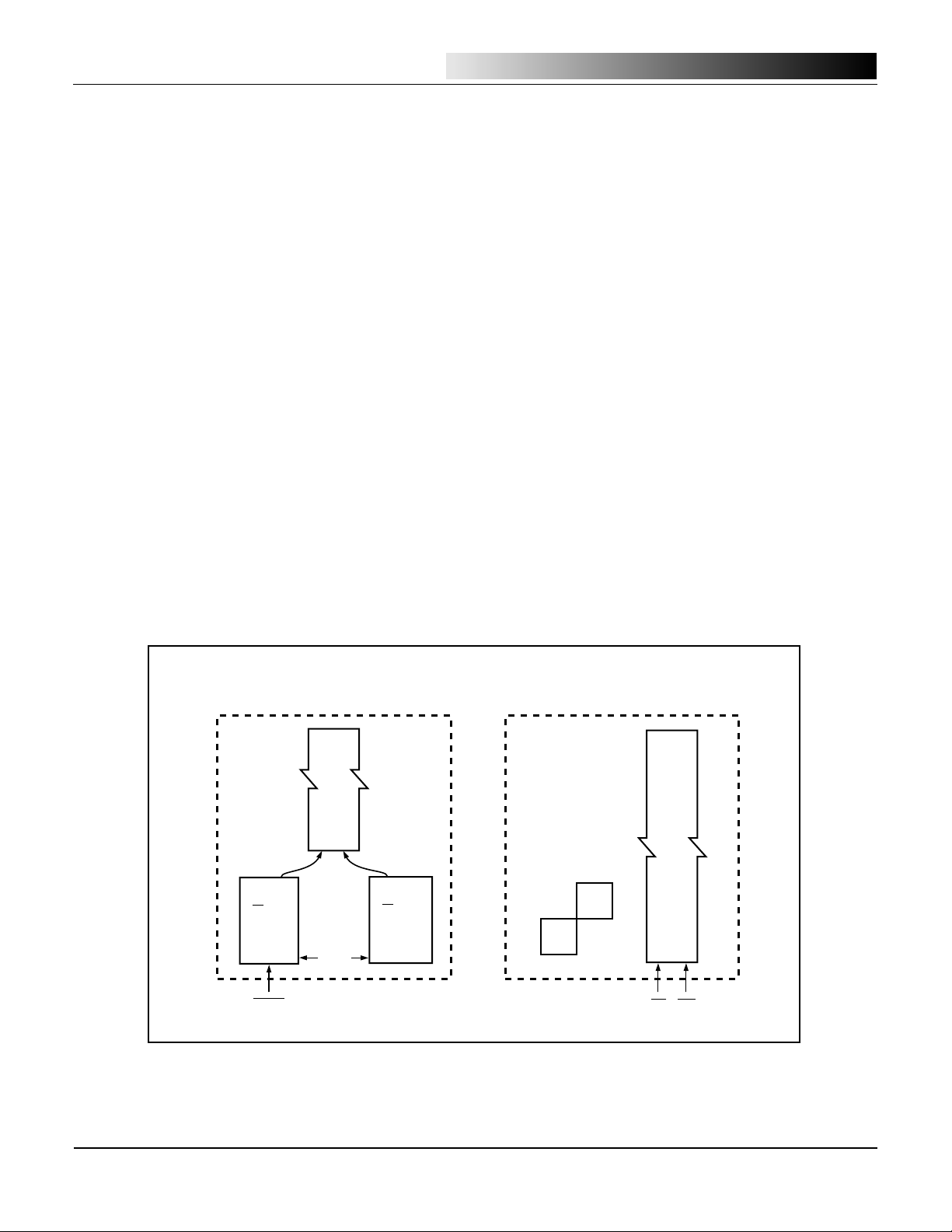

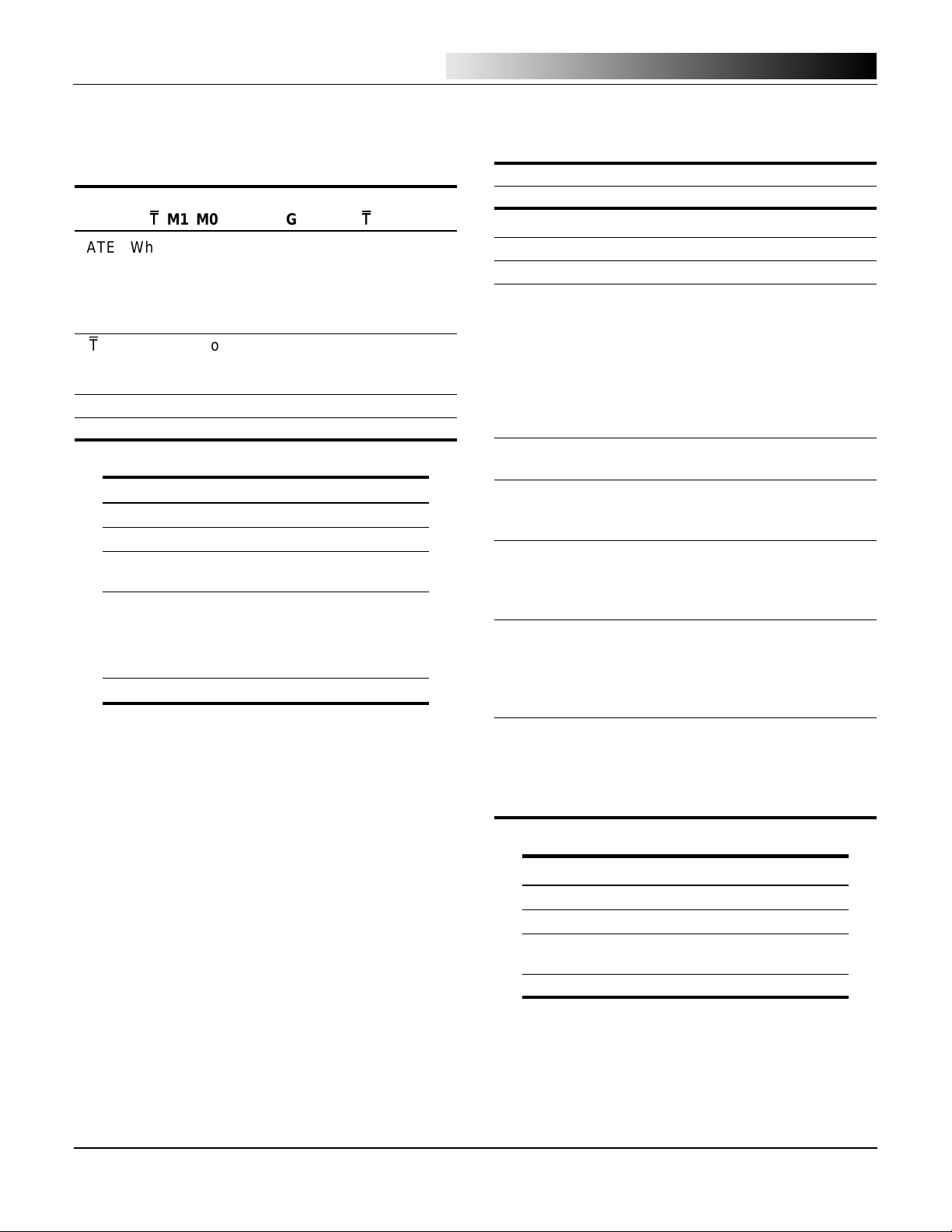

VCC

RAM ADDR

REGISTER

B

REGISTER

P2.0-P2.7

P2

DRIVERS

ADDRESS

DECODER

& 128

BYTES RAM

STACK

POINT

PCON SCON TMOD TCON

TL1

TH0 TL0 TH1

SBUF IE IP

INTERRUPT BLOCK

SERIAL PORT BLOCK

TIMER BLOCK

P2

LATCH

ACC

TMP2

P0.0-P0.7

P0

DRIVERS

P0

LATCH

ALU

TMP1

ADDRESS

DECODER

&

4K ROM

PROGRAM

ADDRESS

REGISTER

PROGRAM

COUNTER

PC

INCREMENTER

PSEN

ALE

RST

EA

TIMING

AND

CONTROL

OSCILLATOR

REGISTER

INSTRUCTION

XTAL2XTAL1

PSW

P3

LATCH

P3

DRIVERS

P3.0-P3.7

P1

LATCH

P1

DRIVERS

P1.0-P1.7

Figure 4. IS80LV51/31 Block Diagram

BUFFER

DPTR

4

Integrated Silicon Solution, Inc.

ADVANCE INFORMATION MC018-0A

10/01/98

IS80LV51

IS80LV31

Table 1. Detailed Pin Description

Symbol PDIP PLCC PQFP I/O Name and Function

ALE 30 33 27 I/O Address Latch Enable: Output pulse for latching the low byte

of the address during an address to the external memory. In

normal operation, ALE is emitted at a constant rate of 1/6 the

oscillator frequency, and can be used for external timing or

clocking. Note that one ALE pulse is skipped during each

access to external data memory.

EA

P0.0-P0.7 39-32 43-36 37-30 I/O Port 0: Port 0 is an 8-bit open-drain, bidirectional I/O port. Port

31 35 29 I External Access enable: EA must be externally held low to

enable the device to fetch code from external program memory

locations 0000H to FFFFH. If EA is held high, the device

executes from internal program memory unless the program

counter contains an address greater than 0FFFH.

0 pins that have 1s written to them float and can be used as

high-impedance inputs. Port 0 is also the multiplexed loworder address and data bus during accesses to external

program and data memory. In this application, it uses strong

internal pullups when emitting 1s.

ISSI

®

P1.0-P1.7 1-8 2-9 40-44 I/O Port 1: Port 1 is an 8-bit bidirectional I/O port with internal

1-3 pullups. Port 1 pins that have 1s written to them are pulled high

by the internal pullups and can be used as inputs. As inputs,

Port 1 pins that are externally pulled low will source current

because of the internal pullups. (See DC Characteristics: IIL).

The Port 1 output buffers can sink/source four TTL inputs.

Port 1 also receives the low-order address byte during ROM

verification.

P2.0-P2.7 21-28 24-31 18-25 I/O Port 2: Port 2 is an 8-bit bidirectional I/O port with internal

pullups. Port 2 pins that have 1s written to them are pulled high

by the internal pullups and can be used as inputs. As inputs,

Port 2 pins that are externally pulled low will source current

because of the internal pullups. (See DC Characteristics: IIL).

Port 2 emits the high order address byte during fetches from

external program memory and during accesses to external

data memory that used 16-bit addresses (MOVX @ DPTR). In

this application, Port 2 uses strong internal pullups when

emitting 1s. During accesses to external data memory that

use 8-bit addresses (MOVX @ Ri [i = 0, 1]), Port 2 emits the

contents of the P2 Special Function Register.

Port 2 also receives the high-order bits and some control

signals during ROM verification.

Integrated Silicon Solution, Inc.

ADVANCE INFORMATION MC018-0A

10/01/98

5

IS80LV51

IS80LV31

®

ISSI

Table 1. Detailed Pin Description

Symbol PDIP PLCC PQFP I/O Name and Function

P3.0-P3.7 10-17 11, 13-19 5, 7-13 I/O Port 3: Port 3 is an 8-bit bidirectional I/O port with internal

10 11 5 I RxD (P3.0): Serial input port.

11 13 7 O TxD (P3.1): Serial output port.

12 14 8 I

13 15 9 I

14 16 10 I T0 (P3.4): Timer 0 external input.

15 17 11 I T1 (P3.5): Timer 1 external input.

16 18 12 O

17 19 13 O

PSEN

29 32 26 O Program Store Enable: The read strobe to external program

(continued)

pullups. Port 3 pins that have 1s written to them are pulled high

by the internal pullups and can be used as inputs. As inputs,

Port 3 pins that are externally pulled low will source current

because of the internal pullups. (See DC Characteristics: IIL).

Port 3 also serves the special features of the IS80LV51/31, as

listed below:

INT0INT0

INT0

(P3.2): External interrupt 0.

INT0INT0

INT1INT1

INT1

(P3.3): External interrupt 1.

INT1INT1

WRWR

WR

(P3.6): External data memory write strobe.

WRWR

RDRD

RD

(P3.7): External data memory read strobe.

RDRD

memory. When the device is executing code from the external

program memory,

cycle except that two

each access to external data memory.

during fetches from internal program memory.

PSEN

is activated twice each machine

PSEN

activations are skipped during

PSEN

is not activated

RST 9 10 4 I Reset: A high on this pin for two machine cycles while the

oscillator is running, resets the device. An internal MOS

resistor to GND permits a power-on reset using only an

external capacitor connected to Vcc.

XTAL 1 19 21 15 I Crystal 1: Input to the inverting oscillator amplifier and

input to the internal clock generator circuits.

XTAL 2 18 20 14 O Crystal 2: Output from the inverting oscillator amplifier.

GND 20 22 16 I Ground: 0V reference.

Vcc 40 44 38 I Power Supply: This is the power supply voltage for operation.

6

Integrated Silicon Solution, Inc.

ADVANCE INFORMATION MC018-0A

10/01/98

IS80LV51

IS80LV31

OPERATING DESCRIPTION

®

ISSI

The detail description of the IS80LV51/31 included in this

description are:

• Memory Map and Registers

• Timer/Counters

• Serial Interface

• Interrupt System

• Other Information

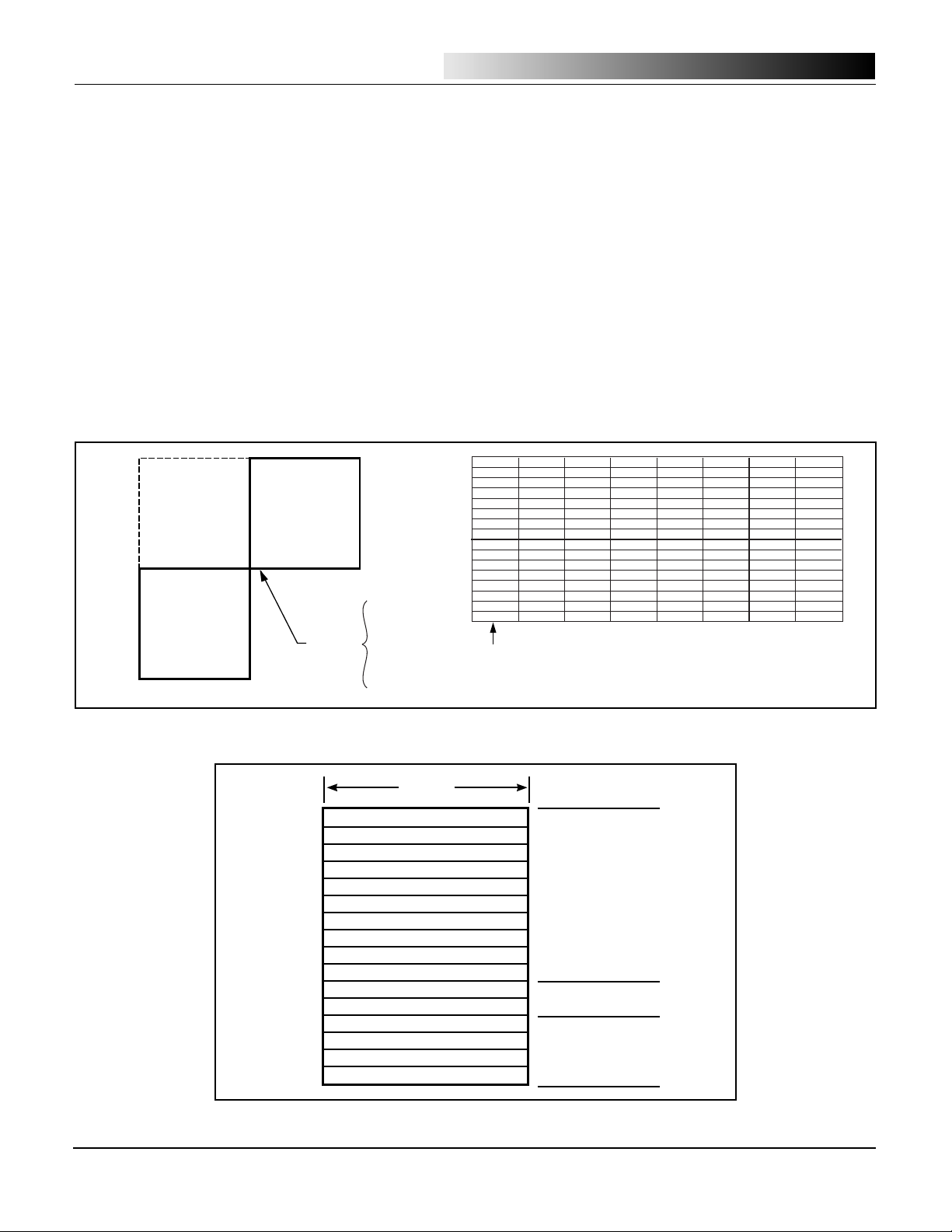

MEMORY MAP AND REGISTERS

Memory

The IS80LV51/31 has separate address spaces for

program and data memory. The program and data memory

can be up to 64K bytes long. The lower 4K program

memory can reside on-chip. (IS80LV51 only) Figure 5

shows a map of the IS80LV51/31 program and data

memory.

The IS80LV51/31 has 128 bytes of on-chip RAM, plus

numbers of special function registers. The lower 128

bytes can be accessed either by direct addressing or by

indirect addressing. Figure 6 shows internal data memory

organization and SFR Memory Map.

The lower 128 bytes of RAM can be divided into three

segments as listed below and shown in Figure 7.

1.

Register Banks 0-3:

locations 00H through 1FH

(32 bytes). The device after reset defaults to register

bank 0. To use the other register banks, the user

must select them in software. Each register bank

contains eight 1-byte registers R0-R7. Reset initializes the stack point to location 07H, and is

incremented once to start from 08H, which is the first

register of the second register bank.

2.

Bit Addressable Area:

16 bytes have been assigned for this segment 20H-2FH. Each one of the

128 bits of this segment can be directly addressed

(0-7FH). Each of the 16 bytes in this segment can

also be addressed as a byte.

3.

Scratch Pad Area:

30H-7FH are available to the

user as data RAM. However, if the data pointer has

been initialized to this area, enough bytes should be

left aside to prevent SP data destruction.

FFFFH:

64K

EA = 0

External

PSEN

Program Memory

(Read Only)

External External

0FFFH:

4K

EA = 1

Internal

0000

00

Data Memory

(Read/Write)

FFFFH

Internal

FFH

80H7FH

0000

Figure 5. IS80LV51/31 Program and Data Memory Structure

RD WR

Integrated Silicon Solution, Inc.

ADVANCE INFORMATION MC018-0A

10/01/98

7

IS80LV51

IS80LV31

SPECIAL FUNCTION REGISTERS

®

ISSI

The Special Function Registers (SFR's) are located in

upper 128 Bytes direct addressing area. The SFR Memory

Map in Figure 6 shows that.

Not all of the addresses are occupied. Unoccupied

addresses are not implemented on the chip. Read

accesses to these addresses in general return random

data, and write accesses have no effect.

User software should not write 1s to these unimplemented

locations, since they may be used in future microcontrollers

to invoke new features. In that case, the reset or inactive

values of the new bits will always be 0, and their active

values will be 1.

The functions of the SFRs are outlined in the following

sections, and detailed in Table 2.

FFH

Upper

128

Lower

128

80H

7FH

0

Not Available

in

IS80LV51/31

Accessible

by Direct

and Indirect

Addressing

Accessible

by Direct

Addressing

Special

Function

Registers

80H

Ports,

Status and

Control Bits,

Timer,

Registers,

Stack Pointer,

Accumulator

(Etc.)

Accumulator (ACC)

ACC is the Accumulator register. The mnemonics for

Accumulator-specific instructions, however, refer to the

Accumulator simply as A.

B Register (B)

The B register is used during multiply and divide operations.

For other instructions it can be treated as another scratch

pad register.

Program Status Word (PSW). The PSW register contains

program status information.

F8

B

F0

E8

ACC

E0

D8

PSW

D0

C8

C0

IP

B8

P3

B0

IE

A8

P2

A0

98

90

88

80

Addressable

SCON

TCON

P1

P0

Bit

SBUF

TMODSPTL0

DPL

TL1

DPH

TH0 TH1

PCON

FF

F7

EF

E7

DF

D7

CF

C7

BF

B7

AF

A7

9F

97

8F

87

Figure 6. Internal Data Memory and SFR Memory Map

8 BYTES

78

70

68

60

58

50

48

40

38

30

28

0 ...

20

18

10

08

00

BANK3

BANK2

BANK 1

BANK 0

...7F

7F

77

6F

67

5F

57

4F

47

3F

37

2F

ADDRESSABLE

27

1F

17

0F

07

SCRATCH

PAD

AREA

BIT

SEGMENT

REGISTER

BANKS

Figure 7. Lower 128 Bytes of Internal RAM

8

Integrated Silicon Solution, Inc.

ADVANCE INFORMATION MC018-0A

10/01/98

IS80LV51

IS80LV31

SPECIAL FUNCTION REGISTERS

(Continued)

®

ISSI

Stack Pointer (SP)

The Stack Pointer Register is eight bits wide. It is

incremented before data is stored during PUSH and

CALL executions. While the stack may reside anywhere

in on-chip RAM, the Stack Pointer is initialized to 07H after

a reset. This causes the stack to begin at location 08H.

Data Pointer (DPTR)

The Data Pointer consists of a high byte (DPH) and a low

byte (DPL). Its function is to hold a 16-bit address. It may

be manipulated as a 16-bit register or as two independent

8-bit registers.

Ports 0 To 3

P0, P1, P2, and P3 are the SFR latches of Ports 0, 1, 2,

and 3, respectively.

Serial Data Buffer (SBUF)

The Serial Data Buffer is actually two separate registers,

a transmit buffer and a receive buffer register. When data

is moved to SBUF, it goes to the transmit buffer, where it

is held for serial transmission. (Moving a byte to SBUF

initiates the transmission.) When data is moved from

SBUF, it comes from the receive buffer.

Timer Registers

Register pairs (TH0, TL0) and (TH1, TL1) are the 16-bit

Counter registers for Timer/Counters 0 and 1, respectively.

Control Registers

Special Function Registers IP, IE, TMOD, TCON, SCON,

and PCON contain control and status bits for the interrupt

system, the Timer/Counters, and the serial port. They are

described in later sections of this chapter.

Integrated Silicon Solution, Inc.

ADVANCE INFORMATION MC018-0A

10/01/98

9

IS80LV51

IS80LV31

Table 2: Special Function Register

Symbol Description Direct Address Bit Address, Symbol, or Alternative Port Function Reset Value

(1)

ACC

(1)

B

DPH Data pointer (DPTR) high 83H 00H

DPL Data pointer (DPTR) low 82H 00H

(1)

IE

(1)

IP

(1)

P0

(1)

P1

(1)

P2

(1)

P3

PCON Power control 87H SMOD — — — GF1 GF0 PD IDL 0XXX0000B

(1)

PSW

SBUF Serial data buffer 99H XXXXXXXXB

(1)

SCON

SP Stack pointer 81H 07H

(1)

TCON

TMOD Timer mode 89H GATE C/

TH0 Timer high 0 8CH 00H

TH1 Timer high 1 8DH 00H

TL0 Timer low 0 8AH 00H

TL1 Timer low 1 8BH 00H

Accumulator E0H E7 E6 E5 E4 E3 E2 E1 E0 00H

B register F0H F7 F6 F5 F4 F3 F2 F1 F0 00H

AF AE AD AC AB AA A9 A8

Interrupt enable A8H EA — — ES ET1 EX1 ET0 EX0 0XX00000B

BF BE BD BC BB BA B9 B8

Interrupt priority B8H — — — PS PT1 PX1 PT0 PX0 XXX00000B

87 86 85 84 83 82 81 80

Port 0 80H P0.7 P0.6 P0.5 P0.4 P0.3 P0.2 P0.1 P0.0 FFH

AD7 AD6 AD5 AD4 AD3 AD2 AD1 AD0

97 96 95 94 93 92 91 90

Port 1 90H P1.7 P1.6 P1.5 P1.4 P1.3 P1.2 P1.1 P1.0 FFH

A7 A6 A5 A4 A3 A2 A1 A0

Port 2 A0H P2.7 P2.6 P2.5 P2.4 P2.3 P2.2 P2.1 P2.0 FFH

AD15 AD14 AD13 AD12 AD11 AD10 AD9 AD8

B7 B6 B5 B4 B3 B2 B1 B0

Port 3 B0H P3.7 P3.6 P3.5 P3.4 P3.3 P3.2 P3.1 P3.0 FFH

RD WR

T1 T0

INT1 INT0

TXD RXD

D7 D6 D5 D4 D3 D2 D1 D0

Program status word D0H CY AC F0 RS1 RS0 OV — P 00H

9F 9E 9D 9C 9B 9A 99 98

Serial controller 98H SM0 SM1 SM2 REN TB8 RB8 TI RI 00H

8F 8E 8D 8C 8B 8A 89 88

Timer control 88H TF1 TR1 TF0 TR0 IE1 IT1 IE0 IT0 00H

T

M1 M0 GATE C/TM1 M0 00H

ISSI

®

Note:

1. Denotes bit addressable.

10

Integrated Silicon Solution, Inc.

ADVANCE INFORMATION MC018-0A

10/01/98

IS80LV51

IS80LV31

®

ISSI

The detail description of each bit is as follows:

PSW:

Program Status Word. Bit Addressable.

76543210

CY AC F0 RS1 RS0 OV — P

Register Description:

CY PSW.7 Carry flag.

AC PSW.6 Auxiliary carry flag.

F0 PSW.5 Flag 0 available to the user for

general purpose.

RS1 PSW.4 Register bank selector bit 1.

RS0 PSW.3 Register bank selector bit 0.

(1)

(1)

OV PSW.2 Overflow flag.

— PSW.1 Usable as a general purpose flag

P PSW.0 Parity flag. Set/Clear by hardware each

instruction cycle to indicate an odd/even

number of “1” bits in the accumulator.

Note:

1. The value presented by RS0 and RS1 selects the corresponding

register bank.

RS1 RS0 R00egister Bank Address

0 0 0 00H-07H

0 1 1 08H-0FH

1 0 2 10H-17H

1 1 3 18H-1FH

PCON:

Power Control Register. Not Bit Addressable.

76543210

SMOD — — — GF1 GF0 PD IDL

Register Description:

SMOD Double baud rate bit. If Timer 1 is used to

generate baud rate and SMOD=1, the baud rate

is doubled when the serial port is used in modes

1, 2, or 3.

— Not implemented, reserve for future use.

— Not implemented, reserve for future use.

— Not implemented, reserve for future use.

GF1 General purpose flag bit.

GF0 General purpose flag bit.

PD Power-down bit. Setting this bit activates power-

down mode.

IDL Idle mode bit. Setting this bit activates idle

mode. If 1s are written to PD and IDL at the

same time, PD takes precedence.

Note:

1. User software should not write 1s to reserved bits. These

bits may be used in future products to invoke new features.

(1)

(1)

(1)

IE:

Interrupt Enable Register. Bit Addressable.

76543210

EA — — ES ET1 EX1 ET0 EX0

Register Description:

EA IE.7 Disable all interrupts. If EA=0, no

interrupt will be acknowledged. If

EA=1, each interrupt source is

individually enabled or disabled by

setting or clearing its enable bit.

— IE.6 Not implemented, reserve for future

— IE.5 Not implemented, reserve for future

ES IE.4 Enable or disable the serial port

ET1 IE.3 Enable or disable the timer 1 overflow

EX1 IE.2 Enable or disable external interrupt 1.

ET0 IE.1 Enable or disable the timer 0 overflow

EX0 IE.0 Enable or disable external interrupt 0.

Note:

To use any of the interrupts in the 80C51 Family, the following three steps must be taken:

1. Set the EA (enable all) bit in the IE register to 1.

2. Set the coresponding individual interrupt enable bit in

the IE register to 1.

3. Begin the interrupt service routine at the corresponding

Vector Address of that interrupt (see below).

Interrupt Source Vector Address

IE0 0003H

TF0 000BH

IE1 0013H

TF1 001BH

RI & TI 0023H

4. In addition, for external interrupts, pins

(P3.2 and P3.3) must be set to 1, and depending on

whether the interrupt is to be level or transition activated,

bits IT0 or IT1 in the TCON register may need to be set to

0 or 1.

ITX = 0 level activated (X = 0, 1)

ITX = 1 transition activated

User software should not write 1s to reserved bits. These

5.

bits may be used in future products to invoke new features.

(5)

use.

(5)

use.

interrupt.

interrupt.

interrupt.

INT0

and

INT1

Integrated Silicon Solution, Inc.

ADVANCE INFORMATION MC018-0A

10/01/98

11

IS80LV51

IS80LV31

®

ISSI

IP:

Interrupt Priority Register. Bit Addressable.

76543210

— — — PS PT1 PX1 PT0 PX0

Register Description:

— IP.7 Not implemented, reserve for future use

— IP.6 Not implemented, reserve for future use

— IP.5 Not implemented, reserve for future use

PS IP.4 Defines Serial Port interrupt priority level

PT1 IP.3 Defines Timer 1 interrupt priority level

PX1 IP.2 Defines External Interrupt 1 priority level

PT0 IP.1 Defines Timer 0 interrupt priority level

PX0 IP.0 Defines External Interrupt 0 priority level

Notes:

1. In order to assign higher priority to an interrupt the

coresponding bit in the IP register must be set to 1. While

an interrupt service is in progress, it cannot be interrupted

by a lower or same level interrupt.

2. Priority within level is only to resolve simultaneous

requests of the same priority level. From high to low,

interrupt sources are listed below:

IE0

TF0

IE1

TF1

RI or TI

User software should not write 1s to reserved bits. These

3.

bits may be used in future products to invoke new features.

(3)

(3)

(3)

TCON:

Timer/Counter Control Register. Bit Addressable

76543210

TF1 TR1 TF0 TR0 IE1 IT1 IE0 IT0

Register Description:

TF1 TCON.7 Timer 1 overflow flag. Set by hardware

when the Timer/Counter 1 overflows.

Cleared by hardware as processor

vectors to the interrupt service routine.

TR1 TCON.6 Timer 1 run control bit. Set/Cleared by

software to turn Timer/Counter 1 ON/

OFF.

TF0 TCON.5 Timer 0 overflow flag. Set by hardware

when the Timer/Counter 0 overflows.

Cleared by hardware as processor

vectors to the interrupt service routine.

TR0 TCON.4 Timer 0 run control bit. Set/Cleared by

software to turn Timer/Counter 0 ON/

OFF.

IE1 TCON.3 External Interrupt 1 edge flag. Set by

hardware when the External Interrupt

edge is detected. Cleared by hardware

when interrupt is processed.

IT1 TCON.2 Interrupt 1 type control bit. Set/Cleared

by software specify falling edge/low

level triggered External Interrupt.

IE0 TCON.1 External Interrupt 0 edge flag. Set by

hardware when the External Interrupt

edge is detected. Cleared by hardware

when interrupt is processed.

IT0 TCON.0 Interrupt 0 type control bit. Set/Cleared

by software specify falling edge/low

level triggered External Interrupt.

12

Integrated Silicon Solution, Inc.

ADVANCE INFORMATION MC018-0A

10/01/98

IS80LV51

IS80LV31

®

ISSI

TMOD:

Timer/Counter Mode Control Register.

Not Bit Addressable.

Timer 1 Timer 0

GATE C/

TT

T

M1 M0 GATE C/

TT

GATE When TRx (in TCON) is set and GATE=1, TIMER/

COUNTERx will run only while INTx pin is high

(hardware control). When GATE=0, TIMER/

COUNTERx will run only while TRx=1 (software

control).

C/

T

Timer or Counter selector. Cleared for Timer

operation (input from internal system clock). Set

for Counter operation (input from Tx input pin).

M1 Mode selector bit.

M0 Mode selector bit.

Note 1:

M1 M0 Operating mode

0 0 Mode 0. (13-bit Timer)

0 1 Mode 1. (16-bit Timer/Counter)

1 0 Mode 2. (8-bit auto-load Timer/

Counter)

1 1 Mode 3. (Splits Timer 0 into TL0 and

TH0. TL0 is an 8-bit Timer/Counter

controller by the standard Timer 0

control bits. TH0 is an 8-bit Timer and

is controlled by Timer 1 control bits.)

1 1 Mode 3. (Timer/Counter 1 stopped).

(1)

(1)

TT

T

M1 M0

TT

SCON:

Serial Port Control Register. Bit Addressable.

76543210

SM0 SM1 SM2 REN TB8 RB8 TI RI

Register Description:

SM0 SCON.7 Serial port mode specifier.

SM1 SCON.6 Serial port mode specifier.

SM2 SCON.5 Enable the multiprocessor com-

munication feature in mode 2 and 3. In

mode 2 or 3, if SM2 is set to 1 then RI

will not be activated if the received 9th

data bit (RB8) is 0. In mode 1, if

SM2=1 then RI will not be activated if

valid stop bit was not received. In

mode 0, SM2 should be 0.

REN SCON.4 Set/Cleared by software to Enable/

Disable reception.

TB8 SCON.3 The 9th bit that will be transmitted in

mode 2 and 3. Set/Cleared by

software.

RB8 SCON.2 In modes 2 and 3, RB8 is the 9th data

bit that was received. In mode 1, if

SM2=0, RB8 is the stop bit that was

received. In mode 0, RB8 is not used.

TI SCON.1 Transmit interrupt flag. Set by

hardware at the end of the 8th bit time

in mode 0, or at the beginning of the

stop bit in the other modes. Must be

cleared by software.

RI SCON.0 Receive interrupt flag. Set by hardware

at the end of the 8th bit time in mode

0, or halfway through the stop bit time

in the other modes (except see SM2).

Must be cleared by software.

(1)

(1)

Integrated Silicon Solution, Inc.

ADVANCE INFORMATION MC018-0A

10/01/98

Note:

SM0 SM1 MODE Description Baud rate

0 0 0 Shift register Fosc/12

0 1 1 8-bit UART Variable

1 0 2 9-bit UART Fosc/64 or

Fosc/32

1 1 3 9-bit UART Variable

13

Loading...

Loading...