ISSI IS61SP6436-117TQI, IS61SP6436-117TQ, IS61SP6436-117PQI, IS61SP6436-117PQ, IS61SP6436-6TQI Datasheet

...

ISS I

®

IS61SP6436

Integrated Silicon Solution, Inc.

1

SR029-1C

08/11/99

This document contains PRELIMINARY data. ISSI reserves the right to make changes to its products at any time without notice in order to improve design and supply the best possible product.

We assume no responsibility for any errors which may appear in this publication. © Copyright 1997, Integrated Silicon Solution, Inc.

FEATURES

• Internal self-timed write cycle

• Individual Byte Write Control and Global Write

• Clock controlled, registered address, data and

control

• Pentium™ or linear burst sequence control

using MODE input

• Three chip enables for simple depth expansion

and address pipelining

• Common data inputs and data outputs

• Power-down control by ZZ input

• JEDEC 100-Pin TQFP and PQFP package

• Single +3.3V power supply

• Two Clock enables and one Clock disable to

eliminate multiple bank bus contention.

• Control pins mode upon power-up:

– MODE in interleave burst mode

– ZZ in normal operation mode

These control pins can be connected to GND

Q

or VCCQ to alter their power-up state

IS S I

®

DESCRIPTION

The ISSI IS61SP6436 is a high-speed, low-power synchronous static RAM designed to provide a burstable, highperformance, secondary cache for the i486™, Pentium™,

680X0™, and PowerPC™ microprocessors. It is organized

as 65,536 words by 36 bits, fabricated with ISSI's advanced

CMOS technology. The device integrates a 2-bit burst counter,

high-speed SRAM core, and high-drive capability outputs into

a single monolithic circuit. All synchronous inputs pass through

registers controlled by a positive-edge-triggered single clock

input.

Write cycles are internally self-timed and are initiated by the

rising edge of the clock input. Write cycles can be from one to

four bytes wide as controlled by the write control inputs.

Separate byte enables allow individual bytes to be written.

BW1

controls DQP1 and DQ1-DQ8,

BW2

controls DQP2 and

DQ9-DQ16,

BW3

controls DQP3 and DQ17-DQ24,

BW4

controls DQP4 and DQ25-DQ32, conditioned by

BWE

being

LOW. A LOW on GW input would cause all bytes to be written.

Bursts can be initiated with either

ADSP

(Address Status

Processor) or

ADSC

(Address Status Cache Controller) input

pins. Subsequent burst addresses can be generated internally by the IS61SP6436 and controlled by the

ADV

(burst

address advance) input pin.

Asynchronous signals include output enable (OE), sleep mode

input (ZZ), clock (CLK) and burst mode input (MODE). A HIGH

input on the ZZ pin puts the SRAM in the power-down state.

When ZZ is pulled LOW (or no connect), the SRAM normally

operates after three cycles of the wake-up period. A LOW

input, i.e., GNDQ, on MODE pin selects LINEAR Burst. A VCCQ

(or no connect) on MODE pin selects INTERLEAVED Burst.

IS61SP6436

64K x 36 SYNCHRONOUS

PIPELINED STATIC RAM

JULY 1999

FAST ACCESS TIME

Symbol Parameter -133 -117 -5 -6 -7 -8 Unit

tKQ Clock Access Time 5 5 5678 ns

tKC Cycle Time 7.5 8.5 10 12 13 15 ns

Frequency 133 117 100 83 75 66 MHz

ISS I

®

IS61SP6436

2

Integrated Silicon Solution, Inc.

SR029-1C

08/11/99

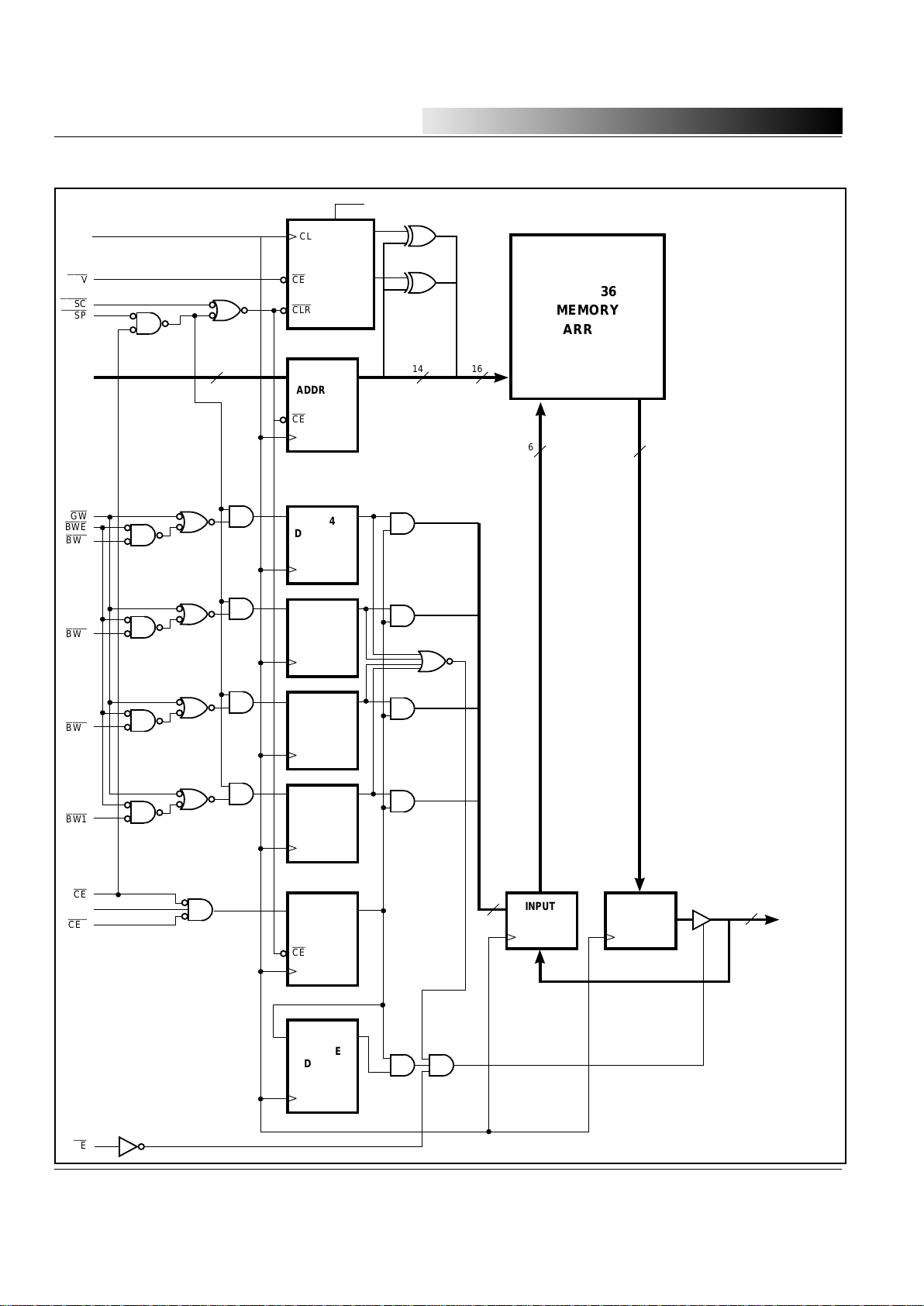

BLOCK DIAGRAM

16

BINARY

COUNTER

A15-A0

BW1

GW

CLR

CE

CLK

Q0

Q1

MODE

A0'

A0

A1

A1'

CLK

ADV

ADSC

ADSP

14 16

ADDRESS

REGISTER

CE

D

CLK

Q

DQP4

DQ32-DQ25

BYTE WRITE

REGISTERS

D

CLK

Q

DQP3

DQ24-DQ17

BYTE WRITE

REGISTERS

D

CLK

Q

DQP2

DQ16-DQ9

BYTE WRITE

REGISTERS

D

CLK

Q

DQP1

DQ8-DQ1

BYTE WRITE

REGISTERS

D

CLK

Q

ENABLE

REGISTER

CE

D

CLK

Q

ENABLE

DELAY

REGISTER

D

CLK

Q

BWE

BW4

CE

CE2

CE2

BW2

BW3

64K x 36

MEMORY

ARRAY

36

INPUT

REGISTERS

CLK

OUTPUT

REGISTERS

CLK

36

OE

4

36

OE

DATA[36:1]

ISS I

®

IS61SP6436

Integrated Silicon Solution, Inc.

3

SR029-1C

08/11/99

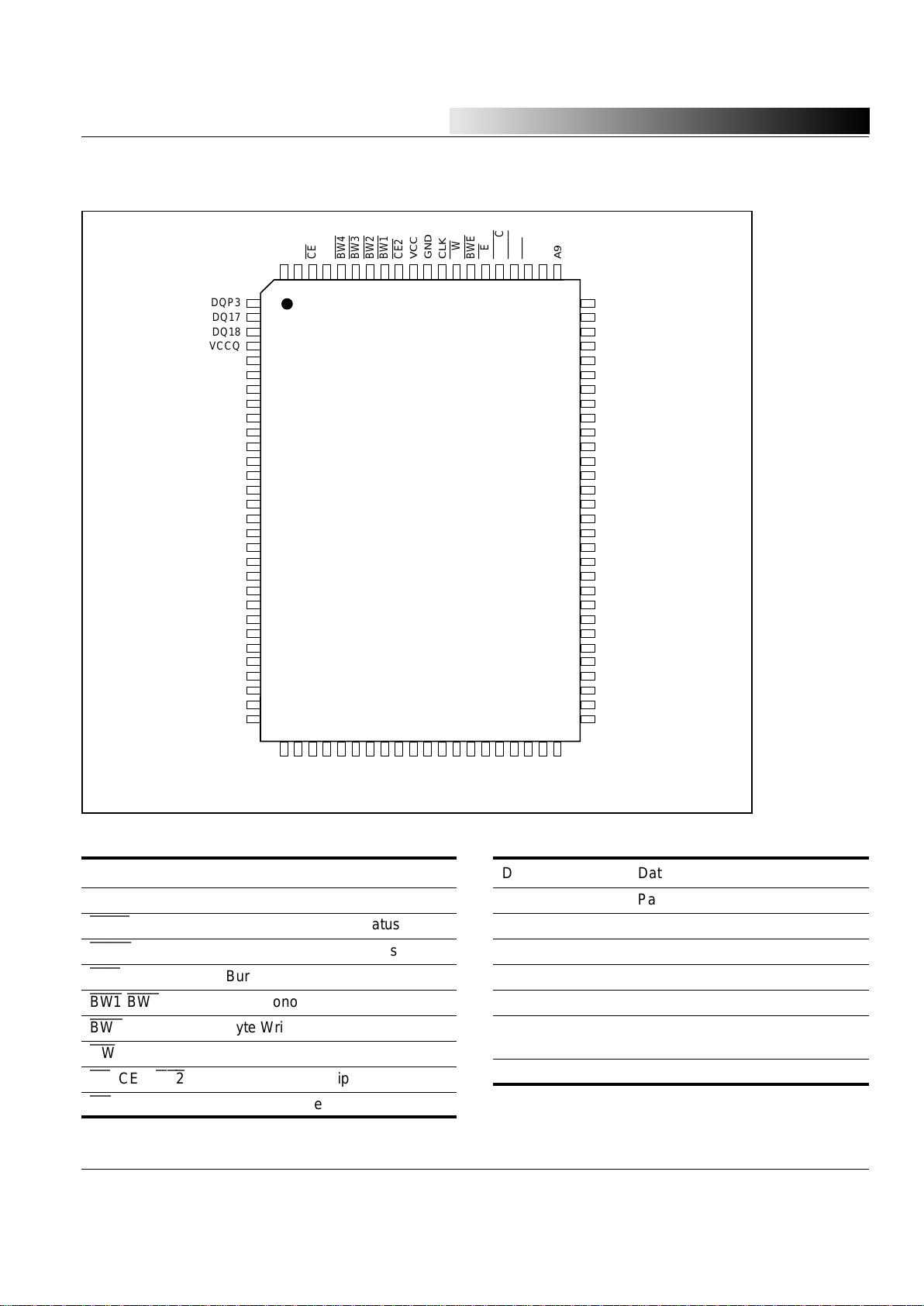

PIN CONFIGURATION

100-Pin TQFP and PQFP (Top View)

DQP2

DQ16

DQ15

VCCQ

GNDQ

DQ14

DQ13

DQ12

DQ11

GNDQ

VCCQ

DQ10

DQ9

GND

NC

VCC

ZZ

DQ8

DQ7

VCCQ

GNDQ

DQ6

DQ5

DQ4

DQ3

GNDQ

VCCQ

DQ2

DQ1

DQP1

A6

A7CECE2

BW4

BW3

BW2

BW1

CE2

VCC

GND

CLK

GW

BWEOEADS

C

ADSPADV

A8

A9

DQP3

DQ17

DQ18

VCCQ

GNDQ

DQ19

DQ20

DQ21

DQ22

GNDQ

VCCQ

DQ23

DQ24

VCCQ

VCC

NC

GND

DQ25

DQ26

VCCQ

GNDQ

DQ27

DQ28

DQ29

DQ30

GNDQ

VCCQ

DQ31

DQ32

DQP4

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

100

99 98 97 96 95 94 93 92 91 90 89 88 87 86 85 84 83 82 81

31 32 33 34 35 36 37 38 39 40 41 42 43 44 45

MODE

A5A4A3A2A1

A0

NC

NC

GND

VCC

NC

NC

A10

A11

A12

A13

A14

A15

NC

46 47 48 49 50

PIN DESCRIPTIONS

A0-A15 Address Inputs

CLK Clock

ADSP

Processor Address Status

ADSC

Controller Address Status

ADV

Burst Address Advance

BW1-BW4

Synchronous Byte Write Enable

BWE

Byte Write Enable

GW

Global Write Enable

CE

, CE2,

CE2

Synchronous Chip Enable

OE

Output Enable

DQ1-DQ32 Data Input/Output

DQP1-DQP4 Parity Inputs/Outputs

ZZ Sleep Mode

MODE Burst Sequence Mode

VCC +3.3V Power Supply

GND Ground

VCCQ Isolated Output Buffer Supply:

+3.3V

GNDQ Isolated Output Buffer Ground

ISS I

®

IS61SP6436

4

Integrated Silicon Solution, Inc.

SR029-1C

08/11/99

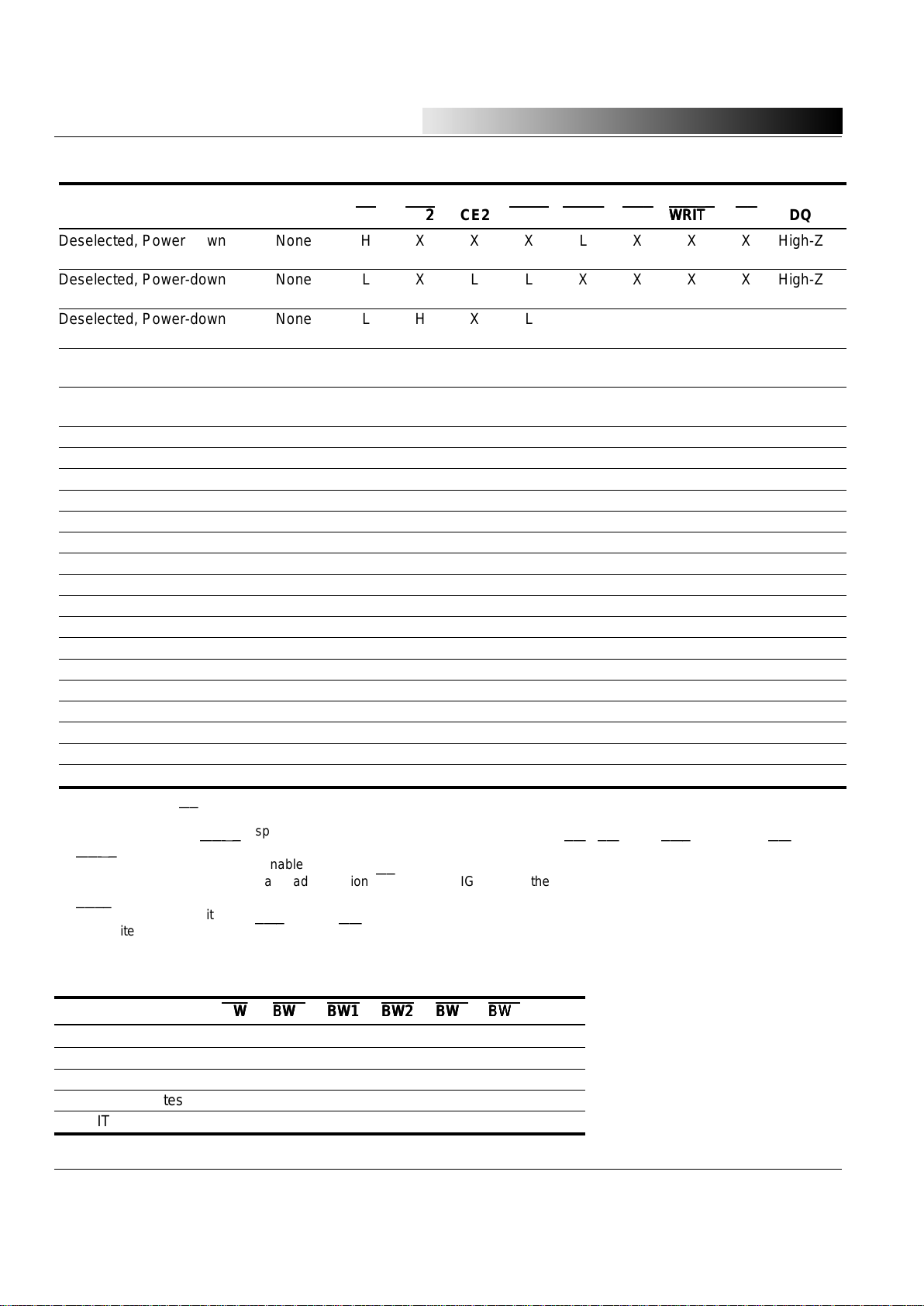

TRUTH TABLE

Address

Operation Used

CECE

CECE

CE

CE2CE2

CE2CE2

CE2

CE2

ADSPADSP

ADSPADSP

ADSP

ADSCADSC

ADSCADSC

ADSC

ADVADV

ADVADV

ADV

WRITEWRITE

WRITEWRITE

WRITE

OEOE

OEOE

OE

DQ

Deselected, Power-down None H X X X L X X X High-Z

Deselected, Power-down None L X L L XXXXHigh-Z

Deselected, Power-down None L H X L XXXXHigh-Z

Deselected, Power-down None L X L H L X X X High-Z

Deselected, Power-down None L H X H L X X X High-Z

Read Cycle, Begin Burst External L L H L X X X L Q

Read Cycle, Begin Burst External L L H L X X X H High-Z

Write Cycle, Begin Burst External L L H H L X L X D

Read Cycle, Begin Burst External L L H H L X H L Q

Read Cycle, Begin Burst External L L H H L X H H High-Z

Read Cycle, Continue Burst Next X X X H H L H L Q

Read Cycle, Continue Burst Next X X X H H L H H High-Z

Read Cycle, Continue Burst Next H X X X H L H L Q

Read Cycle, Continue Burst Next H X X X H L H H High-Z

Write Cycle, Continue Burst Next X X X H H L L X D

Write Cycle, Continue Burst Next H X X X H L L X D

Read Cycle, Suspend Burst Current X X X HHHHLQ

Read Cycle, Suspend Burst Current X X X HHHHHHigh-Z

Read Cycle, Suspend Burst Current H X X X H H H L Q

Read Cycle, Suspend Burst Current H X X X HHHHHigh-Z

Write Cycle, Suspend Burst Current X X X H H H L X D

Write Cycle, Suspend Burst Current H X X X H H L X D

Notes:

1. All inputs except OE must meet setup and hold times for the Low-to-High transition of clock (CLK).

2. Wait states are inserted by suspending burst.

3. X means don't care.

WRITE

=L means any one or more byte write enable signals (BW1-BW4) and

BWE

are LOW or GW is LOW.

WRITE

=H means all byte write enable signals are HIGH.

4. For a Write operation following a Read operation, OE must be HIGH before the input data required setup time and held HIGH

throughout the input data hold time.

5.

ADSP

LOW always initiates an internal READ at the Low-to-High edge of clock. A WRITE is performed by setting one or more

byte write enable signals and

BWE

LOW or GW LOW for the subsequent L-H edge of clock.

PARTIAL TRUTH TABLE

Function

GWGW

GWGW

GW

BWEBWE

BWEBWE

BWE

BW1BW1

BW1BW1

BW1

BW2BW2

BW2BW2

BW2

BW3BW3

BW3BW3

BW3

BW4BW4

BW4BW4

BW4

READ H H X X X X

READ H L H H H H

WRITE Byte 1 H L L H H H

WRITE All Bytes H LLLLL

WRITE All Bytes L XXXXX

ISS I

®

IS61SP6436

Integrated Silicon Solution, Inc.

5

SR029-1C

08/11/99

INTERLEAVED BURST ADDRESS TABLE (MODE = VCCQ or No Connect)

External Address 1st Burst Address 2nd Burst Address 3rd Burst Address

A1 A0 A1 A0 A1 A0 A1 A0

00 01 10 11

01 00 11 10

10 11 00 01

11 10 01 00

LINEAR BURST ADDRESS TABLE (MODE = GNDQ)

0,0

1,0

0,1A1', A0' = 1,1

ABSOLUTE MAXIMUM RATINGS

(1)

Symbol Parameter Value Unit

TBIAS Temperature Under Bias –40 to +85 °C

TSTG Storage Temperature –55 to +150 °C

PD Power Dissipation 1.8 W

IOUT Output Current (per I/O) 100 mA

VIN, VOUT Voltage Relative to GND for I/O Pins –0.5 to VCCQ + 0.3 V

VIN Voltage Relative to GND for –0.5 to 5.5 V

for Address and Control Inputs

VCC Voltage on Vcc Supply Relatiive to GND –0.5 to 4.6 V

Notes:

1. Stress greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause

permanent damage to the device. This is a stress rating only and functional operation of the

device at these or any other conditions above those indicated in the operational sections of

this specification is not implied. Exposure to absolute maximum rating conditions for extended

periods may affect reliability.

2. This device contains circuity to protect the inputs against damage due to high static voltages

or electric fields; however, precautions may be taken to avoid application of any voltage higher

than maximum rated voltages to this high-impedance circuit.

3. This device contains circuitry that will ensure the output devices are in High-Z at power up.

Loading...

Loading...