ISSI IS61LV256 User Manual

IS61LV256

IS61LV256

ISSI

ISS I

32K x 8 LOW VOLT AGE CMOS STA TIC RAM FEBRUARY 1996

®

®

FEATURES

• High-speed access time: 12, 15, 20, 25 ns

• Automatic power-down when chip is deselected

• CMOS low power operation

— 345 mW (max.) operating

— 7 mW (max.) CMOS standby

• TTL compatible interface levels

• Single 3.3V power supply

• Fully static operation: no clock or refresh

required

• Three-state outputs

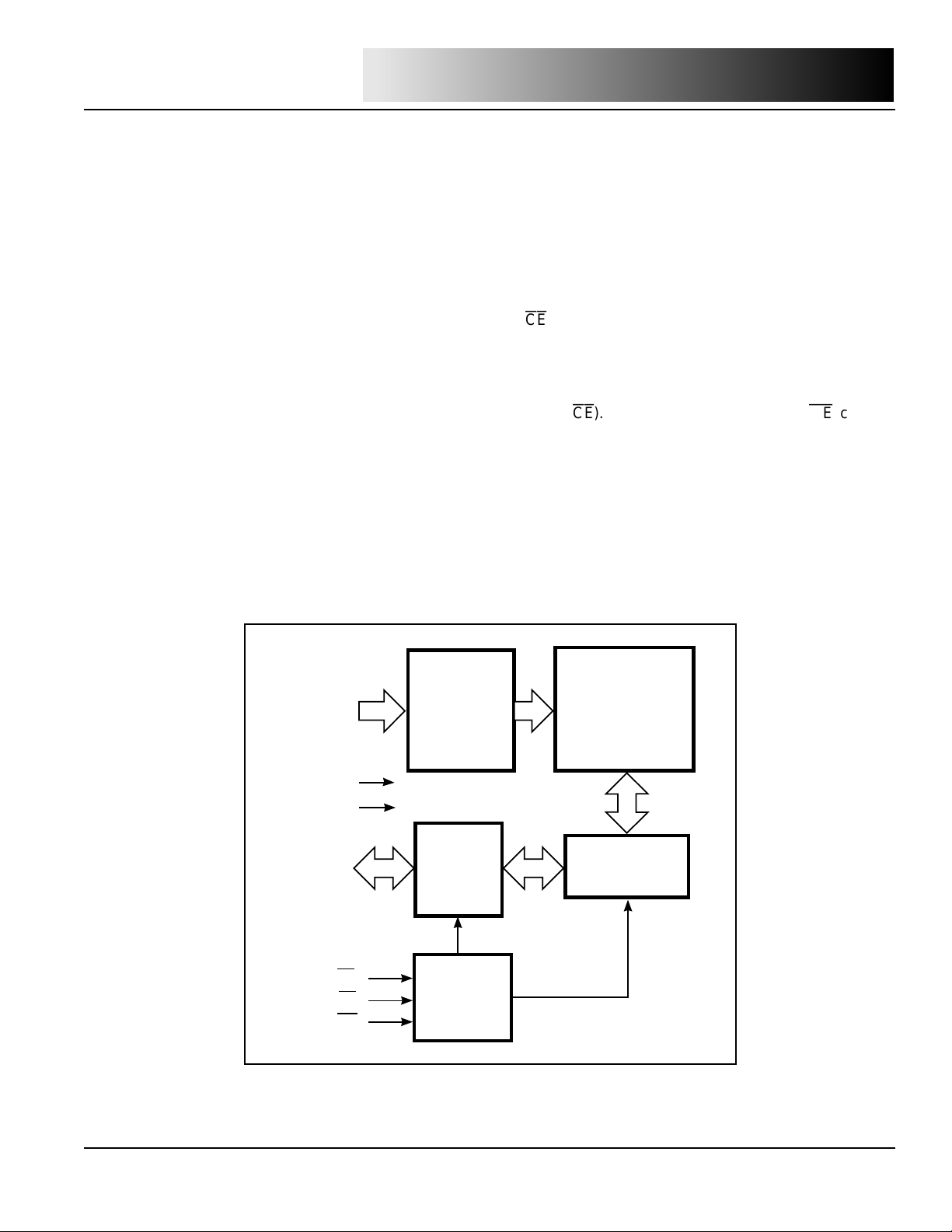

FUNCTIONAL BLOCK DIAGRAM

DESCRIPTION

The ISSI IS61LV256 is a very high-speed, low power,

32,768-word by 8-bit static RAM. It is fabricated using ISSI's

high-performance CMOS technology. This highly reliable process coupled with innovative circuit design techniques, yields

access times as fast as 12 ns maximum.

When CE is HIGH (deselected), the device assumes a standby

mode at which the power dissipation is reduced to

50 µW (typical) with CMOS input levels.

Easy memory expansion is provided by using an active LOW

Chip Enable (CE). The active LOW Write Enable (WE) controls

both writing and reading of the memory.

The IS61LV256 is available in the JEDEC standard 28-pin,

300-mil DIP and SOJ, plus the 450-mil TSOP package.

A0-A14

VCC

GND

I/O0-I/O7

CE

OE

WE

ISSI reserves the right to make changes to its products at any time without notice in order to improve design and supply the best possible product. We assume no responsibility for any errors which

may appear in this publication. © Copyright 1996, Integrated Silicon Solution, Inc.

DECODER

I/O

DATA

CIRCUIT

CONTROL

CIRCUIT

256 X 1024

MEMORY ARRAY

COLUMN I/O

Integrated Silicon Solution, Inc.

Rev. F 0296

SR81995LV61

2-1

ISS I

®

IS61LV256

22

23

24

25

26

27

28

1

2

3

4

5

6

7

21

20

19

18

17

16

15

14

13

12

11

10

9

8

OE

A11

A9

A8

A13

WE

VCC

A14

A12

A7

A6

A5

A4

A3

A10

CE

I/O7

I/O6

I/O5

I/O4

I/O3

GND

I/O2

I/O1

I/O0

A0

A1

A2

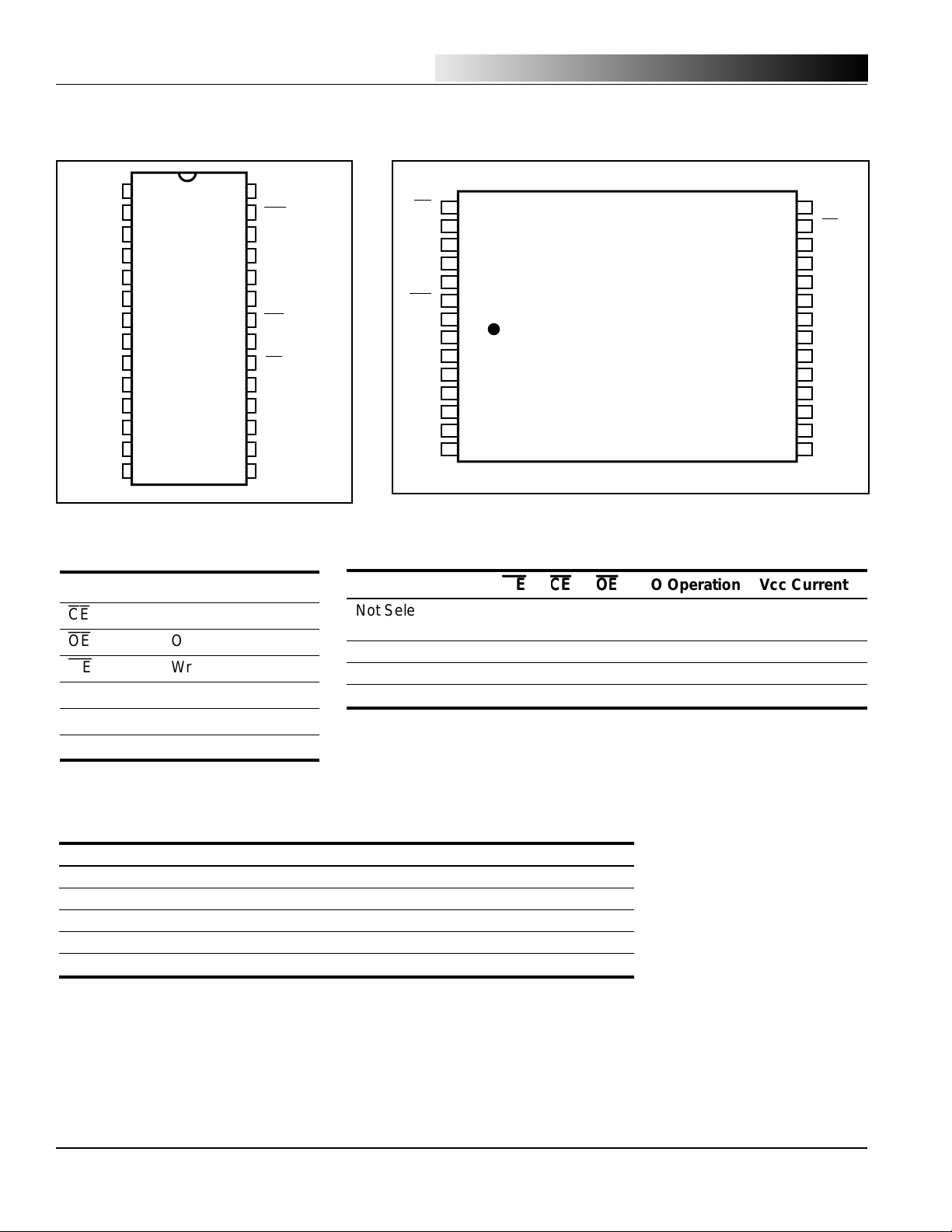

PIN CONFIGURATION

28-Pin DIP and SOJ

A14

A12

A7

A6

A5

A4

A3

A2

A1

A0

I/O0

I/O1

I/O2

GND

1

2

3

4

5

6

7

8

9

10

11

12

13

14

28

27

26

25

24

23

22

21

20

19

18

17

16

15

PIN DESCRIPTIONS

PIN CONFIGURATION

28-Pin TSOP

VCC

WE

A13

A8

A9

A11

OE

A10

CE

I/O7

I/O6

I/O5

I/O4

I/O3

TRUTH TABLE

A0-A14 Address Inputs

CE

OE

WE

Chip Enable Input

Output Enable Input

Write Enable Input

I/O0-I/O7 Input/Output

Mode

Not Selected X H X High-Z ISB1, ISB2

(Power-down)

Output Disabled H L H High-Z ICC1, ICC2

Read H L L DOUT ICC1, ICC2

Write L L X DIN ICC1, ICC2

WEWE

WE

WEWE

Vcc Power

GND Ground

ABSOLUTE MAXIMUM RATINGS

(1)

Symbol Parameter Value Unit

VTERM Terminal Voltage with Respect to GND –0.5 to +4.6 V

TBIAS Temperature Under Bias –55 to +125 °C

TSTG Storage Temperature –65 to +150 °C

PT Power Dissipation 0.5 W

IOUT DC Output Current (LOW) 20 mA

Notes:

1. Stress greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause

permanent damage to the device. This is a stress rating only and functional operation of the

device at these or any other conditions above those indicated in the operational sections of

this specification is not implied. Exposure to absolute maximum rating conditions for extended

periods may affect reliability.

2-2

CECE

CE

CECE

OEOE

OE

I/O Operation Vcc Current

OEOE

Integrated Silicon Solution, Inc.

Rev. F 0296

SR81995LV61

IS61LV256

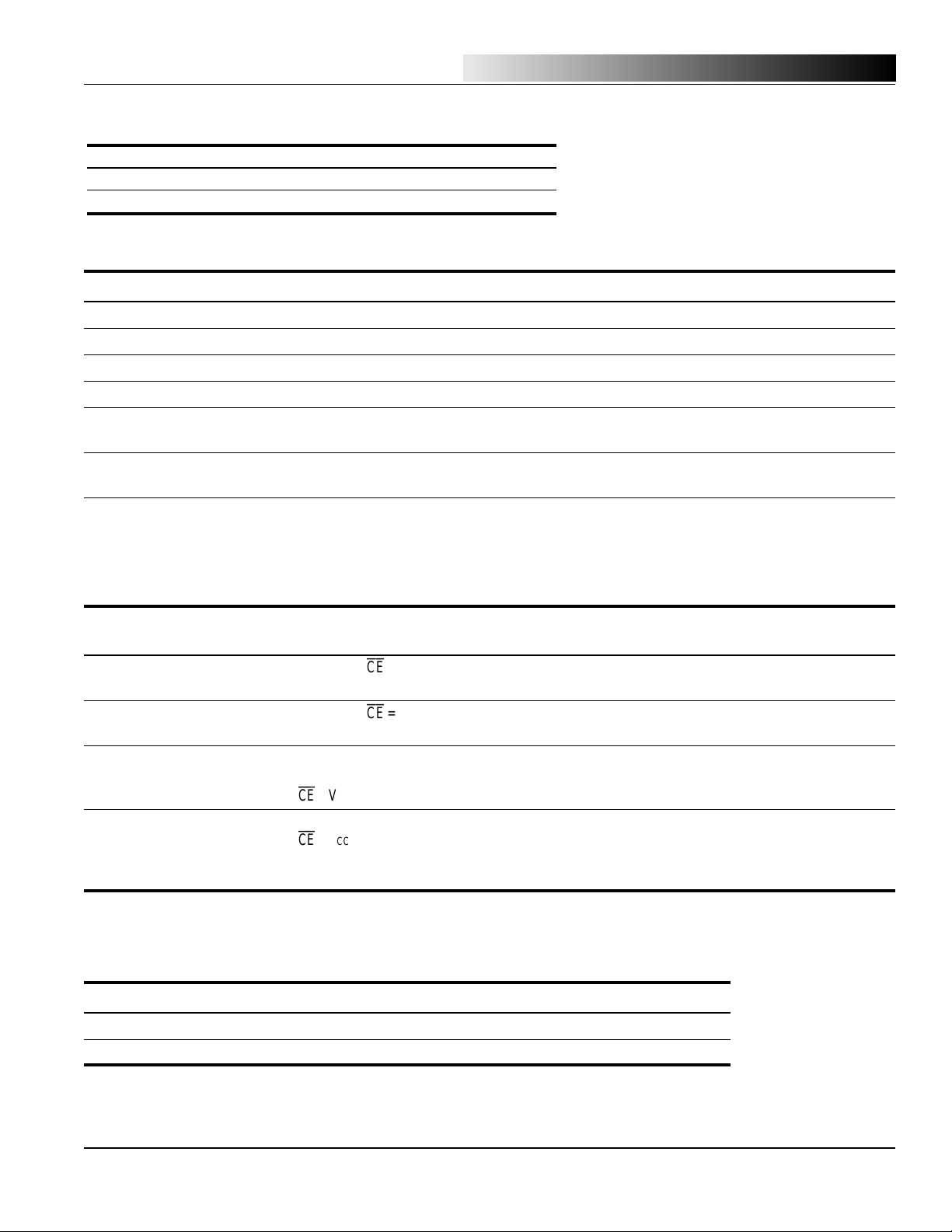

OPERATING RANGE

Range Ambient Temperature VCC

Commercial 0°C to +70°C 3.3V +10%, –5%

Industrial –40°C to +85°C 3.3V ± 5%

DC ELECTRICAL CHARACTERISTICS (Over Operating Range)

Symbol Parameter Test Conditions Min. Max. Unit

VOH Output HIGH Voltage V CC = Min., IOH = –2.0 mA 2.4 — V

VOL Output LOW Voltage VCC = Min., IOL = 4.0 mA — 0.4 V

VIH Input HIGH Voltage 2.2 VCC + 0.3 V

VIL Input LOW Voltage

ILI Input Leakage GND ≤ VIN ≤ VCC Com. –2 2 µA

ILO Output Leakage GND ≤ VOUT ≤ VCC, Outputs Disabled Com. –2 2 µA

(1)

–0.3 0.8 V

Ind. –5 5

Ind. –5 5

®

ISS I

Notes:

1. VIL = –3.0V for pulse width less than 10 ns.

2. Not more than one output should be shorted at one time. Duration of the short circuit should not exceed 30 seconds.

POWER SUPPLY CHARACTERISTICS

(1)

(Over Operating Range)

-12 ns -15 ns -20 ns -25 ns

Symbol Parameter Test Conditions Min. Max. Min. Max. Min. Max. Min. Max. Unit

ICC1 Vcc Operating VCC = Max., CE = VIL Com. — 50 — 50 — 50 — 50 mA

Supply Current IOUT = 0 mA, f = 0 Ind. — — — 60 — 60 — 60

ICC2 Vcc Dynamic Operating VCC = Max., CE = VIL Com. — 100 — 90 — 80 — 70 mA

Supply Current IOUT = 0 mA, f = fMAX Ind. — — — 100 — 90 — 80

ISB1 TTL Standby Current VCC = Max., Com. — 10 — 10 — 10 — 10 mA

(TTL Inputs) VIN = VIH or VIL Ind. — — — 20 — 20 — 20

CE

≥ VIH, f = 0

ISB2 CMOS Standby VCC = Max., Com. — 2 — 2 — 2 — 2 mA

Current (CMOS Inputs)CE ≤ VCC – 0.2V, Ind. — — — 5 — 5 — 5

VIN > VCC – 0.2V, or

VIN ≤ 0.2V, f = 0

Notes:

1. At f = f

CAPACITANCE

MAX, address and data inputs are cycling at the maximum frequency, f = 0 means no input lines change.

(1,2)

Symbol Parameter Conditions Max. Unit

CIN Input Capacitance VIN = 0V 6 pF

COUT Output Capacitance VOUT = 0V 5 pF

Notes:

1. Tested initially and after any design or process changes that may affect these parameters.

2. Test conditions: T

A = 25°C, f = 1 MHz, Vcc = 3.3V.

Integrated Silicon Solution, Inc.

Rev. F 0296

SR81995LV61

2-3

Loading...

Loading...