N-Channel MOSFET

FTP06N40

Applications:

• Ballast and Lighting

• DC-AC Inverter

V

DSS

R

DS(ON)

(Max.) I

400V 1.0 Ω 6A

Features:

• Lead Free

• Low ON Resistance

• Low Gate Charge

• Peak Current vs Pulse Width Curve

• Inductive Switching Curves

Ordering Information

PART NUMBER PACKAGE BRAND

FTP06N40 TO-220 FTP06N40

Absolute Maximum Ratings T

Symbol Parameter Maximum Units

V

DSS

I

D

@ 100 oC Continuous Drain Current Figure 3

D

I

DM

P

D

V

GS

E

AS

I

AS

dv/dt Peak Diode Recovery dv/dt (NOTE *3) 3.0 V/ns

T

L

T

PKG

T

and T

J

Drain-to-Source Voltage (NOTE *1) 400 V

Continuous Drain Current 6

Pulsed Drain Current, VGS@ 10V (NOTE *2) Figure 6

Power Dissipation 89 W

Derating Factor above 25

Gate-to-Source Voltage ± 30 V

Single Pulse Avalanche Engergy

L=500 µH, ID=17.3 Amps

Pulsed Avalanche Rating Figure 8

Maximum Temperature for Soldering

Leads at 0.063in (1.6mm) from Case for 10 seconds

Package Body for 10 seconds

Operating Junction and Storage

STG

Temperature Range

o

C unless otherwise specified

25

=

C

o

C0.71W/

G

D

S

TO-220

Not to Scale

G

75 mJ

300

260

-55 to 150

D

D

S

AI

o

C

o

C

Caution: Stresses greater than those listed in the “Absolute Maximum Ratings” Table may cause permanent damage to the device.

Thermal Resistance

Symbol Parameter Min. Typ. Max. Units Test Conditions

Water cooled heatsink, PD adjusted for a peak junction temperature of +150

o

C

FTP06N40 REV. A April. 2006

R

θJC

R

θJA

Junction-to-Case

Junction-to-Ambient -- -- 62 1 cubic foot chamber, free air.

©2006 InPower Semiconductor Co., Ltd.

-- -- 1.4

o

/W

C

.

OFF Characteristics TJ=25oC unless otherwise specified

Symbol Parameter Min. Typ. Max. Units Test Conditions

BV

∆BV

DSS

DSS

Drain-to-Source Breakdown Voltage 400 -- --

BreakdownVoltage Temperature

/∆ T

J

Coefficient, Figure 11.

-- 0.47 -V/

V

o

C

VGS=0V, ID=250µA

Reference to 25

=250µA

I

D

o

C,

I

DSS

I

GSS

Drain-to-Source Leakage Current

Gate-to-Source Forward Leakage -- -- 100

Gate-to-Source Reverse Leakage -- -- -100 V

ON Characteristics TJ=25

--

-- --

o

unless otherwise specified

C

-- 25

250

µA

nA

=400V, VGS=0V

V

DS

=320V, VGS=0V

V

DS

TJ=125oC

VGS=+30V

= -30V

GS

Symbol Parameter Min. Typ. Max. Units Test Conditions

=10V, ID=3.6A

R

DS(ON)

V

GS(TH)

Static Drain-to-Source On-Resistance

Figure 9 and 10.

Gate Threshold Voltage, Figure 12. 2.0 -- 4.0

gfs Forward Transconductance

-- 0.76 1.0 Ω

--

5.5

-- S

V

V

GS

(NOTE *4)

,

V

V

=

DS

GS

VDS=15V, ID=6A

(NOTE *4)

Dynamic Characteristics Essentially independent of operating temperature

Symbol Parameter Min. Typ. Max. Units Test Conditions

C

iss

C

oss

C

rss

Q

g

Q

gs

Q

gd

Input Capacitance -- 600 --

Output Capacitance -- 105 --

Reverse Transfer Capacitance -- 60 --

Total Gate Charge -- 26.8 --

Gate-to-Source Charge -- 4.6 --

Gate-to-Drain (“Miller”) Charge -- 14.8 --

pF

nC

VGS=0V

V

=25V

DS

f=1.0MHz

Figure 14

VDD=200V

I

D=6A

=10

V

GS

Figure 15

I

D

250µA

=

V

Resistive Switching Characteristics Essentially independent of operating temperature

Symbol Parameter Min. Typ. Max. Units Test Conditions

t

d(ON)

t

rise

t

d(OFF)

t

fall

©2006 InPower Semiconductor Co., Ltd.

Turn-on Delay Time -- 19 --

Rise Time -- 27 -- ID=6A

Turn-Off Delay Time -- 58 -- VGS=10V

ns

Fall Time -- 26 --

VDD=200 V

RG=12Ω

FTP06N40 REV. A April. 2006

Page 2 of 9

Source-Drain Diode Characteristics Tc=25oC unless otherwise specified

Symbol Parameter Min. Typ. Max. Units Test Conditions

I

S

I

SM

V

SD

Reverse Recovery Time -- 310 465 ns VGS=0V

t

rr

Q

rr

Continuous Source Current (Body Diode)

Maximum Pulsed Current (Body Diode)

Diode Forward Voltage

Reverse Recovery Charge -- 640 960

--

--

-- --

-- 6 A Integral pn-diode

--

24 A

1.5

V

nC

in MOSFET

I

=6A, VGS=0V

S

IF=6A, di/dt=100 A/µs

Notes:

*1. TJ = +25oC to +150oC.

*2. Repetitive rating; pulse width limited by maximum junction temperature.

*3. I

= 6A di/dt < 100 A/µs, VDD < BV

SD

*4. Pulse width <

380µs; duty cycle < 2%.

©2006 InPower Semiconductor Co., Ltd.

, TJ=+150oC.

DSS

FTP06N40 REV. A April. 2006

Page 3 of 9

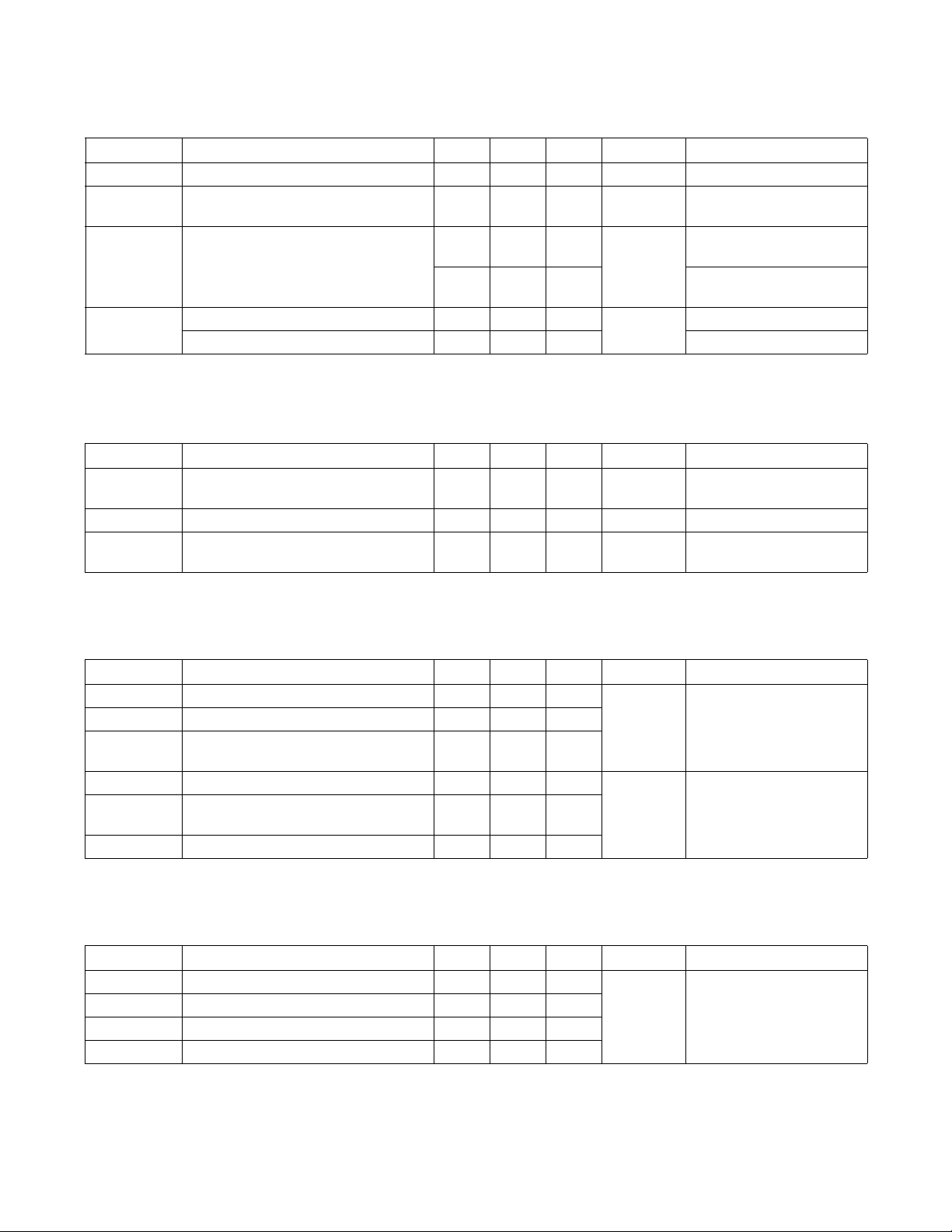

Figure 1. Maximum Effective Thermal Impedance, Junction-to-Case

1.000

Duty Factor

50%

20%

10%

0.100

5

%

P

DM

2%

(Normalized)

, Thermal Impedance

θJC

Z

0.010

1%

single pulse

NOTES:

DUTY FACTOR: D= t1/t2

PEAK TJ=PDM x Z

0.001

1E-05 1E-04 1E-03 1E-02 1E-01 1E+00 1E+01

tp, Rectangular Pulse Duration (s)

θJC

t

1

t

2

x R

θJC+TC

)

W

, Power Dissipation (

P

, Drain Current (A)

D

I

Figure 2.

100

75

50

25

D

0

25

Figure 4. Typical Output Characteristics

15

PULSE DURATION = 250 µS

DUTY FACTOR = 0.5% MAX

TC = 25oC

10

5

0

05

Maximum Power Dissipation

vs Case Temperature

50

V

DS

75

100

TC, Case Temperature (

10

, Drain-to-Source Voltage (V)

125

o

)

C

5

1

=

S

V

G

1

=

S

G

V

5

.

7

=

S

V

G

V

=

7

.

0

V

G

S

VGS = 6.5V

VGS = 6.0V

VGS = 5.5V

VGS = 5.0V

15 20

F i g u r e 3 .

Maximum Continuous Drain Current

vs Case Temperature

6

5

4

3

2

, Drain Current (A)

D

I

1

0

150

25

F i g u r e 5 .

50

75 100 125 150

, Case Temperature (

T

C

o

)

C

Typical Drain-to-Source ON Resistance

vs Gate Voltage and Drain Current

V

V

0

V

2.0

1.5

1.0

ON Resistance (Ω)

RDS(ON), Drain-to-Source

0.5

4

68 16

10 12 14 18 20

VGS, Gate-to-Source Voltage (V)

PULSE DURATION = 250 µS

DUTY FACTOR = 0.5% MAX

TC = 25oC

ID = 12A

I

= 6A

D

ID = 3A

©2006 InPower Semiconductor Co., Ltd.

FTP06N40 REV. A April. 2006

Page 4 of 9

]

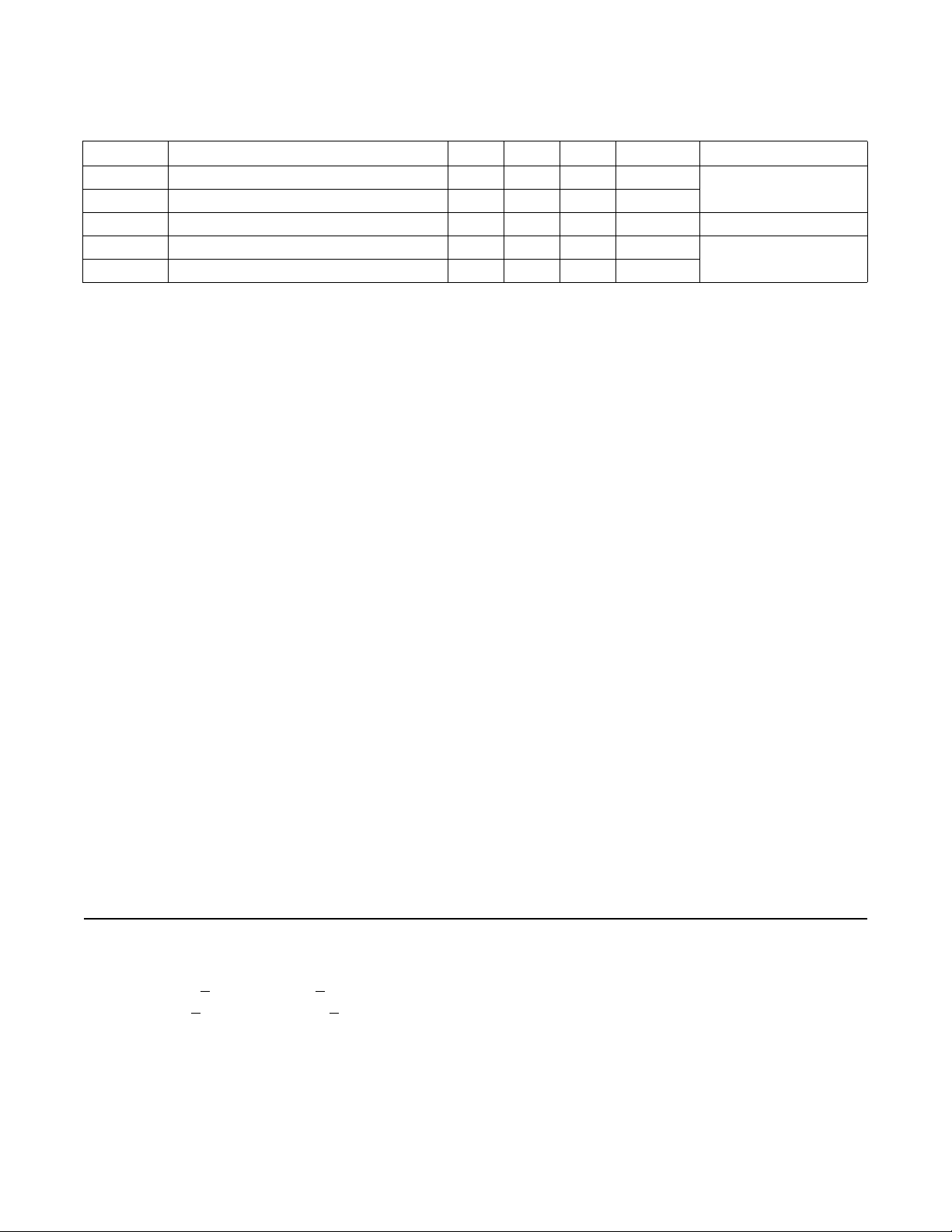

Figure 6. Maximum Peak Current Capability

100

10

, Peak Current (A)

DM

I

VGS = 10V

1

10E-6 100E-6 1E-3 10E-3 100E-3 1E+0 10E+0

TRANSCONDUCTANCE

MAY LIMIT CURRENT IN

THIS REGION

tp, Pulse Width (s)

FOR TEMPERATURES

ABOVE 25oC DERATE PEAK

CURRENT AS FOLLOWS:

II

150 TC–

----------------------=

25

125

, Drain-to-Source Current (A)

D

I

, Drain-to-Source

ON Resistance (Ω)

DS(ON)

R

Figure 7. Typical Transfer Characteristics

20

PULSE DURATION = 250 µs

DUTY CYCLE = 0.5% MAX

18

VDS = 10 V

16

14

12

10

8

6

4

2

0

34 67

2.50

2.25

2.00

1.75

1.50

1.25

1.00

0.75

0.50

+150oC

+25oC

-55oC

5

VGS, Gate-to-Source Voltage (V)

Figure 9.

PULSE DURATION = 2 µs

DUTY CYCLE = 0.5% MAX

TC=25°C

Typical Drain-to-Source ON

Resistance vs Drain Current

ID, Drain Current (A)

VGS = 10V

F i g u r e 8 .

Unclamped Inductive

Switching Capability

100

10

STARTING T

, Avalanche Current (A)

AS

I

Figure 10.

2.6

2.4

2.2

2.0

1.8

1.6

1.4

, Drain-to-Source

1.2

1.0

0.8

DS(ON)

Resistance (Normalized)

R

0.6

0.4

1

1E-6

Typical Drain-to-Source

vs Junction Temperature

-75 -50 -25 0 25 50 75 100 125 1500510

8

15

20

If R= 0: tAV= (L×IAS)/(1.3BV

If R≠ 0: tAV= (L/R) ln[IAS×R)/(1.3BV

R equals total Series resistance of Drain circuit

STARTING TJ = 25oC

= 150oC

J

tAV, Time in Avalanche (s)

PULSE DURATION = 250 µs

DUTY CYCLE = 0.5% MAX

VGS = 10V, ID = 6A

T

, Junction Temperature (

J

DSS-VDD

1E-3

ON

o

)

DSS-VDD

Resistanc

)

C

)+1

10E-310E-6 100E-6

e

©2006 InPower Semiconductor Co., Ltd.

FTP06N40 REV. A April. 2006

Page 5 of 9

1.15

Figure 11.

Typical Breakdown Voltage vs

Junction Temperature

1.2

Figure 12.

Typical Threshold Voltage vs

Junction Temperature

, Drain-to-Source

DSS

BV

Breakdown Voltage (Normalized)

, Drain Current (A)

D

I

1.10

1.05

1.00

0.95

0.90

100.0

10.0

1.0

0.1

-75

-25 0.0 25 50 75 100 125

-50

TJ, Junction Temperature (oC)

Figure 13.

TJ = MAX RATED,

TC = 25oC

OPERATION IN THIS AREA MAY

BE LIMITED BY R

1

Maximum Forward Bias Safe

Operating Area

10

V

, Drain-to-Source Voltage (V)

DS

DS(ON)

1.1

1.0

0.9

, Threshold Voltage

(Normalized)

0.8

GS(TH)

VGS = 0V

ID = 250 µA

150

0.7

0.6

V

V

=

D

S

G

S

A

2

0

µ

=

5

I

D

V

-75 -50 -25 50 10075 125 150250.0

T

, Junction Temperature (oC)

J

Figure 14.

Typical Capacitance vs

Drain-to-Source Voltage

10000

1

0

µ

s

1

0

0

µ

s

1

.

0

m

s

1

0

m

s

D

C

100 0.01 1 10 100

1000

1000

100

VGS = 0V, f = 1MHz

C

= Cgs + C

C, Capacitance (pF)

iss

C

oss

C

rss

≅ Cds + C

= C

gd

10

0.1

gd

gd

VDS, Drain Voltage (V)

C

C

C

iss

oss

rss

1000

Figure 15.

Typical Gate Charge

vs Gate-to-Source Voltage

12

10

VDS = 100V

8

VDS = 200V

VDS = 300V

6

4

2

, Gate-to-Source Voltage (V)

GS

V

0

5

0 0.2 0.4 0.6 0.8 1.0 1.21510

Q

, Total Gate Charge (nC)

G

©2006 InPower Semiconductor Co., Ltd.

ID = 6A

2520

Figure 16.

Typical Body Diode Transfer

Characteristics

60

50

40

30

+150oC

5

2

+

5

-

5

o

C

o

C

20

, Reverse Drain Current (A)

10

SD

I

VGS = 0V

0

30

, Source-to-Drain Voltage (V)

V

SD

1.4

1.6

FTP06N40 REV. A April. 2006

Page 6 of 9

Test Circuits and Waveforms

V

DS

V

GS

I

D

D.U.T.

V

DD

V

GS(TH)

V

DS

I

D

Miller

V

GS

Region

1 mA

Figure 17. Gate Charge Test Circuit Figure 18. Gate Charge Waveform

V

R

L

V

DS

V

GS

R

G

D.U.T.

V

DD

DS

90%

10%

V

GS

Q

gs

Q

gd

Q

g

t

d(ON)

Figure 19. Resistive Switching Test Circuit Figure 20. Resistive Switching Waveforms

©2006 InPower Semiconductor Co., Ltd.

t

rise

FTP06N40 REV. A April. 2006

Page 7 of 9

t

d(OFF)

t

fall

Test Circuits and Waveforms

di/dt adj.

Current

Pump

Double Pulse

D.U.T.

I

D

Figure 21. Diode Reverse Recovery Test Circuit

I

di/dt = 100A/µA

D

V

DD

Q

rr

L

Figure 22. Diode Reverse Recovery Waveform

t

rr

BV

DSS

Series Switch

(MOSFET)

I

AS

V

DD

V

DD

BV

DSS

D.U.T.

L

Commutating

Diode

V

GS

Figure 23. Unclamped Inductive Switching Test Circuit Figure 24. Unclamped Inductive Switching Waveforms

50Ω

I

AS

V

GS

0

t

p

E

=

AS

AS

t

AV

2

LI

2

©2006 InPower Semiconductor Co., Ltd.

FTP06N40 REV. A April. 2006

Page 8 of 9

Disclaimers:

InPower Semiconductor Co., Ltd (IPS) reserves the right to make changes without notice in order to improve reliability,

function or design and to discontinue any product or service without notice. Customers should obtain the latest relevant

information before orders and should verify that such information is current and complete. All products are sold subject to

IPS’s terms and conditions supplied at the time of order acknowledgement.

InPower Semiconductor Co., Ltd warrants performance of its hardware products to the specifications at the time o f sale,

Testing, reliability and quality control are used to the extent IPS deems necessary to support this warrantee. Except where

agreed upon by contractual agreement, testing of all parameters of each product is not necessarily performed.

InPower Semiconductor Co., Ltd does not assume any liability arising from the use of any product or circuit designs described

herein. Customers are responsible for their products and applications using IPS’s components. To minimize risk, customers

must provide adequate design and operating safeguards.

InPower Semiconductor Co., Ltd does not warrant or convey any license either expressed or implied under its patent right s,

nor the rights of others. Reproduction of information in IPS’s data sheets or data books is permissible only if reproduction is

without modification or alteration. Reproduction of this information with any alteration is an unfair and deceptive business

practice. InPower Semiconductor Co., Ltd is not responsible or liable for such alter e d do cu men t ati o n.

Resale of IPS’s products with statements different from or beyond the parameters stated by InPower Semiconductor Co., Ltd

for that product or service voids all express or implied warrantees for the associated IPS’s product or service and is unfair and

deceptive business practice. InPower Semiconductor Co., Ltd is not responsible or liable for any such statements.

Life Support Policy:

InPower Semiconductor Co., Ltd’s products are not authorized for use as critical components in life support devices or

systems without the expressed written approval of InPower Semiconductor Co., Ltd.

As used herein:

1. Life support devices or systems are devices or systems which:

a. are intended for surgical implant into the human body,

b. support or sustain life,

c. whose failure to perform when properly used in accordance with instructions

for used provided in the labeling, can be reasonably expected to result in significant

injury to the user.

2. A critical component is any component of a life support device or system whose failure to perform can be reasoably

expected to cause the failure of the life support device or system. or to affect its safety oreffectiveness.

©2006 InPower Semiconductor Co., Ltd.

FTP06N40 REV. A April. 2006

Page 9 of 9

Loading...

Loading...