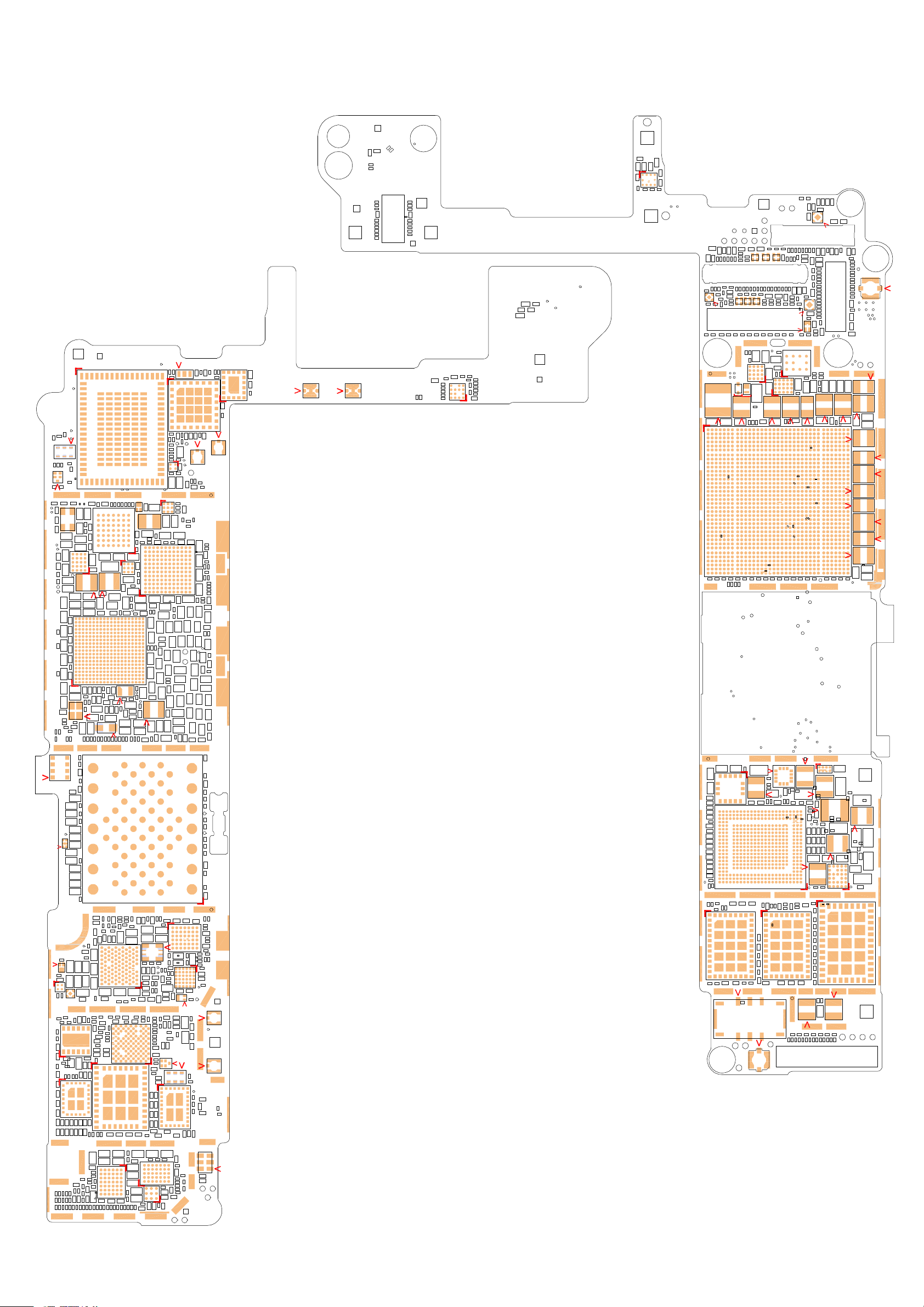

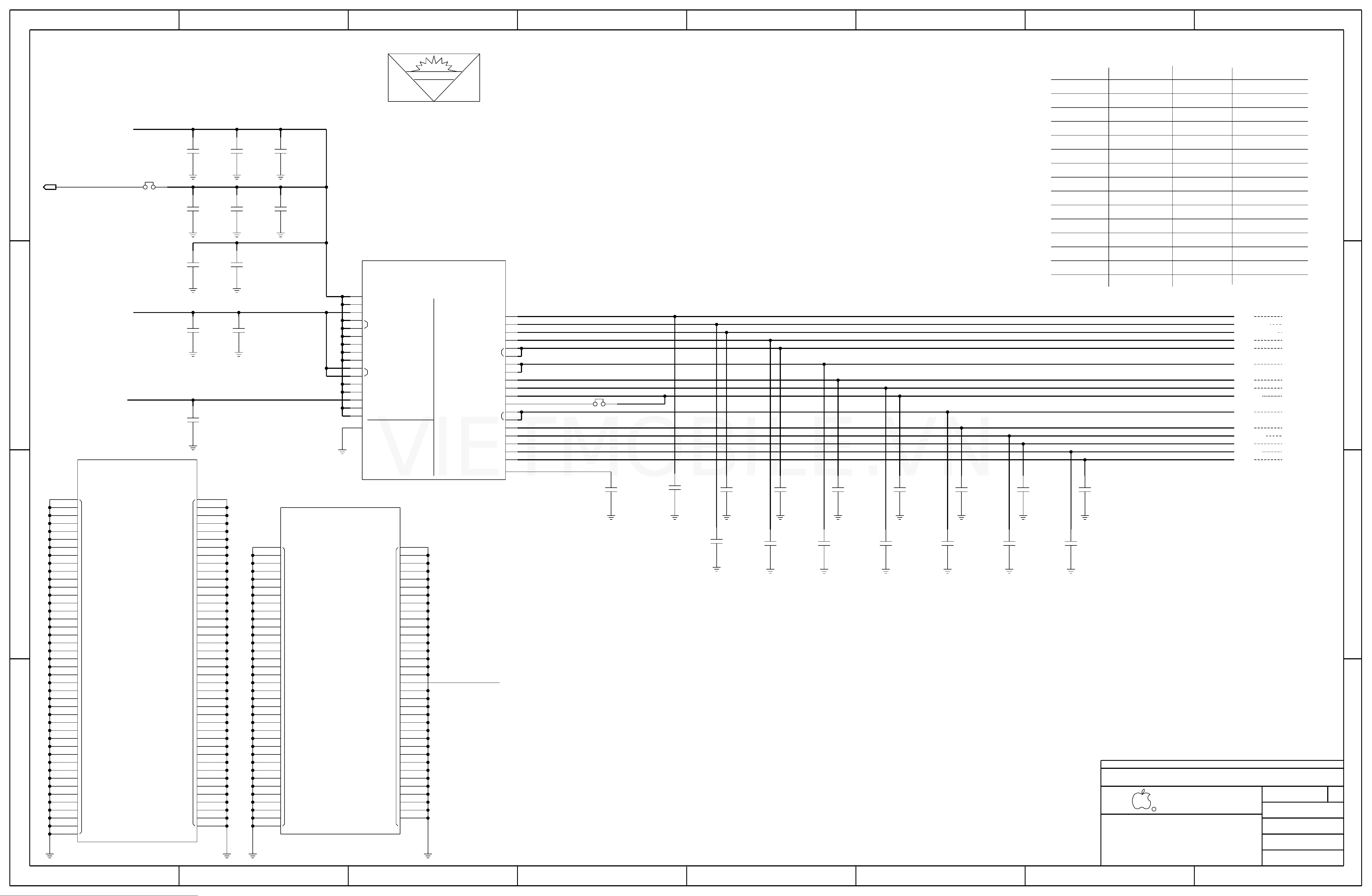

Page 1

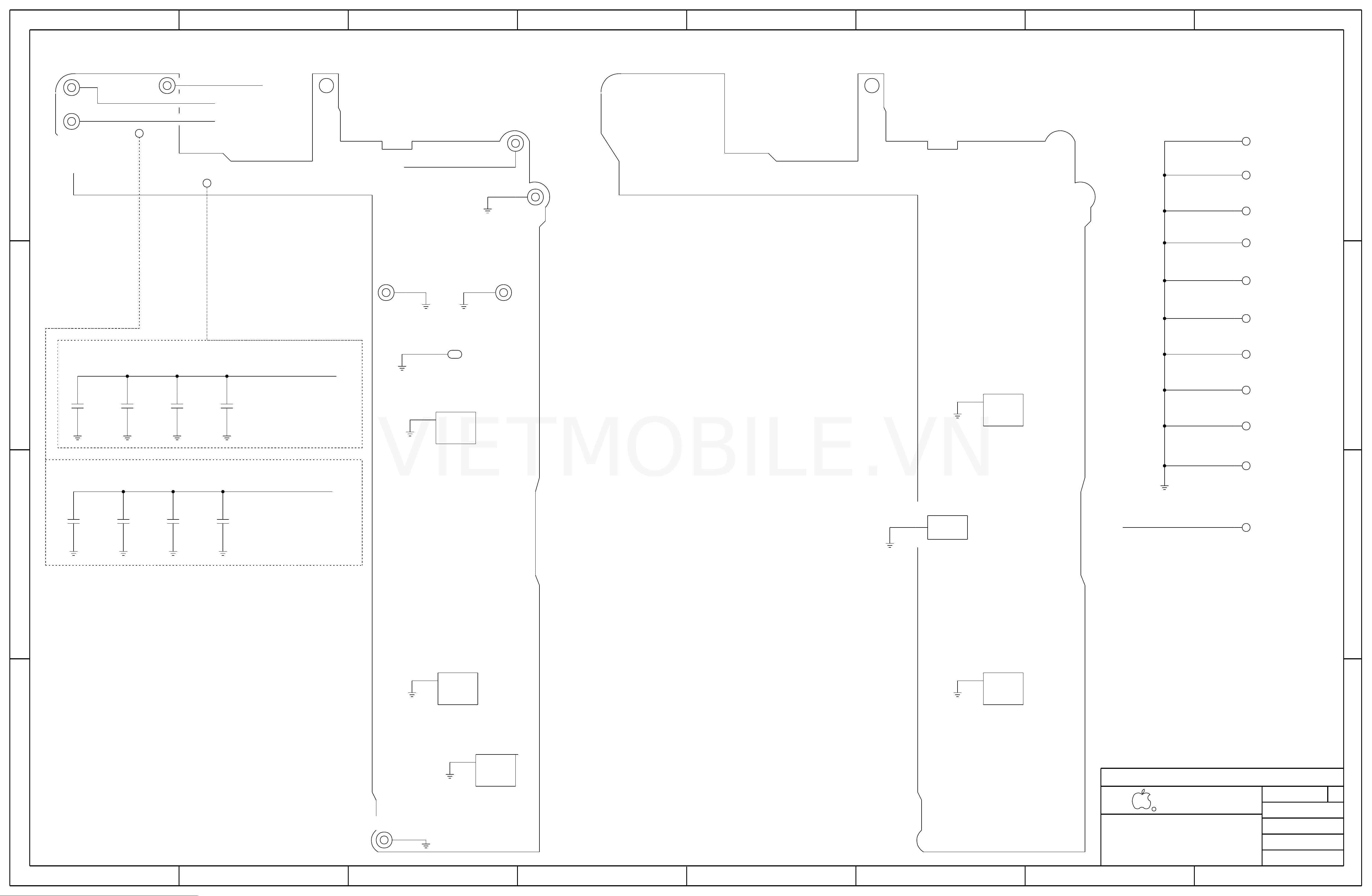

820-5507-A

N71

PP3063_RF

PP3062_RF

UEPRM_RF

C5210_RF

F5201_RF

L5202_RF

R5304_RF

PP3006_RF

PP3019_RF

PP0901

PP0900

C3406_RF

R4106_RF

C2230

C4507_RF

C4212_RF

L5400_RF

C5408_RF

no_refdes+3

C5404_RF

C5402_RF

TP3_RF

C5407_RF

L5401_RF

U5411_RF

no_refdes+7

TOP

C5409_RF

L5403_RF

L5402_RF

C5403_RF

C5405_RF

C5401_RF

PP3002_RF

TP23

PP3001_RF

C4202

C4200

FL4200

C4215

C4204

C4209

C4207

FL4209

FL4255

C4255

C4254

C4231

FL4231

R4240

FL4254

FL3151

U4240

C4240

DZ3151

FL3152

DZ3152

DZ3154

Z3153

D

BS0501

PP3067_RF

PP3064_RF

SH0500

L4020

C4020

C4021

XW1100

R0940 R0941

R0910R0909 R0730

PP3010_RF

PP3008_RF

SH0501

C2123

C2126

C2124

C3116_RF

C3123_RF

C3110_RF

C3113_RF

C3205_RF

R3303_RF

C3203_RF

C3107_RF

C3212_RF

C3214_RF

C3204_RF

C3218_RF

C3210_RF

C3104_RF

C3208_RF

C3211_RF

C3202_RF

C3301_RF

R3410_RF

PP3054_RF

C3404_RF

R4104_RF

L4104_RF

C4107_RF

R4301_RF

C4308_RF

C4301_RF

C4302_RF

BS0500

FD0501

TP22

PP07PP08

FD0511

TP20

TP06TP 07TP16 TP17

TP21

FL4208

FL4205

C4201

R4220

C4205

C4203

R4222

FL4221

C4221

C4222

C4206

C4208

FL4207

J4200

FL4253

FL4220

C4210

C4220

C4253

C4252

C4223

C4230

C4224

FL4210

FL4230

C3127

R3143

FL3102

FL4252

C3103

C3102

XW1110

R0400

C4309_RF

R3144

L3100

L3101L3102

J3100

C3112C3144

C3104

C3111 C3110 C3100

C3125

FL3125

FL3111

L4040

R4020

PP3065_RF

PP3066_RF

U4020

D4021

D4020

C4023

C4022

L4021

R0803

R0802

R0801

C3387

XW0740

R0407

R0405

R0406

R0408

R0402

R0401

R0403

PP1023

PP0903

PP0902

PP3011_RF

PP3009_RF

PP3077_RF

C1501C1502

C3010

C3848

U3010

L3800

C3209_RF

C3013

C4305_RF

L4301_RF

L4304_RF

UMBPA_RF

C4408_RF

L4404_RF

L4305_RF

L4302_RF

C4306_RF

C4307_RF

L4303_RF

L4306_RF

L4407_RF

C3905_RF

XW2400

J2400

TP02TP 03

TP00

FL4232

PP5305_RF

C4041

C1313

R3031

R3030

U_BB_RF

L3904_RF

C3904_RF

J_LAT_RF

R2220

C2220

TP5304_RF

L4200L4201 L4202

FL4250

C4250

C4232

C3129

C3130

FL3126

C3126

C3143

C3145

C3146

CL0502

R3142

C3396

C3373

C3394

L3300

C3386

U0600

XW2070

R1201

R0404

R0640

R3032

C3895

PP3073_RF

C3216_RF

C0715

C0716

C3913_RF

C3915_RF

XW3801_RF

C4406_RF

TP15

C4241

L3902_RF

C3232

FL3231FL3232

C3140C3113

C2115

C3308

U3030

C3902_RF

TP5303_RF

FL4213

FL4251

FL4241

C3128

C3121

C3120

C3010_RF

U3300

R1200

R0409

C3031

R3302_RF

PP3037_RF

UHBP A_RF

C3231

C4213

C4251

DZ3150

DZ3155

R1204

100

no_refdes+2

PP3020_RF

PP3013_RF

C3032

XW3611_RF

R3301_RF

XW3501_RF

L4603_RF

SH0502

FL4614

C3299

FL3230

C4211

C4212

C3122

R3141

DZ3156

L2040

XW2

XW2105

PP1505

R3412_RF

XW3614_RF

XW3615_RF

PP3034_RF

PP3017_RF

L3903_RF

C3903_RF

C3914_RF

C4614

C3230

FL3150

XW3630

U5101_RF

XW2200

R0410

J3001_RF

L4601_RF

C4604_RF

FL4620

C4620

C3233

C3234

C3124

FL3156

Q3140

C2043

C2044

C1301

XW2040

XW2210

PP3014_RF

PP1504

PP3012_RF

PP3080_RF

no_refdes+1

XW3612_RF

R3411_RF

FL4624

C3201

C3123

FL4107

R3140

R0950

XW2030

R0411

PP0600

PP0601

PP3076_RF

PP3084_RF

L3605_RF

C3302_RF

C3219_RF

C5101_RF

XW3613_RF

C3901_RF

L3922_RF

C4624

C5313_RF

C3210

C3202

FL4211

FL4212

FL4110

FL3202

U4100

C4128

C2040

L2041

C2041

R0951

R0945

PP3081_RF

PP3085_RF

PP3016_RF

C3613_RF

PP3036_RF

R3305_RF

C3229_RF

C3122_RF

C3111_RF

C3124_RF

L3901_RF

L2300

FL4621

R4640

C4622

C4640

FL4105

R3014_RF

XW1120

XW2220

C4102

R4130

XW2050

PP1502

C3102_RF

C3121_RF

C3403_RF

C4202_RF

C5312_RF

C5314_RF

J3200

FL3200

C4104

C4103

FL4100

FL4112

C4118

R4117

C4127

R4116

R4111

R4115

C4106

C2042

XW2080

230

240

PP0610

XW3619_RF

C3119_RF

C4410_RF

L4222_RF

C4203_RF

C4403_RF

C4621

C5315_RF

C3200

C4105

FL4120

R0807

R0806

R0911

R0809

C2032

C1310

XW2

XW2

PP1503

PP1500

UBUFR_RF

C3206_RF

C3207_RF

R3306_RF

C3117_RF

C3112_RF

C3701_RF

C3702_RF

L3703_RF

R3409_RF

C4201_RF

L4221_RF L4223_RF

L4224_RF

C2302

C2125

C4623

C3103_RF

R3703_RF

C4612

C5318_RF

C3211

C4100

C4101

C4110

C4112

C4117

C4116

C4111

C4115

C4107

C4124

C0730

PP3051_RFPP3074_RF

PP3052_RF

C3114_RF

C3106_RF

C2301

FL4611R4622

R4623

C5319_RF

U3200

C3221

PP5203_RF

R0808

C2030

L2030

L3602_RF

XW3605_RF

XW3604_RF

XW3610_RF

C3109_RF

C3708_RF

XW3802_RF

C4611

DZ4603

C3220

L3601_RF

XW3607_RF

XW3803_RF

C4606

J4600

C5316_RF

J4100

PP5202_RF

BS0502

C2031

R0960

C1322

PP1501

L3604_RF

XW3701_RF

L3700

DZ4602

C3204

FL3220

PP0906

C3610_RF

XW3608_RF

XW3606_RF

XW3609_RF

C3704_RF

U_QPT_RF

FL4606

TP01

C3203

C3205

C2050

XW3618_RF

BS0505

C3206

C4120

C4121

PP5201_RF

PP5200_RF

L2050

C2122

R2240

PP3091_RF

R3414_RF

C3612_RF

PP3090_RF

ULBPA_RF

C4131

C4134

C4133

C4132

C4125

C2051

XW3616_RF

XW3702_RF

C3707_RF

C4126

PP5297_RF

PP5298_RF

C4123

C4122

C2240

FL3201

R3203

R4131

C4130

FL4130

PP4100

FL4131

FL4134

R4125

PP5301_RF

C2023

XW0650

C2006

no_refdes+8

L3603_RF

C3609_RF

XW3601_RF

XW3602_RF

XW3603_RF

C3706_RF

C3705_RF

L3704_RF

PP5296_RF

PP5293_RF

PP5300_RF

L2021

L2020

C2025

C2026

L2010

L2013

L2003

L2000

C2001

C2007

L3702_RF

no_refdes+6

TP12TP13 TP14

PP5295_RF

PP5292_RF

TP18TP 19

L2011

L2012

L2002

L2001

C3611_RF

C3614_RF

L3701_RF

BS0503

JWLA T_RF

PP5299_RF

PP5289_RF

XW3617_RF

no_refdes+10

C0552

C0553

C5132_RF

no_refdes+9

R5132_RF

FL4712

BS0507

C0551

TPUAT_RF

C0550

C4712

DZ4712

DZ4713

DZ4711

C4700

FL4700

C4701

FL4701

C4702

FL4702

FD0503

FL4720

C4720

DZ4710

J4700

XW3620

R4710

C4722

C4721

C4724

no_refdes+4no_refdes+5

C4723

FD0510

TP5102_RF

TP5100_RF

L5122_RF

C5112_RF

C5122_RF

TP5101_RF

C5111_RF

L5112_RF

FD0504

C4713

C4710

FL4713

R4720

C3000

R2210

C2210

C0540

C3008

C0543

C3002

C0542

C3001

C3006

C0541

C3003

U3000

C3004

FL4711

C3007

C3005

C4711

FD0513

BS0506

BS0508

BOT

FD0502

FD0512

PP5303_RF

C5304_RF

L4000

C0611

L4220_RF

L4212_RF

C5324_RF

C4006

C4000

R2270

C2000

C2060

C0703

C3215_RF

C3503_RF

C3618_RF C3632_RF

L3919_RF

L3912_RF

L3910_RF

C3921_RF

L4502_RF

L4804_RF

C3740

R3701

R3702

R3703

C4698

C0610

C0707

C3629_RF

C3624_RF

C3617_RF

R3508_RF

L3905_RF

L3911_RF

C3922_RF

C3730

C3701

DZ4601

C5330_RF

C2108

C5317_RF

C5321_RF

L5303_RF

C1314

L2080

C1241

C1151

C2094C2093C2090

U2000

C2250

R2250

C2270

C0752

C2131

C2202

C1250

C0751

C1203

C0731

L2060

C0701

C0702

C0706

C0708

C3405_RF

C1504

R3004_RF

C1517

DZ30 1_RF

R3413_RF

R3507_RF

R3603_RF

C3621_RF

C3606_RF

C3607_RF

C3916_RF

C3917_RF

C3906_RF

L3907_RF

L3906_RF

C3910_RF

C3911_RF

C3909_RF

C3812_RF

C3805_RF

C4214_RF

C4801_RF

C4802_RF

C3744

C3743

C3709

C3705

U3700

C3704

XW3702

XW3701

FL4600

C3729

C4699

C4610

FL4610

DZ4600

R0805

C2104

C1330

C0750

C3640_RF

C3223_RF

C3918_RF

C4641

PP5286_RF

R0804

C1153

C0741

C1320

C0718

C0705

C3002_RF

C3605_RF

C3907_RF

C3806_RF

C3813_RF

L4801_RF

C4804_RF

C3741

C3742

FL4641

FL4642

C2080

R5213_RF

U5301_RF

C0743

C0717

R1500

R3501_RF

C3627_RF

UDIVA _RF

U5200_RF

PP5287_RF

C2500_RF

U5302_RF

C2203

Y2200

C0742

C2260

C1561C1560

R1561R1560

C4642

C5201_RF

C5322_RF

C1247

C1227

C1200

C1321

C3620_RF

U_PMU_RF

C3626_RF

C4114_RF

C3737

FL4615

FL3155

C5323_RF

C2081

C2205

PP1102

C2200

C0740

C2114

C2005

C2088

R0720

R2260

C1554

R2200

C2120

PP3033_RF

PP3018_RF

C3603_RF

C3619_RF

R3729

C3745

C3746

R3735

C4656

C4615

FL3146

R2205

C2100

PP1105

C4101_RF

L3908_RF

C3908_RF

C4805_RF

C4613

R5302_RF

C1150

C4510

C5302_RF

R5305_RF

R5314_RF

C3652

C2201

C2121

C2127

R0702

C3920_RF

L4802_RF

C3732

C3735

C3795

FL4613

C1244

R3650

C3612

R5301_RF

C2012

C0612

PP1104

C2101

R4510

C1547

C3213_RF

C3227_RF

R3509_RF

C3919_RF

U_WTR_RF

C2331

C4653

C4650

PP5290_RF

R5205_RF

PP5291_RF

C5209_RF

F5202_RF

L5206_RF

C5205_RF

L5204_RF

C5203_RF

R5202_RF

C5215_RF

XW3_RF

L5205_RF

R5303_RF

C5308_RF

C5310_RF

C5309_RF

XW1_RF

XW2_RF

C2024

L5301_RF

L5302_RF

C5311_RF

T5301_RF

C5320_RF

C4005

R5310_RF

C2022

C5303_RF

C4004

C4001

C2113

U4000

C4003

C4008 C4002

PP1021

R0901

R0900

C4007

C2015

C2014

C2020

C2019

C2021

C2087

C2086

C2013

R0920

R1202

C2091 C2089

C2016 C2017

C2097

C2095C2092

C2010

R2201

C2003

C2099

C2098

C1243

C1248

C2085

C2009

C0651

C2004

C2002

R0650

R0651

C1122

Y0600

C0712

C0650

C0711

FL0610

R0922

R1002

C2061

C2062

C3024

C3025

R1021

R1020

C3023

C0704

C3020

C3022

C1514

U3020

R3020

R1501

C3021

C1522

C1524

C1540

C1548

C1550

C1505

C1513

C1541

PP5100_RF

C1543

C1542

VR301_RF

C1520

C1521

C1525

C1523

C1534

C1500

C1503

C1508

C3622_RF

PP3032_RF

R2302

C3615_RF

C3625_RF

C3634_RF

Q2301

R2301

C3635_RF

C3636_RF

C3633_RF

C3616_RF

C3101_RF

U3301_RF

R3403_RF

R3404_RF

L3705_RF

R4501_RF

C4501_RF

C4109_RF

L4106_RF

C4502_RF

C4503_RF

R2230

U2GPA_RF

L4501_RF

C4505_RF

C4510_RF

C4508_RF

L4503_RF

C4506_RF

XW4500_RF

L4605_RF

L4504_RF

L4211_RF

C4213_RF

L4210_RF

L4219_RF

C4602_RF

C4601_RF

C4603_RF

ULASM_RF

L4218_RF

L4209_RF

C4211_RF

L4213_RF

L4215_RF

L4207_RF

C4208_RF

L4214_RF

C4206_RF

C4209_RF

C4205_RF

L4206_RF

L4203_RF

L4204_RF

C4803_RF

L4205_RF

L4216_RF

C4207_RF

R2320

FL4602

FL4603

FL4607

R4600

FL4612

C4607

FL4601

FL4605

FL4604

C4636

C4632

FL4632

FL4631

FL4630

C4600

C4630

C3763

C4634

C3702

FL4633

C4637

C4631

C3760

C3700

C4633

C4635

C4696

C4697

DZ4610

DZ4604

Q5301_RF

C5200_RF

C1103

C0620

C2105

C1546

C3225_RF

C3912_RF

L3909_RF

C4807_RF

C2330

C2109

L5201_RF

C1201

C3630_RF

PP5294_RF

R5315_RF

C3611

C3653

FL1280

C1280

C1112

C1115

R0600

C0603

C0600

C2011

C2008

C1155

C1123

L2070

C1245

C2110

R2261

U1500

C1551

C1530

C3835

C3832

R3506_RF

C3501_RF

C3502_RF

C3631_RF

C3608_RF

C3120_RF

R3502_RF

R3504_RF

C3118_RF

C4105_RF

L4103_RF

L4105_RF

C4104_RF

C4110_RF

C4112_RF

C3807_RF

C3811_RF

C3804_RF

C4405_RF

L4401_RF

L4406_RF

C4409_RF

L4405_RF

L4410_RF

L4403_RF

C4407_RF

C2321 C2310

C2311 C2323

Q2300

C2332

C2333

PP5302_RF

C2111

R5316_RF

C1105

C1109

C2096

C2130

C1154

C1131

C2070

R1530

C1531

Y_XO_RF

R3505_RF

C3226_RF

R3503_RF

C3220_RF

C3808_RF

C3814_RF

L4408_RF

U2300

C2306

R2300

C3670

C1110

C2132

C1127

R3304_RF

C3108_RF

C3105_RF

C4106_RF

R4105_RF

C4108_RF

R4101_RF

L4101_RF

R4202_RF

L4202_RF

C4806_RF

C2322

C2304

C2303

C4655

U4040

C3803

C3840

C4500

L4201_RF

C4906_RF

L4908_RF

L4803_RF

C2320

R5206_RF

C5211_RF

F5203_RF

C5212_RF

C4904_RF

C4902_RF

C0709

C0710

C4905_RF

L4905_RF

PP0904

PP0905

R0701

R0905

C2107

R0904

R0721

R0907

R0906

PP5288_RF

U0900

C0900

PP5285_RF

R5200_RF

TP5301_RF

FL3110

C5283_RF

C5284_RF

R4041

C3106

R4040

C4042

C4024

C4040

C4043

R4021

C4026

C3610

C3600

C3665

C3660 C3661

C3602

U3500

C3640

XW3600

C3664

C0814

C2018

C1107

R0952

C1108

C1226

C1106

C1224

C1117

C1111

TP1120

TP1100

C1221

C1129

C0601

C1132

C0602

C1128

C1124

C1222

C1126

C1133

C1223

C2071

C1121

C1240

R0700

C2102

C2106

C1317

C3837

C3842

C3012

C3846

U3800

C3800

FL3804

XW3811

FL3803

XW3810

C3802

C3810

R3810

R3811

C3811

U4500

C4502

C4501

C3125_RF

C3115_RF

C4503

Q4500

C3809_RF

R3801_RF

C3802_RF

R3802_RF

C3810_RF

C3803_RF

C3401_RF

R3407_RF

R4201_RF

FLGPS_RF

FLFBR_RF

UHASM_RF

L4701_RF

L4805_RF

C2300

C2307

C2305

R2311

C2412

R2310

C2411

R2400

C2400

C4654

C4652

C4651

FD0515

TP11 TP10

L4903_RF

C1101

C3860

C4504

C3801_RF

C3815_RF

C3402_RF

C2410

U_VOX_RF

FL3100

FL3104

C3651

C1225

C1100

C1139

C1137

C2103

R3803

C3863

R4500

C4000_RF

C4605_RF

R3408_RF

PP3053_RF

C4702_RF

C4704_RF

L5408_RF

R4901_RF

C3105

C3101

C4025

XW3660

C1116

PP1101

C1156

PP1100

C1120

C1130

C1140

C1506

PP3075_RF

PP4500

L4604_RF

L4602_RF

C4703_RF

C4701_RF

L4703_RF

R4902_RF

C3654

C0802

C1114 C1113

PP1002

C1220

C1242

L4706_RF

L4705_RF

C4903_RF

C3663C3662

C3650

C0815

C0801

C1136

C1141

PP1520

PP1521

C4705_RF

L5407_RF

R5401_RF

L4904_RF

J5003_RF

FL3153

C3550

C3551

C3601

R3550

C3506

R3503

R3502

C1104

R1203

C1202

C1125

R0921

DZ302_RF

C1512 C1529

C1533

R1520

R1521

C1510 C1528

C1516

C1511 C1526

C1507

C1515

R3013_RF

R3829

R3835

C3829

C3830

C3809

C3804

C3407_RF

XW3802

C3801

R3802

XW3801

R3801

C3805

L4521

L4522

PP3056_RF

FLDIP_RF

TP05

R5204_RF

C5207_RF

R5402_RF

C5208_RF

L5410_RF

L5100_RF

C5007_RF

UQPL_RF

C4901_RF

L4907_RF

J5004_RF

FL3154

SH0503

C3603

R3515

C3504

C3505

C3554

C3552

C1323

C1300

C1316

R1205

C1246

R0930

C2112

C1157

C1135

C1138

C1134

C1312

C1302

C1532

CL0501

C1527

SH0504

R0722

R0902

R0903

R3401_RF

R3402_RF

R3406_RF

FD0514

J5001_RF

FD0505

J5002_RF

L4307_RF

C4303_RF

L5001_RF

C5006_RF

TP08TP09

J_UAT_RF J5100_RF

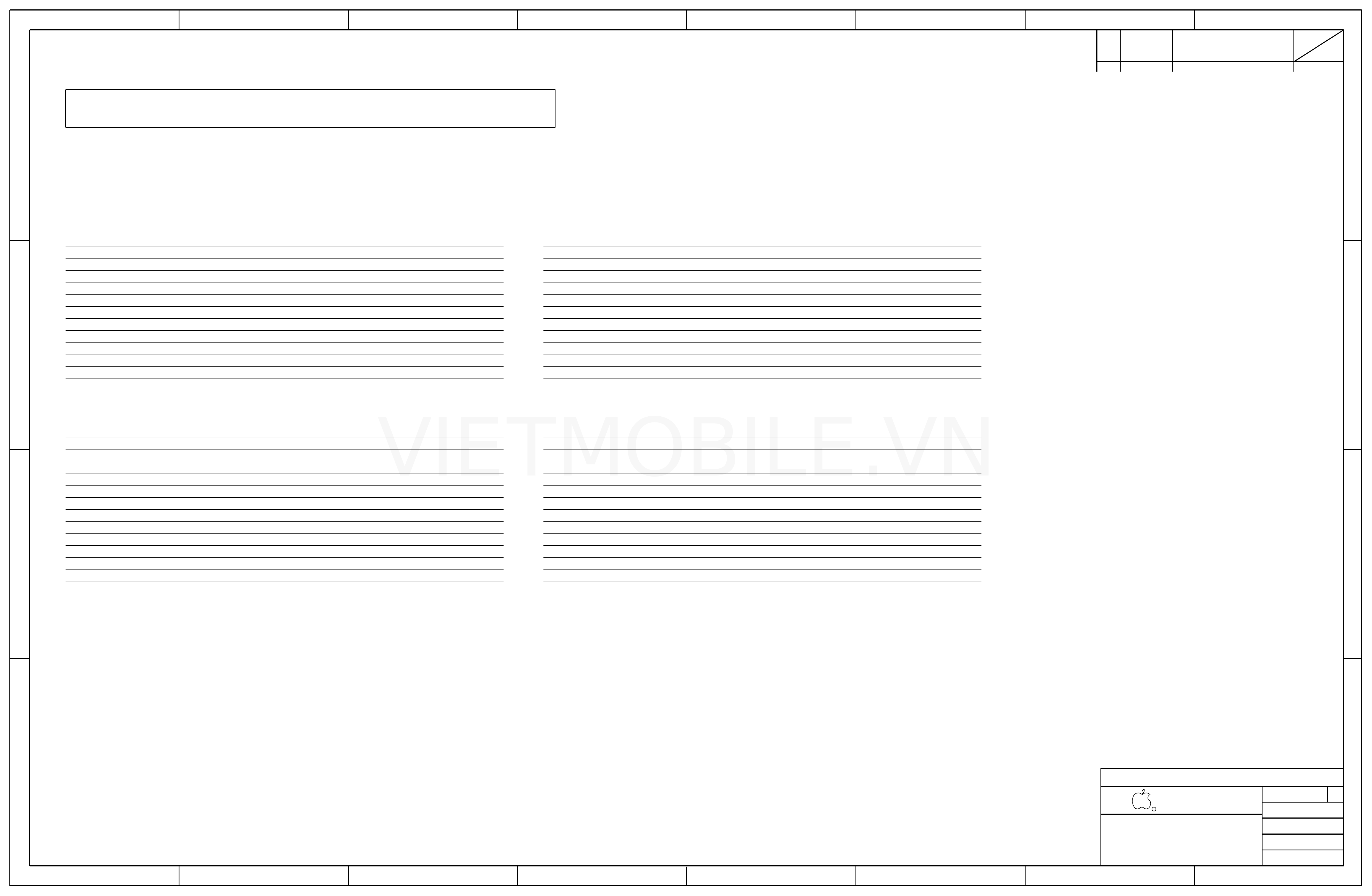

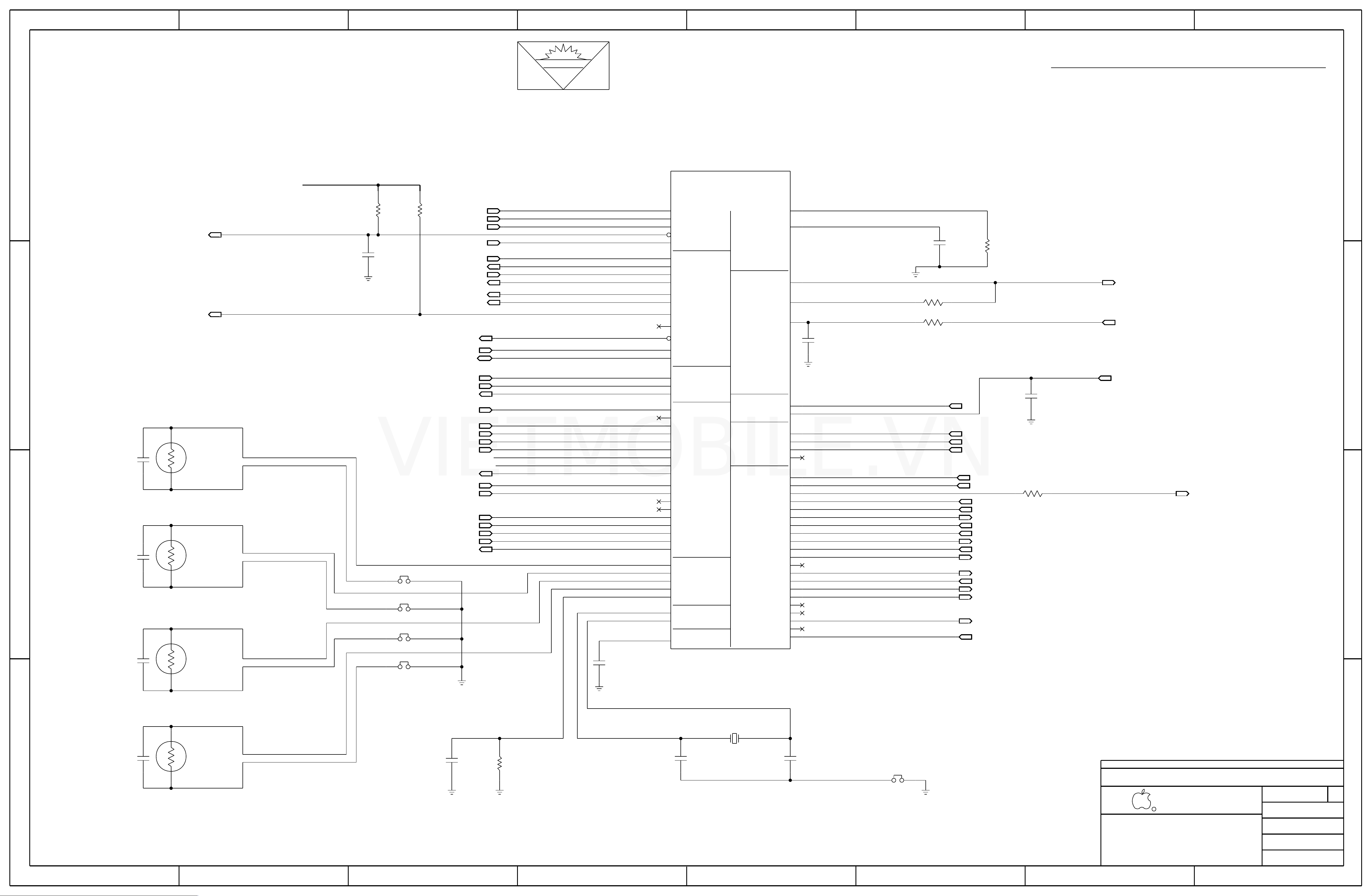

Page 2

8

VIETMOBILE.VN

1. ALL RESISTANCE VALUES ARE IN OHMS, 0.1 WATT +/- 5%.

2. ALL CAPACITANCE VALUES ARE IN MICROFARADS.

3. ALL CRYSTALS & OSCILLATOR VALUES ARE IN HERTZ.

7

N71 MLB - PVT OK2FAB

6 5 4 3

2 1

ECNREV DESCRIPTION OF REVISION

CK

APPD

DATE

2015-07-210004536627A PRODUCTION RELEASED

D

LAST_MODIFICATION=Tue Jul 21 11:39:02 2015

PAGE DATE PAGE DATECONTENTS

1

2

3

4

5

<CSA>

1

3

4

6

7

TABLE OF CONTENTS

SYSTEM:BOM TABLES

SYSTEM:N71 SPECIFIC

SYSTEM:MECHANICAL

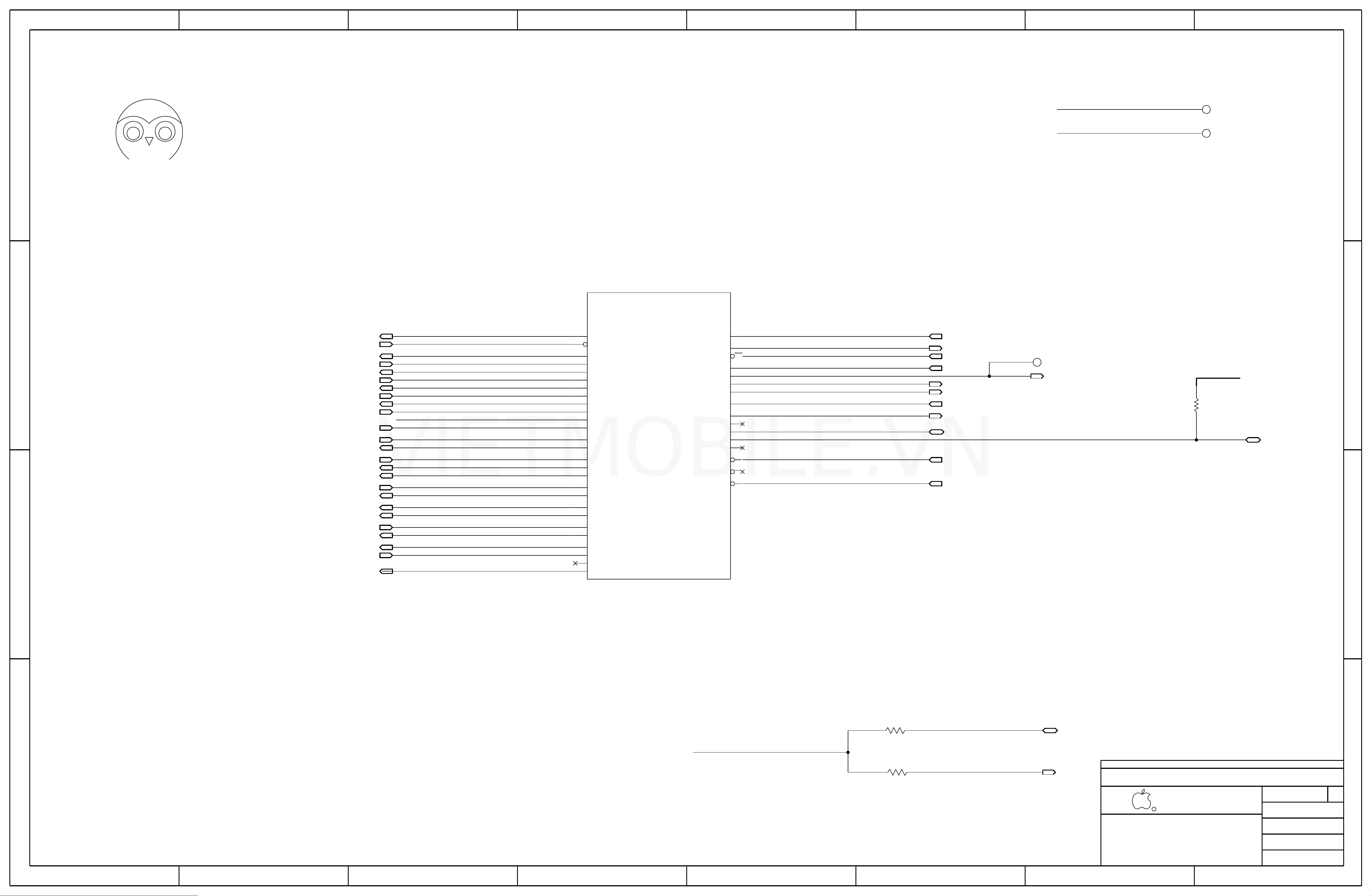

SOC:JTAG,USB,XTAL

31

32

33

34

35

<CSA>

47

49

I/O:DOCK FLEX B2B

I/O:BUTTON FLEX B2B

BASEBAND:RADIO SYMBOL

page1

ELNA & UAT ANT FEED

D

CONTENTS SYNCSYNC

C

7

8

9

10

11

13

14

15

16

17

18

19

8

9

10

11

12

13

1512 SOC:POWER (3/3)

20

21

22

23

24

30 SYSTEM POWER:BATTERY CONN

31

SOC:PCIE6

SOC:CAMERA & DISPLAY

SOC:SERIAL & GPIO

SOC:OWL

SOC:POWER (1/3)

SOC:POWER (2/3)

NAND

SYSTEM POWER:PMU (1/3)

SYSTEM POWER:PMU (2/3)

SYSTEM POWER:PMU (3/3)

SYSTEM POWER:CHARGER

SENSORS:MOTION SENSORS

36

37

38

39

40

41

42

43

44

45

46

47

48

49

FE: ANT CONNECTORS AND UAT TUNER

WLAN LAT 2.4GHZ BAW BPF

DEBUG CONN & TEST POINTS

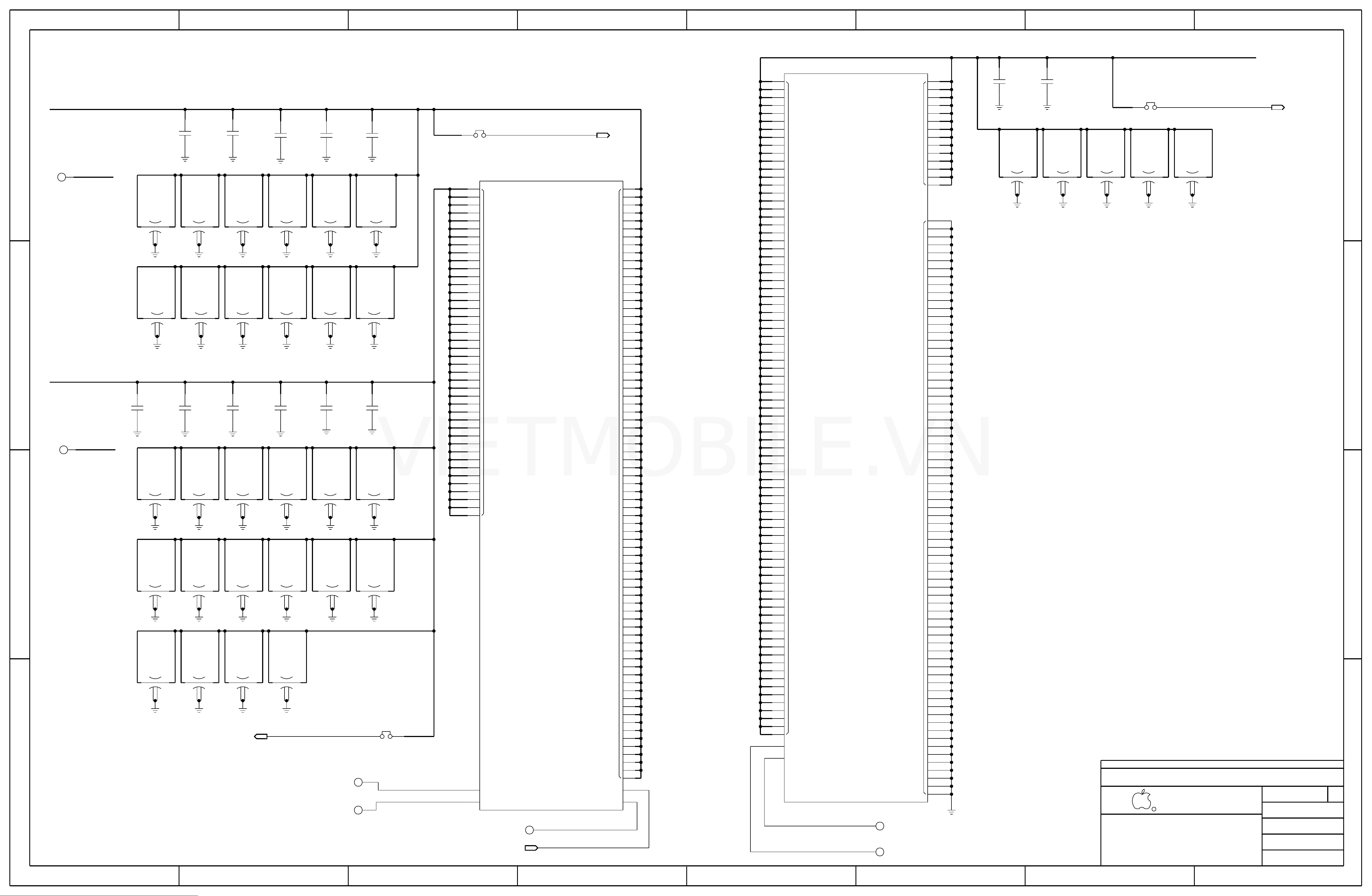

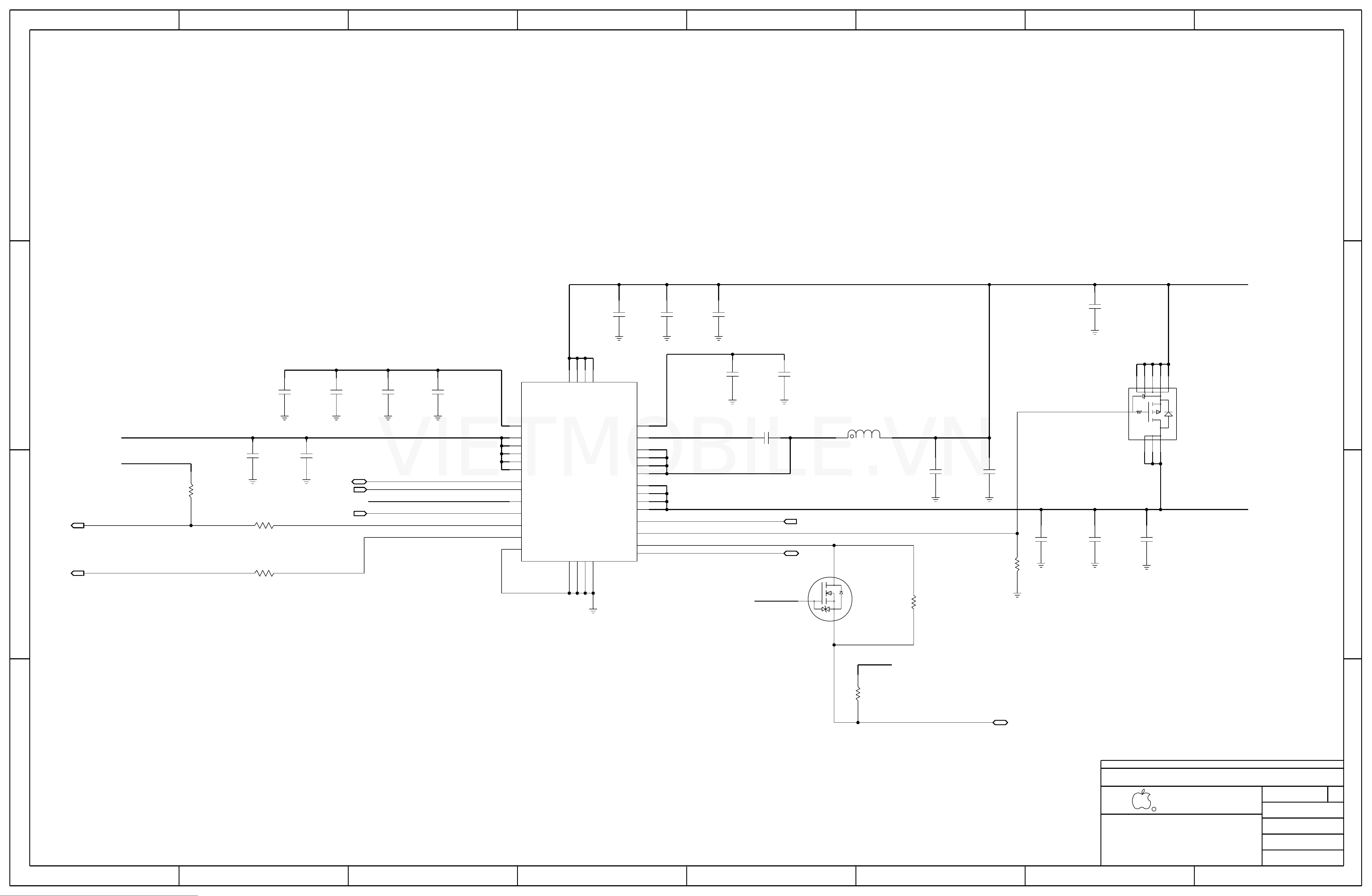

CELLULAR BASEBAND: POWER1

CELLULAR BASEBAND: POWER2

CELLULAR BASEBAND: CONTROL AND INTERFACES

CELLULAR BASEBAND: GPIOS

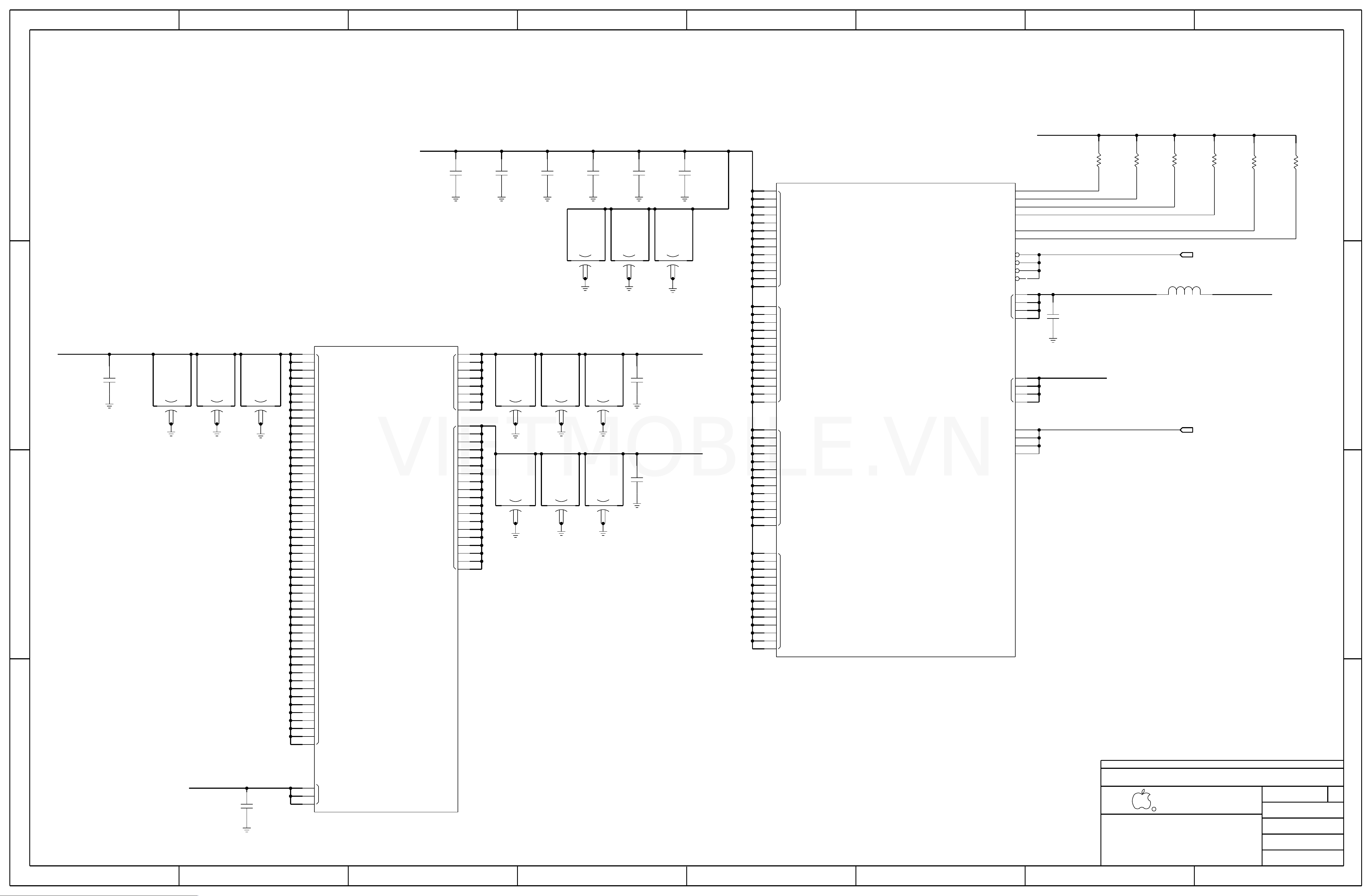

CELLULAR PMU: CONTROL AND CLOCKS

CELLULAR PMU: SWITCHERS AND LDOS

CELLULAR PMU: ET MODULATOR

CELLULAR TRANSCEIVER: POWER

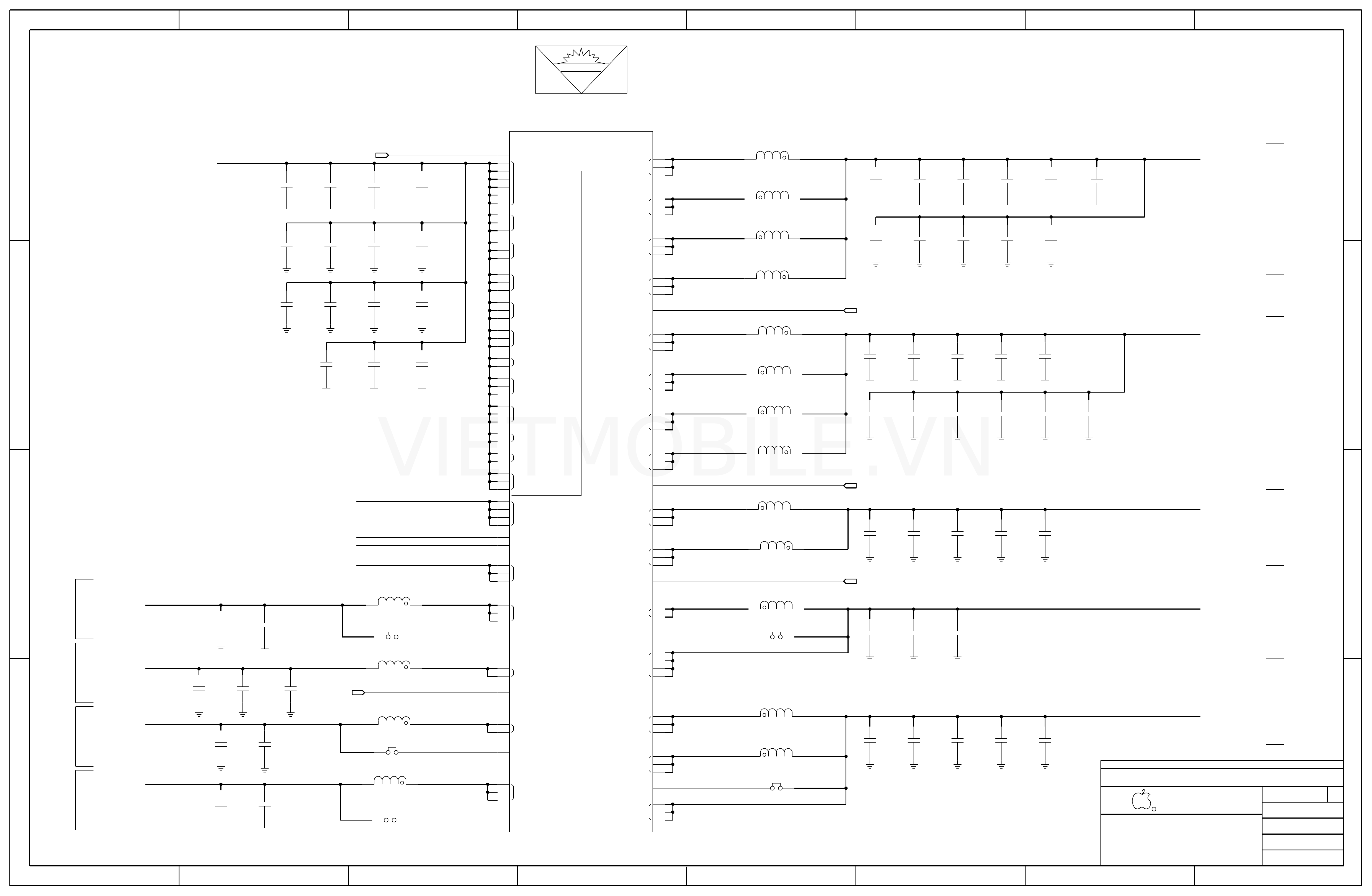

CELLULAR TRANSCEIVER: PRX PORTS

CELLULAR TRANSCEIVER: DRX/GPS PORTS

CELLULAR TRANSCEIVER: TX PORTS

C

B

TABLE

20

21

22

23

24

25

26

27

28

29

30

32

33

35

36

37 AUDIO:CALTRA CODEC (2/2)

38

40

41

42

45

46

CAMERA:FOREHEAD FLEX B2B

CAMERA:REAR CAMERA B2B

CAMERA:STROBE DRIVER

AUDIO:CALTRA CODEC (1/2)

AUDIO:SPEAKER DRIVER

AUDIO:ARC DRIVER

DISPLAY:POWER

TOUCH:ORB & MESA B2B

DISPLAY:KEPLER B2B

I/O:TRISTAR 2

50

51

52

53

54

55

56

57

58

59

CELLULAR FRONT END: LB PAD

CELLULAR FRONT END: MB PAD

CELLULAR FRONT END: HB PAD

CELLULAR FRONT END: 2G PA

CELLULAR FRONT END: LB ASM

CELLULAR FRONT END: MB-HB ASM

CELLULAR FRONT END: DIVERSITY

SIM

WIFI/BT: WIFI/BT MODULE

STOCKHOLM

B

BOM 639-00263 (BETTER,DB30)

BOM 639-00265 (ULTRA,DB30)

BOM 639-00266 (SUPREME,DB30)

SCH 051-1902

BRD 820-5507

MCO 056-01060

A

BOM 639-01056 (BETTER,B30)

BOM 639-01057 (ULTRA,B30)

BOM 639-01058 (SUPREME,B30)

BOM 639-01098 (BETTER,DB30C)

BOM 639-01100 (ULTRA,DB30C)

BOM 639-01099 (SUPREME,DB30C)

BOM 939-01627 (BETTER,DARWIN)

TABLE OF CONTENTS

DRAWING TITLE

SCHEM,SINGLE,BRD,N71

Apple Inc.

R

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

IV ALL RIGHTS RESERVED

051-1902

REVISION

A.0.0

BRANCH

PAGE

1 OF 49

SHEET

1 OF 59

A

SIZEDRAWING NUMBER

D

3

1245678

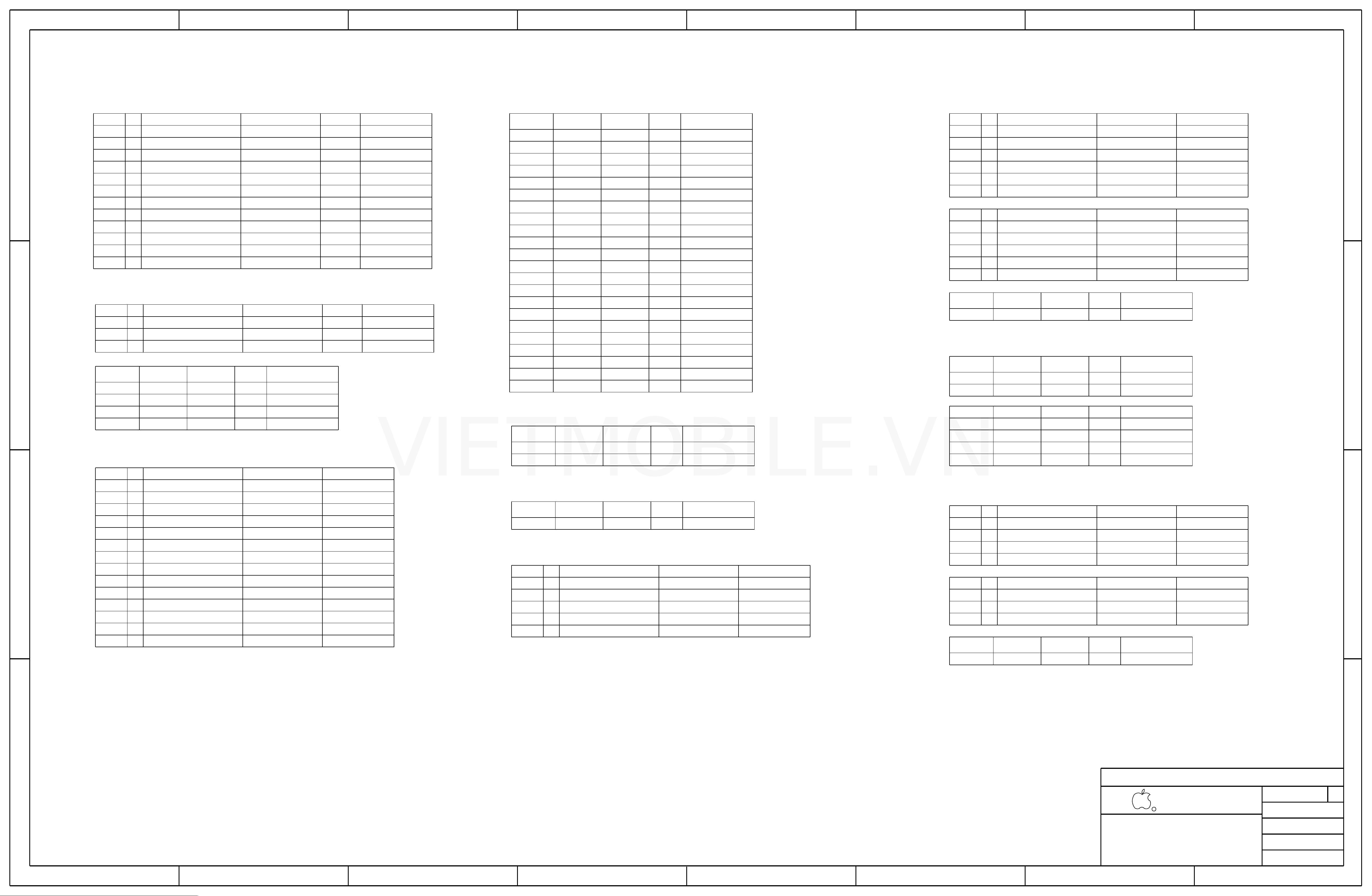

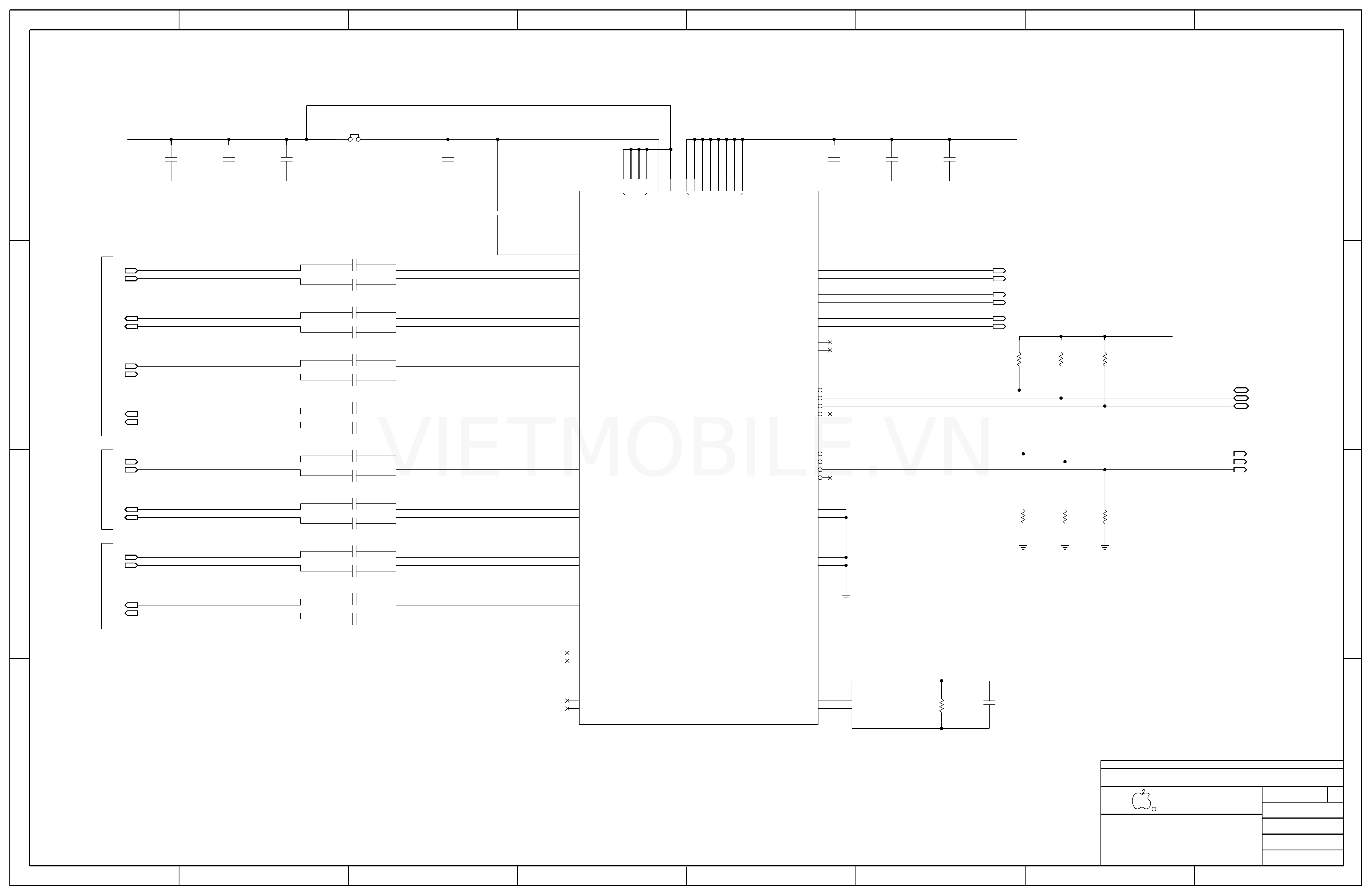

Page 3

345678

VIETMOBILE.VN

2 1

D

C

B

SCHEMATIC & PCB BOM CALLOUTS

REFERENCE DESIGNATOR(S)QTY DESCRIPTIONPART#

SCH1 SCH,SINGLE_BRD,N71051-1902

1 EEEE_G2KM

EEEE CODE FOR 639-00265

825-6838 CRITICAL

EEEE CODE FOR 639-01056

1

EEEE CODE FOR 639-01057825-6838 1 CRITICALEEEE_GKFC

EEEE CODE FOR 639-01058825-6838

825-6838 1 EEEE CODE FOR 639-01098 CRITICAL

EEEE CODE FOR 639-01100 EEEE_GLHR1 CRITICAL825-6838

1

825-6838 EEEE CODE FOR 939-016271

EEEE_G2KLEEEE CODE FOR 639-002661

EEEE_GKF9825-6838 CRITICAL

EEEE_GLHL

EEEE_GLHM825-6838 EEEE CODE FOR 639-01099 CRITICAL

EEEE_GR09 CRITICAL

CRITICAL

CRITICALPCB1?PCBF,SINGLE_BRD,N71820-5507

CRITICAL825-6838 EEEE CODE FOR 639-00263

CRITICALEEEE_G2KN825-6838 1

CRITICALEEEE_GKF81

S3E NAND BOM OPTIONS

REFERENCE DESIGNATOR(S)QTY DESCRIPTIONPART#

NAND,1YNM,16GX8,S3E,64G,T,SLGA70

1 CRITICAL335S00039 U1500

335S00075

335S00079 1 U1500

NAND,1YNM,64GX8,S3E,MLB,64G,H,SLGA70

NAND,1YNM,128GX8,S3E,TLC,128G,H,SLGA70

PART NUMBER

335S00039335S00074 NAND_16G U1500

NAND_64G335S00075335S00078 U1500 HYNIX 64G SLGA70

U1500335S00064 NAND_64G SANDISK 64G SLGA70 1Z335S00075

U15001 NAND_64GCRITICAL

CRITICAL

TABLE_ALT_HEAD

COMMENTS:REF DESBOM OPTIONPART NUMBER ALTERNATE FOR

TABLE_ALT_ITEM

HYNIX 16G SLGA70 C DIE

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

SANDISK 128G SLGA70U1500335S00065 NAND_128G335S00079

CARBON/ACCEL BOM OPTIONS

PART# DESCRIPTIONQTY

IC,ACCEL,3-AXIS,DIG,BMA282,LGA14

117S0202 R30301

138S0831 NOSTUFF1

338S00087 1 INVENSENSE_STANDALONE_CARBONU3010

RES,MF,20 OHM,5%,1/32W,01005

RES,MF,20 OHM,5%,1/32W,01005

RES,MF,20 OHM,5%,1/32W,01005

CAP,CER,X5R,2.2UF,20%,6.3V,0201

CAP,CER,X5R,0.1UF,20%,6.3V,01005

IC,CARBON,MPU-6700-12,LGA16

IC,ACCEL,3-AXIS,DIG,BMA282,LGA14

RES,MF,20 OHM,5%,1/32W,01005

RES,MF,20 OHM,5%,1/32W,01005

CAP,CER,X5R,2.2UF,20%,6.3V,0201

CAP,CER,X5R,0.1UF,20%,6.3V,01005

IC,CARBON 1.1,MPU-6800-00,LGA16

R30321117S0202

C3031

C3032132S0316 NOSTUFF1

U3010 INVENSENSE_CARBON1338S00017

U3030 INVENSENSE_CARBON1338S1163

BOM OPTIONREFERENCE DESIGNATOR(S)

NOSTUFF338S1163 U30301

NOSTUFF

NOSTUFFR3031117S0202 1

NOSTUFF

INVENSENSE_CARBON1 R3030117S0202

INVENSENSE_CARBON1117S0202 R3031RES,MF,20 OHM,5%,1/32W,01005

INVENSENSE_CARBON1117S0202 R3032

INVENSENSE_CARBON1 C3031138S0831

INVENSENSE_CARBON1 C3032132S0316

BOM OPTIONCRITICAL

?

EEEE_16G_DB30

EEEE_64G_DB30

EEEE_128G_DB30

EEEE_16G_B30

EEEE_64G_B30

EEEE_128G_B30

EEEE_16G_DB30C

EEEE_64G_DB30C

EEEE_128G_DB30C

EEEE_16G_DARWIN

BOM OPTIONCRITICAL

NAND_16G

NAND_128G

TABLE_5_HEAD

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_HEAD

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_HEAD

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

ALTERNATE BOM OPTIONS

PART NUMBER

C0610 TY,2.2UF,0201138S00032 ALTERNATE138S0831

ALTERNATE C0610138S00049 KYOCERA,2.2UF,0201138S0831

ALTERNATE FL3100155S0513155S0660 MURATA,FERR,22-OHM

ALTERNATE138S00003 C2000138S00005

ALTERNATE138S00003 C2000138S00048 KYOCERA,15UF,0402

138S0702 138S0657 ALTERNATE C2111 MURATA,4.3UF,0610

118S0717

377S0168 ALTERNATE

155S00009 ALTERNATE155S00012 L3100

155S00095

132S0400

155S0960 ALTERNATE155S0941

155S0653

155S00068 ALTERNATE FL1280

132S0436 ALTERNATE

138S0986138S00024 ALTERNATE C1107

335S0946

155S0511 FL4600ALTERNATE

ALTERNATE118S0764

ALTERNATE138S0835138S00006 TY,4.3UF,0402C1106

ALTERNATE152S1929 L2060 CYNTEC,1UH,1608152S2052

ALTERNATE155S0581155S00067 FL4200

ALTERNATE138S0706 C3302_RF138S0739

ALTERNATE U0900335S00066

R2250

FL3110155S0453155S0773 ALTERNATE TY,FERR,120-OHM,01005

DZ3150377S0140

C3302_RF138S0945 ALTERNATE138S0739

C1280

FL3151

COMMENTS:REF DESBOM OPTIONPART NUMBER ALTERNATE FOR

TY,15UF,0402

PANASONIC,3.92K-OHM,0201

TDK,VARISTOR,6.8V,100PF,01005

TDK,FERR,240-OHM,0201

MURATA,CHOKE,65-OHM,0605

MURATA,CAP,CER,1UF,20%,10V,X5R,0201

KYOCERA,CAP,CER,1UF,20%,10V,X5R,0201

FERR BD,100 OHM,25%,100MA,2 OHM,01005

TY,4.7UF,0402ALTERNATE138S0652138S0648 C3650

CAP,CER,X5R,0.22UF,20%,6.3v,01005

FEER BD,70 OHM,25%,300MA,0.4 DCR,01005

CAP,CER,3-TERM,7.5UF,20%,4V,0402

IC,EEPROM,16KX8,1.8V,I2C,WLCSP4

FERR BD,33 OHM,25%,750MA,0.09DCR,0201

POWER INDUCTOR ALTERNATES

PART NUMBER

152S00120 L2070ALTERNATE152S00077

ALTERNATE152S00118 TAIYO 2016 1.2UHL3700152S00075

COMMENTS:REF DESBOM OPTIONPART NUMBER ALTERNATE FOR

TAIYO 2016 1.0UH 0.65MM

ACTIVE DIODE ALTERNATE

PART NUMBER

376S00106 376S00047 ALTERNATE Q2300 DIODES INC. ACT DIODE

SHIELD PART NUMBERS

PART# DESCRIPTIONQTY

1 COMMON806-02895

SHIELD,EMI,UPPER FRONT,WTOP,N71

SHIELD,EMI,LOWER FRONT,CLOSED,NOMU,N71 SH05011806-04588 COMMON

SHIELD,EMI,SA,OPEN,N711 SH0502 COMMON806-03994

1 SH0503806-02897

SHIELD,EMI,UPPER BACK,WTOP,N71

806-02898 1 SH0504

SHIELD,EMI,LOWER BACK,WTOP,N71

COMMENTS:REF DESBOM OPTIONPART NUMBER ALTERNATE FOR

SH0500

TABLE_ALT_HEAD

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_HEAD

TABLE_ALT_ITEM

TABLE_ALT_HEAD

TABLE_ALT_ITEM

BOM OPTIONREFERENCE DESIGNATOR(S)

COMMON

COMMON

NOT ALL REFERENCE DESIGNATORS LISTED.

USED ~116 TIMES IN DESIGN.

USED ~116 TIMES IN DESIGN.

USED ~7 TIMES IN DESIGN.

USED ~63 TIMES IN DESIGN.

USED ~63 TIMES IN DESIGN.

USED ~3 TIMES IN DESIGN.

USED ~19 TIMES IN DESIGN.

USED ~61 TIMES IN DESIGN.

USED ~9 TIMES IN DESIGN.

USED ~8 TIMES IN DESIGN.

USED ~11 TIMES IN DESIGN.

USED ~17 TIMES IN DESIGN.

USED ~17 TIMES IN DESIGN.

USED ~12 TIMES IN DESIGN.

USED ~2 TIMES IN DESIGN.

USED ~9 TIMES IN DESIGN.

USED ~7 TIMES IN DESIGN.

USED ~4 TIMES IN DESIGN.

TABLE_5_HEAD

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

SOC/PMU SUB BOMS

PART# DESCRIPTIONQTY

338S00120

118S0631

339S00112

SUBBOM,SINGLE,BRD,MAUI,N71

IC,PMU,ANTIGUA,A0,D2255A1,OTP-AL,WLCSP380

1 U2000 MAUI

RES,MF,100 OHM,1%,1/32W,01005

1

CAP,CER,NP0/C0G,100PF,5%,16V,01005

1

PROD FUSED, H DRAM

RES,MF,0 OHM,1/32W,01005

SUBBOM_SOC1685-00069 COMMON

R0730 MAUI

U0600 MAUI1

R0651

PART# DESCRIPTIONQTY

IC,PMU,ANTIGUA,D2255A1,OTP-ZL,WLCSP380

1 MALTA338S00122

RES,MF,3.01KOHM,1%,1/32W,01005

131S0307 1

118S00025 R0651

CAP,CER,NP0/C0G,100PF,5%,16V,01005

M DEV FUSED, M DRAM

RES,MF,330 OHM,1%,1/32W,01005

1 MALTA

PART NUMBER

685-00069 ALTERNATE685-00070

SUBBOM_SOC SUBBOM,SINGLE,BRD,MALTA,N71

U2000

U06001339S00124

COMMENTS:REF DESBOM OPTIONPART NUMBER ALTERNATE FOR

SOC ALTERNATES

PART NUMBER

339S00112

339S00124

339S00124339S00126

339S00124339S00127

339S00124 M PROD FUSED, S DRAM, SCKMALTA U0600339S00129

U0600 PROD FUSED, M DRAM339S00113 MAUI339S00112

U0600 PROD FUSED, S DRAM339S00114 MAUI

MALTA U0600339S00125

MALTA U0600

MALTA U0600

MALTA339S00124339S00128 U0600

COMMENTS:REF DESBOM OPTIONPART NUMBER ALTERNATE FOR

M PROD FUSED, H DRAM, ATK

M PROD FUSED, S DRAM, ATK

M PROD FUSED, M DRAM, SCK

M PROD FUSED, H DRAM, SCK

INDUCTOR SUB BOMS

PART# DESCRIPTIONQTY

1685-00081

SUBBOM,SINGLE,BRD,CYNTEC,N71

152S00081

PART# DESCRIPTIONQTY

6

5

IND,PWR,SHLD,1.0UH,3.6A,0.060 OHM,2016 L2040,L2050,L2300,L3300,L4021

6

IND,PWR,SHLD,0.47UH,3.8A,0.048 OHM,2012 L2001,L2003,L2011,L2013,L2021,L2041

5

IND,PWR,SHLD,1.0UH,3.6A,0.060 OHM,2016 L2040,L2050,L2300,L3300,L4021

6

IND,PWR,SHLD,0.47UH,3.8A,0.048 OHM,2012

PART NUMBER

ALTERNATE685-00081685-00080 SUBBOM_IND SUBBOM,SINGLE,BRD,TAIYO,N71

L2000,L2002,L2010,L2012,L2020,L2030IND,PWR,SHLD,1.0UH,3.6A,0.060 OHM,2016

L2000,L2002,L2010,L2012,L2020,L2030 TAIYO152S00117 IND,PWR,SHLD,1.0UH,3.6A,0.060 OHM,20166

L2001,L2003,L2011,L2013,L2021,L2041

COMMENTS:REF DESBOM OPTIONPART NUMBER ALTERNATE FOR

BOM OPTIONREFERENCE DESIGNATOR(S)

MAUI131S0307 C0730

MAUI1117S0161

BOM OPTIONREFERENCE DESIGNATOR(S)

MALTA118S00009 1 R0730

NOSTUFFC0730

MALTA

TABLE_ALT_HEAD

TABLE_ALT_ITEM

TABLE_ALT_HEAD

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEMTABLE_ALT_ITEM

TABLE_ALT_ITEM

BOM OPTIONREFERENCE DESIGNATOR(S)

COMMONSUBBOM_IND

CYNTEC152S00074

CYNTEC152S00074

CYNTEC

BOM OPTIONREFERENCE DESIGNATOR(S)

TAIYO152S00117

TAIYO152S00121

TABLE_ALT_HEAD

TABLE_ALT_ITEM

TABLE_5_HEAD

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_HEAD

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_HEAD

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_HEAD

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

D

C

B

A

8 7 5 4 2 1

A

PAGE TITLE

SYSTEM:BOM TABLES

DRAWING NUMBER SIZE

Apple Inc.

R

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

IV ALL RIGHTS RESERVED

051-1902

REVISION

A.0.0

BRANCH

PAGE

3 OF 49

SHEET

2 OF 59

D

36

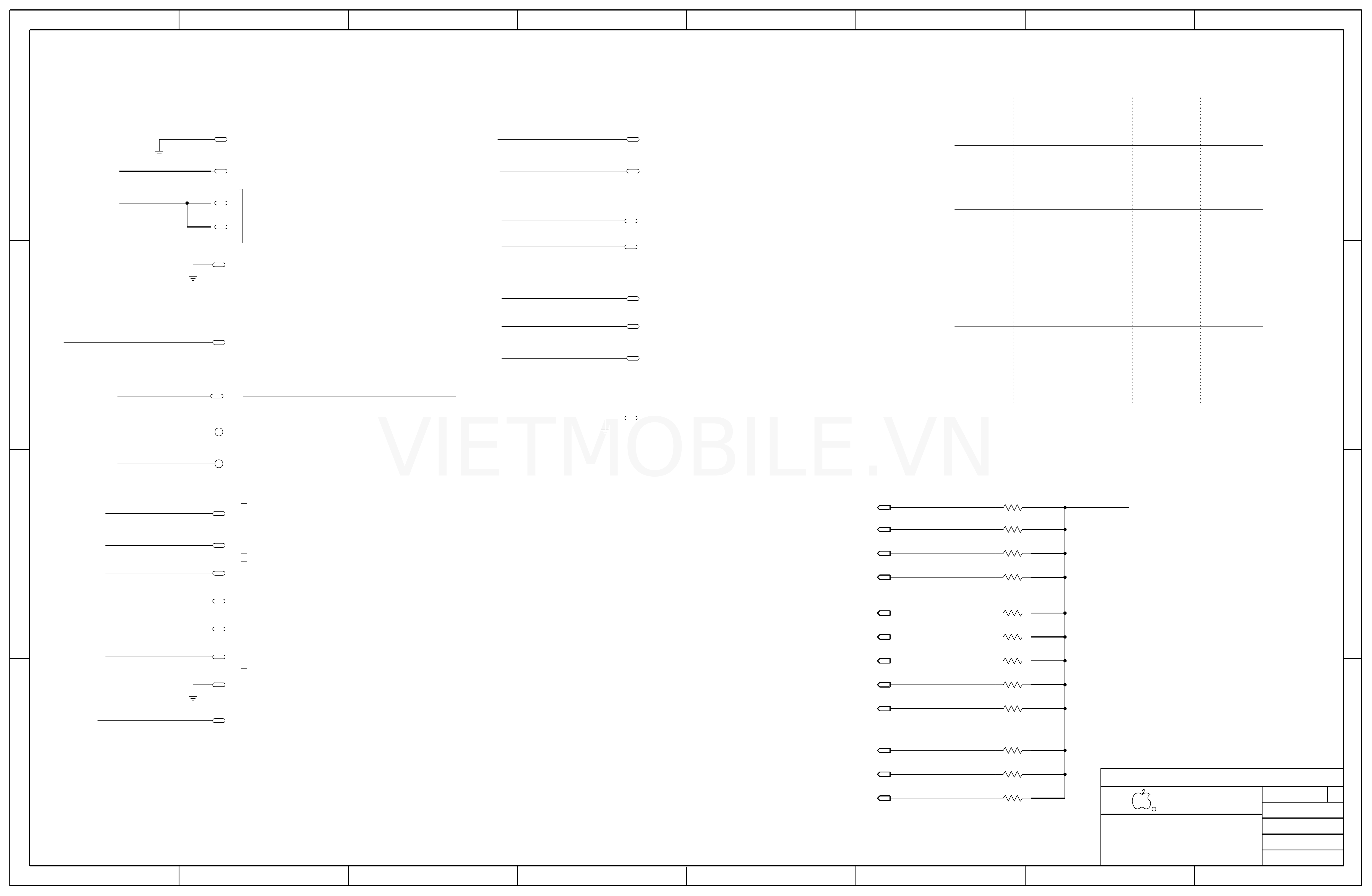

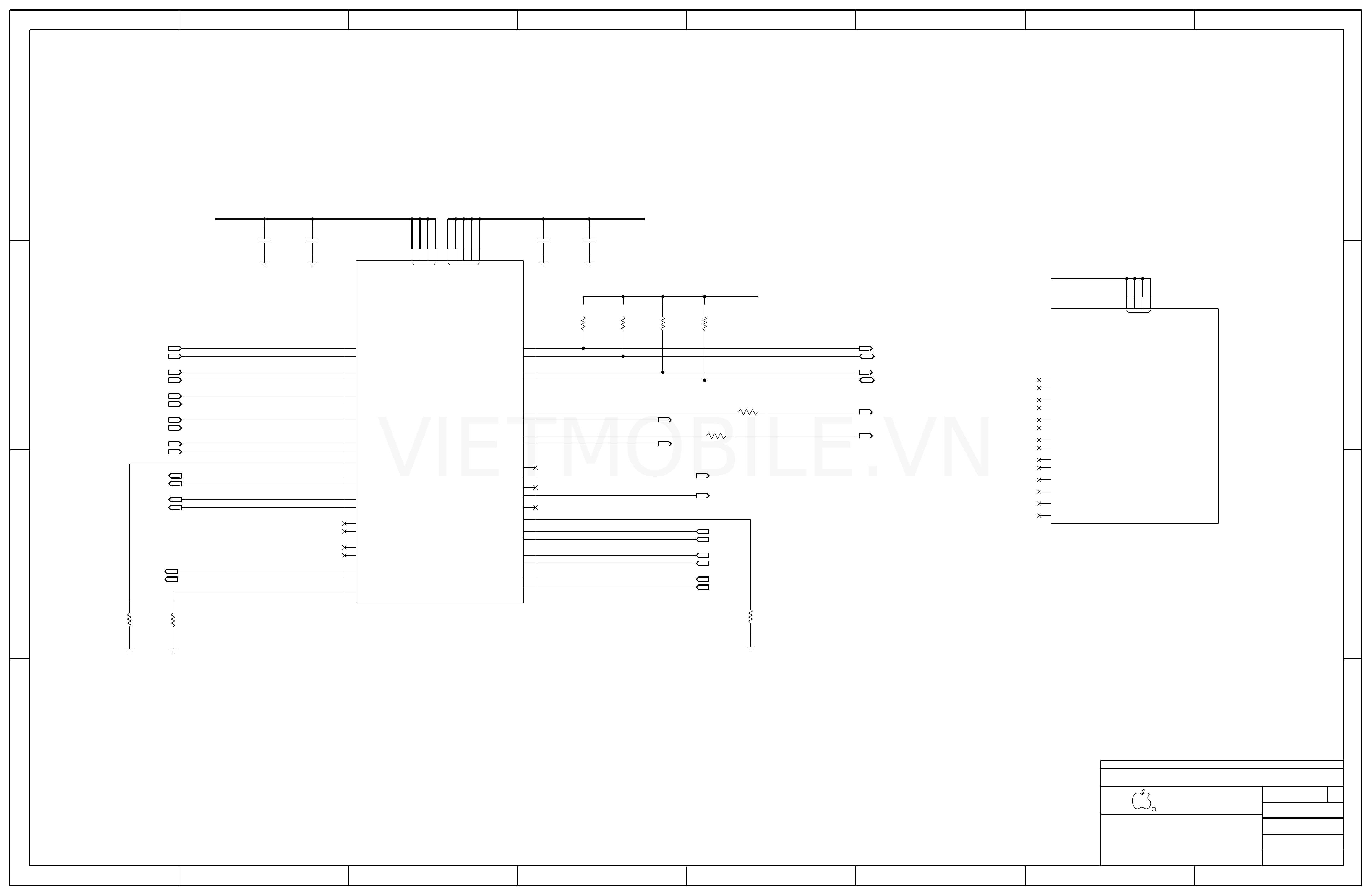

Page 4

345678

VIETMOBILE.VN

2 1

D

TESTPOINTS

POWER

VOLTAGE=0V

31 30 17

18 17

PP5V0_USB

PP_BATT_VCC

TP00

1

TP-P6

ROOM=TEST

TP01

1

TP-P6

ROOM=TEST

TP02

1

TP-P6

ROOM=TEST

TP03

1

TP-P6

ROOM=TEST

TP05

1

TP-P55

ROOM=TEST

N71 I2C DEVICE MAP

I2C BUS

I2C0

AMUX

TP16

PMU_AMUX_AY

A

A

POWER GROUND

VBUS

16

PMU_AMUX_BY

16

1

TP-P55

ROOM=TEST

TP17

1

TP-P55

ROOM=TEST

A

I2C1

A

MOJAVE

A

VBATT

A

A

28 27

28 27

MESA_TO_BOOST_EN

PP16V5_MESA

TP18

1

TP-P55

ROOM=TEST

TP19

1

TP-P55

ROOM=TEST

LCM

A

A

I2C2

OWL

ISP I2C0

DEVICE

ANTIGUA PMU

CHESTNUT

ARC DRIVER 1000001X 0X41 0X82

SPEAKER AMP 1000000X 0X40

TRISTAR 0X1A 0X340011010X

ALS 0101001X

DISP EEPROM

UNUSED N/A N/A N/A

REAR CAM

BINARY

1110100X

0100111X

1100010X 0X62 0XC4MUON

1110101X

1010001X

7-BIT HEX

0X74

0X27 0X4E

0X75TIGRIS

0X29 0X52

0X51 0XA2

TBD TBDTBD

8-BIT HEX

0XE8

D

0XEA

0X80

C

33 16 9 5

21 20 17 14 13 12 9 8 7 6 5 3

PMU_TO_SYSTEM_COLD_RESET_L

FORCE_DFU

33 8

33 29

PP1V8

DFU_STATUS

33 8

RESET

TP06

1

TP-P55

ROOM=TEST

DFU

TP07

1

TP-P55

ROOM=TEST

PP07

P4MM-NSM

SM

1

PP

ROOM=TEST

PP08

P4MM-NSM

SM

1

PP

ROOM=TEST

TP20

PP_LCM_BL_CAT1_CONN

29

PP_LCM_BL_CAT2_CONN

29

A

A

SOC & BB RESET

FORCE DFU PROCEDURE:

PP_LCM_BL_ANODE_CONN

29

SUPER SCREW

1

TP-P55

ROOM=TEST

TP21

1

TP-P55

ROOM=TEST

TP22

1

TP-P55

ROOM=TEST

A

ISP I2C1 FRONT CAM 0X100010000X 0X20

A

TOUCH I2C

A

SEP I2C SEP EEPROM 1010001X 0x51 0xA2

MESON 1000000X 0x40 0x80

MAMBA

0X631100011XLED DRIVER

0x60 0xC01100000X

0x581011000XDOPPLER

0XC6

C

0xB0

1. FROM OFF MODE SHORT TP07 TO PP07

2. PLUG IN E75 CABLE TO FORCE DFU

TP23

1

TP-P80

ROOM=TEST

A

BOOTSTRAPPING:BOARD REV

BOARD ID

BOOT CONFIG

B

31 30

31 30

31 30

31 30

31 30

31 30

31 30

TRISTAR_DP1_CONN_P

TRISTAR_DP1_CONN_N

TRISTAR_DP2_CONN_P

TRISTAR_DP2_CONN_N

PP_TRISTAR_ACC1

PP_TRISTAR_ACC2

TRISTAR_CON_DETECT_L

E75

TP08

1

TP-P55

ROOM=TEST

TP09

1

TP-P55

ROOM=TEST

TP10

1

TP-P55

ROOM=TEST

TP11

1

TP-P55

ROOM=TEST

TP12

1

TP-P55

ROOM=TEST

TP13

1

TP-P55

ROOM=TEST

TP14

1

TP-P55

ROOM=TEST

TP15

1

TP-P55

ROOM=TEST

8

OUT

A

TRISTAR USB

A

A

8

OUT

8

OUT

8

OUT

BOARD_REV3

BOARD_REV2

BOARD_REV1

BOARD_REV0

R0400

NOSTUFF

R0401

01005

NOSTUFF

R0402

01005

R0403

01005 MF

TRISTAR DEBUG UART

A

8

OUT

A

8

OUT

BOARD_ID4

BOARD_ID3

TRISTAR ACCESSORY ID

A

A

A

ACCESSORY POWER

8

OUT

8

OUT

8

OUT

BOARD_ID2

BOARD_ID1

BOARD_ID0

NOSTUFF

R0404

01005

NOSTUFF

R0405

010055%MF

R0406

NOSTUFF

R0407

010055%MF 1/32W

NOSTUFF

R0408

01005 MF

ROOM=SOC

1 2

MF01005 1/32W

5%

ROOM=SOC

1 2

MF

5%

ROOM=SOC

1 2

MF

5%

ROOM=SOC

1 2

5%

ROOM=SOC

MF

5%

ROOM=SOC

1 2

ROOM=SOC

1 2

MF

5%

ROOM=SOC

1 2

ROOM=SOC

1 2

5%

1.00K

1.00K

1/32W

1.00K

1/32W

1.00K

1/32W

1.00K

21

1/32W

1.00K

1/32W

1.00K

1/32W01005

1.00K

1.00K

1/32W

PP1V8

SELECTED -->

SELECTED -->

SELECTED -->

33 29

21 20 17 14 13 12 9 8 7 6 5 3

B

BOARD_REV[3:0]

FLOAT=LOW, PULLUP=HIGH

1111 PROTO1

1110 PROTO2

1101 EVT

1100 EVT DOE 3 (MAMBA LDO)

1011 CARRIER

1010 CARRIER 2 (I2C0 SCL)

1001 DVT

BOARD_ID[4:0]

FLOAT=LOW, PULLUP=HIGH

00100 N71 MLB

00101 N71 DEV

00110 N66 MLB

BOOT_CONFIG[2:0]

FLOAT=LOW, PULLUP=HIGH

000 SPI0

001 SPI0 TEST MODE

010 NVME0 x2 MODE

011 NVME0 x2 TEST MODE

100 NVME0 x1 MODE

101 NVME0 x1 TEST MODE

110 SLOW SPI0 TEST MODE

111 FAST SPI0 TEST MODE

A

8 7 5 4 2 1

NOSTUFF

8

OUT

8

OUT

8

OUT

BOOT_CONFIG2

BOOT_CONFIG1

BOOT_CONFIG0

RESISTOR STUFF = HIGH '1'

RESISTOR NOSTUFF = LOW '0'

R0409

01005 MF

R0410

01005

NOSTUFF

R0411

01005

ROOM=SOC

1 2

5%

ROOM=SOC

1 2

MF

5%

ROOM=SOC

1 2

MF 1/32W

5%

1.00K

1/32W

1.00K

1/32W

1.00K

PAGE TITLE

SYSTEM:N71 SPECIFIC

Apple Inc.

R

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

IV ALL RIGHTS RESERVED

DRAWING NUMBER SIZE

051-1902

REVISION

D

A.0.0

BRANCH

PAGE

4 OF 49

SHEET

3 OF 59

A

36

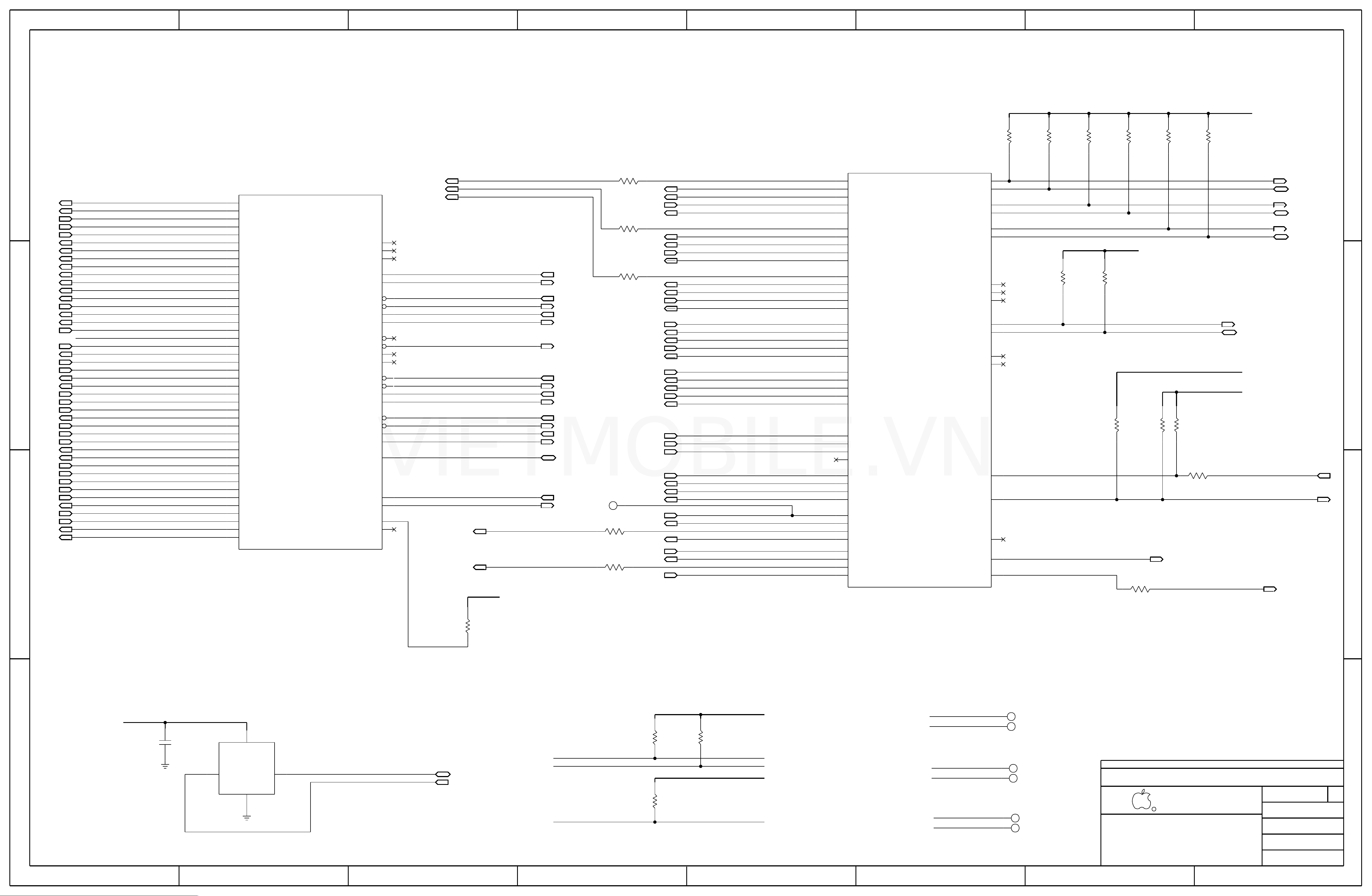

Page 5

PENINSULA STANDOFFS

VIETMOBILE.VN

345678

2 1

D

BS0506

STDOFF-2.2OD0.25H-0.50-1.70

ROOM=ASSEMBLY

1

860-7846

1

806-02971

50_AP_WIFI_5G_CONN_ANT

NORTH_AC_GND_SCREW

BS0508

2.7X1.94X0.25

RING-TH1

ROOM=ASSEMBLY

SHIM WASHER

BS0507

STDOFF-2.6OD0.5H-0.5-1.7-TH

ROOM=ASSEMBLY

860-8396

50_AP_UAT_FEED

1

33

4

33

TOP-SIDE

STOCKHOLM FEED

BS0505

STDOFF-2.56OD1.4ID.99H-SM

860-00109

AP_TO_STOCKHOLM_ANT

33

860-00096

BOTTOM-SIDE

FIDUCIALS

FD0501

ROOM=ASSEMBLY

1

1

BS0503

STDOFF-2.6OD0.81H-TH

ROOM=ASSEMBLY

FID

0P5SM1P0SQ-NSP

1

ROOM=ASSEMBLY

FD0502

FID

0P5SM1P0SQ-NSP

1

ROOM=ASSEMBLY

FD0503

FID

0P5SM1P0SQ-NSP

1

ROOM=ASSEMBLY

FD0505

FID

0P5SM1P0SQ-NSP

1

D

C

STDOFF-2.85OD1.4ID-0.84H

SOUTH DC CURRENT BLOCKING CAPS

SOUTH_AC_GND_SCREW

1

C0540

220PF

10%

10V

2

X7R-CERM

01005

ROOM=ASSEMBLY

1

C0541

100PF

5%

16V

2

NP0-C0G

01005

ROOM=ASSEMBLY

1

C0542

56PF

5%

16V

2

NP0-C0G

01005

ROOM=ASSEMBLY

1

C0543

4.7PF

+/-0.1PF

16V

2

NP0-C0G

01005

ROOM=ASSEMBLY

BS0501

ROOM=ASSEMBLY

32 4

1

PLATED SLOTTED THRU-HOLE

CL0502

TH-NSP

1

SL-1.20X0.40-1.50X0.70-NSP

1

860-00111860-00111

UPPER SHIELD

OMIT_TABLE

1

SH0500

SM

BS0502

STDOFF-2.85OD1.4ID-0.84H

ROOM=ASSEMBLY

UPPER SHIELD

OMIT_TABLE

1

SH0503

SM

SHLD-EMI-UPPER-BACK-N61

ROOM=ASSEMBLY

ROOM=ASSEMBLY

FD0510

FID

0P5SQ-SMP3SQ-NSP

1

ROOM=ASSEMBLY

FD0511

FID

0P5SQ-SMP3SQ-NSP

1

ROOM=ASSEMBLY

FD0512

FID

0P5SQ-SMP3SQ-NSP

1

ROOM=ASSEMBLY

FD0514

FID

0P5SQ-SMP3SQ-NSP

1

ROOM=ASSEMBLY

FD0515

FID

0P5SQ-SMP3SQ-NSP

1

ROOM=ASSEMBLY

C

B

NORTH DC CURRENT BLOCKING CAPS

NORTH_AC_GND_SCREW

1

C0550

220PF

10%

10V

2

X7R-CERM

01005

ROOM=ASSEMBLY

1

C0551

100PF

5%

16V

2

NP0-C0G

01005

ROOM=ASSEMBLY

1

C0552

220PF

10%

10V

2

X7R-CERM

01005

ROOM=ASSEMBLY

1

C0553

100PF

5%

16V

2

NP0-C0G

01005

ROOM=ASSEMBLY

SHLD-EMI-UPPER-FRONT-N61

ROOM=ASSEMBLY

FD0504

FID

0P5SM1P0SQ-NSP

1

ROOM=ASSEMBLY

4

FD0513

FID

0P5SQ-SMP3SQ-NSP

1

ROOM=ASSEMBLY

B

DUAL RF COAX CLIP

CLIP-RETENTION-COAX-DOUBLE

1

CL0501

SM

ROOM=ASSEMBLY

806-01802

32 4

SOUTH_AC_GND_SCREW

LOWER SHIELD

OMIT_TABLE

1

SH0501

SM

SHLD-EMI-LOWER-FRONT-N61

ROOM=ASSEMBLY

SA SHIELD

OMIT_TABLE

A

1

SH0502

SM

SHLD-EMI-SA-N71

ROOM=ASSEMBLY

SOUTH TUBE STANDOFF

BS0500

STDOFF-2.70OD1.84ID-0.88H-TH

1

TODO:UPDATE REF DES

860-7862

ROOM=ASSEMBLY

LOWER SHIELD

OMIT_TABLE

1

SH0504

SM

SHLD-EMI-LOWER-BACK-N61

ROOM=ASSEMBLY

PAGE TITLE

SYSTEM:MECHANICAL

Apple Inc.

R

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

IV ALL RIGHTS RESERVED

DRAWING NUMBER SIZE

051-1902

REVISION

D

A.0.0

BRANCH

PAGE

5 OF 49

SHEET

4 OF 59

A

8 7 5 4 2 1

36

Page 6

MAUI - USB, JTAG, XTAL

VIETMOBILE.VN

345678

2 1

D

15 7 6

VDD12_PLL_LPDP:1.14-1.26V @2mA MAX

VDD12_PLL_SOC: 1.14-1.26V @12mA MAX

VDD12_PLL_CPU: 1.14-1.26V @2mA MAX

R0600

PP1V2

0.00

1/32W

01005

ROOM=SOC

NOTE:LPDP RECEIVES UNFILTERED 1.2V

AS IT IS UNUSED

0%

MF

21

PP1V2_PLL

VOLTAGE=1.2V

C0600

1

0.1UF

20%

6.3V

2

X5R-CERM

01005

ROOM=SOC

C0601

1

0.1UF

20%

6.3V

2

X5R-CERM

01005

ROOM=SOC

C0602

1

0.01UF

10%

6.3V

2

X5R

01005

ROOM=SOC

C0603

1

0.01UF

10%

6.3V

2

X5R

01005

ROOM=SOC

CKPLUS_WAIVE=PWRTERM2GND

AP21

C15

F22

U20

T19

W19

AF13

AL21

1C0612

0.1UF

20%

2

6.3V

X5R-CERM

01005

ROOM=SOC

AN20

PP1V8_XTAL

VOLTAGE=1.8V

AL34

C0611

1

0.1UF

20%

6.3V

2

X5R-CERM

01005

ROOM=SOC

PP3V3_USB

1

C0620

0.1UF

20%

6.3V

2

X5R-CERM

01005

ROOM=SOC

VDD18_USB: 1.71-1.89V @20mA MAX

VDD18_XTAL:1.62-1.98V @2mA MAX

FL0610

1KOHM-25%-0.2A

21

1

C0610

2.2UF

20%

6.3V

2

X5R-CERM

0201

ROOM=SOC

15

VDD33_USB:3.14-3.46V @5mA MAX

0201

ROOM=SOC

PP1V8

33

D

29 21 20 17 14 13 12 9 8 7 6 3

C

30

30

BI

IN

SWD_DOCK_BI_AP_SWDIO

SWD_DOCK_TO_AP_SWCLK

NC

NC

NC

NC

NC

NC

NC

AN22

AN21

C16

D15

Y32

AC32

AB31

AA32

AB32

AA31

VDD12_UH1_HSIC0

UH1_HSIC0_DATA

UH1_HSIC0_STB

UH2_HSIC1_DATA

UH2_HSIC1_STB

JTAG_SEL

JTAG_TRST*

JTAG_TDO

JTAG_TDI

JTAG_TMS

JTAG_TCK

VDD12_PLL_LPDP

VDD12_UH2_HSIC1

VDD18_USB

VDD12_PLL_CPU

VDD12_PLL_SOC

OMIT_TABLE

CRITICAL

U0600

MAUI-2GB-25NM-DDR-H

FCMSP

SC58980B0B-A040

SYM 1 OF 14

ROOM=SOC

VDD33_USB

VDD18_XTAL

ANALOGMUX_OUT

USB_D_P

USB_D_N

USB_VBUS

USB_ID

AP24

AT20

AT19

AP19

AR19

AP_TO_PMU_AMUX_OUT

USB_AP_DATA_P

USB_AP_DATA_N

USB_VBUS_DETECT

NC

OUT

P3MM-NSM

SM

1

PP

ROOM=SOC

30

BI

30

BI

P3MM-NSM

SM

1

PP

ROOM=SOC

17

IN

C

16

PP0600

PP0601

B

PP0610

30 27 16 9

ROOM=SOC

P3MM-NSM

SM

1

PP

33 16 9 3

16

13

IN

IN

OUT

OUT

PMU_TO_SYSTEM_COLD_RESET_L

PMU_TO_OWL_ACTIVE_READY

AP_TO_PMU_TEST_CLKOUT

AP_TO_NAND_RESET_L

AC31

H33

AR23

AN23

H32

AF6

AL22

AG25

COLD_RESET*

CFSB

TST_CLKOUT

S3E_RESET*

HOLD_RESET

TESTMODE

FUSE1_FSRC

FUSE2_FSRC

USB_REXT

WDOG

XI0

XO0

AP18

Y33

AK35

AL35

USB_REXT

AP_TO_PMU_WDOG_RESET

XTAL_AP_24M_IN

XTAL_AP_24M_OUT

OUT

16

1

R0650

511K

1%

1/32W

MF

01005

2

1

R0640

2

ROOM=SOC

200

1%

1/32W

MF

01005

ROOM=SOC

OMIT_TABLE

R0651

0.00

0%

1/32W

MF

01005

ROOM=SOC

B

CRITICAL

ROOM=SOC

Y0600

1.60X1.20MM-SM

24.000MHZ-30PPM-9.5PF-60OHM

21

SOC_24M_O

1

C0650

12PF

5%

16V

2

CERM

01005

ROOM=SOC

31

42

AP_XTAL_GND

VOLTAGE=0.0V

1

C0651

12PF

5%

16V

2

CERM

01005

ROOM=SOC

XW0650

SHORT-10L-0.1MM-SM

ROOM=SOC

21

A

8 7 5 4 2 1

SYNC_DATE=N/ASYNC_MASTER=N/A

PAGE TITLE

A

SOC:JTAG,USB,XTAL

DRAWING NUMBER SIZE

Apple Inc.

R

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

IV ALL RIGHTS RESERVED

051-1902

REVISION

A.0.0

BRANCH

PAGE

SHEET

6 OF 49

5 OF 59

D

36

Page 7

D

VIETMOBILE.VN

MAUI - PCIE INTERFACES

VDD12_PCIE_REFBUF:1.08-1.26V @50mA MAX

VDD12_PCIE_TXPLL: 1.08-1.32V @10mA MAX

VDD12_PCIE: 1.14-1.26V @115mA MAX

XW0740

SHORT-10L-0.1MM-SM

15 7 5 14 11 7

PP1V2 PP_FIXED

ROOM=SOC

1

C0740

2.2UF

20%

6.3V

2

X5R-CERM

0201

ROOM=SOC

1

C0741

1.0UF

20%

6.3V

2

X5R

0201-1

ROOM=SOC

1

C0742

0.1UF

20%

6.3V

2

X5R-CERM

01005

ROOM=SOC

21

XW TO ISOLATE C0442,3 FROM C0740,1.

PP1V2_XW

VOLTAGE=1.2V

1

C0743

0.1UF

20%

6.3V

2

X5R-CERM

01005

ROOM=SOC

AK25

AK28

AL27

AL24

AL26

AJ26

AJ25

AH28

AJ29

AL23

AJ24

AL29

AJ27

AK27

1

C0752

0.1UF

20%

6.3V

2

X5R-CERM

01005

ROOM=SOC

345678

VDD085_PCIE:0.802-TBDV @TBDmA MAX

1

C0751

1.0UF

20%

6.3V

2

X5R

0201-1

ROOM=SOC

1

C0750

2.2UF

20%

6.3V

2

X5R-CERM

0201

ROOM=SOC

2 1

D

C

13

13

13

13

13

13

13

13

IN

IN

OUT

OUT

IN

IN

OUT

OUT

PCIE_NAND_TO_AP_RXD0_P

PCIE_NAND_TO_AP_RXD0_N

PCIE_AP_TO_NAND_TXD0_P

PCIE_AP_TO_NAND_TXD0_N

PCIE_NAND_TO_AP_RXD1_P

PCIE_NAND_TO_AP_RXD1_N

PCIE_AP_TO_NAND_TXD1_P

PCIE_AP_TO_NAND_TXD1_N

C0701

ROOM=SOC

C0702

ROOM=SOC

ROOM=SOC

ROOM=SOC

C0705

ROOM=SOC

C0706

ROOM=SOC

C0707

ROOM=SOC

C0708

ROOM=SOC

21

20%

6.3V

20%

6.3V

20%

6.3V

20%

6.3V

20%

6.3V

20%

6.3V 01005

20%

6.3V

20%

6.3V

X5R-CERM

01005

21

X5R-CERM

01005

21C0703

X5R-CERM

01005

21C0704

X5R-CERM

01005

21

X5R-CERM

01005

21

X5R-CERM

21

X5R-CERM

01005

21

X5R-CERM

01005

0.1UF

0.1UF

0.1UF

0.1UF

0.1UF

0.1UF

0.1UF

0.1UF

1

C0731

2

PCIE_EXT_C

PCIE_NAND_TO_AP_RXD0_C_P

PCIE_NAND_TO_AP_RXD0_C_N

PCIE_AP_TO_NAND_TXD0_C_P

PCIE_AP_TO_NAND_TXD0_C_N

PCIE_NAND_TO_AP_RXD1_C_P

PCIE_NAND_TO_AP_RXD1_C_N

PCIE_AP_TO_NAND_TXD1_C_P

PCIE_AP_TO_NAND_TXD1_C_N

0.1UF

20%

6.3V

X5R-CERM

01005

ROOM=SOC

AP29

AM30

AN30

AT32

AR32

AM28

AN28

AT31

AR31

PCIE_EXT_C

PCIE_RX0_P

PCIE_RX0_N

PCIE_TX0_P

PCIE_TX0_N

PCIE_RX1_P

PCIE_RX1_N

PCIE_TX1_P

PCIE_TX1_N

VDD12_PCIE

VDD12_PCIE_TXPLL

MAUI-2GB-25NM-DDR-H

VDD085_PCIE

VDD12_PCIE_REFBUF

OMIT_TABLE

CRITICAL

U0600

FCMSP

SC58980B0B-A040

SYM 2 OF 14

ROOM=SOC

PCIE_REF_CLK0_P

PCIE_REF_CLK0_N

PCIE_REF_CLK1_P

PCIE_REF_CLK1_N

PCIE_REF_CLK2_P

PCIE_REF_CLK2_N

PCIE_REF_CLK3_P

PCIE_REF_CLK3_N

PCIE_CLKREQ0*

PCIE_CLKREQ1*

PCIE_CLKREQ2*

PCIE_CLKREQ3*

AN35

AP35

AN34

AP34

AM32

AN32

AM31

AN31

AT11

AP12

AR12

AT12

NC

NC

NC

PCIE_AP_TO_NAND_REFCLK_P

PCIE_AP_TO_NAND_REFCLK_N

PCIE_AP_TO_WLAN_REFCLK_P

PCIE_AP_TO_WLAN_REFCLK_N

PCIE_AP_TO_BB_REFCLK_P

PCIE_AP_TO_BB_REFCLK_N

OUT

OUT

OUT

OUT

OUT

OUT

13

13

33

33

33

33

1

R0720

100K

5%

1/32W

MF

01005

2

ROOM=SOC

BI

BI

BI

29 21 20 17 14 13 12 9 8 7 5 3

13

33

33

1

R0721

100K

5%

1/32W

MF

01005

2

ROOM=SOC

NOSTUFF

1

R0722

100K

5%

1/32W

MF

01005

2

ROOM=SOC

PP1V8

33

PCIE_NAND_TO_AP_CLKREQ_L

PCIE_WLAN_TO_AP_CLKREQ_L

PCIE_BB_BI_AP_CLKREQ_L

NOTE:CLKREQ_L PULL-UP FOR BB IN RADIO_MLB_MIMO SECTION

C

B

33

IN

33

IN

33

OUT

33

OUT

33

IN

33

IN

33

OUT

33

PCIE LINK 2 PCIE LINK 0PCIE LINK 1

OUT

PCIE_WLAN_TO_AP_RXD_P

PCIE_WLAN_TO_AP_RXD_N

PCIE_AP_TO_WLAN_TXD_P

PCIE_AP_TO_WLAN_TXD_N

PCIE_BB_TO_AP_RXD_P

PCIE_BB_TO_AP_RXD_N

PCIE_AP_TO_BB_TXD_P

PCIE_AP_TO_BB_TXD_N

C0709

ROOM=SOC

C0710

ROOM=SOC

C0711

ROOM=SOC

C0712

ROOM=SOC

C0715

ROOM=SOC

C0716

ROOM=SOC

C0717

ROOM=SOC

C0718

ROOM=SOC

20%

6.3V

20%

6.3V

20%

6.3V

20%

6.3V

20%

6.3V

20%

6.3V

20%

6.3V

20%

6.3V

21

0.1UF

X5R-CERM

01005

0.1UF

21

X5R-CERM

01005

21

0.1UF

X5R-CERM

01005

0.1UF

21

X5R-CERM

01005

21

0.1UF

X5R-CERM

01005

0.1UF

21

X5R-CERM

01005

21

0.1UF

X5R-CERM

01005

21

0.1UF

X5R-CERM

01005

PCIE_WLAN_TO_AP_RXD_C_P

PCIE_WLAN_TO_AP_RXD_C_N

PCIE_AP_TO_WLAN_TXD_C_P

PCIE_AP_TO_WLAN_TXD_C_N

PCIE_BB_TO_AP_RXD_C_P

PCIE_BB_TO_AP_RXD_C_N

PCIE_AP_TO_BB_TXD_C_P

PCIE_AP_TO_BB_TXD_C_N

AM27

AN27

AT28

AR28

AM26

AN26

AT26

AR26

PCIE_RX2_P

PCIE_RX2_N

PCIE_TX2_P

PCIE_TX2_N

PCIE_RX3_P

PCIE_RX3_N

PCIE_TX3_P

PCIE_TX3_N

PCIE_PERST0*

PCIE_PERST1*

PCIE_PERST2*

PCIE_PERST3*

PCIE_EXT_REF_CLK_P

PCIE_EXT_REF_CLK_N

PCIE_RX_TX_BYPASS_CLK_P

PCIE_RX_TX_BYPASS_CLK_N

AR10

AT10

AP11

AR11

AR33

AT33

AT29

AR29

NC

1

R0700

100K

5%

1/32W

MF

01005

2

ROOM=SOC

1

R0701

100K

5%

1/32W

MF

01005

2

ROOM=SOC

PCIE_AP_TO_NAND_RESET_L

PCIE_AP_TO_WLAN_RESET_L

PCIE_AP_TO_BB_RESET_L

1

R0702

100K

5%

1/32W

MF

01005

2

ROOM=SOC

OUT

OUT

OUT

13

33

33

B

NC

NC

NC

NC

AM25

AN25

AR24

AT24

PCIE_RX4_P

PCIE_RX4_N

PCIE_TX4_P

PCIE_TX4_N

A

PCIE_RCAL_P

PCIE_RCAL_N

AT30

AR30

PCIE_RCAL_P

PCIE_RCAL_N

OMIT_TABLE

1

R0730

100

1%

1/32W

MF

01005

2

ROOM=SOC

OMIT_TABLE

1

C0730

100PF

5%

16V

2

NP0-C0G

01005

ROOM=SOC

SYNC_MASTER=N/A

PAGE TITLE

SOC:PCIE

Apple Inc.

R

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

IV ALL RIGHTS RESERVED

SYNC_DATE=N/A

DRAWING NUMBER SIZE

051-1902

REVISION

D

A.0.0

BRANCH

PAGE

7 OF 49

SHEET

6 OF 59

A

8 7 5 4 2 1

36

Page 8

MAUI - CAMERA & DISPLAY INTERFACES

VIETMOBILE.VN

345678

2 1

D

C

B

29

29

21

21

21

21

21

21

21

21

21

21

29

29

29

29

OUT

OUT

OUT

OUT

OUT

OUT

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

0.756-0.893V @11mA MAX

1

C0814

0.1UF

20%

6.3V

2

X5R-CERM

01005

ROOM=SOC

MIPI_RCAM_TO_AP_DATA0_CONN_P

MIPI_RCAM_TO_AP_DATA0_CONN_N

MIPI_RCAM_TO_AP_DATA1_CONN_P

MIPI_RCAM_TO_AP_DATA1_CONN_N

MIPI_RCAM_TO_AP_DATA2_CONN_P

MIPI_RCAM_TO_AP_DATA2_CONN_N

MIPI_RCAM_TO_AP_DATA3_CONN_P

MIPI_RCAM_TO_AP_DATA3_CONN_N

MIPI_RCAM_TO_AP_CLK_CONN_P

MIPI_RCAM_TO_AP_CLK_CONN_N

RCAM_REXT

MIPI_AP_TO_LCM_DATA0_P

MIPI_AP_TO_LCM_DATA0_N

MIPI_AP_TO_LCM_DATA1_P

MIPI_AP_TO_LCM_DATA1_N

MIPI_AP_TO_LCM_CLK_P

MIPI_AP_TO_LCM_CLK_N

LCM_REXT

1

C0801

0.1UF

20%

6.3V

2

X5R-CERM

01005

ROOM=SOC

NC

NC

NC

NC

B8

MIPI0C_DATA0_P

A8

MIPI0C_DATA0_N

A9

MIPI0C_DATA1_P

B9

MIPI0C_DATA1_N

A13

MIPI0C_DATA2_P

B13

MIPI0C_DATA2_N

B14

MIPI0C_DATA3_P

A14

MIPI0C_DATA3_N

A12

MIPI0C_CLK_P

B12

MIPI0C_CLK_N

D12

MIPI0C_REXT

A3

MIPID_DATA0_P

B3

MIPID_DATA0_N

B4

MIPID_DATA1_P

A4

MIPID_DATA1_N

B6

MIPID_DATA2_P

A6

MIPID_DATA2_N

A7

MIPID_DATA3_P

B7

MIPID_DATA3_N

A5

MIPID_CLK_P

B5

MIPID_CLK_N

D9

MIPID_REXT

E10

VDD085_MIPI

D10

E7

E14

E11

D8

VDD18_MIPI

D13

E8

E13

U0600

MAUI-2GB-25NM-DDR-H

FCMSP

SC58980B0B-A040

SYM 3 OF 14

CRITICAL

ROOM=SOC

SENSOR0_ISTRB

SENSOR0_XSHUTDOWN

SENSOR1_ISTRB

SENSOR1_XSHUTDOWN

MIPICSI_MUXSEL

MIPI1C_DATA0_P

MIPI1C_DATA0_N

MIPI1C_DATA1_P

MIPI1C_DATA1_N

ISP_I2C0_SCL

ISP_I2C0_SDA

ISP_I2C1_SCL

ISP_I2C1_SDA

SENSOR0_CLK

SENSOR0_RST

SENSOR1_CLK

SENSOR1_RST

MIPI1C_REXT

MIPI1C_CLK_P

MIPI1C_CLK_N

G31

G32

F35

G34

D33

D32

F33

E34

D34

F32

C35

C34

G35

D14

B17

A17

B19

A19

A18

B18

1.62-1.98V @23mA MAX

PP1V8PP_FIXED

1

C0802

0.1UF

20%

6.3V

2

X5R-CERM

01005

ROOM=SOC

1

C0815

0.1UF

20%

6.3V

2

X5R-CERM

01005

ROOM=SOC

1

R0804

1.00K

5%

1/32W

MF

01005

2

ROOM=SOC

1

R0805

1.00K

5%

1/32W

MF

01005

2

ROOM=SOC

AP_TO_RCAM_CLK_R

AP_TO_RCAM_SHUTDOWN_L

AP_TO_FCAM_CLK_R

AP_TO_FCAM_SHUTDOWN_L

NC

AP_TO_STOCKHOLM_DWLD_REQUEST

NC

AP_TO_MUON_BL_STROBE_EN

NC

FCAM_REXT

MIPI_FCAM_TO_AP_DATA0_P

MIPI_FCAM_TO_AP_DATA0_N

MIPI_FCAM_TO_AP_DATA1_P

MIPI_FCAM_TO_AP_DATA1_N

MIPI_FCAM_TO_AP_CLK_P

MIPI_FCAM_TO_AP_CLK_N

33 29

1

2

OUT

OUT

R0806

1.00K

5%

1/32W

MF

01005

ROOM=SOC

21

20

1

2

R0809

33.2

1% MF

ROOM=SOC

OUT

OUT

IN

IN

IN

IN

IN

IN

21 20 17 14 13 12 9 8 7 6 5 3 14 11 6

PP1V8

R0807

1.00K

5%

1/32W

MF

01005

ROOM=SOC

R0808

MF1% 1/32W

21

01005

1/32W

33

27

20

20

20

20

20

20

33 29

I2C_ISP_TO_RCAM_SCL

I2C_ISP_BI_RCAM_SDA

I2C_ISP_TO_FCAM_SCL

I2C_ISP_BI_FCAM_SDA

33.2

01005

ROOM=SOC

21

AP_TO_RCAM_CLK

AP_TO_FCAM_CLK

D

NOTE:VDD12_LPDP SHOULD BE POWERED

EVEN WHEN LPDP IS NOT USED

15 6 5

21 20 17 14 13 12 9 8 7 6 5 3

OUT

BI

22 21

22 21

PP1V2

E23

E25

F24

E27

VDD12_LPDP

C

U0600

OUT

BI

OUT

OUT

20

21

20

20

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

A29

LPDP_AUX_P

B29

LPDP_AUX_N

A33

LPDP_TX0_P

B33

LPDP_TX0_N

A32

LPDP_TX1_P

B32

LPDP_TX1_N

A31

LPDP_TX2_P

B31

LPDP_TX2_N

A30

LPDP_TX3_P

B30

LPDP_TX3_N

D24

LPDP_CAL_DRV_OUT

D25

LPDP_CAL_VSS_EXT

AL4

EDP_HPD

H35

DP_WAKEUP

MAUI-2GB-25NM-DDR-H

FCMSP

SC58980B0B-A040

SYM 4 OF 14

CRITICAL

ROOM=SOC

B

R0801

4.02K

1%

1/32W

MF

01005

ROOM=SOC

1

2

R0802

4.02K

1%

1/32W

MF

01005

ROOM=SOC

1

1

2

R0803

4.02K

1%

1/32W

MF

01005

2

ROOM=SOC

A

8 7 5 4 2 1

SYNC_MASTER=N/A

PAGE TITLE

SYNC_DATE=N/A

A

SOC:CAMERA & DISPLAY

DRAWING NUMBER SIZE

Apple Inc.

R

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

IV ALL RIGHTS RESERVED

051-1902

REVISION

A.0.0

BRANCH

PAGE

8 OF 49

SHEET

7 OF 59

D

36

Page 9

MAUI - GPIO & SERIAL INTERFACES

VIETMOBILE.VN

345678

2 1

D

C

B

31

31

33 32 16

33 32 16

25

25

25

33

33

33

22

28

29

16

33

33

26

33 29 9

26

33

26

33

33 3

33 3

24 16

33

13

29

33

33

33 32 16 8

33

28

R0900

1.00K

1%

1/32W

MF

01005

ROOM=SOC

1

R0901

2

2.2K

1/32W

01005

ROOM=SOC

5%

MF

1

R0902

2

2.2K

1/32W

01005

ROOM=SOC

5%

MF

1

R0903

2

2.2K

1/32W

01005

ROOM=SOC

5%

MF

1

R0904

2

1.33K

1%

1/32W

MF

01005

ROOM=SOC

1

R0905

2

1.33K

1%

1/32W

MF

01005

ROOM=SOC

PP1V8

1

2

33 29

21 20 17 14 13 12 9 8 7 6 5 3

D

R0920

24

OUT

26

OUT

25

OUT

OUT

IN

IN

IN

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

IN

OUT

OUT

3

IN

AP_TO_HP_HS3_CTRL

AP_TO_HP_HS4_CTRL

BUTTON_VOL_UP_L

BUTTON_VOL_DOWN_L

SPEAKERAMP_TO_AP_INT_L

AP_TO_SPEAKERAMP_STAYIN_ALIVE

AP_TO_SPEAKERAMP_RESET_L

AP_TO_BT_WAKE

AP_TO_BB_RESET_L

PCIE_AP_TO_WLAN_DEV_WAKE

AP_TO_LED_DRIVER_EN

AP_TO_TOUCH_RESET_L

AP_TO_LCM_RESET_L

PMU_TO_AP_IRQ_L

AP_TO_BB_PCIE_DEV_WAKE

AP_TO_STOCKHOLM_DEV_WAKE

BOARD_ID3

NC_AP_TO_STOCKHOLM_SIM_SEL

3

IN

OUT

IN

IN

OUT

OUT

IN

3

IN

IN

OUT

3

IN

3

IN

IN

OUT

OUT

IN

3

IN

3

IN

3

IN

3

IN

OUT

IN

IN

OUT

OUT

BOOT_CONFIG0

AP_TO_ARC_RESET_L

LCM_TO_OWL_BSYNC

ARC_TO_AP_INT_L

BB_TO_AP_GPS_TIME_MARK

AP_TO_ARC_STAYIN_ALIVE

BB_TO_AP_RESET_DETECT_L

BOOT_CONFIG1

FORCE_DFU

DFU_STATUS

BOOT_CONFIG2

BOARD_ID4

CODEC_TO_AP_PMU_INT_L

AP_TO_BB_RADIO_ON_L

AP_TO_NAND_FW_STRAP

TOUCH_TO_AP_INT_L

BOARD_REV3

BOARD_REV2

BOARD_REV1

BOARD_REV0

AP_TO_BB_COREDUMP

BB_IPC_GPIO

BUTTON_RINGER_A

AP_TO_BB_MESA_UP_L

MAMBA_EXT_LDO_EN

(AP TO BB)

C1

D2

D1

F1

E2

F3

F2

H3

G3

J1

H4

K1

J3

K2

J4

L2

K3

L3

N1

AH2

AH3

AH4

AJ1

AJ2

AJ3

AJ4

AK1

AP3

AN4

AP4

AP5

AR2

AR3

AR4

AP6

AT3

AT4

AR6

AP7

AT5

AP8

AP9

AP10

GPIO_0

GPIO_1

GPIO_2

GPIO_3

GPIO_4

GPIO_5

GPIO_6

GPIO_7

GPIO_8

GPIO_9

GPIO_10

GPIO_11

GPIO_12

GPIO_13

GPIO_14

GPIO_15

GPIO_16

GPIO_17

GPIO_18

GPIO_19

GPIO_20

GPIO_21

GPIO_22

GPIO_23

GPIO_24

GPIO_25

GPIO_26

GPIO_27

GPIO_28

GPIO_29

GPIO_30

GPIO_31

GPIO_32

GPIO_33

GPIO_34

GPIO_35

GPIO_36

GPIO_37

GPIO_38

GPIO_39

GPIO_40

GPIO_41

GPIO_42

U0600

MAUI-2GB-25NM-DDR-H

FCMSP

SC58980B0B-A040

SYM 5 OF 14

CRITICAL

ROOM=SOC

OMIT_TABLE

TMR32_PWM0

TMR32_PWM1

TMR32_PWM2

UART0_RXD

UART0_TXD

UART1_CTS*

UART1_RTS*

UART1_RXD

UART1_TXD

UART2_CTS*

UART2_RTS*

UART2_RXD

UART2_TXD

UART3_CTS*

UART3_RTS*

UART3_RXD

UART3_TXD

UART4_CTS*

UART4_RTS*

UART4_RXD

UART4_TXD

UART5_RTXD

UART6_RXD

UART6_TXD

UART7_RXD

UART7_TXD

AE1

AF2

AF3

AE3

AE4

K31

K32

L33

L32

AT23

AR20

AP23

AP22

N4

P3

R3

R2

J33

J34

J35

K33

T32

AF1

AE2

J31

J32

NC

NC

NC

UART_AP_DEBUG_RXD

UART_AP_DEBUG_TXD

UART_BT_TO_AP_CTS_L

UART_AP_TO_BT_RTS_L

UART_BT_TO_AP_RXD

UART_AP_TO_BT_TXD

NC

CAM_EXT_LDO_EN

NC

NC

UART_STOCKHOLM_TO_AP_CTS_L

UART_AP_TO_STOCKHOLM_RTS_L

UART_STOCKHOLM_TO_AP_RXD

UART_AP_TO_STOCKHOLM_TXD

UART_WLAN_TO_AP_CTS_L

UART_AP_TO_WLAN_RTS_L

UART_WLAN_TO_AP_RXD

UART_AP_TO_WLAN_TXD

SWI_AP_BI_TIGRIS

UART_ACCESSORY_TO_AP_RXD

UART_AP_TO_ACCESSORY_TXD

NC

OUT

I2S_AP_TO_CODEC_MCLK

I2S_AP_TO_ARC_MCLK

I2S_AP_TO_SPEAKERAMP_MCLK

33 30

33 30

33

33

33

33

21

33

33

33

33

33

33

33

33

17 9

30

30

29

OUT

IN

OUT

IN

OUT

IN

OUT

OUT

IN

OUT

IN

OUT

IN

OUT

IN

OUT

BI

IN

OUT

SPI_AP_TO_TOUCH_SCLK

ROOM=SOC

PP0906

P2MM-NSM

R0960

01005

33.2

1/32W

01005

ROOM=SOC

R0921

33.2

1/32W

01005

ROOM=SOC

R0922

33.2

1/32W

01005

ROOM=SOC

SM

1

PP

ROOM=SOC

0.00

0%

ROOM=SOC

R0930

28

OUT

PP1V8

SPI_AP_TO_MESA_SCLK

33 29

21 20 17 14 13 12 9 8 7 6 5 3

01005

0.00

0%

1%

MF

1%

MF

1%

MF

21

1/32W

21

21

24 9

24 9

24 9

21

21

26 25 24

26 25 24

26 25 24

26 25 24

30 16

MF

MF1/32W

24

33

33

33

33

20

33

33

33

33

24

24

24

24

24

24

24

24

29

29

29

28

28

28

I2S_AP_TO_CODEC_MCLK_R

OUT

OUT

IN

OUT

I2S_AP_OWL_TO_CODEC_XSP_BCLK

I2S_AP_OWL_TO_CODEC_XSP_LRCLK

I2S_CODEC_TO_AP_OWL_XSP_DIN

I2S_AP_TO_CODEC_XSP_DOUT

I2S_AP_TO_ARC_MCLK_R

OUT

OUT

IN

OUT

I2S_AP_TO_BT_BCLK

I2S_AP_TO_BT_LRCLK

I2S_BT_TO_AP_DIN

I2S_AP_TO_BT_DOUT

I2S_AP_TO_SPEAKERAMP_MCLK_R

OUT

OUT

IN

OUT

IN

OUT

OUT

IN

OUT

IN

OUT

OUT

IN

OUT

3

IN

3

IN

3

IN

IN

OUT

OUT

OUT

IN

OUT

I2S_AP_TO_CODEC_ASP_BCLK

I2S_AP_TO_CODEC_ASP_LRCLK

I2S_CODEC_TO_AP_ASP_DIN

I2S_AP_TO_CODEC_ASP_DOUT

ALS_TO_AP_INT_L

I2S_AP_TO_BB_BCLK

I2S_AP_TO_BB_LRCLK

I2S_BB_TO_AP_DIN

I2S_AP_TO_BB_DOUT

TRISTAR_TO_AP_INT

I2S_AP_TO_CODEC_MSP_BCLK

I2S_AP_TO_CODEC_MSP_LRCLK

I2S_CODEC_TO_AP_MSP_DIN

I2S_AP_TO_CODEC_MSP_DOUT

BOARD_ID2

BOARD_ID1

BOARD_ID0

SPI_CODEC_TO_AP_MISO

SPI_AP_TO_CODEC_MOSI

SPI_AP_TO_CODEC_SCLK

SPI_AP_TO_CODEC_CS_L

SPI_TOUCH_TO_AP_MISO

SPI_AP_TO_TOUCH_MOSI

SPI_AP_TO_TOUCH_SCLK_R

SPI_AP_TO_TOUCH_CS_L

OUT

IN

OUT

SPI_MESA_TO_AP_MISO

SPI_AP_TO_MESA_MOSI

SPI_AP_TO_MESA_SCLK_R

IN

MESA_TO_AP_INT

NC

P34

R34

N34

N35

M33

M4

M3

P1

N3

L4

U32

V33

U33

T33

V34

AM3

AM4

AN2

AP1

AN1

R32

R31

V32

P31

P32

AD4

AC3

AB2

AD3

P33

V35

N32

M31

E33

E35

F34

F31

AA2

Y2

AA3

AC4

I2S0_MCK

I2S0_BCLK

I2S0_LRCK

I2S0_DIN

I2S0_DOUT

I2S1_MCK

I2S1_BCLK

I2S1_LRCK

I2S1_DIN

I2S1_DOUT

I2S2_MCK

I2S2_BCLK

I2S2_LRCK

I2S2_DIN

I2S2_DOUT

I2S3_MCK

I2S3_BCLK

I2S3_LRCK

I2S3_DIN

I2S3_DOUT

I2S4_MCK

I2S4_BCLK

I2S4_LRCK

I2S4_DIN

I2S4_DOUT

SPI0_MISO

SPI0_MOSI

SPI0_SCLK

SPI0_SSIN

SPI1_MISO

SPI1_MOSI

SPI1_SCLK

SPI1_SSIN

SPI2_MISO

SPI2_MOSI

SPI2_SCLK

SPI2_SSIN

SPI3_MISO

SPI3_MOSI

SPI3_SCLK

SPI3_SSIN

U0600

FCMSP

SC58980B0B-A040

SYM 6 OF 14

MAUI-2GB-25NM-DDR-H

CRITICAL

ROOM=SOC

SEP_SPI0_SCLK

SEP_SPI0_MISO

SEP_SPI0_MOSI

CPU_ACTIVE_STATUS

NAND_SYS_CLK

I2C0_SCL

I2C0_SDA

I2C1_SCL

I2C1_SDA

I2C2_SCL

I2C2_SDA

SEP_I2C_SCL

SEP_I2C_SDA

SEP_GPIO0

SEP_GPIO1

SOCHOT0

SOCHOT1

CLK32K_OUT

ANALOG_PROX

PIN J31 (UART7_RXD) SHOULD BE

BRIEFLY SWITCHED TO PD TO CHECK STATE.

STUFF R0911 FOR ANALOG PROX.

NOSTUFF R0911 FOR DOPPLER PROX.

PROX_SELECT

1

R0911

1.00K

5%

1/32W

MF

01005

2

ROOM=SOC

E31

D35

AH1

AG4

L31

M32

1

R0907

2

W3

AA4

U2

NC

NC

R0906

2.2K

5%

1/32W

MF

01005

ROOM=SOC

NC

V3

Y4

Y3

NC

AB4

NC

AM1

PMU_TO_AP_SOCHOT0_R_L

AM2

H31

NC

H34

AP_TO_TOUCH_CLK32K_RESET_L

AM24

AP_TO_NAND_SYS_CLK_R

2.2K

5%

1/32W

MF

01005

ROOM=SOC

R0941

ROOM=SOC

PP1V8