IOR IR2114SS, IR21141SS, IR2214SS, IR22141SS User Manual

查询IR2114SS供应商

Data Sheet No. PD60213 revC

IR2114SS/ IR21141SS

HALF-BRIDGE GATE DRIVER IC

Features

• Floating channel up to +600 or +1200V

• Soft over-current shutdown

• Synchronization signal to synchronize shut down with the other phases

• Integrated desaturation detection circuit

• Two stage turn on output for di/dt control

• Separate pull-up/pull-down output drive pins

• Matched delay outputs

• Under voltage lockout with hysteresis band

Description

The IR2114/21141/2214/IR22141 gate driver family is suited to drive a single

half bridge in power switching applications. The high gate driving capability (2A

source, 3A sink) and the low quiescent current enable bootstrap supply

techniques in medium power systems. These drivers feature full short circuit

protection by means of the power transistor desaturation detection and manages

all the half-bridge faults by turning off smoothly the desaturated transistor

through the dedicated soft shut down pin, therefore preventing over-voltages and

reducing EM emissions. In multi-phase system IR2114/21141/2214/IR22141

drivers communicate using a dedicated local network (SY_FLT and FAULT/SD

signals) to properly manage phase-to-phase short circuits. The system controller

may force shutdown or read device fault state through the 3.3 V compatible

CMOS I/O pin (FAULT/SD). To improve the signal immunity from DC-bus noise,

the control and power ground use dedicated pins enabling low-side emitter

current sensing as well. Undervoltage conditions in floating and low voltage

circuits are managed independently.

IR2214SS/IR22141SS

Product Summary

V

OFFSET

IO+/- (typ) 2.0 A / 3.0A

V

10.4V - 20V

OUT

Deadtime matching (max) 75 nsec

Deadtime (typ) 330 nsec

Desat blanking time (typ) 3 µsec

DSH, DSL input voltage

threshold (typ)

Soft shutdown time (typ) 9.25 µsec

Package

24-Lead SSOP

600V or

1200V max.

8.0 V

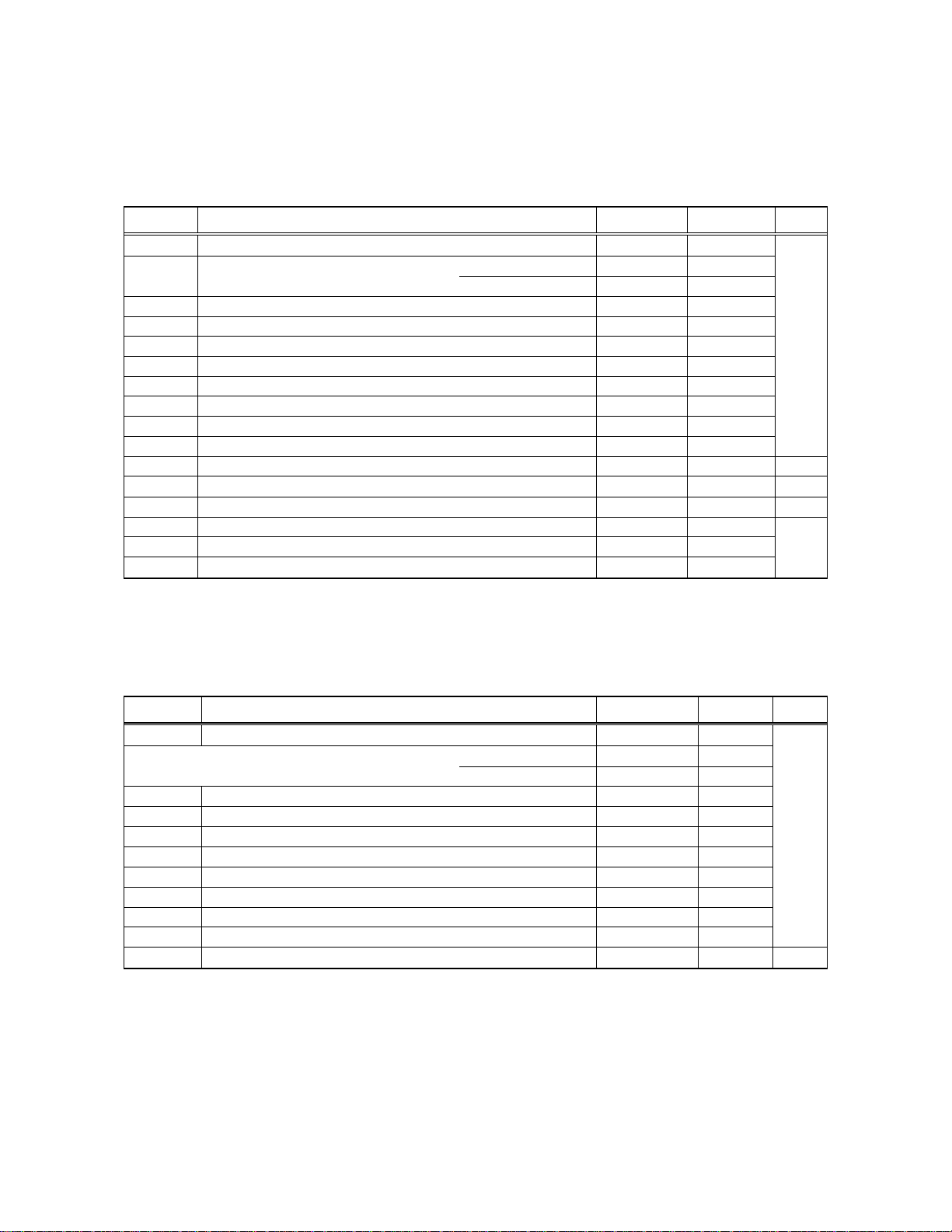

Typical connection

DC BUS

(1200V)

15 V

uP,

Control

VCC

LIN

HIN

FAULT/SD

FLT_CLR

SY_FLT

VSS

IR2214

HOP

HON

SSDH

DSH

LOP

LON

SSDL

COM

DC+

VB

DC-

Motor

VS

DSL

1

IR2114/IR21141/IR2214/IR22141

Absolute Maximum Ratings

Absolute maximum ratings indicate sustained limits beyond which damage to the device may occur. All

voltage parameters are absolute voltages referenced to V

The thermal resistance and power dissipation ratings are measured under board mounted and still air

conditions.

Symbol Definition Min. Max. Units

VS High side offset voltage VB - 25 VB + 0.3

VB High side floating supply voltage

VHO High side floating output voltage (HOP, HON and SSDH) VS - 0.3 VB + 0.3

VCC Low side and logic fixed supply voltage -0.3 25

COM Power ground VCC - 25 VCC + 0.3

VLO Low side output voltage (LOP, LON and SSDL) VCOM -0.3 VCC + 0.3

VIN Logic input voltage (HIN, LIN and FLT_CLR) VSS -0.3 VCC + 0.3

VFLT FAULT input/output voltage (FAULT/SD and SY_FLT) VSS -0.3 VCC + 0.3

VDSH High side DS input voltage VS -3 VB + 0.3

VDSL Low side DS input voltage VCOM -3 VCC + 0.3

dVs/dt Allowable offset voltage slew rate — 50 V/ns

PD Package power dissipation @ TA +25°C — 1.5 W

RthJA Thermal resistance, junction to ambient — 65 °C/W

TJ Junction temperature — 125

TS Storage temperature -55 150

TL Lead temperature (soldering, 10 seconds) — 300

SS, all currents are defined positive into any lead

(IR2114 or IR21141)

(IR2214 or IR22141)

-0.3 625

-0.3 1225

V

°C

Recommended Operating Conditions

For proper operation the device should be used within the recommended conditions. All voltage parameters

are absolute voltages referenced to V

differential.

Symbol Definition Min. Max. Units

VB High side floating supply voltage (Note 1) VS + 11.5 VS + 20

VS High side floating supply offset

voltage

VHO High side output voltage (HOP, HON and SSDH) VS VS + 20

VLO Low side output voltage (LOP, LON and SSDL) VCOM VCC

VCC Low side and logic fixed supply voltage (Note 1) 11.5 20

COM Power ground -5 5

VIN Logic input voltage (HIN, LIN and FLT_CLR) VSS VCC

VFLT Fault input/output voltage (FAULT/SD and SY_FLT) VSS VCC

VDSH High side DS pin input voltage VS - 2.0 VB

VDSL Low side DS pin input voltage VCOM - 2.0 VCC

TA Ambient temperature -40 125 °C

Note 1: While internal circuitry is operational below the indicated supply voltages, the UV lockout disables

the output drivers if the UV thresholds are not reached.

Note 2: Logic operational for V

V

SS-VBS. (Please refer to the Design Tip DT97-3 for more details).

S from VSS-5V to VSS+600V or 1200V. Logic state held for VS from VSS-5V to

SS. The VS offset rating is tested with all supplies biased at 15V

(IR2114 or IR21141)

(IR2214 or IR22141)

Note 2 600

Note 2 1200

V

2

IR2114/IR21141/IR2214/IR22141

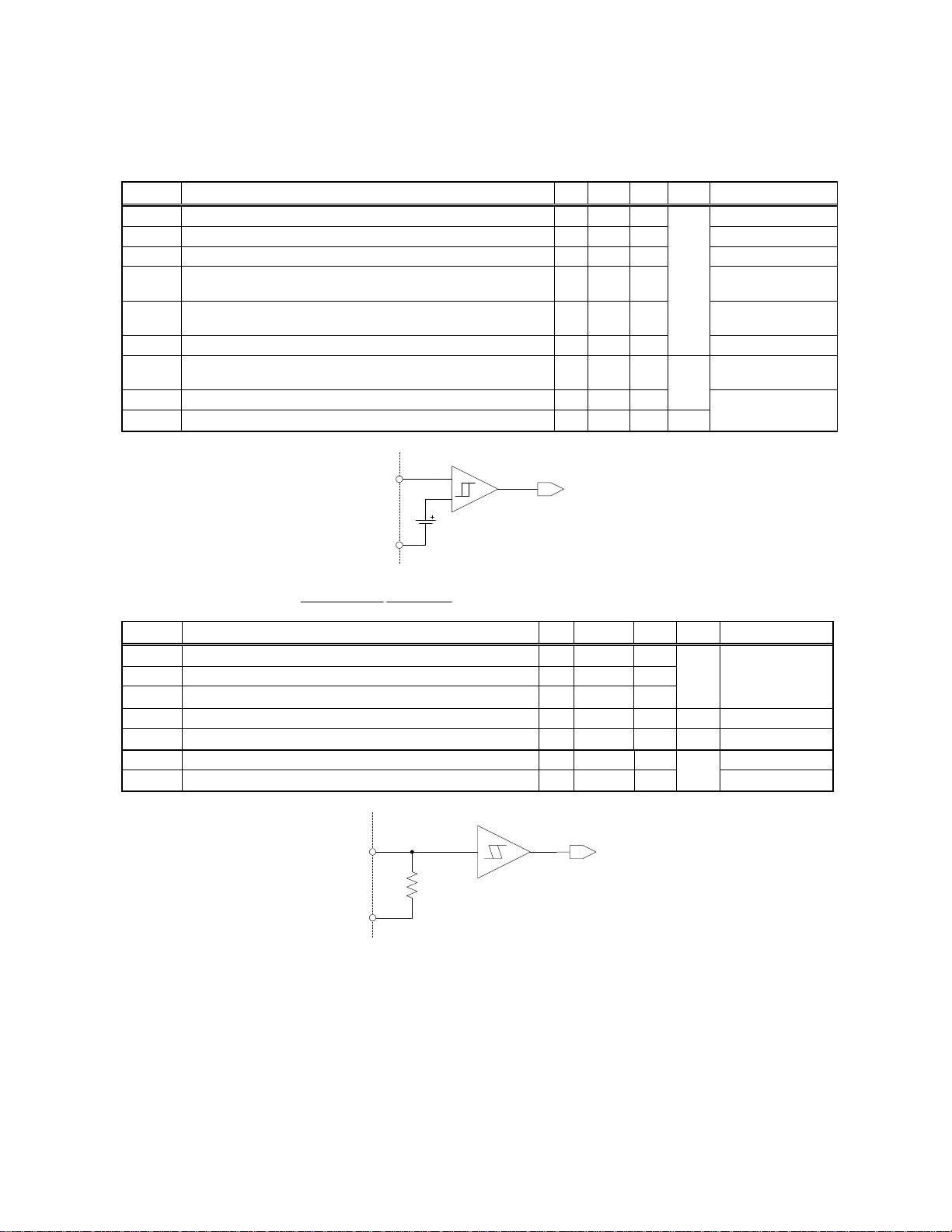

Static Electrical Characteristics

= 15 V, VSS = COM = 0 V, VS = 0 ÷ 600V or 1200 V and TA = 25 °C unless otherwise specified.

V

CC

Pin: V

Symbol Definition Min Typ Max Units Test Conditions

VCCUV+ Vcc supply undervoltage positive going threshold 9.3 10.2 11.4

VCCUV- Vcc supply undervoltage negative going threshold 8.7 9.3 10.3

VCCUVH Vcc supply undervoltage lockout hysteresis - 0.9 -

VBSUV+ (VB-VS) supply undervoltage positive going threshold 9.3 10.2 11.4 VS=0V, VS=600V

VBSUV- (VB-VS) supply undervoltage negative going

VBSUVH (VB-VS) supply undervoltage lockout hysteresis - 0.9 -

IQCC Quiescent Vcc supply current - 0.7 2.5

, VSS, VB, VS

CC

V

or 1200V

8.7 9.3 10.3 VS=0V, VS=600V

threshold

or 1200V

ILK Offset supply leakage current - - 50 VB = VS = 600V or

µA

IQBS Quiescent VBS supply current - 400 800

1200V

V

IN = 0V or 3.3V

mA (No load)

VCC/VB

comparator

internal

UV

signal

VCCUV/VBSUV

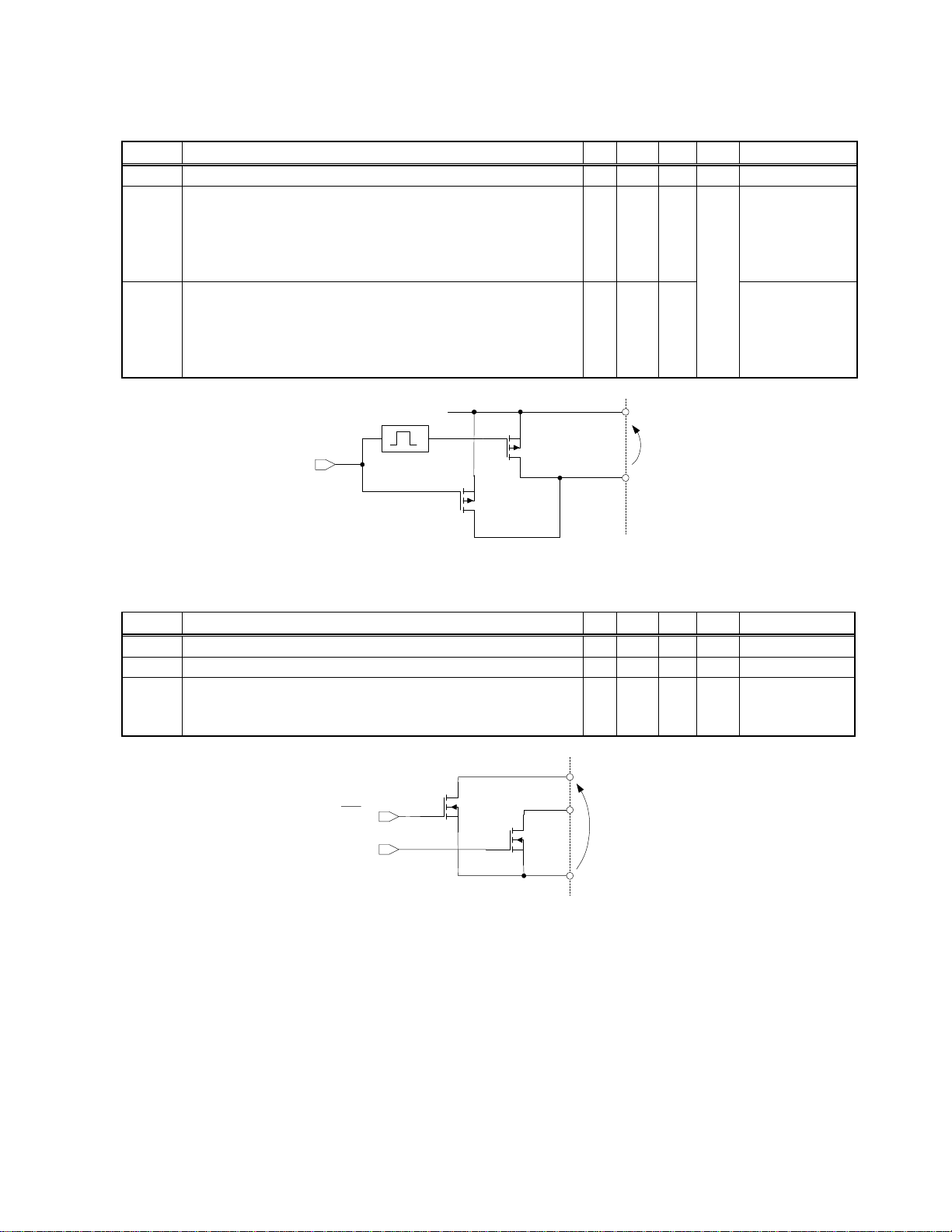

VSS/VS

Figure 1: Undervoltage diagram

Pin: HIN, LIN, FLTCLR, FAULT/SD, SY_FLT

Symbol Definition Min Typ Max Units Test Conditions

VIH Logic "1" input voltage 2.0 - VIL Logic "0" input voltage - - 0.8

VIHSS

IIN+ Logic "1" input bias current - 370 -

IIN- Logic "0" input bias current -1 - 0

RON,FLT FAULT/SD open drain resistance - 60 -

RON,SY SY_FLT open drain resistance - 60 -

Logic input hysteresis 0.2 0.4 -

CC = VCCUV- to

V

V

µA

20V

V

IN = 3.3V

V

IN = 0V

PW 7 µs

schmitt

HIN/LIN/

FLTCLR

VSS

trigger

10k

internal

signal

Figure 2: HIN, LIN and FLTCLR diagram

3

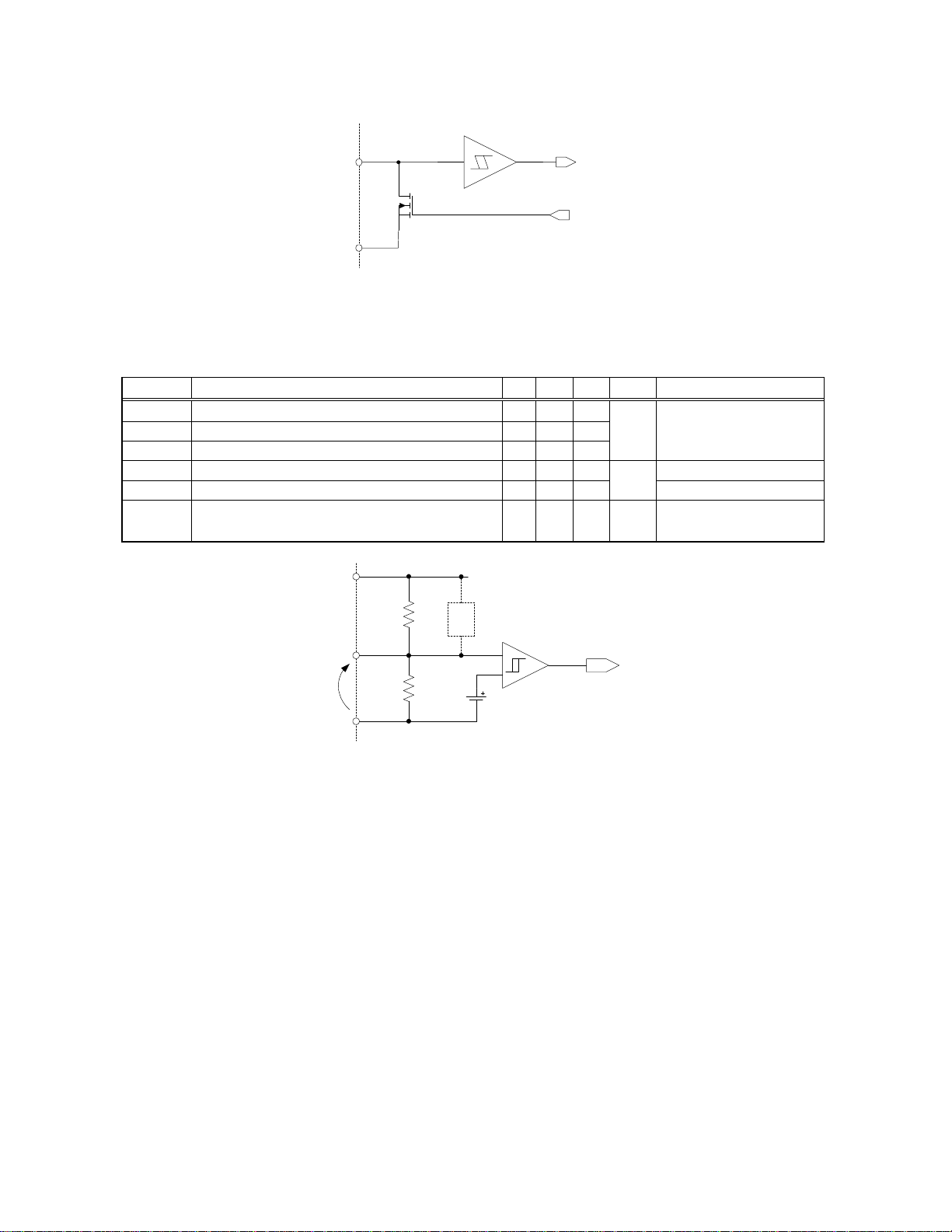

IR2114/IR21141/IR2214/IR22141

FAULT/SD

SY_FLT

VSS

RON

schmitt

trigger

fault/hold

inte rnal signa l

hard/s oft shut down

inte rnal signa l

Figure 3: FAULT/SD and SY_FLT diagram

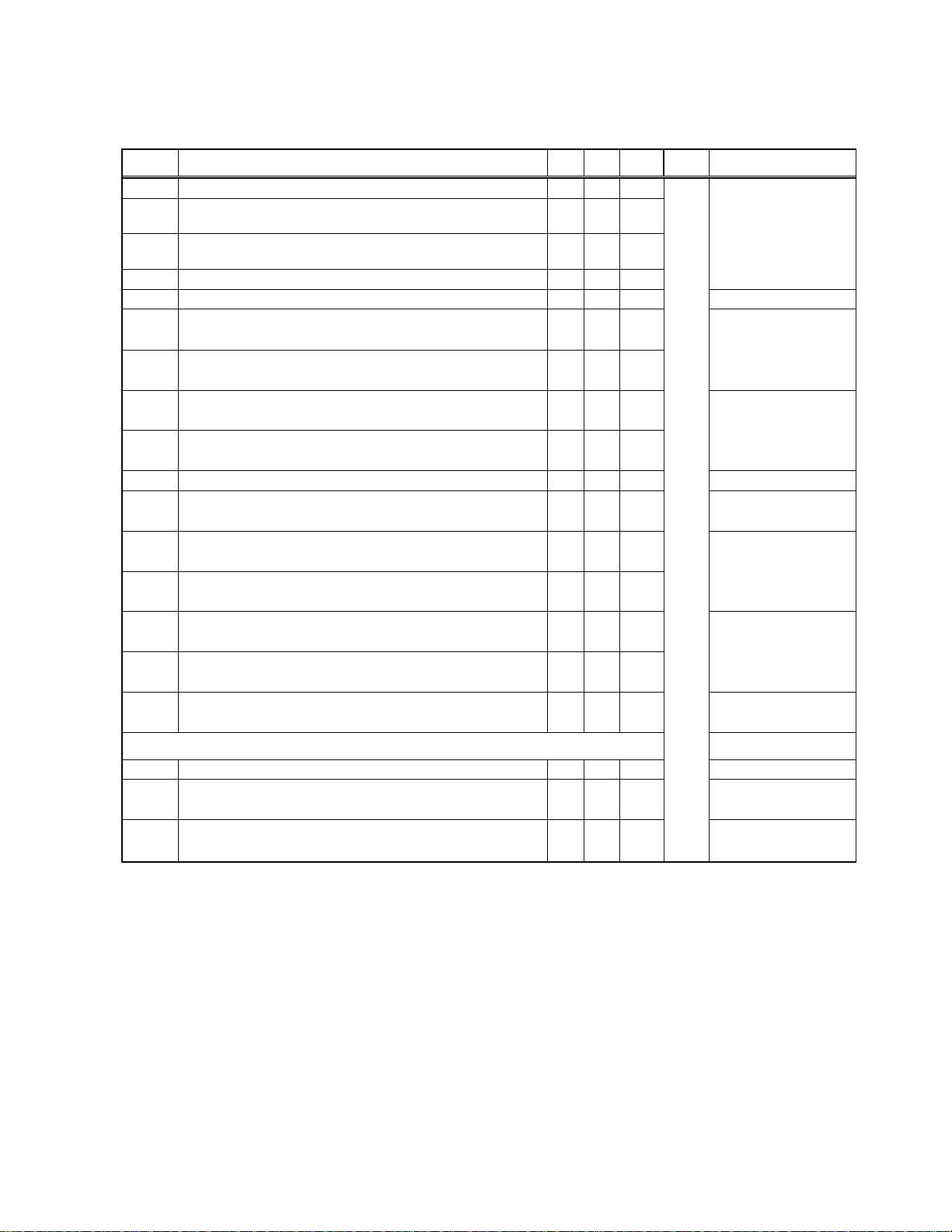

Pin: DSL, DSH

The active bias is present only in IR21141 and IR22141. V

COM and V

Symbol Definition Min Typ Max Units Test Conditions

VDESAT+ High desat input threshold voltage 7.2 8.0 8.8

VDESAT- Low desat input threshold voltage 6.3 7.0 7.7

VDSTH Desat input voltage hysteresis - 1.0 -

IDS+ High DSH or DSL input bias current - 21 - VDESAT = VCC or VBS

IDS- Low DSH or DSL input bias current - -160 -

IDSB DSH or DSL input bias current - -20 - mA VDESAT =

(IR21141 and IR22141 only) (VCC or VBS) - 2V

respectively for DSL and DSH.

S

DESAT

, IDS and I

parameters are referenced to

DSB

V See Fig. 16, 4

µA

VDESAT = 0V

VCC/VBS

DSL/DSH

DESAT

V

COM/VS

active

100k

bias

comparator

700k

Figure 4: DSH and DSL diagram.

SSD

internal

signal

4

IR2114/IR21141/IR2214/IR22141

Pin: HOP, LOP

Symbol Definition Min Typ Max Units Test Conditions

VOH High level output voltage, VB – VHOP or Vcc –VLOP - 40 300

mV I

IO1+ Output high first stage short circuit pulsed current - 2 - VHOP/LOP=0V,

IO2+ Output high second stage short circuit pulsed current

- 1 -

A

200ns

oneshot

VCC/VB

O = 20mA

H

or LIN= 1,

IN

PW200ns,

resistive load,

see Fig. 8

VHOP/LOP=0V,

H

or LIN = 1,

IN

400nsPW10µs,

resistive load,

see Fig. 8

on/off

internal signal

VOH

LOP/HOP

Figure 5: HOP and LOP diagram

Pin: HON, LON, SSDH, SSDL

Symbol Definition Min Typ Max Units Test Conditions

VOL Low level output voltage, VHON or VLON - 45 300

RON,SSD Soft Shutdown on resistance (Note 1) - 90 -

IO- Output low short circuit pulsed current - 3 - A VHOP/LOP=15V,

mV I

O = 20mA

PW 7 µs

H

or LIN = 0,

IN

PW10µs

Note 1: SSD operation only.

LON/HON

on/off

internal signal

desat

internal signal

RON,SSD

SSDL/SSDH

VOL

COM/VS

Figure 6: HON, LON, SSDH and SSDL diagram

5

IR2114/IR21141/IR2214/IR22141

AC Electrical Characteristics

VCC = VBS = 15V, VS = VSS and TA = 25°C unless otherwise specified.

Symbol Definition Min. Typ. Max. Units Test Conditions

ton Turn on propagation delay 220 440 660 VIN = 0 & 1

toff Turn off propagation delay 220 440 660 VS = 0 to 600V or

1200V

tr Turn on rise time (C

tf Turn off fall time (C

ton1 Turn on first stage duration time 120 200 280 Figure 8

tDESAT1 DSH to HO soft shutdown propagation delay at HO 2000 3300 4600

turn on VHIN= 1

tDESAT2 DSH to HO soft shutdown propagation delay after 1050 — — VDESAT = 15V,Fig.10

Blanking

tDESAT3 DSL to LO soft shutdown propagation delay at LO 2000 3300 4600

turn on VLIN = 1

tDESAT4 DSL to LO soft shutdown propagation delay after 1050 — — VDESAT = 15V,Fig.10

Blanking

tDS Soft shutdown minimum pulse width of desat 1000 — — Figure 9

tSS Soft shutdown duration period 5000 9250 13500

VDS=15V,Fig. 9

=1nF) — 24 — HOP shorted to HON,

LOAD

=1nF) — 7 — Figure 7

LOAD

LOP shorted to LON,

ns

tSY_FLT, DSH to SY_FLT propagation delay at HO turn on — 3600 —

DESAT1

tSY_FLT, DSH to SY_FLT propagation delay after blanking 1300 — — VDS = 15V, Fig. 10

DESAT2

tSY_FLT, DSL to SY_FLT propagation delay at LO turn on — 3050 —

DESAT3

tSY_FLT, DSL to SY_FLT propagation delay after blanking 1050 — — VDESAT=15V,Fig.10

DESAT4

tBL DS blanking time at turn on — 3000 — VHIN = VLIN = 1

VDESAT=15V,Fig.10

Dead-time/Delay Matching Characteristics

DT Dead-time — 330 — Figure 11

MDT Dead-time matching, MDT=DTH-DTL — — 75 External DT=0nsec

Figure 11

PDM Propagation delay matching, — — 75 External DT>

Max(ton, toff) - Min(ton, toff)

VHIN = 1

VLIN = 1

500nsec, Fig.7

6

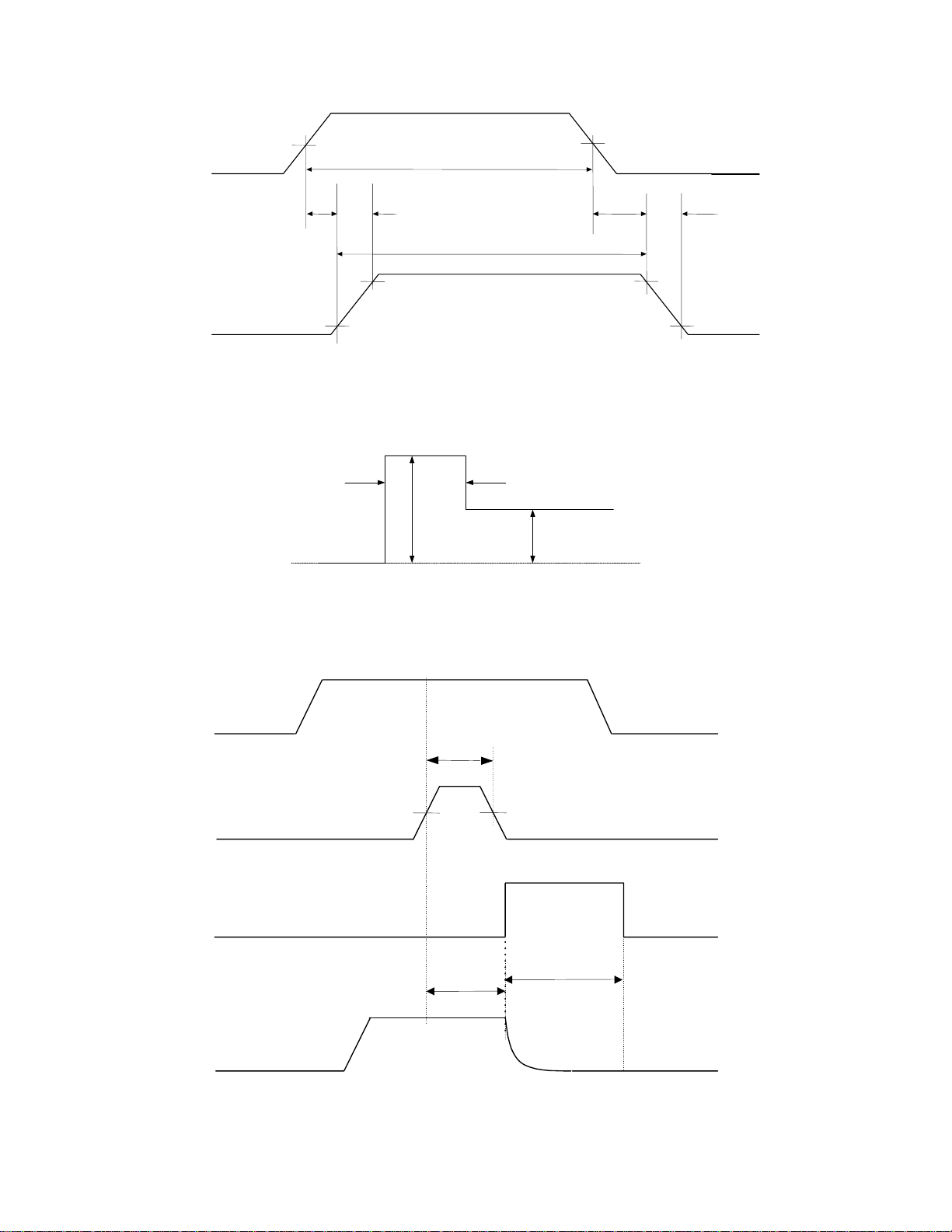

HIN

LIN

IR2114/IR21141/IR2214/IR22141

3.3V

t

on

50%

t

r

PW

in

PW

out

50%

t

off

t

f

HO (HOP=HON)

LO (LOP=LON)

90%

90%

10%

10%

Figure 7: Switching Time Waveforms

Ton1

Io1+

Io2+

Figure 8: Output Source Current

3.3V

HIN/LIN

t

DS

DSH/DSL

SSD Driver Enable

8V

t

DESAT

8V

t

SS

HO/LO

Figure 9: Soft Shutdown Timing Waveform

7

Loading...

Loading...