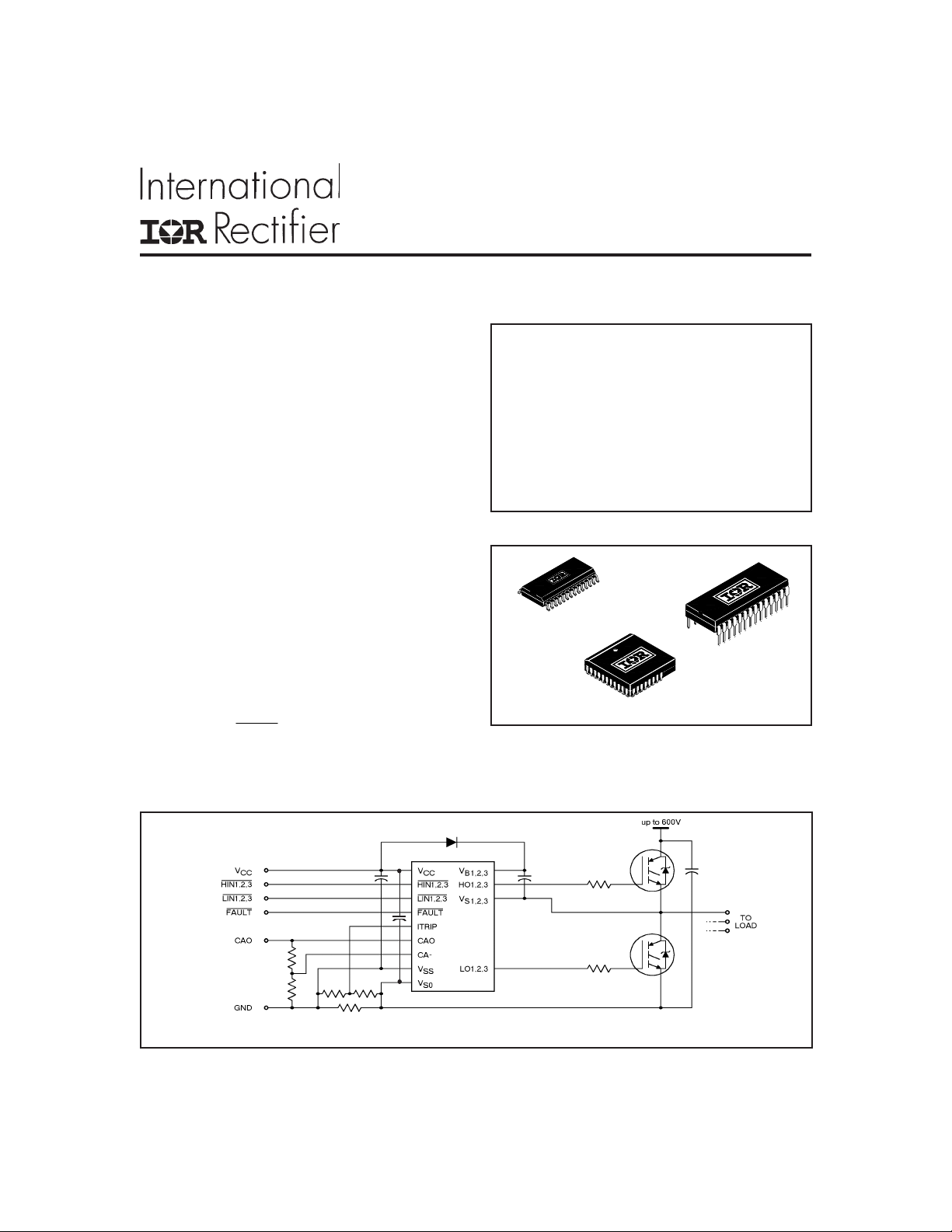

Data Sheet No. PD60019 Rev.P

IR2130/IR2132(J)(S) & (PbF)

3-PHASE BRIDGE DRIVER

Features

• Floating channel designed for bootstrap operation

Fully operational to +600V

Tolerant to negative transient voltage

dV/dt immune

• Gate drive supply range from 10 to 20V

• Undervoltage lockout for all channels

• Over-current shutdown turns off all six drivers

• Independent half-bridge drivers

Product Summary

V

OFFSET

IO+/- 200 mA / 420 mA

V

OUT

t

(typ.) 675 & 425 ns

on/off

600V max.

10 - 20V

• Matched propagation delay for all channels

• 2.5V logic compatible

• Outputs out of phase with inputs

• Cross-conduction prevention logic

Deadtime (typ.) 2.5 µs (IR2130)

0.8 µs (IR2132)

• Also available LEAD-FREE

Packages

Description

The IR2130/IR2132(J)(S) is a high voltage, high speed

power MOSFET and IGBT driver with three independent high and low side referenced output channels. Proprietary HVIC technology enables ruggedized

monolithic construction. Logic inputs are compatible with

CMOS or LSTTL outputs, down to 2.5V logic. A

ground-referenced operational amplifier provides

analog feedback of bridge current via an external current sense resistor. A current trip function which terminates all six outputs is also derived from this resistor.

FAULT

An open drain

rent or undervoltage shutdown has occurred. The output drivers feature a high pulse current buffer stage designed

for minimum driver cross-conduction. Propagation delays are matched to simplify use at high frequencies. The

floating channels can be used to drive N-channel power MOSFETs or IGBTs in the high side configuration

which operate up to 600 volts.

signal indicates if an over-cur-

28-Lead SOIC

28-Lead PDIP

44-Lead PLCC w/o 12 Leads

Typical Connection

(Refer to Lead Assignments for correct pin configuration). This/These diagram(s) show electrical connections only. Please refer

to our Application Notes and DesignTips for proper circuit board layout.

www.irf.com 1

IR2130/IR2132(J)(S) & (PbF)

Absolute Maximum Ratings

Absolute Maximum Ratings indicate sustained limits beyond which damage to the device may occur. All voltage parameters are absolute voltages referenced to VS0. The Thermal Resistance and Power Dissipation ratings are measured

under board mounted and still air conditions. Additional information is shown in Figures 50 through 53.

Symbol Definition Min. Max. Units

V

B1,2,3

V

S1,2,3

V

HO1,2,3

V

CC

V

SS

V

LO1,2,3

V

IN

V

FLT

V

CAO

V

CA-

dVS/dt Allowable Offset Supply Voltage Transient — 50 V/ns

P

D

Rth

JA

T

J

T

S

T

L

High Side Floating Supply Voltage -0.3 625

High Side Floating Offset Voltage V

High Side Floating Output Voltage V

B1,2,3

S1,2,3

- 25 V

- 0.3 V

B1,2,3

B1,2,3

Low Side and Logic Fixed Supply Voltage -0.3 25

Logic Ground VCC - 25 V

Low Side Output Voltage -0.3 V

Logic Input Voltage (

HIN1,2,3, LIN1,2,3

& ITRIP) VSS - 0.3 (V

SS

(V

+ 0.3

CC

+ 0.3

CC

+ 15) or

+ 0.3)

CC

whichever is

lower

Output Voltage VSS - 0.3 V

FAULT

Operational Amplifier Output Voltage VSS - 0.3 V

Operational Amplifier Inverting Input Voltage VSS - 0.3 V

CC

CC

CC

+ 0.3

+ 0.3

+ 0.3

Package Power Dissipation @ TA ≤ +25°C (28 Lead DIP) — 1.5

(28 Lead SOIC) — 1.6 W

(44 Lead PLCC) — 2.0

Thermal Resistance, Junction to Ambient (28 Lead DIP) — 83

(28 Lead SOIC) — 78 °C/W

(44 Lead PLCC) — 63

Junction Temperature — 150

Storage Temperature -55 1 50

L ead Temperature (Soldering, 10 seconds) — 30 0

+ 0.3

+ 0.3

V

°C

Recommended Operating Conditions

The Input/Output logic timing diagram is shown in Figure 1. For proper operation the device should be used within the

recommended conditions. All voltage parameters are absolute voltages referenced to VS0. The VS offset rating is tested

with all supplies biased at 15V differential. Typical ratings at other bias conditions are shown in Figure 54.

Symbol Definition Min. Max. Units

V

B1,2,3

V

S1,2,3

V

HO1,2,3

V

CC

V

SS

V

LO1,2,3

V

IN

V

FLT

V

CAO

V

CA-

T

A

Note 1: Logic operational for VS of (VS0 - 5V) to (VS0 + 600V). Logic state held for VS of (VS0 - 5V) to (VS0 - VBS).

(Please refer to the Design Tip DT97-3 for more details).

Note 2: All input pins, CA- and CAO pins are internally clamped with a 5.2V zener diode.

2 www.irf.com

High Side Floating Supply Voltage V

S1,2,3

+ 10 V

S1,2,3

+ 20

High Side Floating Offset Voltage Note 1 600

High Side Floating Output Voltage V

S1,2,3

V

B1,2,3

Low Side and Logic Fixed Supply Voltage 10 20

Logic Ground -5 5

Low Side Output Voltage 0 V

Logic Input Voltage (

Output Voltage V

FAULT

Operational Amplifier Output Voltage V

Operational Amplifier Inverting Input Voltage V

HIN1,2,3, LIN1,2,3

& ITRIP) V

SS

SS

SS

SS

CC

VSS + 5

V

CC

VSS + 5

VSS + 5

Ambient Temperature -40 12 5 °C

V

IR2130/IR2132(J)(S) & (PbF)

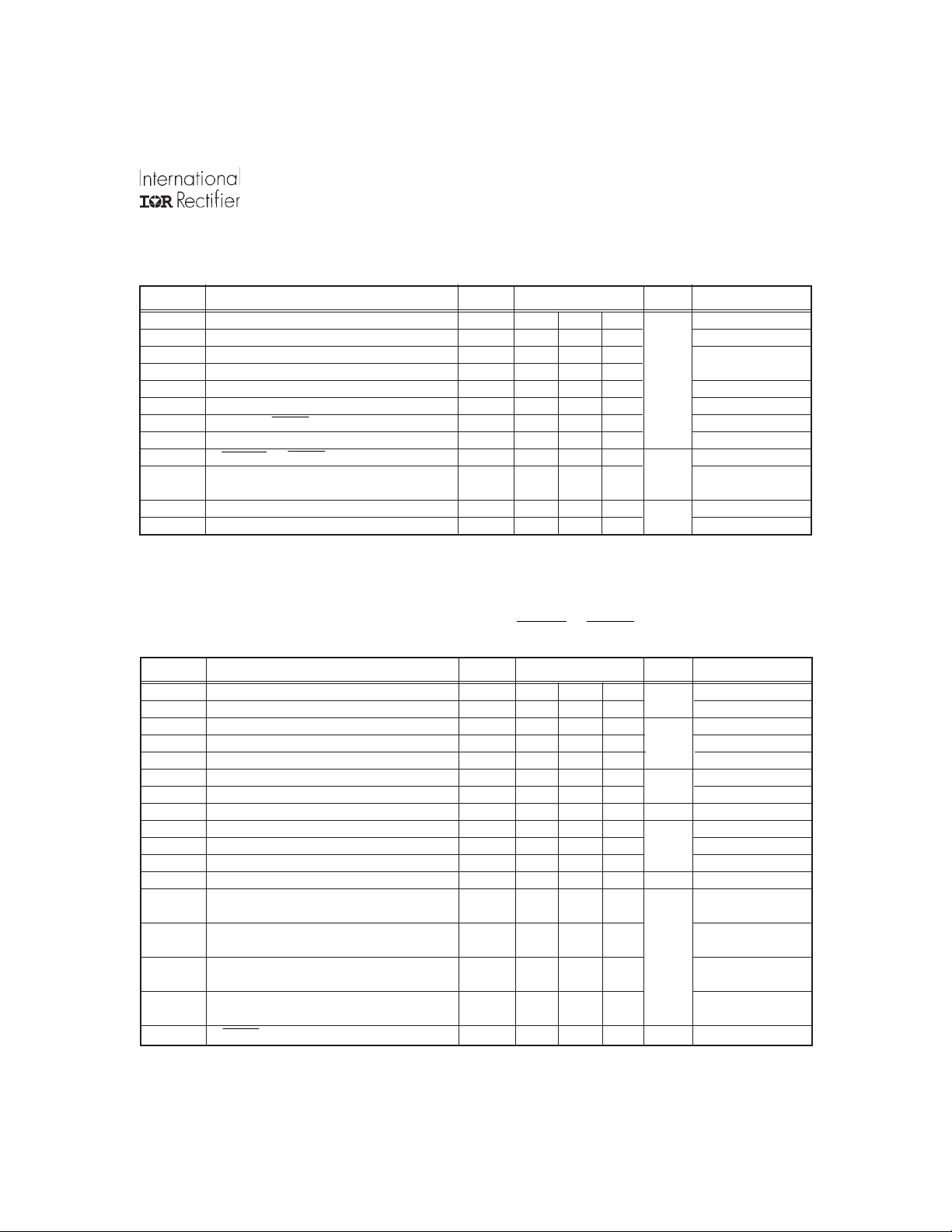

Dynamic Electrical Characteristics

V

(VCC, V

BIAS

electrical characteristics are defined in Figures 3 through 5.

Symbol Definition Figure Min. Typ. Max. Units Test Conditions

t

on

t

off

t

r

t

f

t

itrip

t

bl

t

flt

t

flt,in

t

fltclr

DT Deadtime (IR2130) 18 1.3 2.5 3.7

SR+ Operational Amplifier Slew Rate (+) 19 4.4 6.2 —

SR- Operational Amplifier Slew Rate (-) 20 2.4 3.2 —

NOTE: For high side PWM, HIN pulse width must be ≥ 1.5µsec

Static Electrical Characteristics

V

(VCC, V

BIAS

are referenced to VSS and are applicable to all six logic input leads:

are referenced to V

BS1,2,3

) = 15V, V

= VSS, CL = 1000 pF and TA = 25°C unless otherwise specified. The dynamic

S0,1,2,3

Turn-On Propagation Delay 11 500 675 850

Turn-Off Propagation Delay 12 300 425 550 V

Turn-On Rise Time 13 — 80 125 V

S1,2,3

Turn-Off Fall Time 14 — 35 55

ITRIP to Output Shutdown Prop. Delay 15 400 660 920 VIN, V

ITRIP Blanking Time — — 400 — V

ns

ITRIP to FAULT Indication Delay 16 335 590 845 VIN, V

Input Filter Time (All Six Inputs) — — 310 — V

LIN1,2,3

to FAULT Clear Time 17 6.0 9.0 12.0 VIN, V

(IR2132) 18 0.4 0. 8 1.2

µs

V

V/µs

BS1,2,3

) = 15V, V

and are applicable to the respective output leads: HO1,2,3 or LO1,2,3.

S0,1,2,3

= VSS and TA = 25°C unless otherwise specified. The VIN, VTH and IIN parameters

S0,1,2,3

HIN1,2,3

&

LIN1,2,3

. The VO and IO parameters

= 0 & 5V

IN

= 0 to 600V

= 0 & 5V

ITRIP

= 1V

ITRIP

= 0 & 5V

ITRIP

= 0 & 5V

IN

= 0 & 5V

ITRIP

= 0 & 5V

IN

Symbol Definition Figure Min. Typ. Max. Units Test Conditions

V

IH

V

V

IT,TH+

V

OH

V

OL

I

LK

I

QBS

I

QCC

I

IN+

I

IN-

I

ITRIP+

I

ITRIP-

V

BSUV+

V

BSUV-

V

CCUV+

V

CCUV-

R

on,FLT

www.irf.com 3

Logic “0” Input Voltage (OUT = LO) 21 2.2 — —

Logic “1” Input Voltage (OUT = HI) 22 — — 0.8

IL

V

ITRIP Input Positive Going Threshold 23 400 490 580

High Level Output Voltage, V

- VO 24 — — 100 VIN = 0V, IO = 0A

BIAS

mV

Low Level Output Voltage, VO 25 — — 100 VIN = 5V, IO = 0A

Offset Supply Leakage Current 26 — — 50 VB = VS = 600V

Quiescent VBS Supply Current 27 — 15 30 VIN = 0V or 5V

µA

Quiescent VCC Supply Current 28 — 3 .0 4.0 mA VIN = 0V or 5V

Logic “1” Input Bias Current (OUT = HI) 29 — 4 50 650 VIN = 0V

Logic “0” Input Bias Current (OUT = LO) 30 — 2 25 400 VIN = 5V

µA

“High” ITRIP Bias Current 31 — 75 150 ITRIP = 5V

“Low” ITRIP Bias Current 32 — — 100 nA ITRIP = 0V

VBS Supply Undervoltage Positive Going 33 7.5 8.35 9.2

Threshold

VBS Supply Undervoltage Negative Going 34 7.1 7.95 8.8

Threshold

VCC Supply Undervoltage Positive Going 35 8.3 9. 0 9.7

V

Threshold

VCC Supply Undervoltage Negative Going 36 8.0 8. 7 9.4

Threshold

Low On-Resistance 37 — 55 75 Ω

FAULT

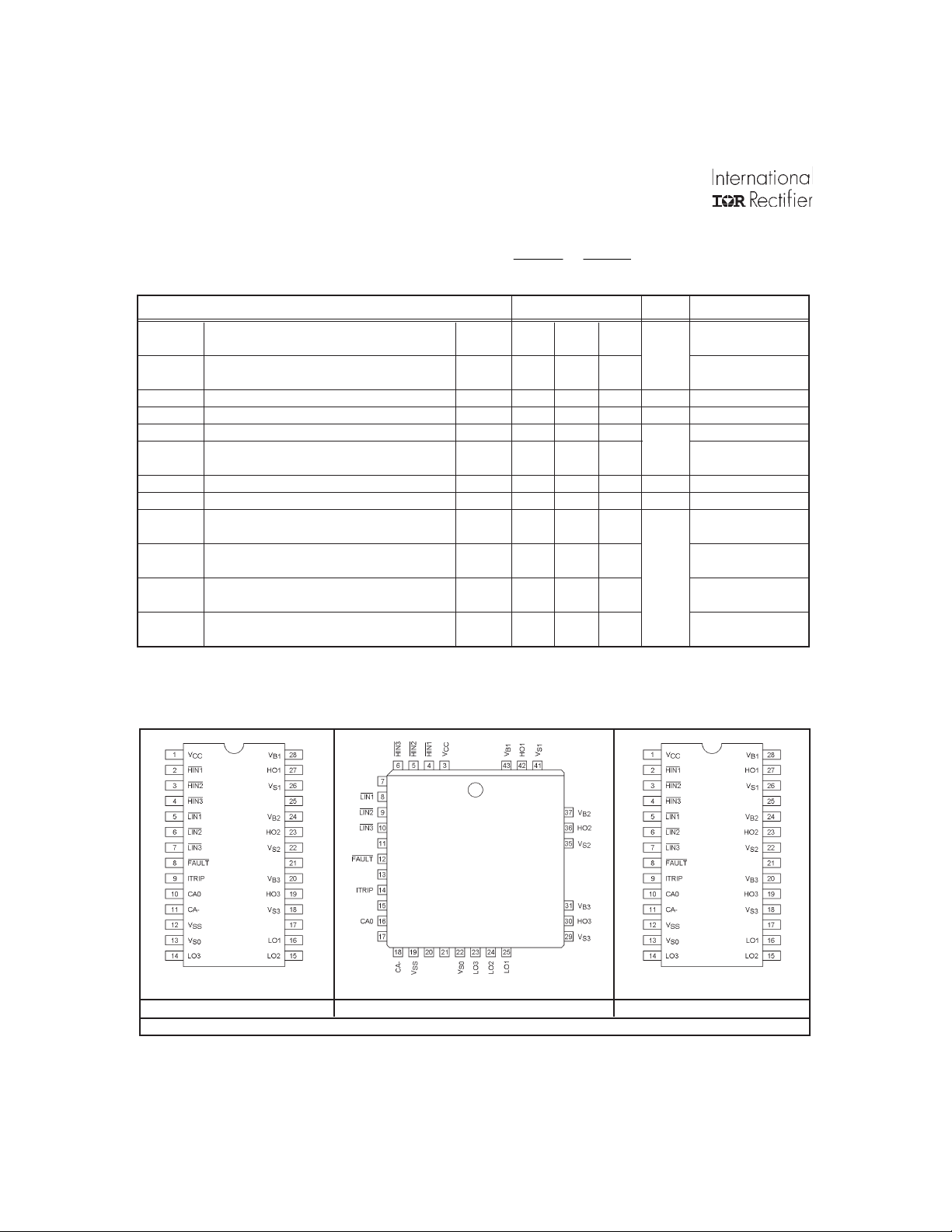

IR2130/IR2132(J)(S) & (PbF)

Static Electrical Characteristics -- Continued

V

(VCC, V

BIAS

are referenced to VSS and are applicable to all six logic input leads:

are referenced to V

Symbol Definition Figure Min. Typ. Max. Units Test Conditions

I

O+

I

O-

V

OS

I

CA-

CMRR Op. Amp. Common Mode Rejection Ratio 42 60 80 — VS0=V

PSRR Op. Amp. Power Supply Rejection Ratio 43 55 75 — VS0 = V

V

OH,AMP

V

OL,AMP

I

SRC,AMP

I

SRC,AMP

I

O+,AMP

I

O-,AMP

BS1,2,3

S0,1,2,3

) = 15V, V

and are applicable to the respective output leads: HO1,2,3 or LO1,2,3.

= VSS and TA = 25°C unless otherwise specified. The VIN, VTH and IIN parameters

S0,1,2,3

HIN1,2,3

&

LIN1,2,3

. The VO and IO parameters

Output High Short Circuit Pulsed Current 38 200 250 — VO = 0V, V

PW ≤ 10 µs

Output Low Short Circuit Pulsed Current 39 420 500 — VO = 15V, V

mA

PW ≤ 10 µs

Operational Amplifer Input Offset Voltage 40 — — 30 mV VS0 = V

CA- Input Bais Current 41 — — 4.0 nA V

dB

CA-

= 2.5V

CA-

=0.1V & 5V

CA-

CA-

VCC = 10V & 20V

Op. Amp. High Level Output Voltage 44 5.0 5.2 5.4 V V

Op. Amp. Low Level Output Voltage 45 — — 20 mV V

Op. Amp. Output Source Current 46 2.3 4.0 — V

Op. Amp. Output Sink Current 47 1.0 2.1 — V

mA

Operational Amplifier Output High Short 48 — 4. 5 6.5 V

Circuit Current V

Operational Amplifier Output Low Short 49 — 3 .2 5.2 V

Circuit Current V

= 0V, VS0 = 1V

CA-

= 1V, VS0 = 0V

CA-

= 0V, VS0 = 1V

CA-

V

CAO

= 1V, VS0 = 0V

CA-

V

CAO

= 0V, VS0 = 5V

CA-

CAO

= 5V, VS0 = 0V

CA-

CAO

IN

IN

= 0.2V

= 0.2V

= 4V

= 2V

= 0V

= 5V

= 0V

= 5V

Lead Assignments

28 Lead PDIP 44 Lead PLCC w/o 12 Leads 28 Lead SOIC (Wide Body)

IR2130 / IR2132 IR2130J / IR2132J IR2130S / IR2132S

Part Number

4 www.irf.com

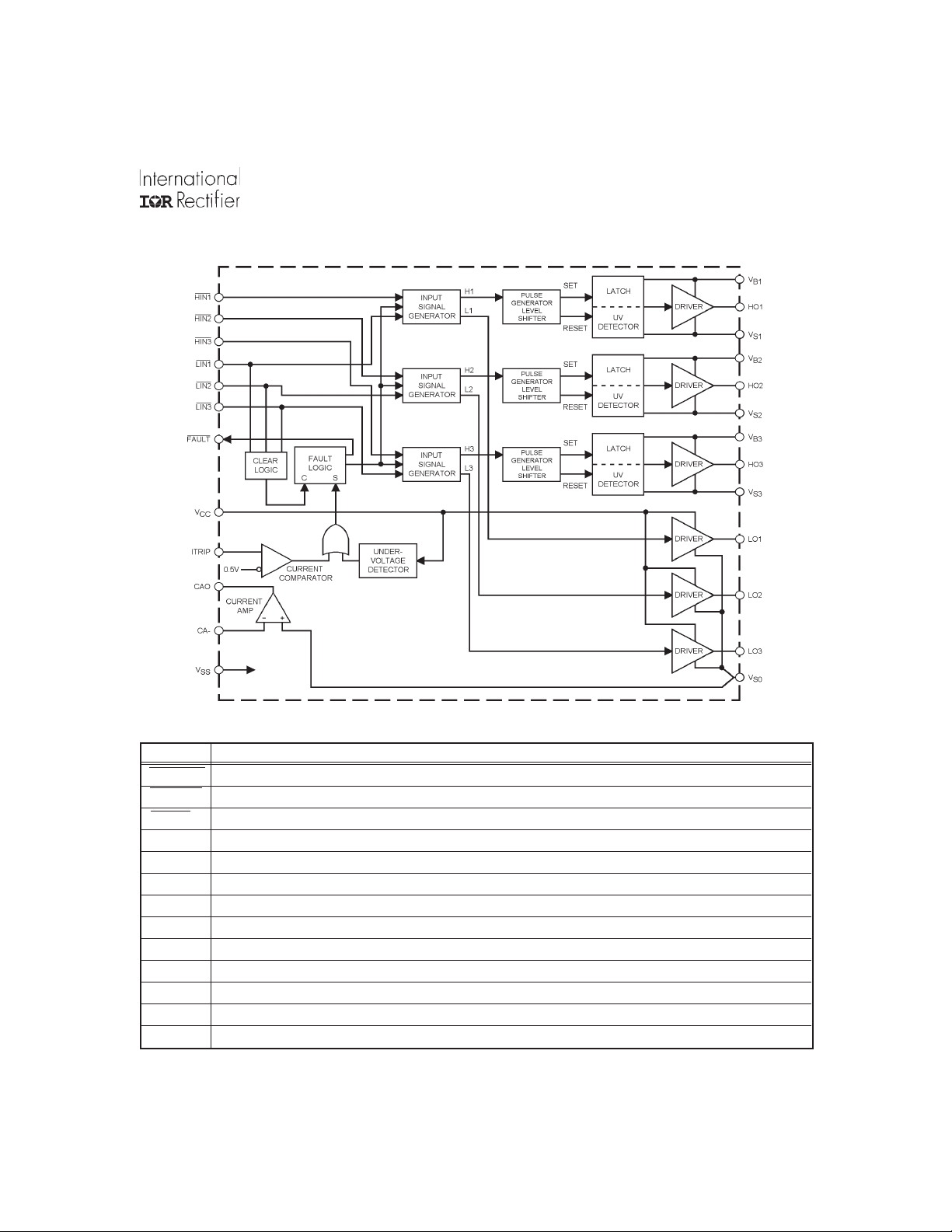

Functional Block Diagram

IR2130/IR2132(J)(S) & (PbF)

Lead Definitions

Symbol Description

HIN1,2,3 Logic inputs for high side gate driver outputs (HO1,2,3), out of phase

LIN1,2,3 Logic inputs for low side gate driver output (LO1,2,3), out of phase

FAULT Indicates over-current or undervoltage lockout (low side) has occurred, negative logic

V

CC

ITRIP Input for over-current shutdown

CAO Output of current amplifier

CA- Negative input of current amplifier

V

SS

V

B1,2,3

HO1,2,3 High side gate drive outputs

V

S1,2,3

LO1,2,3 Low side gate drive outputs

V

S0

www.irf.com 5

Low side and logic fixed supply

Logic ground

High side floating supplies

High side floating supply returns

Low side return and positive input of current amplifier

IR2130/IR2132(J)(S) & (PbF)

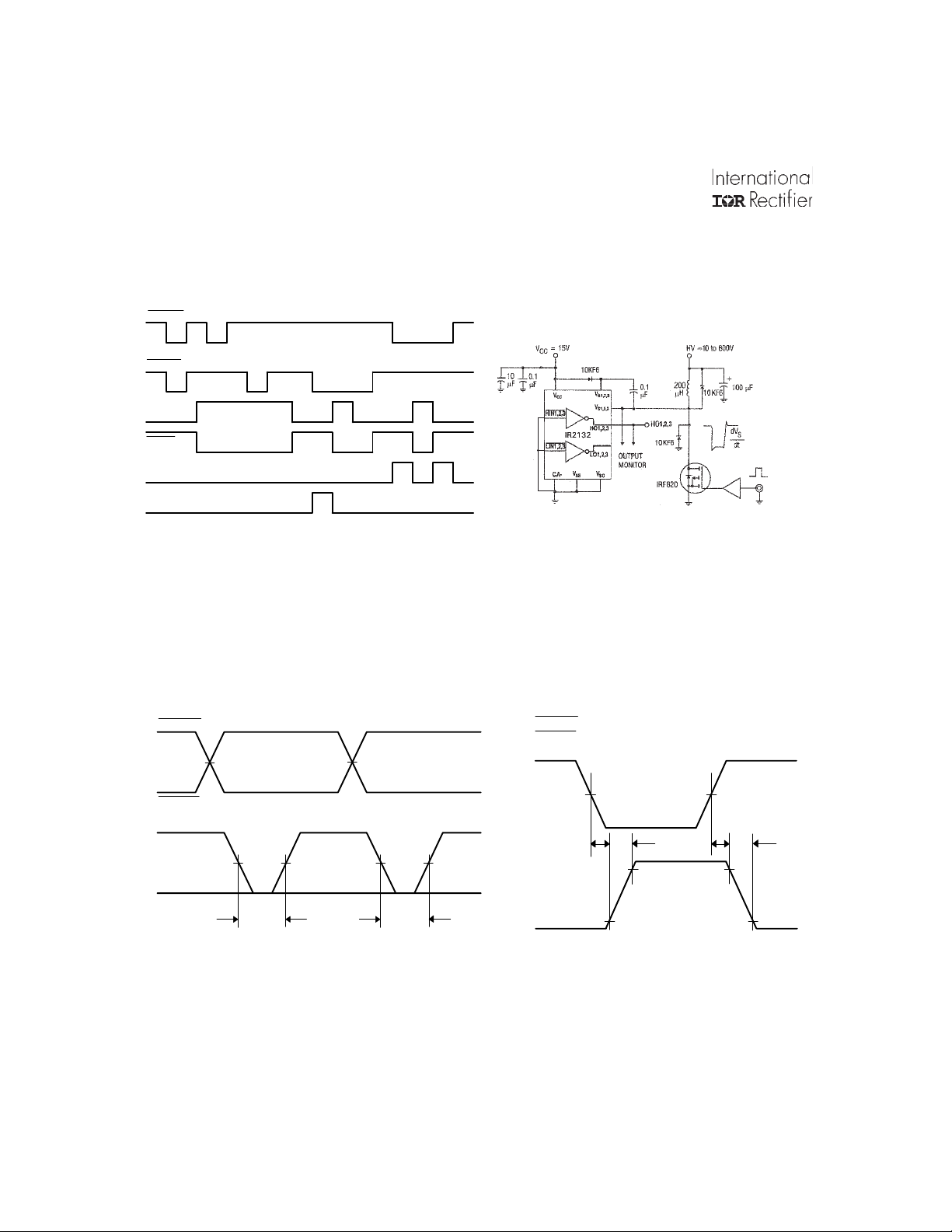

HIN1,2,3

LIN1,2,3

ITRIP

FAULT

HO1,2,3

LO1,2,3

Figure 1. Input/Output Timing Diagram Figure 2. Floating Supply Voltage Transient Test Circuit

<50 V/ns

HIN1,2,3

50% 50%

HIN1,2,3

LIN1,2,3

50% 50%

LIN1,2,3

LO1,2,3

HO1,2,3

50% 50%

DT DT

HO1,2,3

LO1,2,3

t

t

r

on

90% 90%

10% 10%

t

t

off

f

Figure 3. Deadtime Waveform Definitions Figure 4. Input/Output Switching Time Waveform

Definitions

6 www.irf.com

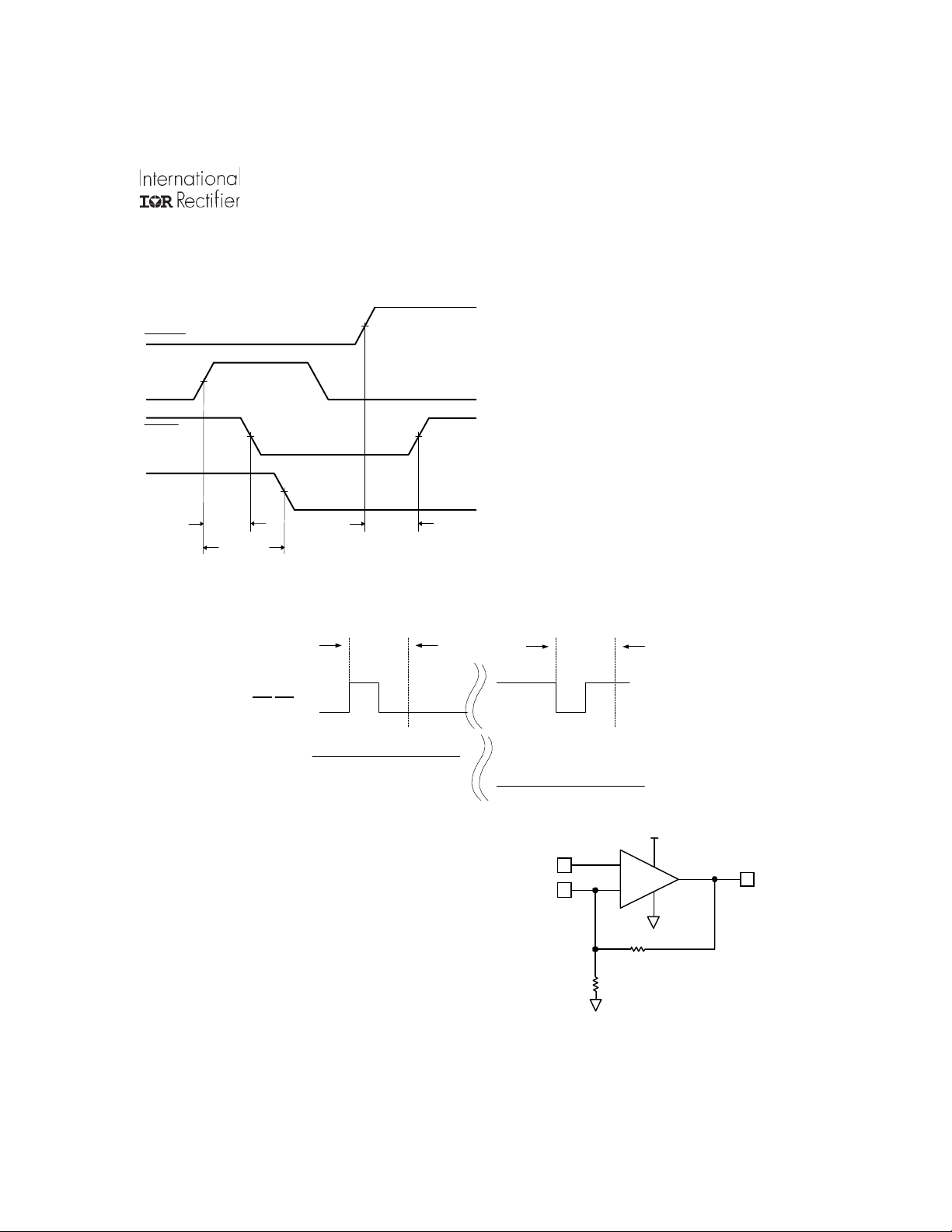

IR2130/IR2132(J)(S) & (PbF)

LIN1,2,3

ITRIP

FAULT

LO1,2,3

50%

50% 50%

50%

t

flt

t

itrip

50%

t

Figure 5. Overcurrent Shutdown Switching Time

Waveform Definitions

t

in,fil

HIN/LIN

on

high

HO/LO

fltclr

on on off

offoff

t

low

in,fil

U

Figure 5.5 Input Filter Function

V

S0

CA-

V

CC

+

V

SS

V

SS

CAO

Figure 6. Diagnostic Feedback Operational Amplifier Circuit

www.irf.com 7

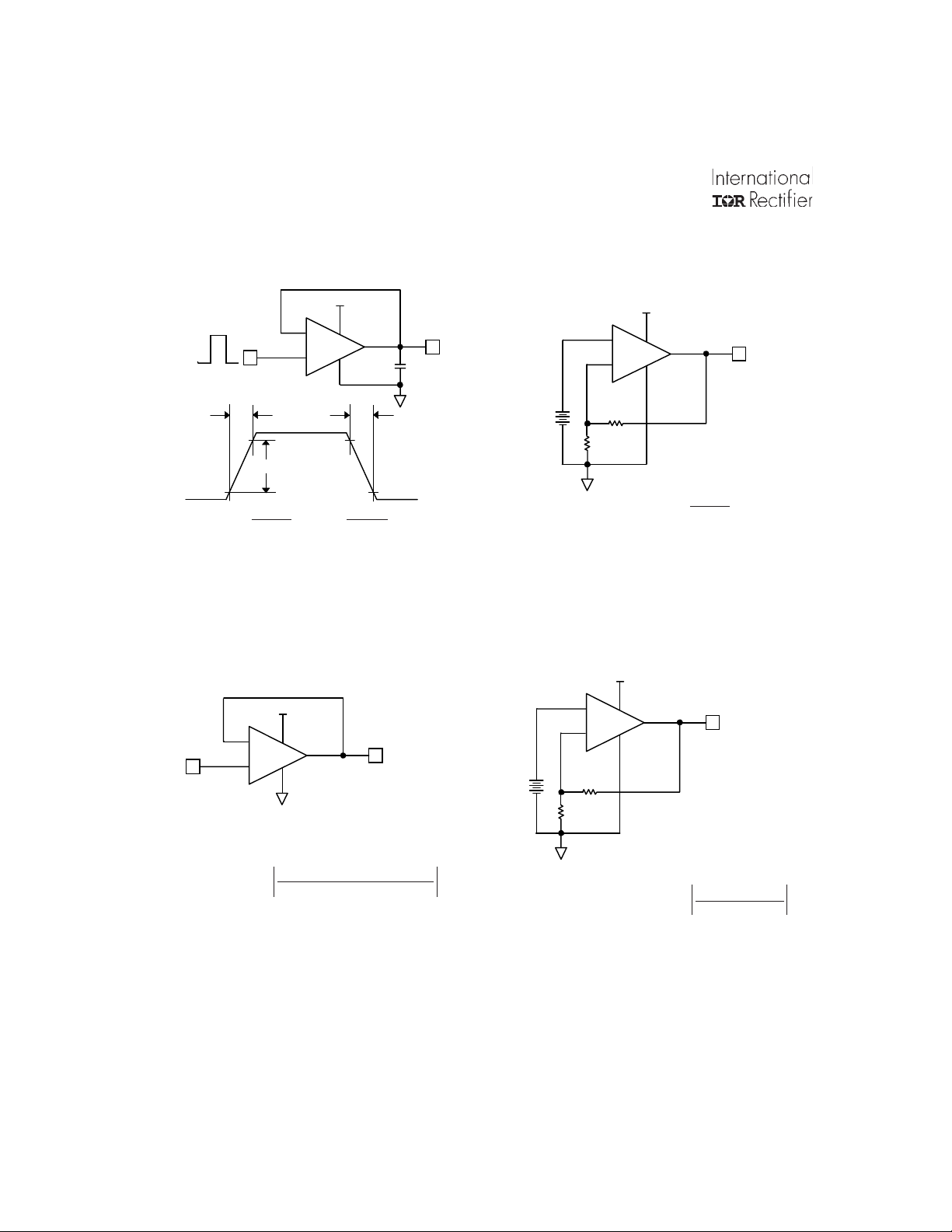

IR2130/IR2132(J)(S) & (PbF)

15V

V

3V

0V

3V

0V

SR+ =

CAV

S0

∆T1 ∆T2

90%

∆V

10%

∆V

∆T1

+

-

SR- =

V

CC

SS

∆V

∆T2

Figure 7. Operational Amplifier Slew Rate

Measurement

15V

V

CC

-

CA-

+

V

S0

Measure V

CAO1

V

CAO2

CMRR = -20*LOG

V

SS

at VS0 = 0.1V

at V

= 5V

S0

(V

-0.1V) - (V

CAO1

CAO2

4.9V

CAO

50 pF

-5V)

CAO

(dB)

15V

20k

V

CC

+

V

SS

V

VOS =

CAO

21

CAO

- 0.2V

0.2V

V

S0

CA-

+

1k

Figure 8. Operational Amplifier Input Offset Voltage

Measurement

V

CC

V

S0

0.2V

CA-

+

20k

1k

Measure V

PSRR = -20*LOG

+

V

SS

at VCC = 10V

CAO1

V

at V

CAO2

= 20V

CC

V

CAO1

(10V) (21)

CAO

- V

CAO2

Figure 9. Operational Amplifier Common Mode

Rejection Ratio Measurements

Figure 10. Operational Amplifier Power Supply

Rejection Ratio Measurements

8 www.irf.com

Loading...

Loading...