查询IR21093(S)供应商

Data Sheet No. PD60193

IR21093

(S)

HALF-BRIDGE DRIVER

Features

Floating channel designed for bootstrap operation

•

Fully operational to +600V

Tolerant to negative transient voltage

dV/dt immune

Gate drive supply range from 10 to 20V

•

Undervoltage lockout for both channels

•

3.3V, 5V and 15V input logic compatible

•

Cross-conduction prevention logic

•

Matched propagation delay for both channels

•

High side output in phase with IN input

•

Logic and power ground +/- 5V offset

•

Internal 540ns dead-time

•

Lower di/dt gate driver for better noise immunity

•

Description

The IR21093(S) are high voltage, high speed power

MOSFET and IGBT drivers with dependent high and

low side referenced output channels. Proprietary HVIC

and latch immune CMOS technologies enable ruggedized monolithic construction. The logic input is

compatible with standard CMOS or LSTTL output,

down to 3.3V logic. The output drivers feature a high

pulse current buffer stage designed for minimum driver cross-conduction. The floating channel can be used to

drive an N-channel power MOSFET or IGBT in the high side configuration which operates up to 600 volts.

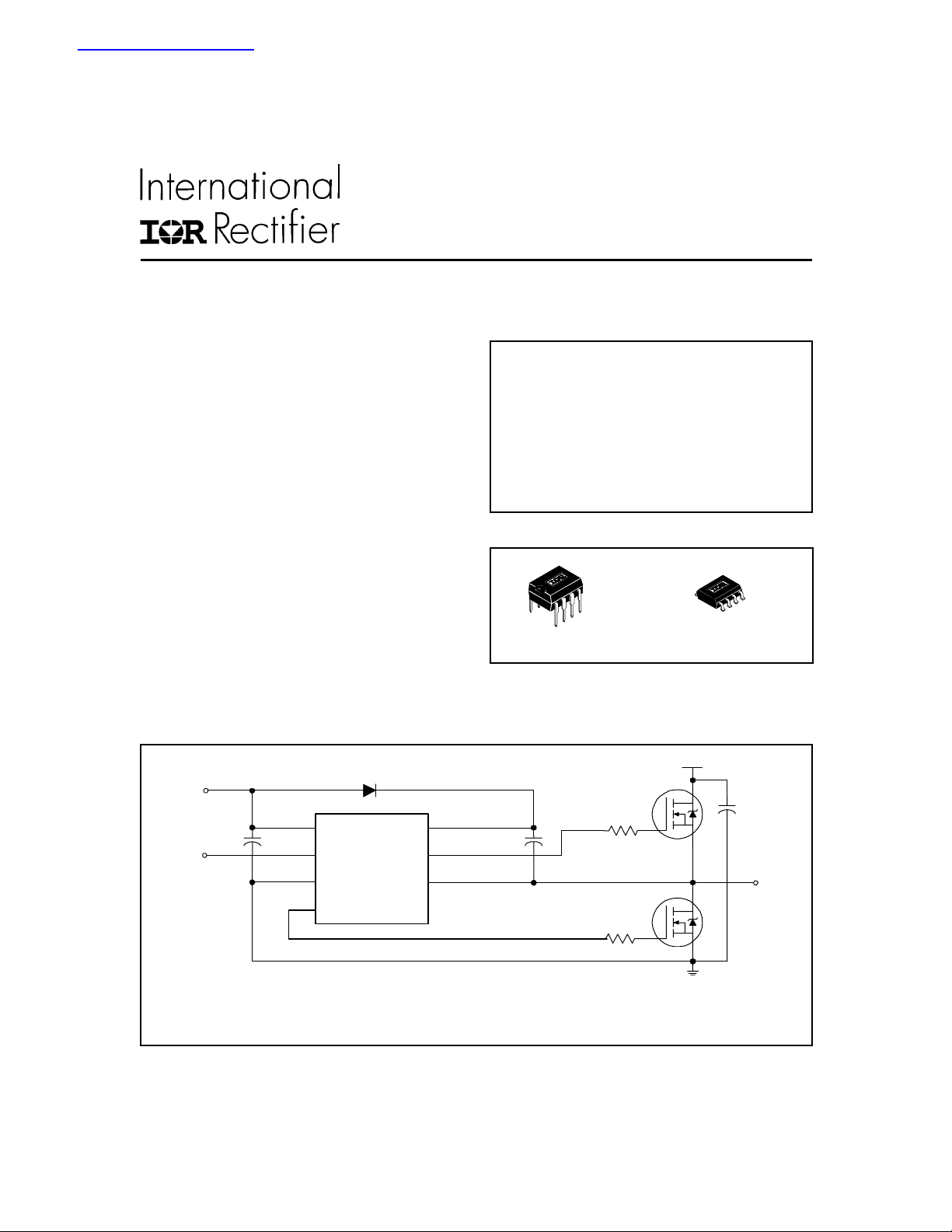

Product Summary

V

OFFSET

IO+/- 120 mA / 250 mA

V

OUT

t

(typ.) 750 & 200 ns

on/off

Dead Time 540 ns

600V max.

Packages

8-Lead PDIP

10 - 20V

8-Lead SOIC

Typical Connection

up to 600V

V

CC

V

CC

IN

(Refer to Lead Assignments for correct configuration). This/These diagr am(s) show electrical connections only. Please ref er to our

Application Notes and DesignTips for proper circuit board layout.

www.irf.com 1

IN

COM

LO

V

HO

V

B

TO

S

IR21093

LOAD

)

(

IR21093

S

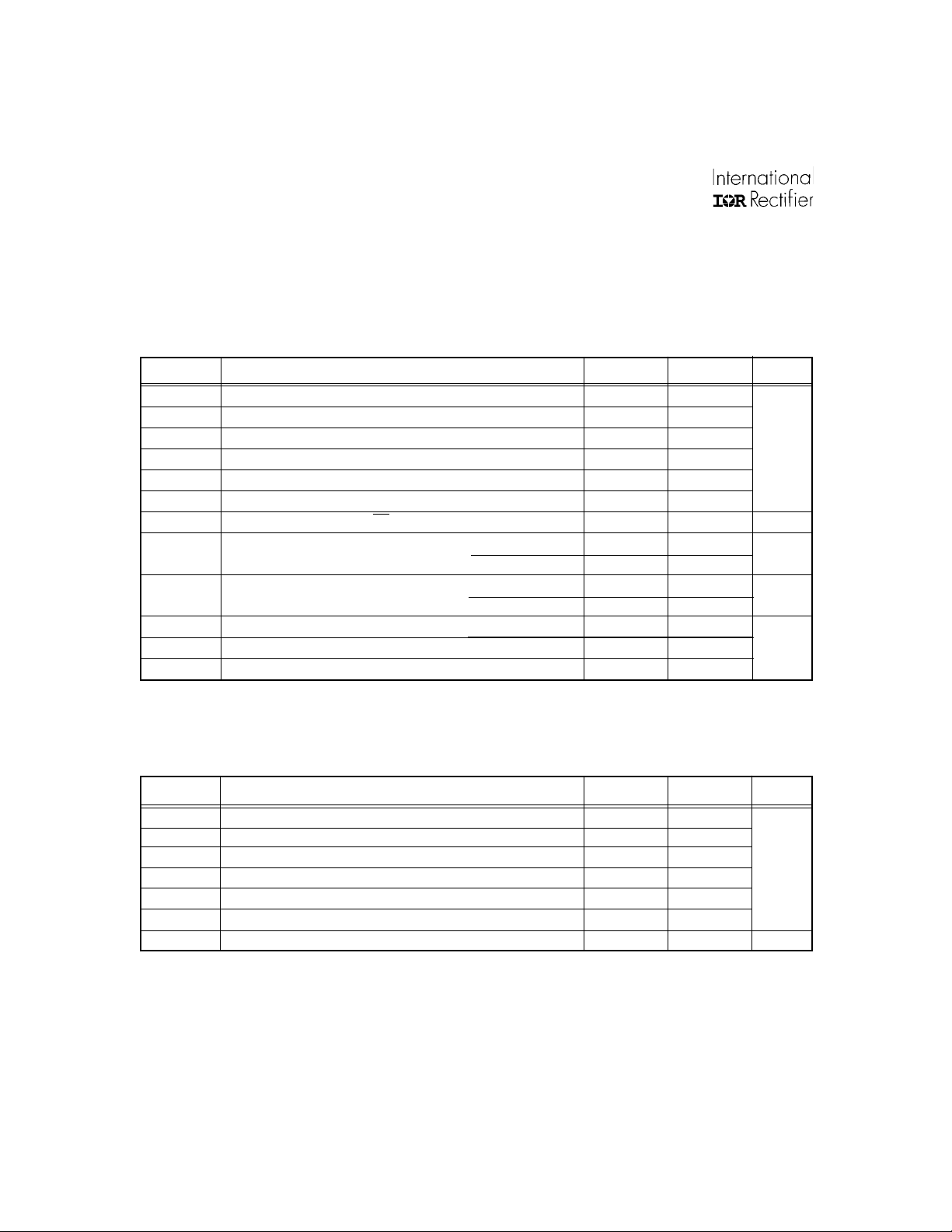

Absolute Maximum Ratings

Absolute maximum ratings indicate sustained limits beyond which damage to the device may occur. All voltage parameters are absolute voltages referenced to COM. The thermal resistance and power dissipation ratings are measured

under board mounted and still air conditions.

Symbol Definition Min. Max. Units

V

B

V

S

V

HO

V

CC

V

LO

V

IN

dVS/dt Allowable offset supply voltage transient — 50 V/ns

P

D

Rth

JA

T

J

T

S

T

L

High side floating absolute voltage -0.3 625

High side floating supply offset voltage VB - 25 VB + 0.3

High side floating output voltage VS - 0.3 V

Low side and logic fixed supply voltage -0.3 25

Low side output voltage -0.3 VCC + 0.3

Logic input voltage VSS - 0.3 V

Package power dissipation @ TA ≤ +25°C (8 Lead PDIP) — 1.0

(8 Lead SOIC) — 0.625

Thermal resistance, junction to ambient (8 Lead PDIP) — 125

(8 Lead SOIC) — 200

Junction temperature — 150

Storage temperature -50 150

Lead temperature (soldering, 10 seconds) — 300

CC

B

+ 0.3

+ 0.3

W

°C/W

°C

V

Recommended Operating Conditions

The input/output logic timing diagram is shown in figure 1. For proper operation the device should be used within the

recommended conditions. The VS offset rating is tested with all supplies biased at 15V differential.

Symbol Definition Min. Max. Units

VB High side floating supply absolute voltage VS + 10 VS + 20

V

S

V

HO

V

CC

V

LO

V

IN

T

A

Note 1: Logic operational for VS of -5 to +600V. Logic state held for VS of -5V to -VBS. (Please refer to the Design Tip

DT97-3 for more details).

2 www.irf.com

High side floating supply offset voltage Note 1 600

High side floating output voltage V

Low side and logic fixed supply voltage 10 20

Low side output voltage 0 V

Logic input voltage V

Ambient temperature -40 125 °C

S

SS

V

B

CC

V

CC

V

Loading...

Loading...