Page 1

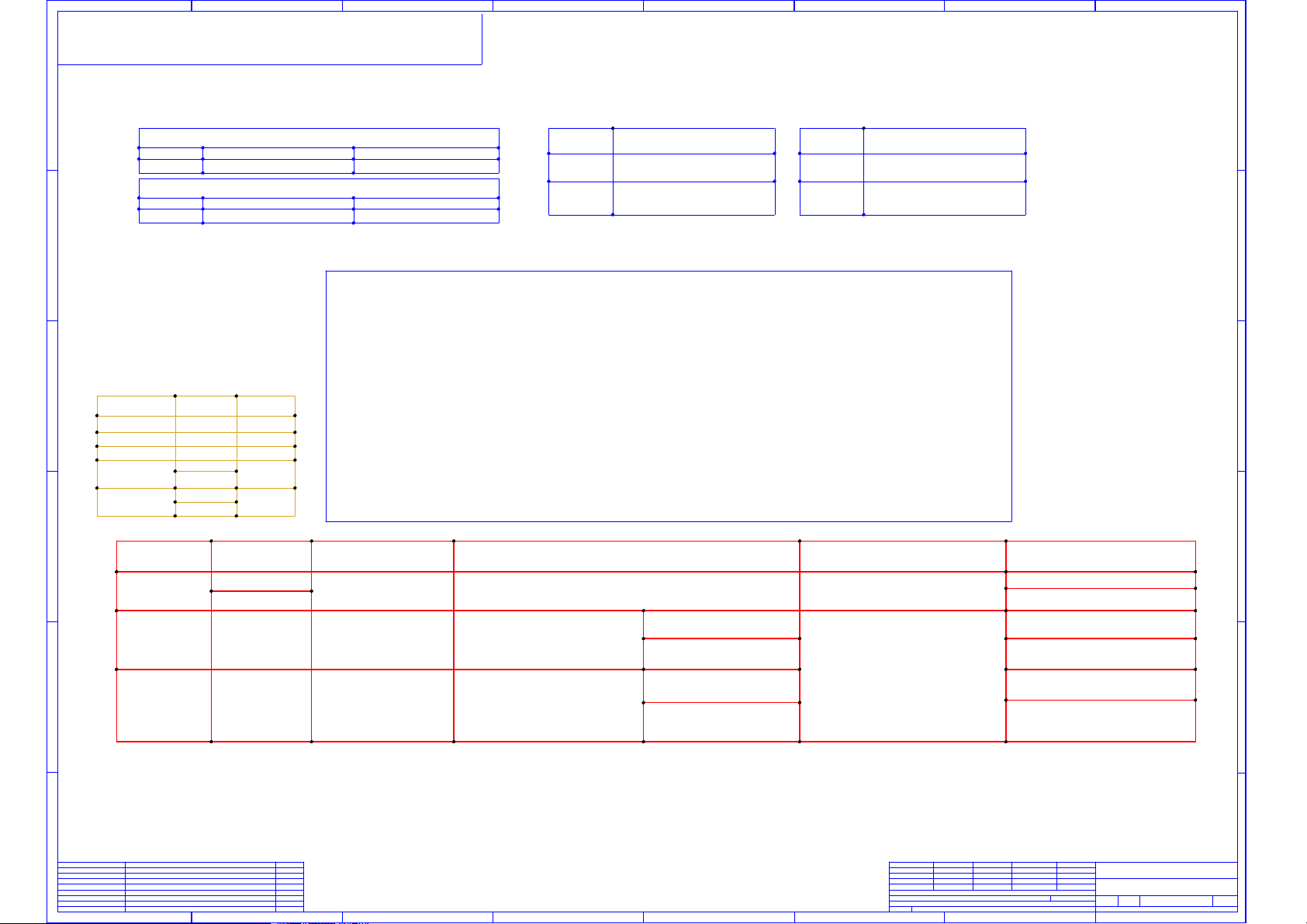

07dc0c1a02352f034a005270e0005460

THIS DRAWING AND SPECIFICATIONS,HEREIN,ARE THE PROPERTY OF INVENTEC

CORPORATION AND SHALL NOT BE REPODUCED,COPIED,OR USED IN WHOLE OR

IN PART AS THE BASIS FOR THE MANUFACTURE OR SALE OF ITEMS WITHOUT

WRITTEN PERMISSION,INVENTEC CORPORATION, ALL RIGHT RESERVED.

8

7 6 5 4 3 2 1

HSF Property:ROHS or Halogen-Free

E

D

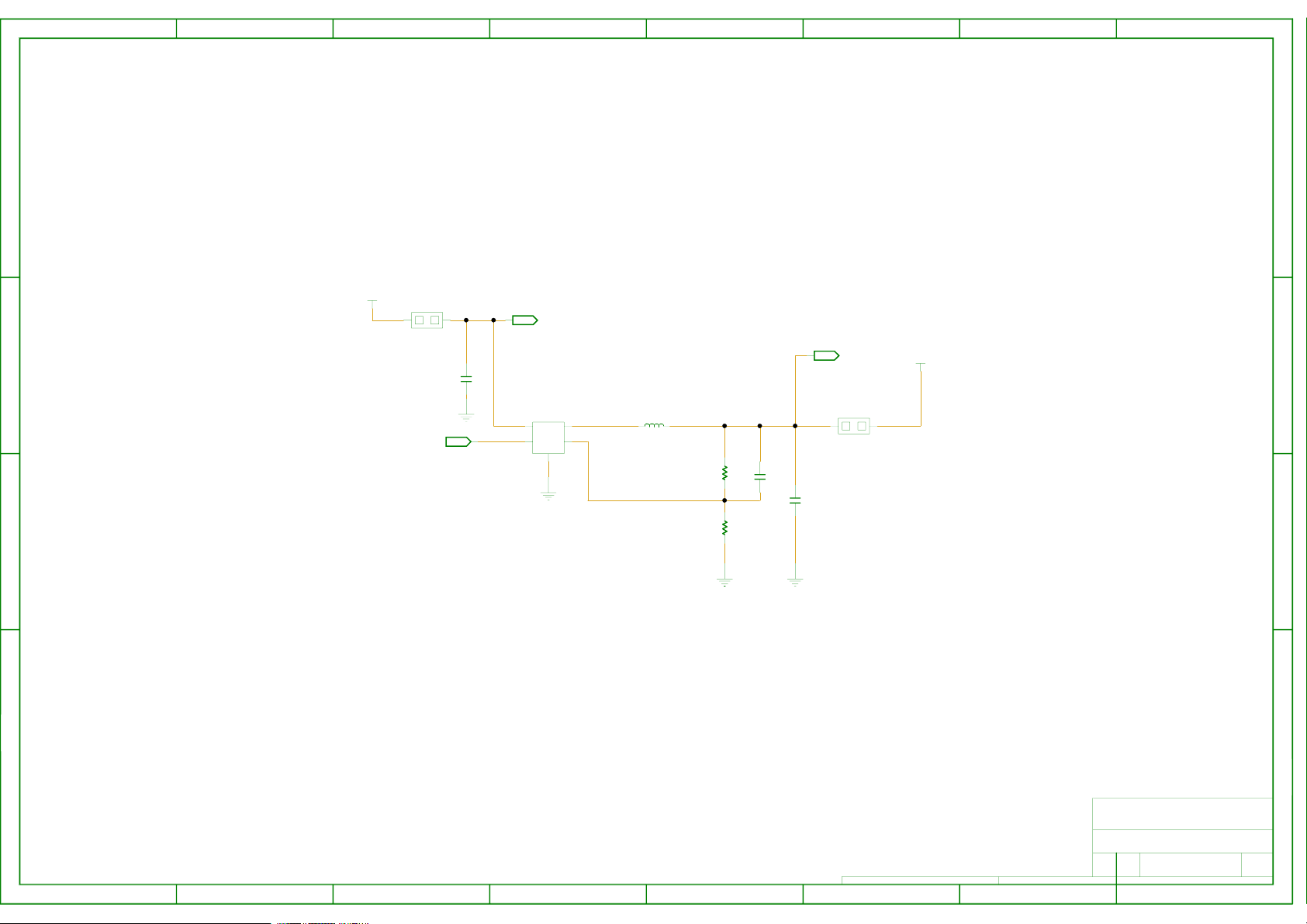

U800

USB BOARD (6L)

USB BOARD (8L)

POWER BOARD (6L)

POWER BOARD (8L)

EMI BOARD (6L)

EMI BOARD (8L)

R5279

R5279 HYNIX:6019B0971701 6013A0088503

R5061

R5061

CN6050

SAMSUNG:6019B0971801

SAMSUNG:6019B1033601

MICRON:6019B1033501

IS NOT P/N

GT

GV2

6013A0017501

6013A0107901

6013A0017501

15SBGV2

1310A2548501

1310A2548601

1310A2548701

1310A2548801

1310A2552101

1310A2552102

1310A2552201

1310A2552202

6050A2548501

6050A2548601

6050A2548701

6050A2548801

6050A2552101

6050A2552201

SHARK BAY PGA

MOUNT

DEL

DIS SKU

R4834

R307

R4832

R309

UMA SKU

MOUNT

DEL

R4819

R7496

R4636

PV BUILD

2012.12.25

R4638

FF

R4639

E

D

C

Platform

CPU

GPU

37W (Quad)

UMA

DIS

B

A

21-OCT-2002

07dc0c1a02352f034a005270e0005460

DATE CHANGE NO.

DIS

8

47W (Quad)

37W (Quad)

47W (Quad)

A03

MV

MV

A02

A01

PV

AX2

SI2

AX1

SI

DB2

X02

X01

DB2012-5-22

7 6 5 4 3

N14P-GV2 23*23 (25W)

N14P-GV2 23*23 (25W)

REV

NA

VRAM

NA

128Mx16 DDR3 8pcs (2G)

128Mx16 DDR3 8pcs (2G)

Samsung K4W2G1646E-BC1A (E-die)

HP P/N: 601498-955

IEC P/N: 6019B1033601

Micron MT41J128M16JT-093G:K

HP P/N: 601498-654

IEC P/N: 6019B1033601

Samsung K4W2G1646E-BC1A (E-die)

HP P/N: 601498-955

IEC P/N: 6019B1033601

Micron MT41J128M16JT-093G:K

HP P/N: 601498-654

IEC P/N: 6019B1033601

PCB count

6050A2547701(6L)

6050A2548101 (8L)

DRAWER

DESIGN

CHECK

RESPONSIBLE

SIZE=

FILE NAME:

P/N

IEC P/N

C

1310A2547701

1310A2547702

1310A2548101

1310A2548102

1310A2548105

B

1310A2548106

A

POWER

DATEDATEEE

XXX

VER:

2

INVENTEC

TITLE

MODEL,PROJECT,FUNCTION

CODE

SIZE

C

CS

SHEET

Main Board

DOC.NUMBER REV

1310xxxxx-0-0

1

1

A01

of

70

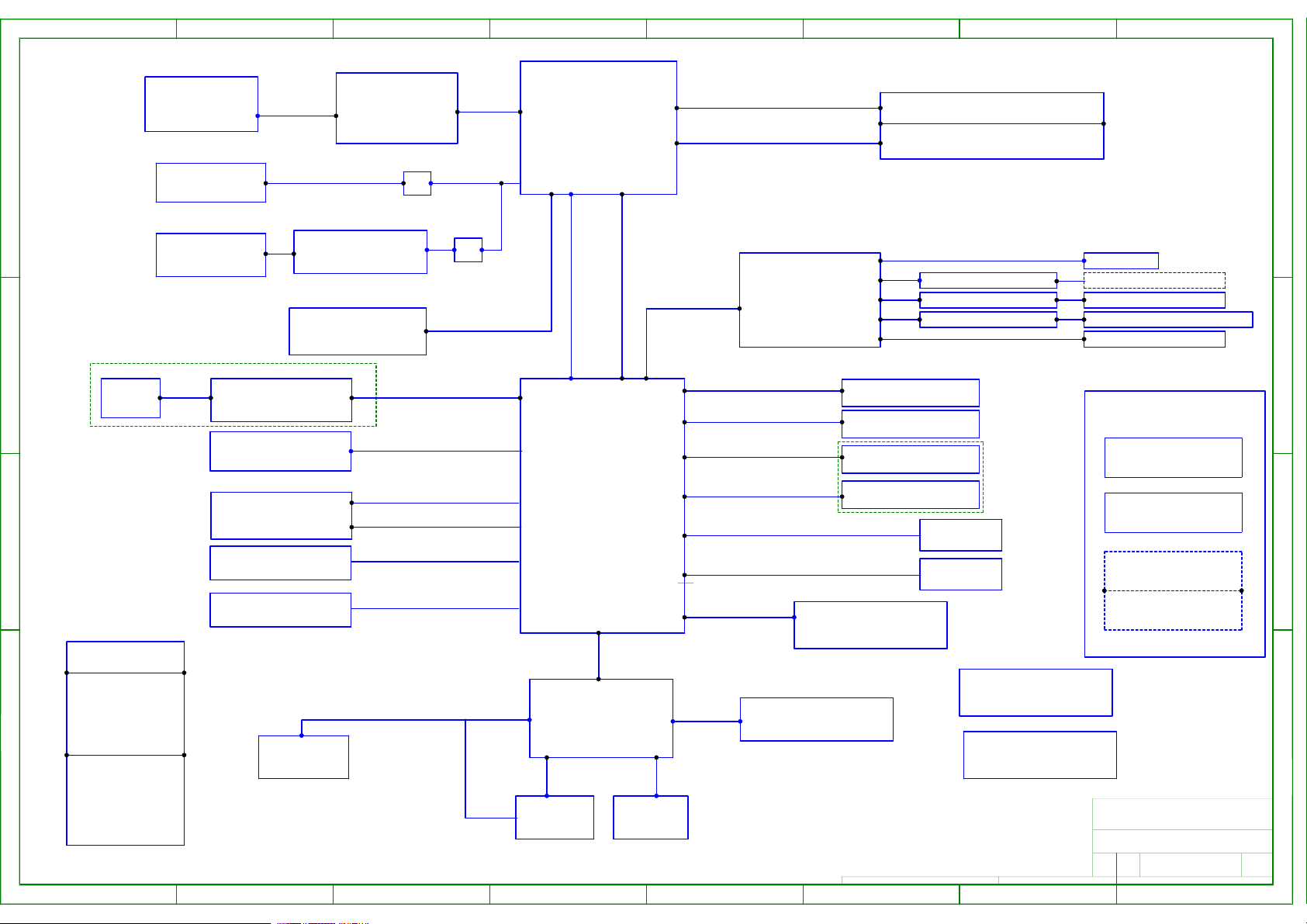

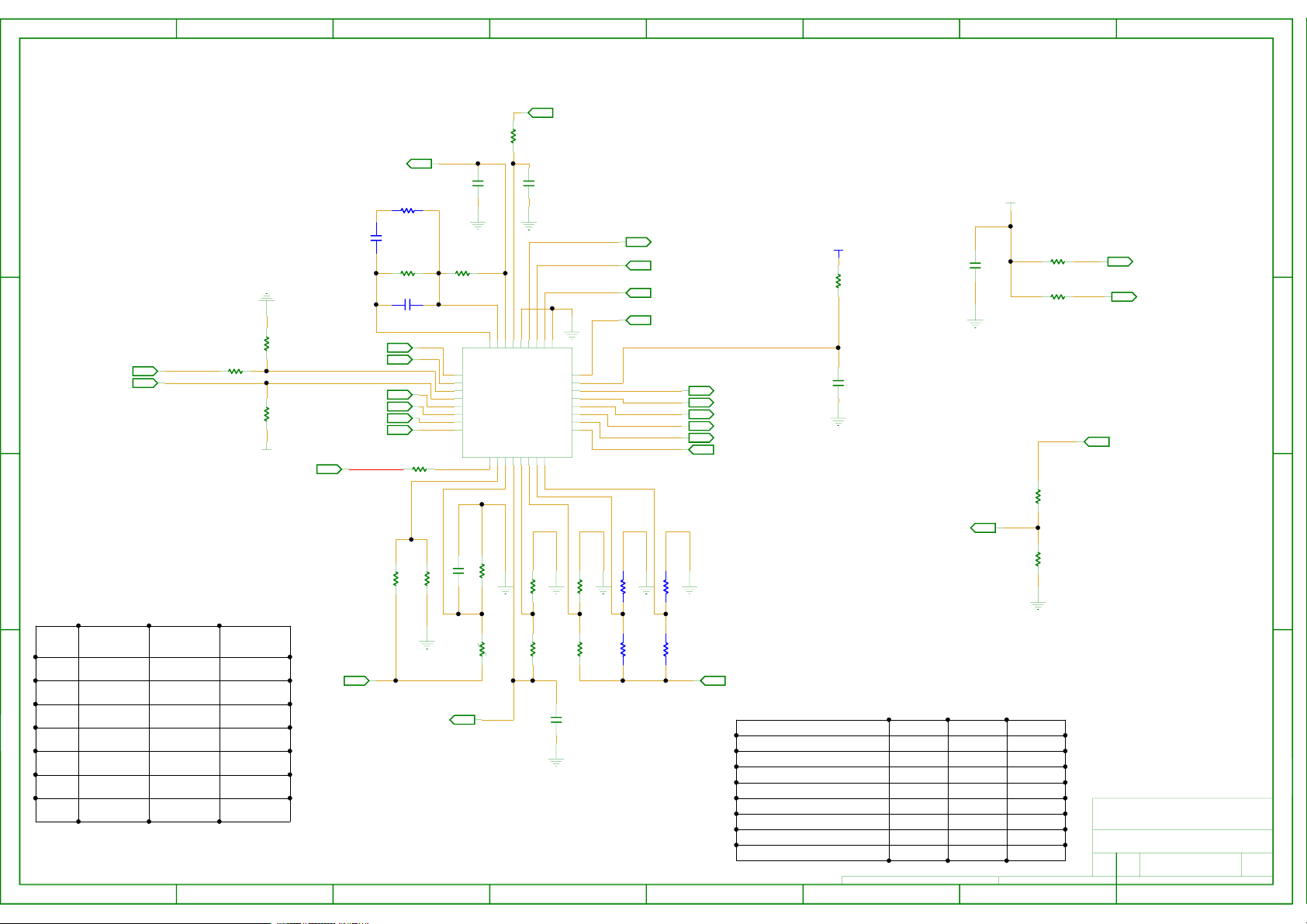

Page 2

07dc0c1a02352f034a005270e0005460

8 7

6 5

PAGE INDEX

4

3 2 1

D

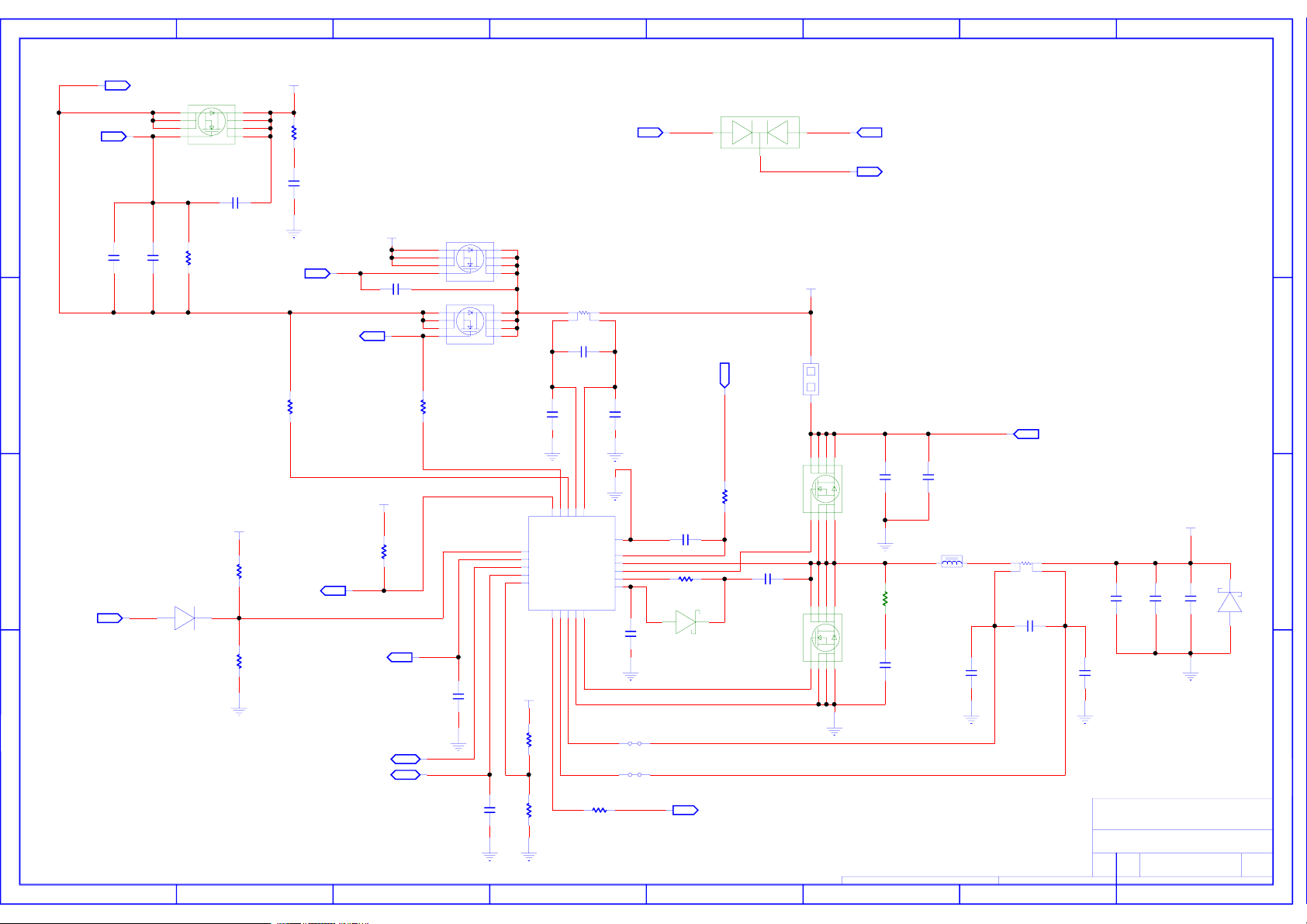

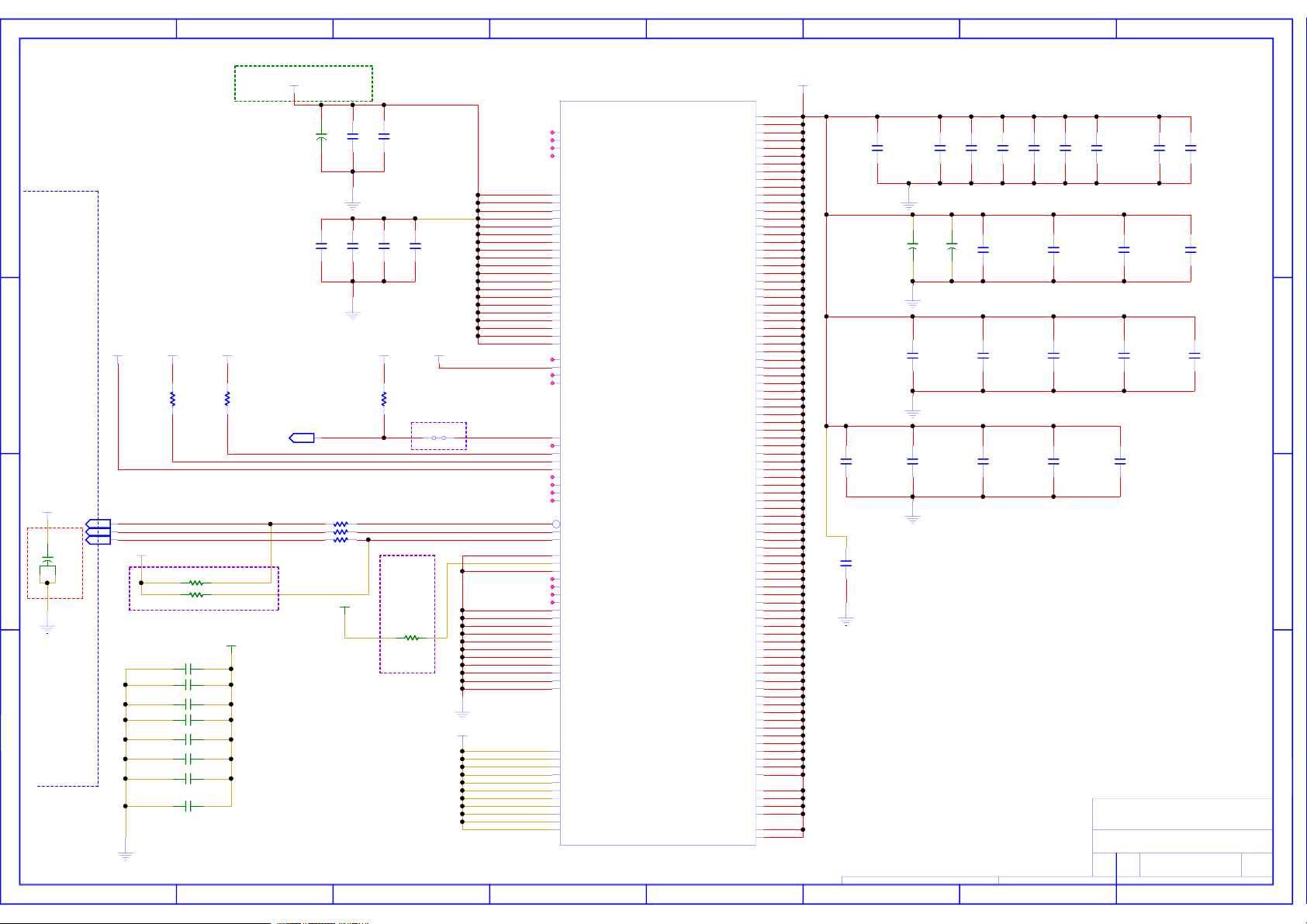

01 PCH-326Project Name

Page Index PCH-42702

PCH-5

Block Diagram

03

Power Procedure

04

Seletor

05

06

Charger

07

P3v3_P5v0

08

Pvddq

09

P1v05s_PCH

P1v5s_PCH

10

PVCORE-1

11

PVCORE-2

12

Power Switch

13

Enable Pin

14

Thermal & Fan

15

CPU-1

B

16

17

18

CPU-2

CPU-3

CPU-419

20

CPU-5

21 CPU-6

DDR3L-1

22

DDR3L-2

23

PCH-124

PCH-2

25

28

PCH-6

29

30

PCH-7

31

PCH-8

PCH-9

32

33

PCH-10

34

EC ITE8527

35

KB & LED

36

EDP2LVDS

37

LCM CONN

38

HDMI

39

SATA HDD&mSATA

CARD READER

40

AUDIO-1

41

AUDIO-2

42

AUDIO-3

43

WLAN

44

Finger Printer

45

46

MB to DB CONN&Screw

47

G-SENSOR

48

USB3.0 CONN

AUB_BLANK49

AUB_USB30-1

50

51

AUB_USB30-2

52

LAN RTL8161GSH-CG

53

Transformer & RJ45

54

COMBOJACK&MB to AUB CONN

55

DB Board

56

ESD BOARD

57

EMI CAP

58

N14P-GV2

59

GPU-1

60

GPU-2

61

GPU-3

62

GPU-4

63

GPU-5

VRAM DDR3-1

64

65

VRAM DDR3-2

66

PVCORE_DGPU

67

P1V5S_DGPU

68

DGPU_LOAD SWITCH

69

POWER SEQUENCE 1

POWER SEQUENCE 2

70

D

CC

B

AA

8

07dc0c1a02352f034a005270e0005460

7 6

5 4

CHANGE by

XXX

DATE

21-OCT-2002

23

INVENTEC

TITLE

MODEL,PROJECT,FUNCTION

INDEX

DOC.NUMBER

CODE

SIZE

A3

CS

1310xxxxx-0-0

SHEET

2

of

70

1

REV

A01

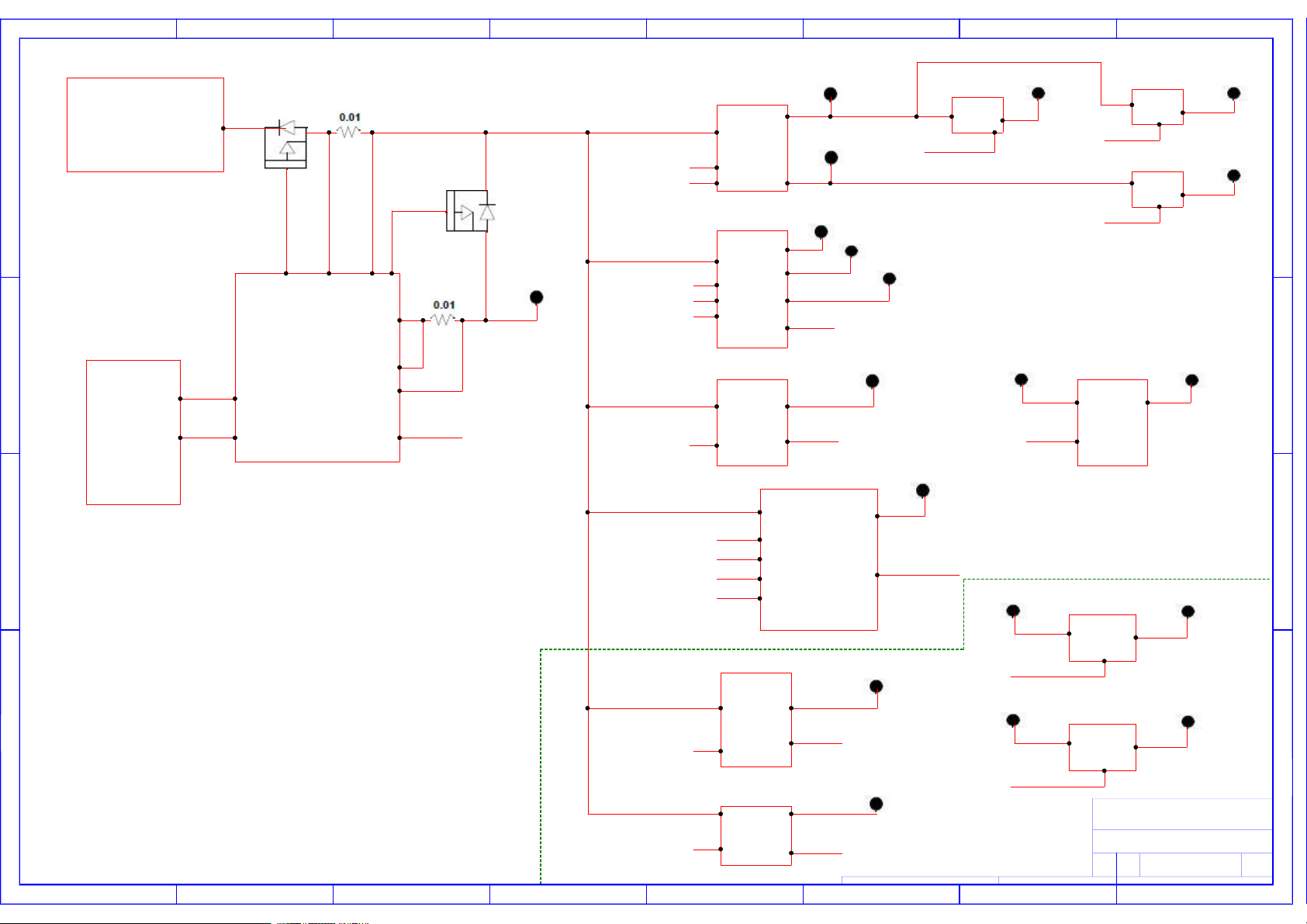

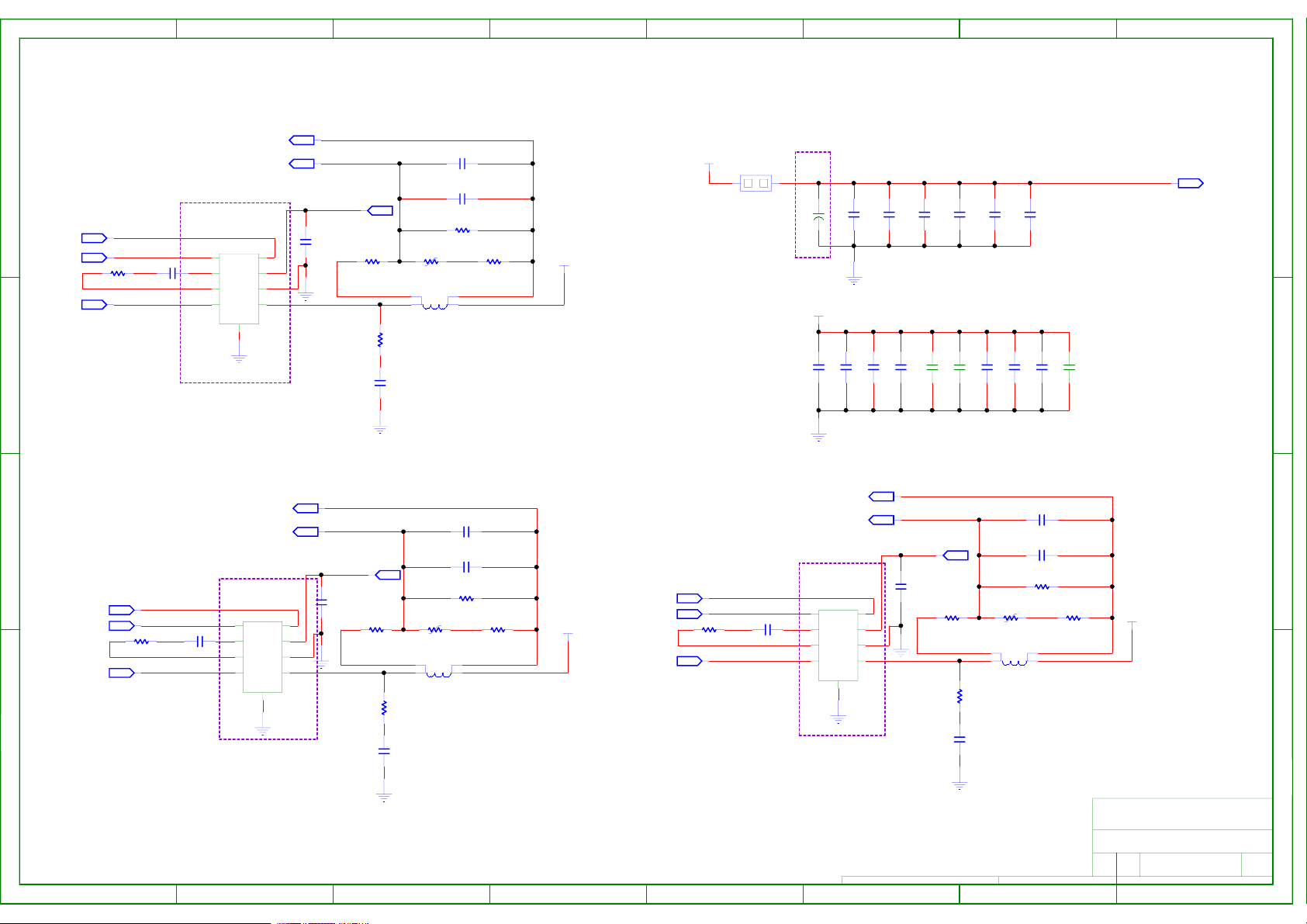

Page 3

07dc0c1a02352f034a005270e0005460

8 7

6 5

4

3 2 1

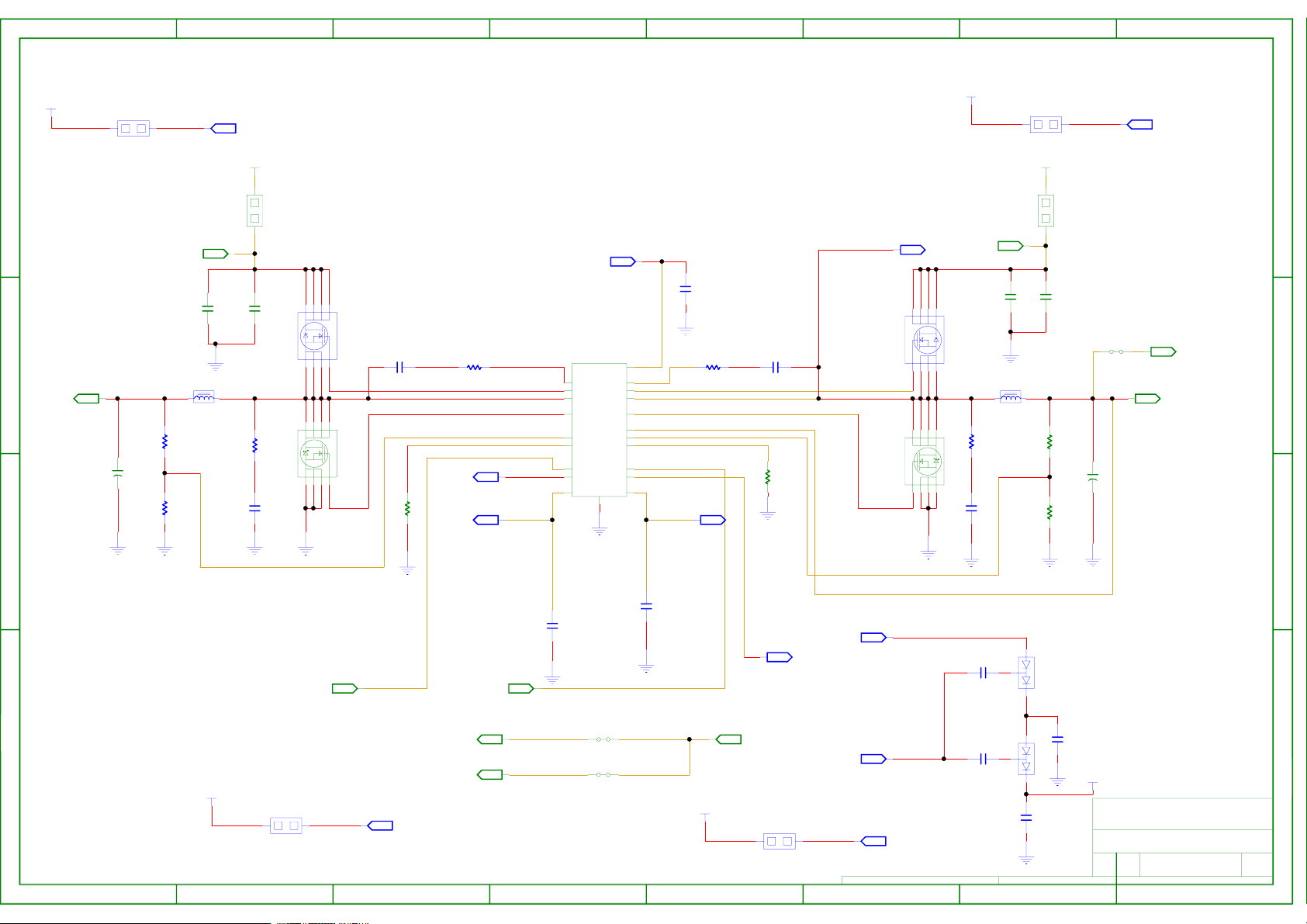

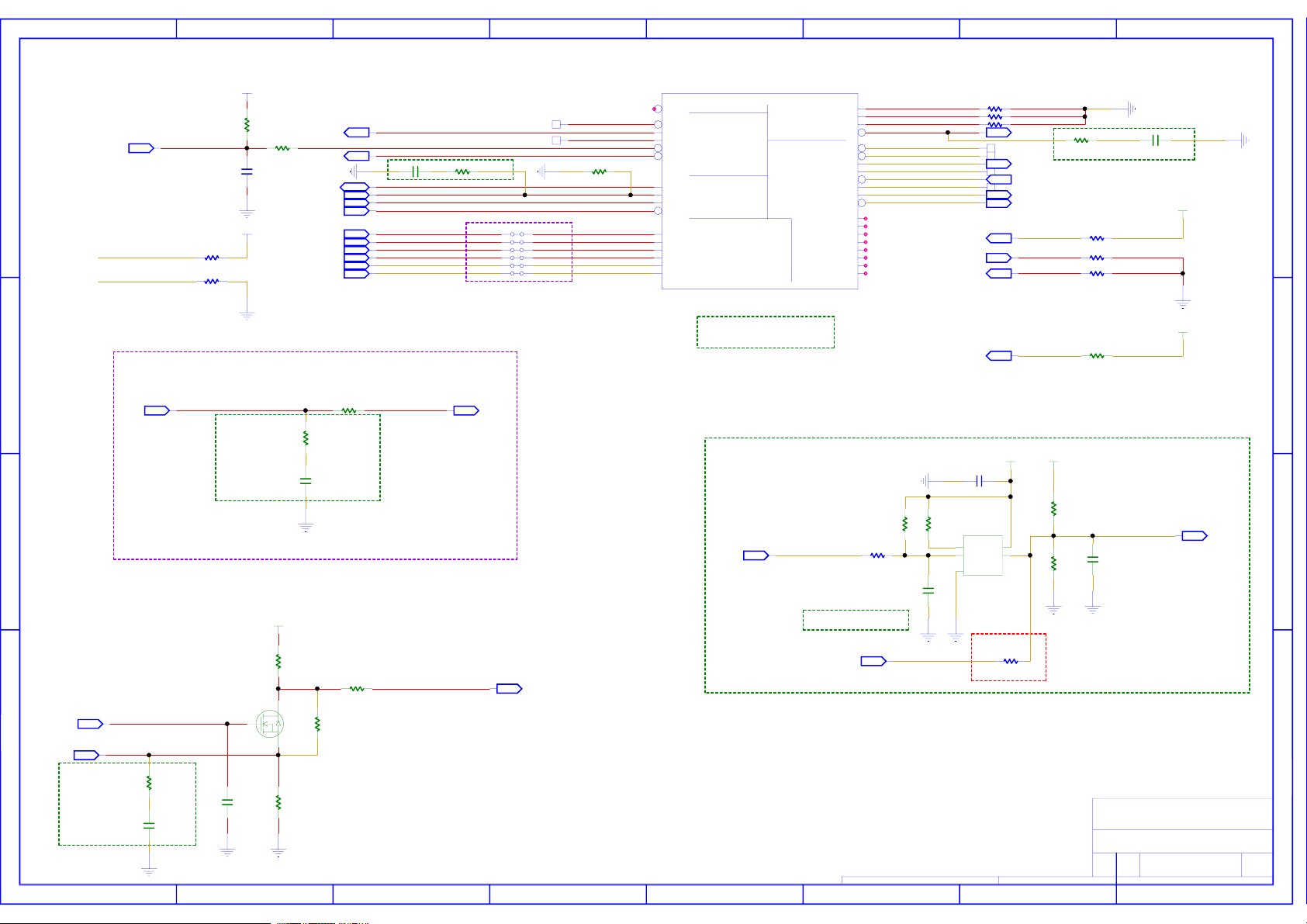

gDDR3

128M x 16 x 8PCS

P64~P65

D

EDP

PANEL 15.6

P59~P63

P37

LVDS

PANEL 15.6

P37

eDP TO LVDS

RTD2136S

P36

HDMI 1.4a

P38

Daughter Board

RJ45

P53

B

MB to DB Conn

PWR Button Conn

USB3.0 x2

NIC

HP/MIC Combo Jack

P46

KB Backlight

P35

8

07dc0c1a02352f034a005270e0005460

REALTEK

RTL8151

GSH-CG

P52

CARD READER

REALTEK

RTS5237

P40

WIFI+BT3.0

P44

P37

Intel

WEBCAM

FINGER PRINTER

P45

G-SENSOR

ST HP3DC2

P47

7 6

NVIDIA

N14P-GV2

R

PCIE_7

PCIE_4

PCIE_3

USB2.0_3

USB2.0_8

USB2.0_7

PEGX8

EDP

R

TMDS

SMBUS

CPU

INTEL HASWELL-M

r-PGA

SV

37W/47W

P16~P21

FDI

DMI 2.0

PCH

LYNX POINT 3W

HM87

P24~33

LPC

EC

ITE_ITE8527

P34

PS2

Synaptics

P46

5 4

KEYBOARDTOUCH PAD

Sunrex

P35

CHANNEL A

CHANNEL B

AUDIO CODEC

HDA

IDT 92HD99

P41

USB3.0 PORT1/2.0 PORT0

USB3.0 PORT2/2.0 PORT1

USB3.0 PORT3/2.0 PORT2

USB3.0 PORT4/2.0 PORT3

SATA PORT 0

SATA PORT 1

EC_SPI

PCH_SPI

SPI FLASH 512KB

P34

SPI FLASH 8MB

P25

DDR3L 1.35V

1067/1333/1600 MHZ

DDR3L 1.35V

1067/1333/1600 MHZ

P42

P43

P43

USB 3.0 PORTS

P48

USB 3.0 PORTS

P48

USB 3.0 PORTS

Daughter Board

P50

USB 3.0 PORTS

Daughter Board

P51

P39

P39

CHANGE by

XXX

H=8

H=4

TPA6130A2RTJR

TPA2012D2RTJR

TPA3111D1

(Charger port)

(Debug port)

HDD

M-SATA

ESD Board x 2

P56

Power Button Board

P55

DATE

21-OCT-2002

23

P22

P23

DMIC

P37

Daughter Board

HP / MIC COMBO

REAR SPEAKER

SUBWOOFER SPEAKER

FRONT SPEAKER

DB Board

HP/MIC

Combo Jacker

NIC+RJ45

USB3.0 x 2

USB3.0 REDRIVER

TI SN65LVPE502A

P50~P55

INVENTEC

TITLE

MODEL,PROJECT,FUNCTION

Block Diagram

DOC.NUMBER

CODE

SIZE

A3

CS

1310xxxxx-0-0

SHEET

3

of

D

P54

P43

P43

P41

CC

B

AA

REV

A01

70

1

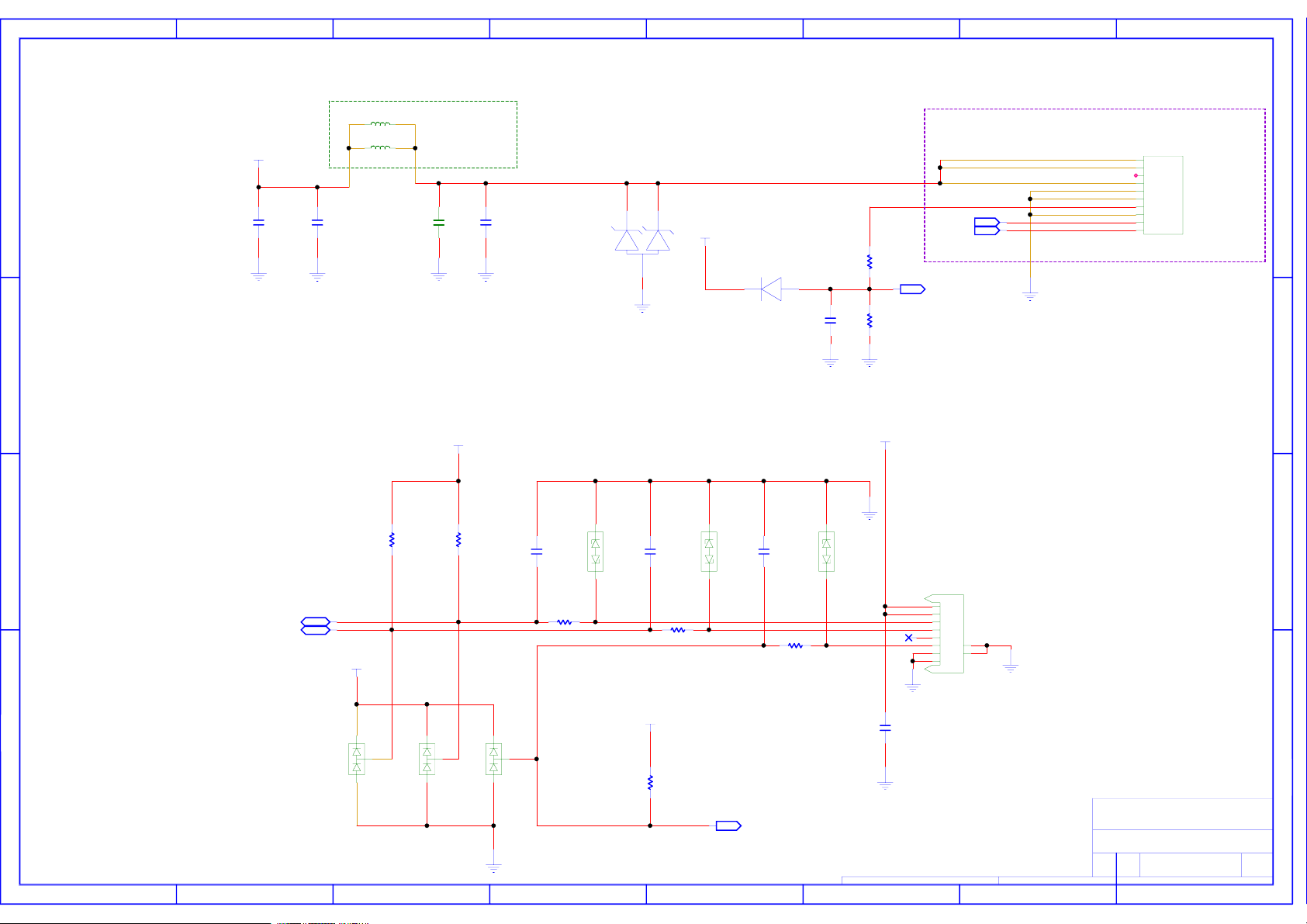

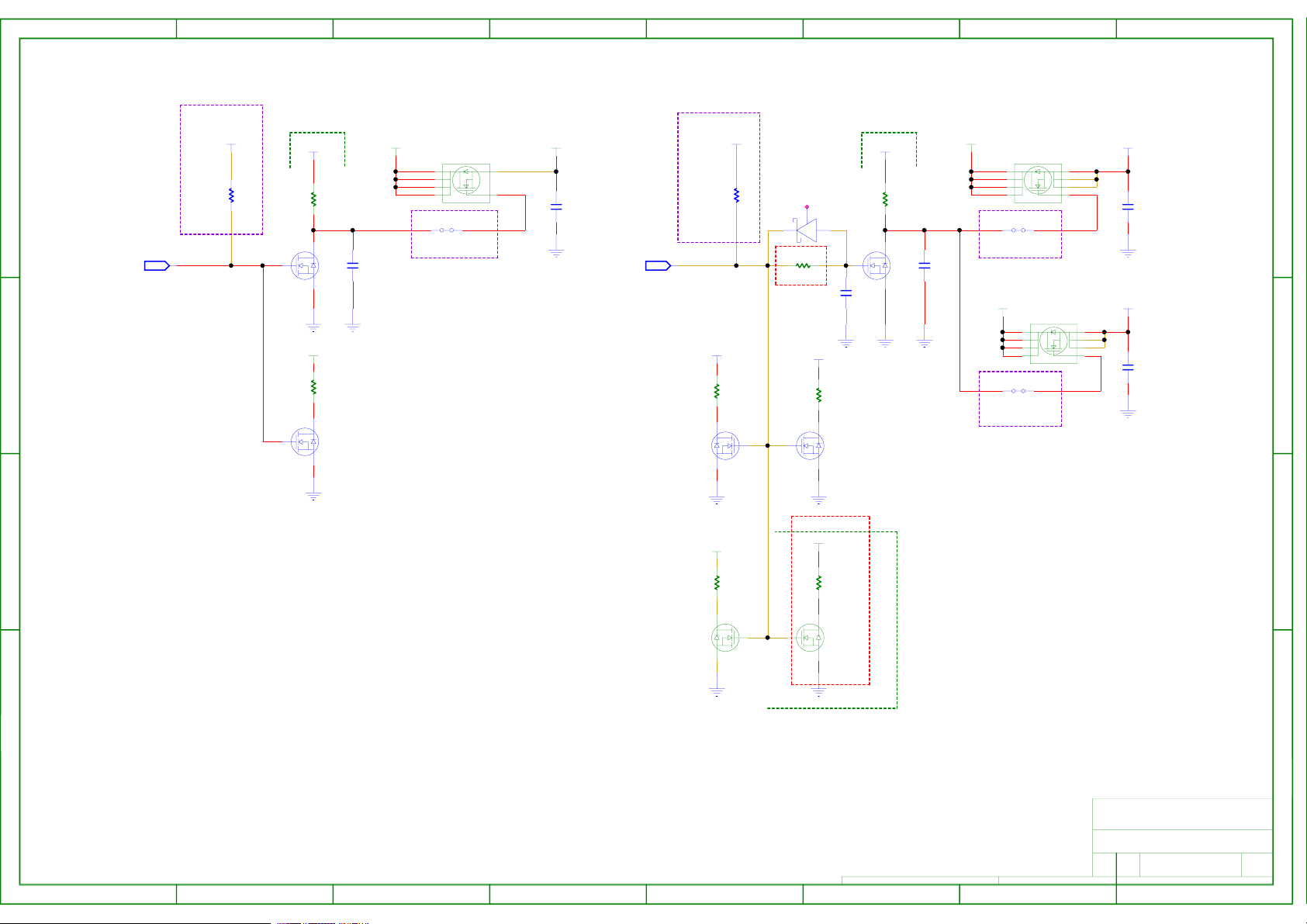

Page 4

07dc0c1a02352f034a005270e0005460

8 7

6 5

4

3 2 1

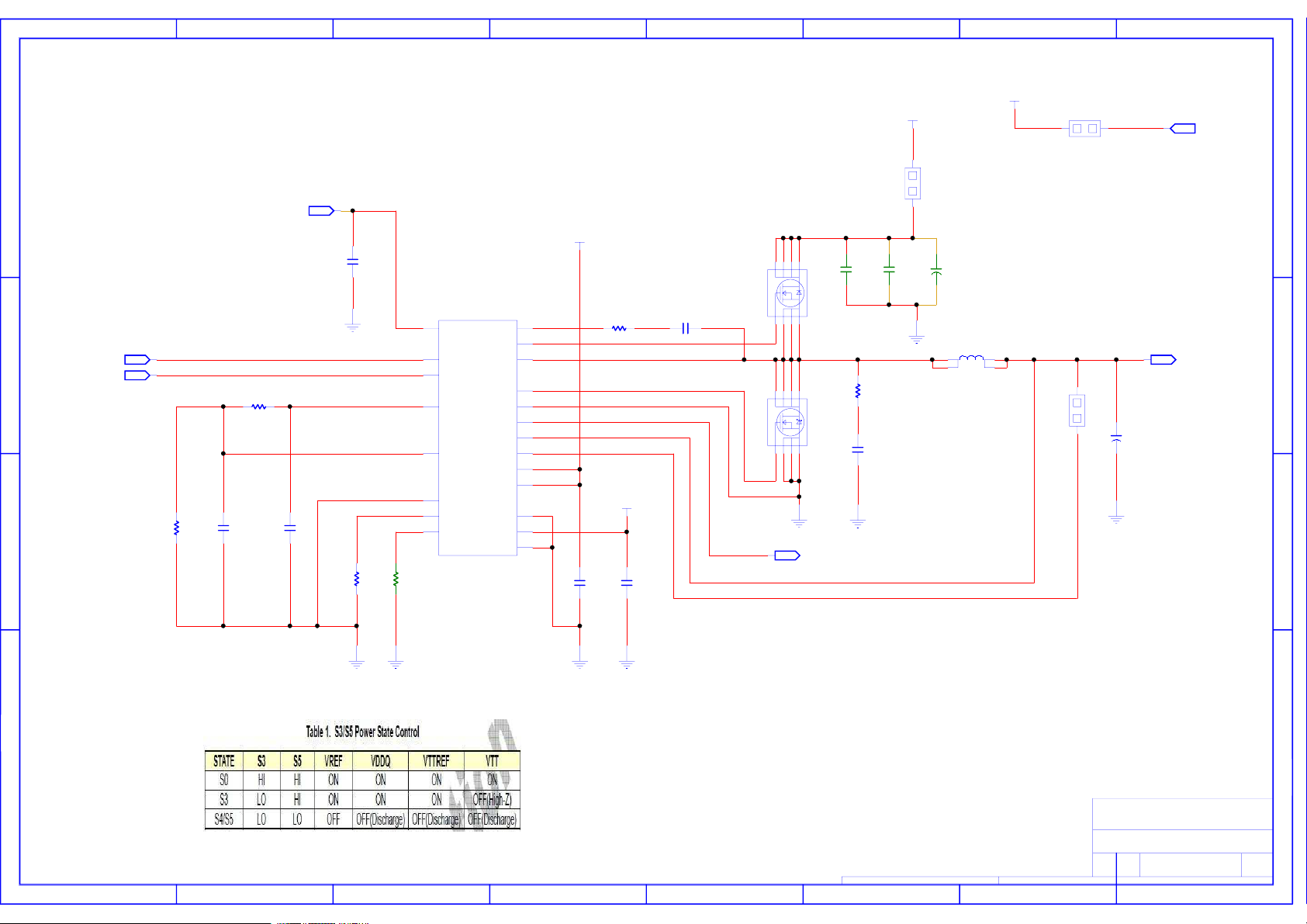

ADAPTER

DCIN JACK

D

P5

RQ3E080BNFU7TB

CHARGER

U6000

BATT_CLK

BATT_DAT

CN6050

P5

B

8

07dc0c1a02352f034a005270e0005460

SCL

SDA

P6

BQ24738

7 6

ACDET

PVBAT

RQ3E080BNFU7TB

PVPACK

AC_OK

EN_3V

EN_5V

TPS51225CRUKR

EN_VRPVTT

EN_VRPVDDQ

DDR3L_SEL

TPS51216RUKR

EN_P1V05

EN_PVCORE

VR_SVID_ALERT#

VR_SVID_CLK

VR_SVID_DATA

DGPU_PWR_EN

TPS51219RTER

EN_P1V5S_DGPU

5 4

U6100

5/3.3V

P7

U6200

VO

S3

S5

VREF

P8

VO

VO

PG

U6300

VO

EN

P9

PG

TPS51362

VR_ON

ALERT#

SCLK

SDA

P11~P12

TPS51631RSM

U6750

VO

U6250

PG

VO

PG

EN

P66

EN

P67

TPS51362

OCP 8.5A

P3V3DS

OCP 8A

P5V0DS

OCP 10A

P1V35

OCP 1A

P0V675S

P0V675M_VREF

VRPVDDQ_PG

OCP 12A

P1V05S_PCH

P1V05_PG

U6600

VOUT

PGOOD

PVCORE_DGPU

DGPU_PG

P1V5S_DGPU

P1V5S_DGPU_PG

CHANGE by

2.71A

PMN35EN

Q7003

P13

P3V3A

G

P3V3A_5A_PWEN#

OCP 1A

P3V3DS

EN_P1V5S

OCP 105A

PVCORE

PVCORE_PG

P1V05S_PCH

EN_P3V3S_DGPU

OCP 40A

P3V3S

EN_P3V3S_DGPU

OCP 8A

GPU POWER

DATE

XXX

21-OCT-2002

23

PMN35EN

Q7000

G

CORE_PWEN#

CORE_PWEN#

P13

PMN35EN

Q7002

G

P13

P1V5S_PCH

U6351

VO

EN

P10

APW7104BTI

FDMC7692

Q7403

P68

PMN35EN

Q7408

P68

P1V05S_DGPU

G

P3V3S_DGPU

G

INVENTEC

TITLE

MODEL,PROJECT,FUNCTION

POWER PROCEDURE

DOC.NUMBER

CODE

SIZE

A3

CS

1310xxxxx-0-0

SHEET

OCP 1.6A

3.968A

of

4

1

5.82 A

P3V3S

3.54 A

P5V0S

0.855A

70

REV

A01

D

CC

B

AA

Page 5

07dc0c1a02352f034a005270e0005460

8 7

9/31 BOM CHANGE 6014B0225501

PVADPTR

D

C6038

2 1

CSC0402_DY

C6037

2 1

1000PF_50V_2

6 5

L6015

21

HCB2012KF_121T30_120R_3A

HCB2012KF_121T30_120R_3A

L6016

21

4

1

2

C6036

2 1

C6035

2 1

0.1UF_25V_2

1000PF_50V_2

SEM_SM24_SOT23_3P_DY

D6035

1

3

3

P3V3AL

2

D6045

21

21

1SS355VMTE_17

2 1

3 2 1

3457

IN

3457

IN

R6048

1K_1%_2

2 1

OUT

R6047

C6048

2 1

12K_1%_2

ADP_ID

34

CHG_LED#

AC_LED#

0.0015UF_50V_2

6012B0422401

JACK6015

1

1

2

2

3

3

4

4

5

5

6

6

7

7

8

8

9

9

10

10

ACES_59012_0100N_003_10P

D

PV

CC

B

6

34

34

BATT_DAT

6

BATT_CLK

BI

BI

P3V3AL

D7500

8

7 6

07dc0c1a02352f034a005270e0005460

P3V3AL

PVPACK

D7504,D7505,D7506 SI Change to 6011B0132401

REV

A01

B

AA

R6052

2 1

2.2K_5%_2

R6050

2 1

2.2K_5%_2

2 1

C7500

100PF_50V_2

R6051

100_5%_2

D7504

2 1

2 1

21

2 1

LITEON_L13ESD5V0CA2_SOD523_2P

C7501

100PF_50V_2

R6053

100_5%_2

D7505

2 1

2 1

21

2 1

LITEON_L13ESD5V0CA2_SOD523_2P

P3V3AL

C7502

100PF_50V_2

R6057

100_5%_2

D7506

2 1

2 1

LITEON_L13ESD5V0CA2_SOD523_2P

21

CN6050

1

1

2

2

3

3

4

4

5

5

6

7

8

G1

G

6

G2

G

7

8

TAI_TWUN_PMPCR3_08MNBK2ZZ4H2_8P

21

C6050

3

2 1

DIODES_BAV99

3

D7501

2 1

DIODES_BAV99

3

D7502

0.1UF_25V_2

2 1

2 1

R6058

100K_5%_2

OUT

DIODES_BAV99

BATT_IN#

5 4

34

CHANGE by

XXX

DATE

21-OCT-2002

23

INVENTEC

TITLE

MODEL,PROJECT,FUNCTION

Block Diagram

DOC.NUMBER

CODE

SIZE

A3

CS

1310xxxxx-0-0

SHEET

5

of

70

1

Page 6

07dc0c1a02352f034a005270e0005460

8 7

6 5

4

3 2 1

PVADPTR

8

7

6

R6033

2_5%_6

2 1

ACDRV

OUT

IN

VADPBL

Q6010

1

2

3

4 5

S

G

NMOS_4D3S

AON6414AL

D

D

2 1

C6031

2200PF_50V_2

C6019

C6020

0.047UF_25V_2

2 1

2 1

0.1UF_25V_2

R6017

2 1

RSC_0402_DY

BATDRV

2 1

C6033

1UF_25V_3

IN

ACDRV

6

R6028

2 1

4.3K_5%_2

PVADPTR

B

R6021

OUT

34

34

BATT_DAT

34

BATT_CLK

VRP1V5S

10

8

IN

D6018

2 1

2 1

1SS355VMTE_17

ACDET>0.6V = SMBUS OK

ACDET>1.8V = ADP_PRES HI

ACDET>2.4V = AC_OK TO CHARGE

ACDET>3.15V = AC_OVP

ADP_PRES

2 1

300K_1%_2

R6049

2 1

47K_1%_2

7 6

07dc0c1a02352f034a005270e0005460

2 1

C6032

0.01UF_50V_2

OUT

P3V3AL

I_ADP

PVPACK

R6024

2 1

OUT

1

2

3

4 5

RQ3E080BNFU7TB

1

2

3

4 5

RQ3E080BNFU7TB

R6018

2 1

TI_BQ24738RGRR_QFN_20P

10K_5%_2

BI

BI

PVADPTR

D6099

IN

3

BAV70W

21

IN

OUT

PVBAT

VRP5V0A_VIN

D

Q6012

8

D

S

G

NMOS_4D3S

S

G

NMOS_4D3S

4.3K_5%_2

C6046

100PF_50V_2

7

6

PVBAT

Q6011

8

D

7

6

0.1UF_16V_2

21

C6029

1UF_25V_3

6

ACDET

7

IOUT

8

SDA

9

SCL

10

ILIM

BATDRVACPRES

115

P3V3A

2 1

R6023

2 1

100K_1%_236.5K_1%_2

C6047

2 1

CSC0402_DY

R6046

2 1

21

43

R6000

0.01_1%_6

21

C6028

C6030

2 1

CSC0402_DY

VRPVADPTR_CSN

VRPVADPTR_CSP

3

214

1UF_10V_2

21

20

19

18

17

16

R6025

R6020

2 1

C6027

0.047UF_25V_3

2 1

R6015

2.2_5%_2

D6016

2 1

DB2J31300L

21

21

OUT

21

BATDRV

ACDRV

U6000

SRN

12

ACP

CMSRC

GND

SRP

13

14

4.3K_5%_2

ACN

TML

VCC

PHASE

HIDRV

BTST

REGN

LODRV

15

SHORT_0402_5

SHORT_0402_5

R6043

C6025

21

5 4

6

7

IN

VRP5V0A_VIN

R6027

2 1

20_1%_5

VRPVPACK_HG

VRPVPACK_PH

C6015

0.047UF_16V_2

VRPVPACK_LG

6

12

PAD6015

2 1

POWERPAD_2_0610

IN

R6001

0.01_1%_6

C6023

0.1UF_16V_2

PVBAT_CHG

21

43

21

678

LQ3E080BNFU7TB

21

LQ3E080BNFU7TB

Q6000

D

NMOS_4D3S

C6000

G

S

3

2145

2 1

RSC_0603_DY

2 1

10UF_25V_5

ETQP3W4R7WFN

C6001

10UF_25V_5

L6000

21

R7600

678

Q6001

D

NMOS_4D3S

21

CSC0402_DY

G

S

3

214 5

C7600

21

C6024

2 1

CSC0402_DY

57

PVPACK

C6012

C6011

C6010

2 1

10UF_25V_5

C6021

2 1

0.1UF_25V_2

2 1

2 1

10UF_25V_5

CSC0805_DY

2 1

VRPVPACK_CSP

CC

B

D6019

B0530W_7

AA

VRPVPACK_CSN

INVENTEC

TITLE

MODEL,PROJECT,FUNCTION

Block Diagram

CHANGE by

XXX

DATE

21-OCT-2002

23

SIZE

DOC.NUMBER

CODE

1310xxxxx-0-0

CS

A3

SHEET

of

6

1

REV

A01

70

Page 7

07dc0c1a02352f034a005270e0005460

8 7

P3V3DS

D

PAD6100

2 1

POWERPAD_2_0610

12

IN

VRPVBAT_3V

PAD6110

IN

POWERPAD_2_0610

VRP3V3A

PVBAT

12

2 1

6 5

VRP5V0A_VIN

4

3 2 1

OCP=8AMPOCP=7AMP

P5V0DS

PAD6150

2 1

POWERPAD_2_0610

12

IN

VRP5V0A

7

PVBAT

D

12

POWERPAD_2_0610

6

VRP5V0A_PH

IN

OUT

VRPVBAT_5V

7

PAD6160

IN

2 1

C6110

OUT

VRP3V3A

+

C6100

2 1

150UF_6.3V

B

L6100

ETQP3W3R3WFN

R6100

2 1

6.8K_1%_2

R6101

2 1

10K_1%_2

C6111

2 1

2 1

10UF_25V_5

21

D

10UF_25V_5

Q6100

NMOS_4D3S

AON7410

G

S

3

214 5

678

D

R7610

Q6101

2 1

AON7752

C7610

2 1

CSC0402_DY RSC_0 603_DY

S

214 5

G

3

VO=((6.8K/10K)+1)*2

678

7

IN

P3V3AL

PAD6103

2 1

12

POWERPAD1X1M

8

7 6

07dc0c1a02352f034a005270e0005460

C6115

0.1UF_16V_2 2.2_5%_3

21

VRP3V3A_HG

VRP3V3A_PH

VRP3V3A_LG

46.4K_1%_2

R6110

21

EN_3V

IN

VRP3V3A_LDO

R6115

21

5V_PG

14

OUT

VRP3V3A_LDO

7

OUT

7

7

OUT

7

OUT

TI_TPS51225CRUKR_QFN_20P

9

10

8

11

4

5

6

7

3

C6121

2 1

1UF_6.3V_2

IN

EN_3V

SHORT_0402_5

EN_5V

SHORT_0402_5

5 4

DRVH2

SW2

VFB2

CS2

EN2

PGOOD

VREG3

U6100

VBST2

DRVL2

EN_5V

TMD

21

R6987

R6988

VBST1

DRVH1

DRVL1

VREG5

VFB1

VCLK

VIN

SW1

VO1

CS1

EN1

21

21

12

17

16

18

15

14

2

1

20

19

13

VRP5V0A_LDO

C6120

2 1

1UF_6.3V_2

C6122

2 1

1UF_25V_3

R6165

2.2_5%_3

VRP5V0A_HG

VRP5V0A_PH

VRP5V0A_LG

OUT

P5V0AL

21

7

IN

C6165

0.1UF_16V_2

60.4K_1%_2

R6160

21

VRP5V0A_CLK

OUT

EN_3A5A

PAD6105

2 1

12

POWERPAD1X1M

678

D

NMOS_4D3S

Q6150

G

S

21

Q6151

AON7752

AON7410

3

214 5

678

D

G

S

3

214 5

L6150

ETQP3W4R7WFN

R7615

2 1

C7615

2 1

CSC0402_DY RSC_0 603_DY

2 1

C6161

C6160

2 1

10UF_25V_5

10UF_25V_5

SHORT_0402_5

21

R6161

VR_VDD5

21

VRP5V0A

OUT

OUT

8 91112

7

67

66

CC

R6150

21

+

10.5K_1%_216.5K_1%_2

C6150

2 1

R6151

150UF_6.3V

21

B

VO=((15.4K/10K)+1)*2

7

7

14

7

CHANGE by

VRP5V0A

IN

VRP5V0A_CLK

IN

IN

VRP5V0A_LDO

XXX

2 1

C6156

0.1UF_16V_2

C6157

0.1UF_16V_2

2 1

D6151

DIODES_BAV99

3

3

DATE

21

D6150

DIODES_BAV99

21

2 1

C6159

1UF_25V_3

2 1

21-OCT-2002

23

C6158

0.1UF_16V_2

P15V0A

INVENTEC

TITLE

MODEL,PROJECT,FUNCTION

Block Diagram

CODE

SIZE

A3

CS

1310xxxxx-0-0

SHEET

DOC.NUMBER

of

7

AA

REV

A01

70

1

Page 8

07dc0c1a02352f034a005270e0005460

8 7

6 5

4

3 2 1

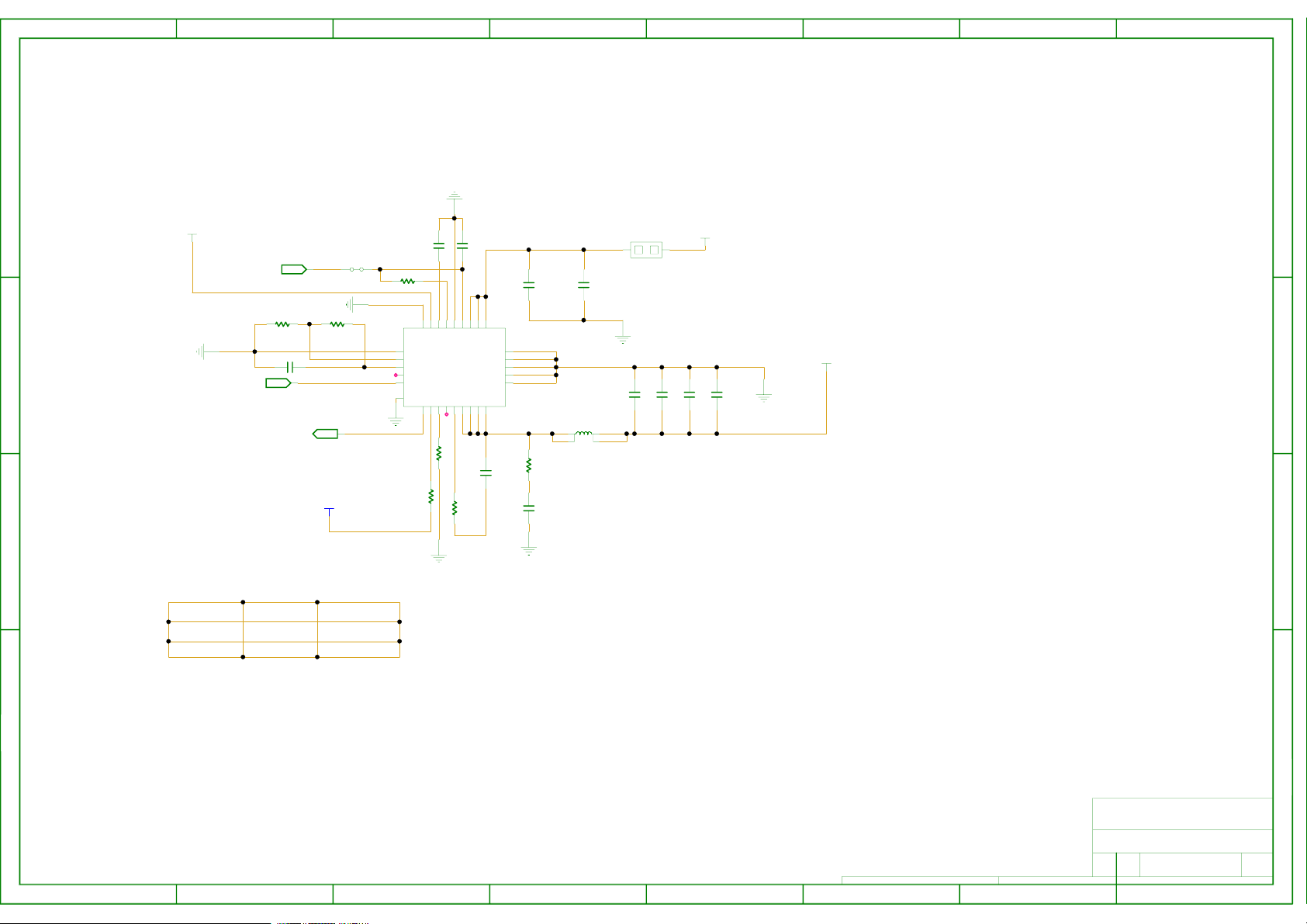

P1V35

PVBAT

PAD6200

2 1

POWERPAD_2_0610

12

IN

VRPVDDQ

8

D

67 661211

14

14

EN_VRPVTT

EN_VRPVDDQ

IN

IN

R6200

16.5K_1%_2

21

C6217

B

R6201

2 1

52.3K_1%_2

0.01UF_50V_2

VR_VDD5

9 7

IN

NMOS_4D3S

678

G

3

678

G

3

OUT

PVBAT_VDDQ

Q6200

D

S

214 5

Q6201

D

S

2145

VRPVDDQ_PG

C6211

2 1

10UF_25V_5

21

2 1

P0V675S

C6216

2 1

2.2UF_6.3V_3

U6200

17

S3

16

S5

21

C6218

2 1

0.1UF_16V_2

R6203

2 1

100K_5%_2

6

VREF

8

REFIN

7

GND

19

MODE

18

TRIP

21

TI_TPS51216RUKR_QFN_20P

R6202

86.6K_1%_2

VBSTV5IN

DRVH

DRVL

PGND

PGOOD

VDDQSNS

VLDOIN

VTTSNS

VTTGND

VTTREF

1512

14

13

SW

11

10

20

9

2

3

VTT

1

4

5

21

TML

2.2_5%_3

VRPVDDQ_HG

VRPVDDQ_PH

VRPVDDQ_LG

P0V675M_VREF

C6220

2 1

10UF_6.3V_3

R6215

2 1

21

C6221

C6215

0.1UF_16V_2

0.22UF_6.3V_2

21

AON7410

AON7752

12

PAD6210

2 1

POWERPAD_2_0610

+

C6210

C6299

47UF_25V

2 1

2 1

10UF_25V_5_DY

D

OCP=10AMP

L6200

PAN_ETQP3W1R0WFN_4P

R7620

RSC_0603_DY

C7620

CSC0402_DY

16

1 2

3 4

21

43

OUT

VRPVDDQ

8

CC

21

1 2

PAD6220

POWERPAD1X1M

+

C6200

2 1

330UF_2V_9MR_PANA_-35%

B

VOUT=REFIN=1.8*(52.3K/(16.5K+52.3K))

MODE=100KOHM:TRACKING DISCHARGE

8

7 6

07dc0c1a02352f034a005270e0005460

5 4

CHANGE by

XXX

DATE

21-OCT-2002

23

INVENTEC

TITLE

MODEL,PROJECT,FUNCTION

Block Diagram

DOC.NUMBER

CODE

SIZE

A3

CS

1310xxxxx-0-0

SHEET

8

of

70

1

REV

A01

AA

Page 9

07dc0c1a02352f034a005270e0005460

8 7

6 5

4

3 2 1

D

P1V05S_PCH

C6317

R6304

C6318

IN

21

100K_1%_2113K_1%_2

OUT

SHORT_0402_15

R6300

21

14

11

6766

12

VR_VDD5

EN_P1V05

R6301

2 1

0.22UF_6.3V_2

IN

14

P1V05_PG

P3V3DS

B

P1V05S-PCH

R6301

R6300

0

DY

INCREASE1%DEFAULT

113K_1%

100K_1%

C6316

21

0_5%_2

24

25

26

27

28

29

R6303

U6300

REFIN2

REFIN

VREF

RA

EN

TML

2700PF_50V_2

21

232221

GSNS

PGOOD

1

R6306

R6305

0_5%_2_DY

2.2UF_6.3V_3

2 1

2 1

C6311

1918171615

20

V5

VIN

VIN

VIN

GND

TRIP

VSNS

SLEW

LP#

2

21

0_5%_2_DY

21

21

R6315

10

PGND

11

PGND

12

PGND

13

PGND

14

PGND

SWSWSWSWBSTNCMODE

TI_TPS51362RVER_QFN_28P

9876543

VRP1V05_PH

RSC_0603_DY

CYN_PCMC063T_R68MN_4P

R7630

C6315

2 1

0.1UF_16V_2

C7630

2.2_5%_3

C6310

2 1

2 1

0.1UF_25V_2

L6300

21

2 1

CSC0402_DY

PAD6310

2 1

POWERPAD_2_0610

10UF_25V_5

21

C6300

21

43

PVBAT

12

21

21

21

C6302

C6301

22UF_6.3V_5

MODE= FLOAT FSW= 800K

TRIP =5V OCP=10A

REFIN =GND VOUT=1.05V

VOUT=2V*R6301/(R6300+R6301)=1.06V

C6303

22UF_6.3V_5

CSC0805_DY

22UF_6.3V_5

P1V05S_PCH

IOUT=6A

D

CC

B

8

7 6

07dc0c1a02352f034a005270e0005460

5 4

CHANGE by

XXX

DATE

21-OCT-2002

23

INVENTEC

TITLE

MODEL,PROJECT,FUNCTION

Block Diagram

DOC.NUMBER

CODE

SIZE

A3

CS

1310xxxxx-0-0

SHEET

9

of

70

1

REV

A01

AA

Page 10

07dc0c1a02352f034a005270e0005460

8 7

6 5

4

3 2 1

D

D

P3V3DS

PAD6360

1 2

POWERPAD1X1M

21

OUT

VRP1V5_1V5IN

OUT

VRP1V5S

6

OCP=1.6AMP

P1V5S_PCH

CC

C6360

2 1

4.7UF_6.3V_3

4 3

14

EN_1V5S

IN

ANPEC_APW7104BTI_TRG_5P

1

B

U6350

VIN SW

RUN

GND

2

VRP1V5S_PH

5

FB

L6350

PAN_ELL5PR2R2N

VOUT=((309K/200K)+1)*0.6

PAD6350

21

R6350

C6353

2 1

309K_1%_2200K_1%_2

2 1

330PF_50V_2

R6351

C6350

2 1

10UF_6.3V_3

POWERPAD1X1M

2 1

1 2

21

B

8

7 6

07dc0c1a02352f034a005270e0005460

5 4

CHANGE by

XXX

DATE

21-OCT-2002

23

INVENTEC

TITLE

MODEL,PROJECT,FUNCTION

Block Diagram

DOC.NUMBER

CODE

SIZE

A3

CS

1310xxxxx-0-0

SHEET

of

7010

1

REV

A01

AA

Page 11

07dc0c1a02352f034a005270e0005460

8 7

D

R6662

19

20

12

12

12

12

PVBAT_CPU

12

VCCSENSE

VSSSENSE

CPU_CSP2

CPU_CSN2

CPU_CSN1

CPU_CSP1

IN

0_5%_2_DY

R6664

2 1

CPU_CSN3

12

IN

12

IN

CPU_CSP3

0_5%_2

21

R6663

0_5%_2_DY

2 1

P3V3A

B

57W

3 PHASE

36.5K

VREF_CPU

11

IN

127K

75K

91K

DNP

DNP

POP

7 6

R6646

R6650

R6655

R6662

R6663

37W

2 PHASE

64.9K

549KR6649

150K

178K

POP

POP

DNPR6664

8

47W

3 PHASE

36.5K

150K

75K

91K

DNP

DNP

POP

07dc0c1a02352f034a005270e0005460

6 5

VREF_CPU

11

OUT

21

21

2.94K_1%_2

21

10K_5%_3

21

21

39K_1%_2

C6644

2 1

R6651

21

24

VFB

23

GFB

22

CSN3

21

CSP3

20

CSP2

19

CSN2

18

CSN1

17

CSP1

C6646

R6658

2 1

0.1UF_16V_2_DY

R6661

CPU_IMON

OUT

21

21

R6666

10K_1%_2

C6647

330PF_50V_2

2 1

R6656

10K_1%_2

C6640

CSC0402_DY

IN

IN

IN

IN

IN

IN

R6657

21

R6659

R6660

RSC_0402

VR_VDD5

21

10_5%_3

0.47UF_6.3V_2

V5A

GND

VREF

COMP

DROOP

IMON

VBAT

SLEWA

THERM

OCP-I

16151413121110

10K_1%_2

R6654

R6655

100K_5%_NTC

7 8 91266 67

IN

R6665

C6643

1UF_6.3V_2

2 1

OUT

IN

IN

IN

333231

3032928272625

VCLK

PWPD

ALERT#

1

VDIO

VR_HOT#

B-RAMP

21

21

2

VDD

PGOOD

4

PWM3

5

PWM2

6

PWM1

7

SKIP#

8

VR_ON

F-IMAX

O-USR

U6600

TI_TPS51631RSM_QFN_32P

9

21

R6653

150K_1%_2

39K_1%_2

21

R6652

95.3K_1%_2

C6645

RSC_0402

2 1

4700PF_50V_2

21

R6650

75K_1%_2

21

R6649

127K_1%

5 4

CPU_PROCHOT#

VR_SVID_CLK

VR_SVID_ALERT#

VR_SVID_DATA

OUT

OUT

OUT

OUT

OUT

IN

21

20K_1%_2

R6647

21

R6646

VREF_CPU

36.5K_1%_2

4

16

34

19

11

19

11

19

26

PVCORE_PG

CPU_PWM3

CPU_PWM2

CPU_PWM1

CPU_SKIP#

VR_ON

11

IN

14

12

12

12

12

11

INPUT VOLTAGE RANGE

MAX CURRENT

THERMAL DESIGN CURRENT

DYNAMIC CURRENT

OVER CURRENT LEVEL

SWITCHING FREQUENCY

BOOT VOLTAGE

P3V3DS

21

10_5%_3

1UF_6.3V_2

2 1

CHANGE by

3 2 1

PVCCIO_OUT

VR_SVID_DATA

R6640

130_1%_2

R6641

54.9_1%_2

21

R6643

10K_1%_2

21

R6644

21

21

IN

OUT

VR_SVID_CLK

OUT

EN_PVCORE

R6645

C6642

11

VR_ON

C6641

2 1

0.1UF_10V_2_DY

OUT

4.99K_1%_2

37W

9V TO 20V

55A

21A

35A

70A

1MHZ

1.7V

1.5MOHMDC LOAD-LINE

XXX

47W

9V TO 20V

85A

27A

60A

105A 105A

800KHZ

1.7V

1.5MOHM

57W

9V TO 20V

95A

33A

60A

800KHZ

1.7V

1.5MOHM

DATE

21-OCT-2002

23

INVENTEC

TITLE

MODEL,PROJECT,FUNCTION

CODE

SIZE

CS

A3

19

11

19

11

Block Diagram

DOC.NUMBER

1310xxxxx-0-0

SHEET

D

CC

14

B

AA

REV

of

11

A01

70

1

Page 12

07dc0c1a02352f034a005270e0005460

8 7

6 5

4

3 2 1

OUT

OUT

OUT

OUT

1

2

3

VR_VDD5

C6616

1UF_10V_2

2 1

C6626

1UF_10V_2

2 1

CPU_CSN1

CPU_CSP1

2.32K_1%

CPU_CSN2

CPU_CSP2

VR_VDD5

2.32K_1%

IN

R6616

2 1

2 1

R6626

21

R7661

RSC_0603_DY

C7661

CSC0402_DY

IN

21

10K_1%_NTC

R7662

RSC_0603_DY

2 1

C7662

CSC0402_DY

2 1

CSC0402_DY

0.15UF_10V_2

17.8K_1%_2

R6617

21

ETQP4LR15AFM

3 4

1 2

L6610

CSC0402_DY

0.15UF_10V_2

17.8K_1%_2

R6627

ETQP4LR15AFM

3 4

1 2

L6620

C6618

C6617

R6619

21

43

21

C6628

C6627

R6629

43

21

21

21

21

R6618

3.01K_1%_210K_1%_NTC

21

21

21

R6628

3.01K_1%_2

PVBAT

PAD6610

21

1 2

6766

1211987

21

PVCORE

POWERPAD_2_0610

PV

PVBAT_CPU

+

C6699

47UF_25V

2 1

C6611

C6610

2 1

2 1

10UF_25V_5

10UF_25V_5

C6621

C6620

2 1

2 1

10UF_25V_5

10UF_25V_5

C6631

C6630

2 1

2 1

10UF_25V_5

10UF_25V_5

OUT

11

12

D

PVCORE

C6604

2 1

22UF_6.3V_5

CPU_CSN3

CPU_CSP3

2.32K_1%

CSC0805_DY

R6636

C6605

2 1

IN

C6600

2 1

2 1

22UF_6.3V_5

PV

IN

IN

2.2_5%_3

IN

CPU_SKIP#

CPU_PWM3

R6635

PVBAT_CPU

C6635

21

TI_CSD97374CQ4M_SON_8P

21

0.1UF_16V_2

U6630

8

PWM

SKIP#

7

BOOT

VDD

6

BOOT_R

PGND

5 4

VIN VSW

PGND

9

11

12

21

PVCORE

11

11

12

2 1

2 1

22UF_6.3V_5

22UF_6.3V_5

11

OUT

11

OUT

VR_VDD5

C6636

1UF_10V_2

2 1

1

2

3

C6603

C6602

C6601

C6606

2 1

CSC0805_DY

21

10K_1%_NTC

R7663

RSC_0603_DY

C6607

2 1

22UF_6.3V_5

CSC0402_DY

0.15UF_10V_2

17.8K_1%_2

R6637

ETQP4LR15AFM

3 4

1 2

L6630

22UF_6.3V_5

21

C6608

2 1

C6638

C6637

R6639

43

21

C6609

2 1

22UF_6.3V_5

21

21

21

R6638

3.01K_1%_2

CSC0805_DY

21

PVCORE

2 1

C7663

CSC0402_DY

CC

B

AA

2 1

11

11

D

11

12

11

11

12

CPU_SKIP#

IN

CPU_PWM1

IN

R6615

2.2_5%_3

PVBAT_CPU

IN

TI_CSD97374CQ4M_SON_8P

21

0.1UF_16V_2

C6615

B

PV

8

PWM

21

7

BOOT

6

BOOT_R

5 4

VIN VSW

U6610

SKIP#

PGND

PGND

9

1

2

VDD

3

11

11

PV

11

12

11

11

12

CPU_SKIP#

IN

CPU_PWM2

IN

R6625

21

2.2_5%_3

PVBAT_CPU

IN

TI_CSD97374CQ4M_SON_8P

C6625

0.1UF_16V_2

8

PWM

7

21

BOOT

6

BOOT_R

5 4

VIN VSW

U6620

SKIP#

PGND

PGND

9

VDD

8

7 6

07dc0c1a02352f034a005270e0005460

5 4

CHANGE by

XXX

DATE

21-OCT-2002

23

INVENTEC

TITLE

MODEL,PROJECT,FUNCTION

Block Diagram

DOC.NUMBER

CODE

SIZE

A3

CS

1310xxxxx-0-0

SHEET

of

7012

1

REV

A01

Page 13

07dc0c1a02352f034a005270e0005460

8 7

6 5

4

3 2 1

CHECK !

PV

CHECK !

P3V3AL

D

34

IN

R7077

10K_5%_2

2 1

P3V3A_5A_PWEN#

R7021

1M_5%_2

2 1

P15V0A_RC_3A_5A

3

Q7009

DS

1

G

2

SSM3K7002BFU

P3V3A

R7020

100_5%_5

2 1

3

Q7010

DS

1

G

2

SSM3K7002BFU

P3V3DS

C7013

2 1

2200pF_50V_2

6015B0132801

Q7003

1

D

2

5

NMOS_4D1S NMOS_4D3S

PMN35EN

SHORT_0402_5

R7006

4

S

36

G

21

PV

P3V3A

C7010

2 1

10uF_6.3V_3

34

IN

PV

P3V3AL

R7078

10K_5%_2

CORE_PWEN#

P5V0S

R7016

100_5%_5

2 1

3

Q7005

DS

G

2

SSM3K7002BFU

P15V0AP15V0A

2

2 1

D7002

NC

DIODE-BAT54-TAP-PHP

R7023

10K_1%_2

CORE_PWEN#_RC

21

9/21

R7011

1M_5%_2

2 1

G

P15V0A_RC_3S_5S

3

DS

C7008

2

SSM3K7002BFU

13

Q7001

1

21

C7014

0.01uF_50V_2

P3V3S

R7015

100_5%_5

2 1

3

Q7004

DS

1

1

G

2

SSM3K7002BFU

P3V3DS

Q7000

8

D

7

6

RQ3E080BNFU7TB

SHORT_0402_5

R7004

PV

2 1

2200pF_50V_2

P5V0DS P5V0S

8

7

6

RQ3E080BNFU7TB

SHORT_0402_5

R7005

21

Q7002

D

21

NMOS_4D3S

1

S

2

3

45

G

S

G

PV

P3V3S

D

C7007

2 1

10uF_6.3V_3

1

2

3

45

C7009

2 1

10uF_6.3V_3

CC

9/20

1

Q7006

G

P1V05S_PCH

21

R7017

47_5%_3

3

9/21

DS

2

B

P0V675S

21

R7018

22_5%_2_DY

3

Q7007

DS

1

G

SSM3K7002BFU_DY SSM3K7002BFU

2

B

8

7 6

07dc0c1a02352f034a005270e0005460

5 4

CHECK !

CHANGE by

XXX

DATE

21-OCT-2002

23

INVENTEC

TITLE

MODEL,PROJECT,FUNCTION

Block Diagram

DOC.NUMBER

CODE

SIZE

A3

CS

1310xxxxx-0-0

SHEET

of

7013

1

REV

A01

AA

Page 14

07dc0c1a02352f034a005270e0005460

8 7

R6997

21

7

EN_3A5A

IN

C6999

2 1

1K_5%_2

R6998

2 1

200K_5%_2

0.1UF_25V_2

ALWAYS_PW_EN

OUT

34

D

7

34 26

IN

IN

5V_PG

RSMRST#

R7498

21

0_5%_2

C7498

6010071020AT

2 1

1000PF_50V_2_DY

B

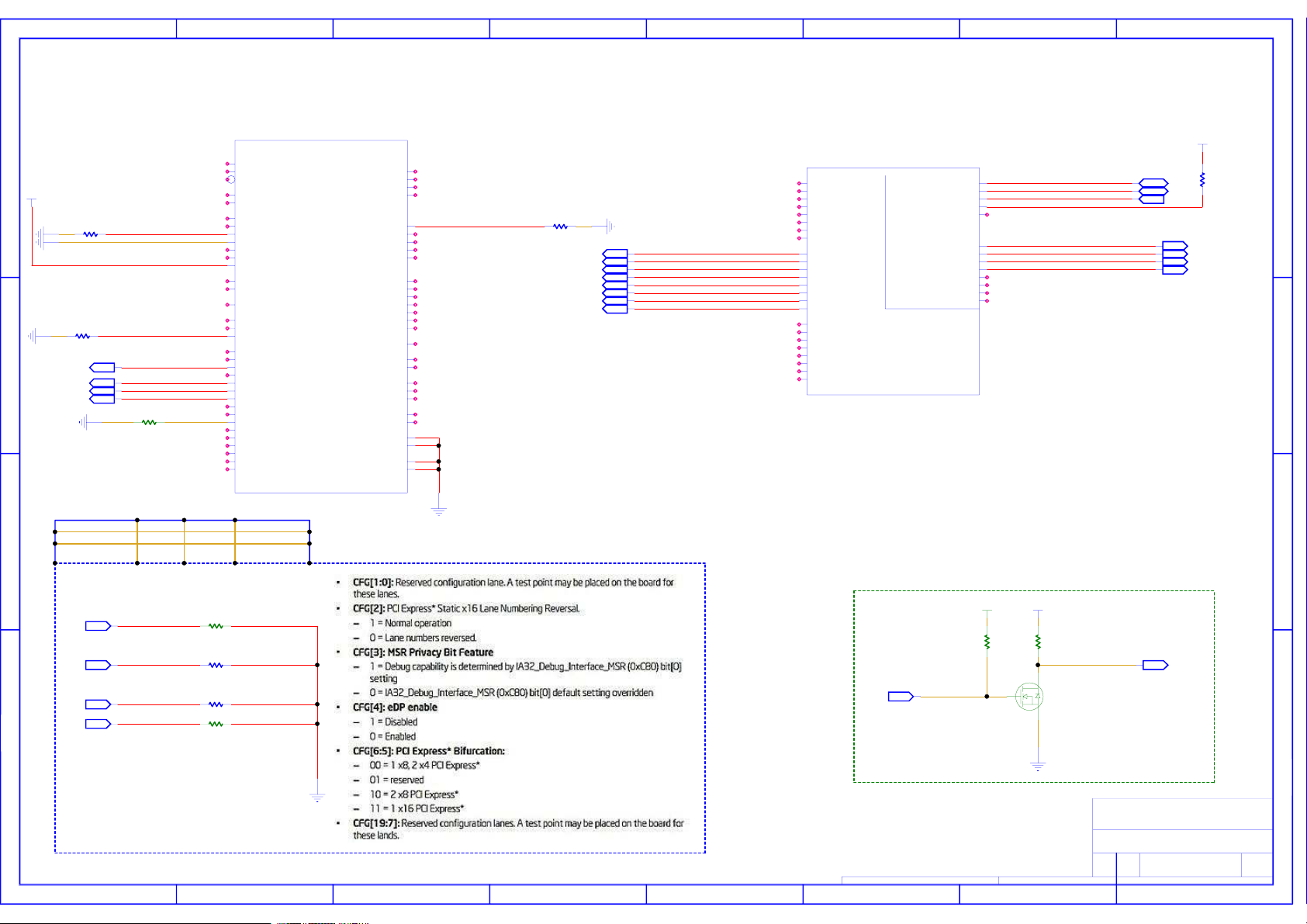

SUPPORT GC6 ONLY

66

67

DGPU_PG

IN

IN

8

PV

P3V3S

R7499

0_5%_2

P1V5S_DGPU_PG

0_5%_2_DY

9/31

9/21

P3V3S_DGPU

10K_5%_2

2 1

R7495

21

R7494

21

7 6

R7496

2 1

10K_5%_2_DY

C7480

2 1

CSC0402_DY

07dc0c1a02352f034a005270e0005460

P3V3AL

21

R7497

DGPU_PWROK

6 5

11

UNMOUNT

3428

OUT

PVCORE_PG

100K_5%_2_DY

R7496

26

DIS UMA

MOUNT

OUT

P3V3S

9/20

R7014

10K_5%_2

2 1

5 4

4

34

IN

3834

IN

3 2 1

R7010

RESUME_PWEN EN_VRPVDDQ

9/31

CLOSE TO POWER SIDE

CORE_PWEN

DIODE-BAT54-TAP-PHP

100K_1%_2

C7005

2 1

CSC0402_DY

2

D7000

NC

R7012

100K_1%_2

2 1

C7006

21

13

21

9/21

100PF_50V_2

EN_VRPVTT

OUT

OUT

8

8

D

CLOSE TO POWER SIDE

9/20

R7003

141434

38

CORE_PWEN EN_P1V05

IN

0.01UF_50V_2_DY

CLOSE TO POWER SIDE

0_5%_2

C7000

2 1

21

OUT

9

CC

2

D7001

NC

13

DIODE-BAT54-TAP-PHP

IN

IN

CORE_PWEN

CPU_PWEN

14

38

34

34

R7008

330K_1%_2

C7003

2 1

0.01uF_50V_2

CLOSE TO POWER SIDE

R7009

0_5%_2

C7004

2 1

0.1uF_16V_2_DY

CLOSE TO POWER SIDE

9/20

21

EN_1V5S

21

EN_PVCORE

OUT

OUT

10

11

B

P3V3S

R7000

2 1

10K_5%_2

R7001

100_1%_2

21

ALL_PWGD_IN

OUT

34

9

P1V05_PG

IN

AA

9/21

INVENTEC

TITLE

MODEL,PROJECT,FUNCTION

Block Diagram

DOC.NUMBER

CODE

SIZE

A3

CS

1310xxxxx-0-0

SHEET

of

7014

1

REV

A01

CHANGE by

XXX

C7001

2 1

2200PF_50V_2

DATE

21-OCT-2002

23

Page 15

07dc0c1a02352f034a005270e0005460

8 7

6 5

9/20

4

3 2 1

D

P3V3S

D

21

FAN CONN

P5V0SP3V3S

C4413

2 1

4.7uF_6.3V_3

C4414

2 1

R4411

R4412

2 1

2 1

4.7K_5%_2

FAN_TACH0

34

OUT

IN

CPUFAN1_ON#

C4411

2 1

CSC0402_DY

34

0.1uF_16V_2

CN4411

4.7K_5%_2_DY

1

1

2

2

3

3

4

GG4

ACES_50273_0047N_001_4P

PN: 6012A0081607

G1

G2

B

34

PN: 60130B1040ZT

THERMTRIP#

OUT

R4301

10.5K_1%_2

42

THM_SMCLK_AU THM_SMDAT_AU

NCT7717U I2C/SMBUS ADDRESS IS 1001000XB (X IS R/W BIT)

6019B0914301

U4301

2

GND

3

ALERT#

NUVO_NCT7717U_SOT23_5P

SI-1016

51

SDASCL

P3V3S

4

VDD

42

BIBI

C4302

2 1

2.2UF_6.3V_2

CC

B

8

7 6

07dc0c1a02352f034a005270e0005460

5 4

CHANGE by

XXX

DATE

21-OCT-2002

23

INVENTEC

TITLE

MODEL,PROJECT,FUNCTION

THERMAL & FAN

DOC.NUMBER

CODE

SIZE

A3

CS

1310xxxxx-0-0

SHEET

of

7015

1

REV

A01

AA

Page 16

07dc0c1a02352f034a005270e0005460

8 7

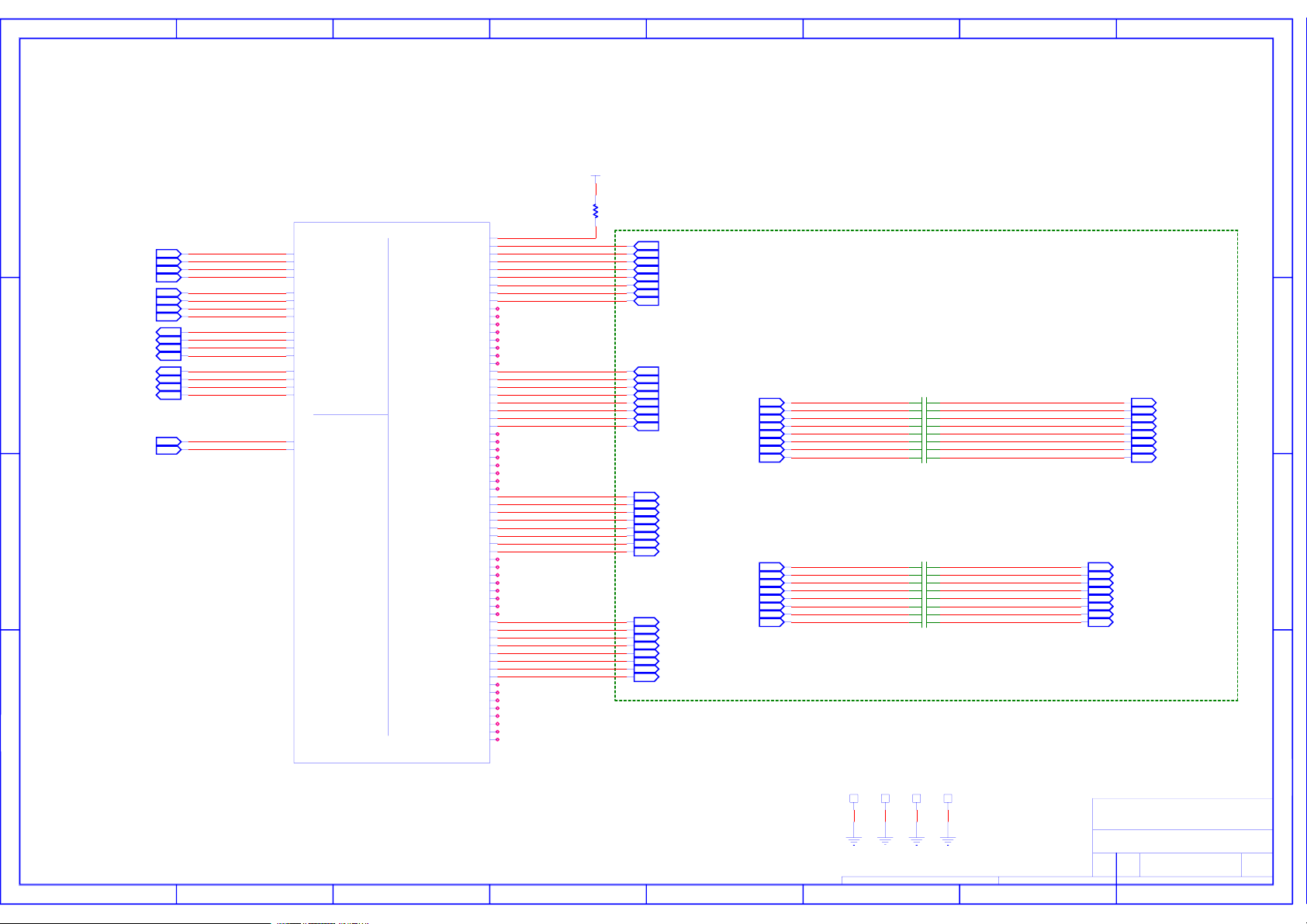

CPU

LOCATION 4500-4699

VER.01_20120808

D

34

11

IN

CLK_DP_SSC_R_DP

CLK_DP_SSC_R_DN

CPU_PROCHOT#

47pF_50V_2

PVCCIO_OUT

R4648

2 1

10K_5%_2_DY

R4649

10K_5%_2_DY

PVCCIO_OUT

R4506

63.4_1%_2

2 1

C4507

2 1

21

R4699

56.2_1%_2

34

21

OUT

28

OUT

26

BI

28

IN

16

IN

16

IN

30

IN

30

IN

30

IN

30

IN

30

IN

30

IN

6 5

H_PECI

CPU_PROCHOT#_R

PM_THRMTRIP#

C4678

H_PM_SYNC

H_CPUPWRGD

PM_DRAM_PWRGD_CPU

CPU_RST#

CLK_DP_NONSSC_DN

CLK_DP_NONSSC_DP

CLK_DP_SSC_DN

CLK_DP_SSC_DP

CLK_DMI_DN

CLK_DMI_DP

21

CSC0402_DY

R4678

21

RSC_0402_DY

R4516

R4517

R4518

R4519

R4502

R4503

EMI

2 1

2 1

2 1

2 1

2 1

2 1

PV

TP4521

TP4525

TP24

TP24

SHORT_0402_5

SHORT_0402_5

SHORT_0402_5

SHORT_0402_5

SHORT_0402_5

SHORT_0402_5

1

H_CATERR#

1

FC_AK31

R4504

2 1

10K_5%_2

CLK_DP_NONSSC_R_DN

CLK_DP_NONSSC_R_DP

CLK_DP_SSC_R_DN

CLK_DP_SSC_R_DP

CLK_DMI_R_DN

CLK_DMI_R_DP

4

Haswell rPGA EDS

CN4500

CHECK !

MISC

SM_RCOMP_0

THERMAL

PWR

SM_RCOMP_1

SM_RCOMP_2

SM_DRAMRST*

DDR3

JTAG

CLOCK

AP32

SKTOCC*

AN32

CATERR*

AR27

PECI

AK31

FC

AM30

PROCHOT*

AM35

THERMTRIP*

AT28

PM_SYNC

AL34

PWRGOOD

AC10

SM_DRAMPWROK

AT26

PLTRSTIN*

G28

DPLL_REF_CLKN

H28

DPLL_REF_CLKP

F27

SSC_DPLL_REF_CLKN

E27

SSC_DPLL_REF_CLKP

D26

BCLKN

E26

BCLKP

SOCKET,CPU,947P,1.0mm,1.0cc,GOLD,15U,BGA,TRAY

PRDY*

PREQ*

TCK

TMS

TRST*

TDO

DBR*

BPM_N_0

BPM_N_1

BPM_N_2

BPM_N_3

BPM_N_4

BPM_N_5

BPM_N_6

BPM_N_7

3 2 1

SM_RCOMP0

TDI

AP3

SM_RCOMP1

AR3

SM_RCOMP2

AP2

AN3

CPU_DRAMRST#

AR29

H_PRDY#

AT29

H_PREQ#

AM34

H_TCK

AN33

H_TMS

AM33

H_TRST#

AM31

H_TDI

AL33

H_TDO

AP33

H_BDR#

AR30

AN31

AN29

AP31

AP30

AN28

AP29

AP28

R4540

R4541

R4542

TP24

TP24

TP24

TP24

21

100_1%_2

21

75_1%_2

21

100_1%_2

16

OUT

1

TP4528

1

TP4529

OUT

1

TP4530

16

IN

1

TP4531

OUT

16

OUT

OUT

IN

OUT

H_TDO

H_TCK

H_TRST#

16

16

16

R4680

21

RSC_0402_DY

16

16

R4512

R4545

R4546

EMI

21

C4680

51_5%_2

21

51_5%_2

21

51_5%_2

21

CSC0402_DY

P1V05S_PCH

D

PV

28

PLTRST_PROC#

RSC_0402_DY

R4677

EMI

C4677

CSC0402_DY

B

P1V35

R4536

2 1

Q4531

3

DS

1

G

2

R4532

2 1

0.047uF_16V_2_DY

7 6

34 25

18

16

EMI

IN

IN

RSC_0402_DY

C4679

CSC0402_DY

8

PCH_DDR_RST

CPU_DRAMRST#

1

R4679

2

1

2

BSS138LT1_DY

C4526

2 1

R4544

0_5%_2

2 1

2 1

1K_1%_2_DY

R4538

1K_5%_2

R4537

0_5%_2

2 1

4.99K_1%_2_DY

07dc0c1a02352f034a005270e0005460

21

CPU_RST#

21

DIMM_DRAMRST#

CN4500

6026B0231701

16

16

OUTIN

OUT

H_BDR#

R4513

21

1K_5%_2

P3V3S

CC

P3V3DS P1V35

C4501

21

0.1uF_16V_2

21

U4501

R4500

1

100K_5%_2

100K_5%_2

C4502

2 1

0.01UF_50V_2

VCC

B

2

Y

A

3

GND

NXP_74AHC1G09GV_SOT753_5P

0_5%_2_DY

R4511

R4697

1.8K_1%_2

2 1

5

4

PM_DRAM_PWRGD_CPU

R4510

C4503

2 1

3.3K_1%_2

2 1

DS3

OUT

16

B

CSC0402_DY

CHECK !

21

09/21

OUT

21

DS3

VRPVDDQ_PG

8

IN

6019B0773901

2322

R4509

0_5%_2

26

IN

R4501

21

PM_DRAM_PWRGD

AA

INVENTEC

TITLE

MODEL,PROJECT,FUNCTION

Block Diagram

5 4

CHANGE by

XXX

DATE

21-OCT-2002

23

SIZE

DOC.NUMBER

CODE

1310xxxxx-0-0

CS

A3

SHEET

of

16

1

REV

A01

70

Page 17

07dc0c1a02352f034a005270e0005460

8 7

CPU

LOCATION 4500-4699

VER.01_20120808

6 5

4

3 2 1

D

26

26

26

26

26

26

26

26

26

26

26

26

26

26

26

26

26

26

B

GV2

Haswell rPGA EDS

CN4500

IN

IN

IN

IN

IN

IN

IN

IN

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

IN

IN

DMI_TX0_DN

DMI_TX1_DN

DMI_TX2_DN

DMI_TX3_DN

DMI_TX0_DP

DMI_TX1_DP

DMI_TX2_DP

DMI_TX3_DP

DMI_RX0_DN

DMI_RX1_DN

DMI_RX2_DN

DMI_RX3_DN

DMI_RX0_DP

DMI_RX1_DP

DMI_RX2_DP

DMI_RX3_DP

FDI_CSYNC

FDI_INT

D21

C21

B21

A21

D20

C20

B20

A20

D18

C17

B17

A17

D17

C18

B18

A18

H29

J29

DMI_RXN_0

DMI_RXN_1

DMI_RXN_2

DMI_RXN_3

DMI_RXP_0

DMI_RXP_1

DMI_RXP_2

DMI_RXP_3

DMI_TXN_0

DMI_TXN_1

DMI_TXN_2

DMI_TXN_3

DMI_TXP_0

DMI_TXP_1

DMI_TXP_2

DMI_TXP_3

FDI_CSYNC

FDI_INT

PEG

FDIDMI

PEG_RCOMP

PEG_RXN_0

PEG_RXN_1

PEG_RXN_2

PEG_RXN_3

PEG_RXN_4

PEG_RXN_5

PEG_RXN_6

PEG_RXN_7

PEG_RXN_8

PEG_RXN_9

PEG_RXN_10

PEG_RXN_11

PEG_RXN_12

PEG_RXN_13

PEG_RXN_14

PEG_RXN_15

PEG_RXP_0

PEG_RXP_1

PEG_RXP_2

PEG_RXP_3

PEG_RXP_4

PEG_RXP_5

PEG_RXP_6

PEG_RXP_7

PEG_RXP_8

PEG_RXP_9

PEG_RXP_10

PEG_RXP_11

PEG_RXP_12

PEG_RXP_13

PEG_RXP_14

PEG_RXP_15

PEG_TXN_0

PEG_TXN_1

PEG_TXN_2

PEG_TXN_3

PEG_TXN_4

PEG_TXN_5

PEG_TXN_6

PEG_TXN_7

PEG_TXN_8

PEG_TXN_9

PEG_TXN_10

PEG_TXN_11

PEG_TXN_12

PEG_TXN_13

PEG_TXN_14

PEG_TXN_15

PEG_TXP_0

PEG_TXP_1

PEG_TXP_2

PEG_TXP_3

PEG_TXP_4

PEG_TXP_5

PEG_TXP_6

PEG_TXP_7

PEG_TXP_8

PEG_TXP_9

PEG_TXP_10

PEG_TXP_11

PEG_TXP_12

PEG_TXP_13

PEG_TXP_14

PEG_TXP_15

E23

M29

K28

M31

L30

M33

L32

M35

L34

E29

D28

E31

D30

E35

D34

E33

E32

L29

L28

L31

K30

L33

K32

L35

K34

F29

E28

F31

E30

F35

E34

F33

D32

H35

H34

J33

H32

J31

G30

C33

B32

B31

A30

B29

A28

B27

A26

B25

A24

J35

G34

H33

G32

H31

H30

B33

A32

C31

B30

C29

B28

C27

B26

C25

B24

PVCCIOA_OUT

PEG_RCOMP

PEG_RX0_C_DN

PEG_RX1_C_DN

PEG_RX2_C_DN

PEG_RX3_C_DN

PEG_RX4_C_DN

PEG_RX5_C_DN

PEG_RX6_C_DN

PEG_RX7_C_DN

PEG_RX0_C_DP

PEG_RX1_C_DP

PEG_RX2_C_DP

PEG_RX3_C_DP

PEG_RX4_C_DP

PEG_RX5_C_DP

PEG_RX6_C_DP

PEG_RX7_C_DP

PEG_TX0_DN

PEG_TX1_DN

PEG_TX2_DN

PEG_TX3_DN

PEG_TX4_DN

PEG_TX5_DN

PEG_TX6_DN

PEG_TX7_DN

PEG_TX0_DP

PEG_TX1_DP

PEG_TX2_DP

PEG_TX3_DP

PEG_TX4_DP

PEG_TX5_DP

PEG_TX6_DP

PEG_TX7_DP

R4645

24.9_1%_2

2 1

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

D

UMA DELETE

59

IN

59

IN

59

IN

59

IN

59

IN

59

IN

59

IN

59

IN

59

IN

59

IN

59

IN

59

IN

59

IN

59

IN

59

IN

59

IN

17

17

17

17

17

17

17

17

17

17

17

17

17

17

17

17

17

IN

17

IN

17

IN

17

IN

17

IN

17

IN

17

IN

17

IN

17

IN

17

IN

17

IN

17

IN

17

IN

17

IN

17

IN

17

IN

CLOSE TO CPU

PEG_TX7_DN PEG_TX7_C_DN

PEG_TX6_DN PEG_TX6_C_DN

PEG_TX5_DN PEG_TX5_C_DN

PEG_TX4_DN PEG_TX4_C_DN

PEG_TX3_DN PEG_TX3_C_DN

PEG_TX2_DN PEG_TX2_C_DN

PEG_TX1_DN PEG_TX1_C_DN

PEG_TX0_DN PEG_TX0_C_DN

PEG_TX7_DP PEG_TX7_C_DP

PEG_TX6_DP PEG_TX6_C_DP

PEG_TX5_DP PEG_TX5_C_DP

PEG_TX4_DP PEG_TX4_C_DP

PEG_TX3_DP PEG_TX3_C_DP

PEG_TX2_DP PEG_TX2_C_DP

PEG_TX1_DP PEG_TX1_C_DP

PEG_TX0_DP PEG_TX0_C_DP

C4688

C4689

C4690

C4691

C4693

C4694

C4695

C4692

C4696

C4697

C4698

C4699

C4504

C4505

C4506

C4508

FOR DGPU SCREW

21

0.22UF_16V_2

21

0.22UF_16V_2

21

0.22UF_16V_2

21

0.22UF_16V_2

21

0.22UF_16V_2

21

0.22UF_16V_2

21

0.22UF_16V_2

21

0.22UF_16V_2

21

0.22UF_16V_2

21

0.22UF_16V_2

21

0.22UF_16V_2

21

0.22UF_16V_2

21

0.22UF_16V_2

21

0.22UF_16V_2

21

0.22UF_16V_2

21

0.22UF_16V_2

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

CC

59

OUT

59

OUT

59

OUT

59

OUT

59

OUT

59

OUT

59

OUT

59

OUT

B

59

59

59

59

59

59

59

59

AA

LOTES_AZIF0012_P001B_947P

8

7 6

07dc0c1a02352f034a005270e0005460

5 4

S5000

1

SCREW330_600_1P

CHANGE by

S5001

1

SCREW330_600_1P

XXX

1

1

SCREW330_600_1P

SCREW330_600_1P

DATE

21-OCT-2002

23

INVENTEC

TITLE

MODEL,PROJECT,FUNCTION

Block Diagram

DOC.NUMBER

CODE

SIZE

1310xxxxx-0-0

CS

A3

SHEET

of

7017

1

REV

A01

S5003

S5002

Page 18

07dc0c1a02352f034a005270e0005460

8 7

CPU

LOCATION 4500-4699

VER.01_20120808

D

B

P0V675M_VREF_H

18

OUT

18

OUT

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

M_A_DQ<0>

BI

M_A_DQ<1>

BI

M_A_DQ<2>

BI

M_A_DQ<3>

BI

M_A_DQ<4>

BI

M_A_DQ<5>

BI

M_A_DQ<6>

BI

M_A_DQ<7>

BI

M_A_DQ<8>

BI

M_A_DQ<9>

BI

M_A_DQ<10>

BI

M_A_DQ<11>

BI

M_A_DQ<12>

BI

M_A_DQ<13>

BI

M_A_DQ<14>

BI

M_A_DQ<15>

BI

M_A_DQ<16>

BI

M_A_DQ<17>

BI

M_A_DQ<18>

BI

M_A_DQ<19>

BI

M_A_DQ<20>

BI

M_A_DQ<21>

BI

M_A_DQ<22>

BI

M_A_DQ<23>

BI

M_A_DQ<24>

BI

M_A_DQ<25>

BI

M_A_DQ<26>

BI

M_A_DQ<27>

BI

M_A_DQ<28>

BI

M_A_DQ<29>

BI

M_A_DQ<30>

BI

M_A_DQ<31>

BI

M_A_DQ<32>

BI

M_A_DQ<33>

BI

M_A_DQ<34>

BI

M_A_DQ<35>

BI

M_A_DQ<36>

BI

M_A_DQ<37>

BI

M_A_DQ<38>

BI

M_A_DQ<39>

BI

M_A_DQ<40>

BI

M_A_DQ<41>

BI

M_A_DQ<42>

BI

M_A_DQ<43>

BI

M_A_DQ<44>

BI

M_A_DQ<45>

BI

M_A_DQ<46>

BI

M_A_DQ<47>

BI

M_A_DQ<48>

BI

M_A_DQ<49>

BI

M_A_DQ<50>

BI

M_A_DQ<51>

BI

M_A_DQ<52>

BI

M_A_DQ<53>

BI

M_A_DQ<54>

BI

M_A_DQ<55>

BI

M_A_DQ<56>

BI

M_A_DQ<57>

BI

M_A_DQ<58>

BI

M_A_DQ<59>

BI

M_A_DQ<60>

BI

M_A_DQ<61>

BI

M_A_DQ<62>

BI

M_A_DQ<63>

BI

CPUDDR_WR_VREF1

CPUDDR_WR_VREF2

AR15

AT14

AM14

AN14

AT15

AR14

AN15

AM15

AJ10

AK10

Haswell rPGA EDS

SA_DQ_0

SA_DQ_1

SA_DQ_2

SA_DQ_3

SA_DQ_4

SA_DQ_5

SA_DQ_6

SA_DQ_7

AM9

SA_DQ_8

AN9

SA_DQ_9

AM8

SA_DQ_10

AN8

SA_DQ_11

AR9

SA_DQ_12

AT9

SA_DQ_13

AR8

SA_DQ_14

AT8

SA_DQ_15

AJ9

SA_DQ_16

AK9

SA_DQ_17

AJ6

SA_DQ_18

AK6

SA_DQ_19

SA_DQ_20

SA_DQ_21

AJ7

SA_DQ_22

AK7

SA_DQ_23

AF4

SA_DQ_24

AF5

SA_DQ_25

AF1

SA_DQ_26

AF2

SA_DQ_27

AG4

SA_DQ_28

AG5

SA_DQ_29

AG1

SA_DQ_30

AG2

SA_DQ_31

J1

SA_DQ_32

J2

SA_DQ_33

J5

SA_DQ_34

H5

SA_DQ_35

H2

SA_DQ_36

H1

SA_DQ_37

J4

SA_DQ_38

H4

SA_DQ_39

F2

SA_DQ_40

F1

SA_DQ_41

D2

SA_DQ_42

D3

SA_DQ_43

D1

SA_DQ_44

F3

SA_DQ_45

C3

SA_DQ_46

B3

SA_DQ_47

B5

SA_DQ_48

E6

SA_DQ_49

A5

SA_DQ_50

D6

SA_DQ_51

D5

SA_DQ_52

E5

SA_DQ_53

B6

SA_DQ_54

A6

SA_DQ_55

E12

SA_DQ_56

D12

SA_DQ_57

B11

SA_DQ_58

A11

SA_DQ_59

E11

SA_DQ_60

D11

SA_DQ_61

B12

SA_DQ_62

A12

SA_DQ_63

AM3

SM_VREF

F16

SA_DIMM_VREFDQ

F13

SB_DIMM_VREFDQ

LOTES_AZIF0012_P001B_947P

6 5

CN4500

VSS

AC7

M_CLK_DDR0_DN

U4

M_CLK_DDR0_DP

V4

M_CKE0

AD9

M_CLK_DDR1_DN

U3

M_CLK_DDR1_DP

V3

M_CKE1

AC9

U2

V2

AD8

U1

V1

AC8

M_CS#0

M7

M_CS#1

L9

M9

M10

M_ODT0

M8

M_ODT1

L7

L8

L10

M_A_BS0

V5

M_A_BS1

U5

M_A_BS2

AD1

V10

M_A_RAS#

U6

M_A_WE#

U7

M_A_CAS#

U8

M_A_A<0>

V8

M_A_A<1>

AC6

M_A_A<2>

V9

M_A_A<3>

U9

M_A_A<4>

AC5

M_A_A<5>

AC4

M_A_A<6>

AD6

M_A_A<7>

AC3

M_A_A<8>

AD5

M_A_A<9>

AC2

M_A_A<10>

V6

M_A_A<11>

AC1

M_A_A<12>

AD4

M_A_A<13>

V7

M_A_A<14>

AD3

M_A_A<15>

AD2

M_A_DQS0_DN

AP15

M_A_DQS1_DN

AP8

M_A_DQS2_DN

AJ8

M_A_DQS3_DN

AF3

M_A_DQS4_DN

J3

M_A_DQS5_DN

E2

M_A_DQS6_DN

C5

M_A_DQS7_DN

C11

M_A_DQS0_DP

AP14

M_A_DQS1_DP

AP9

M_A_DQS2_DP

AK8

M_A_DQS3_DP

AG3

M_A_DQS4_DP

H3

M_A_DQS5_DP

E3

M_A_DQS6_DP

C6

M_A_DQS7_DP

C12

RSVD_AC7

SA_CK_N_0

SA_CK_P_0

SA_CKE_0

SA_CK_N_1

SA_CK_P_1

SA_CKE_1

SA_CK_N_2

SA_CK_P_2

SA_CKE_2

SA_CK_N_3

SA_CK_P_3

SA_CKE_3

SA_CS_N_0

SA_CS_N_1

SA_CS_N_2

SA_CS_N_3

SA_ODT_0

SA_ODT_1

SA_ODT_2

SA_ODT_3

SA_BS_0

SA_BS_1

SA_BS_2

SA_RAS*

SA_WE*

SA_CAS*

SA_MA_0

SA_MA_1

SA_MA_2

SA_MA_3

SA_MA_4

SA_MA_5

SA_MA_6

SA_MA_7

SA_MA_8

SA_MA_9

SA_MA_10

SA_MA_11

SA_MA_12

SA_MA_13

SA_MA_14

SA_MA_15

SA_DQS_N_0

SA_DQS_N_1

SA_DQS_N_2

SA_DQS_N_3

SA_DQS_N_4

SA_DQS_N_5

SA_DQS_N_6

SA_DQS_N_7

SA_DQS_P_0

SA_DQS_P_1

SA_DQS_P_2

SA_DQS_P_3

SA_DQS_P_4

SA_DQS_P_5

SA_DQS_P_6

SA_DQS_P_7

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

4

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

M_B_DQ<0>

M_B_DQ<1>

M_B_DQ<2>

M_B_DQ<3>

M_B_DQ<4>

M_B_DQ<5>

M_B_DQ<6>

M_B_DQ<7>

M_B_DQ<8>

M_B_DQ<9>

M_B_DQ<10>

M_B_DQ<11>

M_B_DQ<12>

M_B_DQ<13>

M_B_DQ<14>

M_B_DQ<15>

M_B_DQ<16>

M_B_DQ<17>

M_B_DQ<18>

M_B_DQ<19>

M_B_DQ<20>

M_B_DQ<21>

M_B_DQ<22>

M_B_DQ<23>

M_B_DQ<24>

M_B_DQ<25>

M_B_DQ<26>

M_B_DQ<27>

M_B_DQ<28>

M_B_DQ<29>

M_B_DQ<30>

M_B_DQ<31>

M_B_DQ<32>

M_B_DQ<33>

M_B_DQ<34>

M_B_DQ<35>

M_B_DQ<36>

M_B_DQ<37>

M_B_DQ<38>

M_B_DQ<39>

M_B_DQ<40>

M_B_DQ<41>

M_B_DQ<42>

M_B_DQ<43>

M_B_DQ<44>

M_B_DQ<45>

M_B_DQ<46>

M_B_DQ<47>

M_B_DQ<48>

M_B_DQ<49>

M_B_DQ<50>

M_B_DQ<51>

M_B_DQ<52>

M_B_DQ<53>

M_B_DQ<54>

M_B_DQ<55>

M_B_DQ<56>

M_B_DQ<57>

M_B_DQ<58>

M_B_DQ<59>

M_B_DQ<60>

M_B_DQ<61>

M_B_DQ<62>

M_B_DQ<63>

3 2 1

AR18

AT18

AM17

AM18

AR17

AT17

AN17

AN18

AT12

AR12

AN12

AM11

AT11

AR11

AM12

AN11

AR5

AR6

AM5

AM6

AN5

AN6

AM1

AN1

AK1

Haswell rPGA EDS

SB_DQ_0

SB_DQ_1

SB_DQ_2

SB_DQ_3

SB_DQ_4

SB_DQ_5

SB_DQ_6

SB_DQ_7

SB_DQ_8

SB_DQ_9

SB_DQ_10

SB_DQ_11

SB_DQ_12

SB_DQ_13

SB_DQ_14

SB_DQ_15

SB_DQ_16

SB_DQ_17

SB_DQ_18

SB_DQ_19

AT5

SB_DQ_20

AT6

SB_DQ_21

SB_DQ_22

SB_DQ_23

AJ4

SB_DQ_24

AK4

SB_DQ_25

AJ1

SB_DQ_26

AJ2

SB_DQ_27

SB_DQ_28

SB_DQ_29

AK2

SB_DQ_30

SB_DQ_31

L2

SB_DQ_32

M2

SB_DQ_33

L4

SB_DQ_34

M4

SB_DQ_35

L1

SB_DQ_36

M1

SB_DQ_37

L5

SB_DQ_38

M5

SB_DQ_39

G7

SB_DQ_40

J8

SB_DQ_41

G8

SB_DQ_42

G9

SB_DQ_43

J7

SB_DQ_44

J9

SB_DQ_45

G10

SB_DQ_46

J10

SB_DQ_47

A8

SB_DQ_48

B8

SB_DQ_49

A9

SB_DQ_50

B9

SB_DQ_51

D8

SB_DQ_52

E8

SB_DQ_53

D9

SB_DQ_54

E9

SB_DQ_55

E15

SB_DQ_56

D15

SB_DQ_57

A15

SB_DQ_58

B15

SB_DQ_59

E14

SB_DQ_60

D14

SB_DQ_61

A14

SB_DQ_62

B14

SB_DQ_63

RSVD

SB_CKN0

SB_CK0

SB_CKE_0

SB_CKN1

SB_CK1

SB_CKE_1

SB_CKN2

SB_CK2

SB_CKE_2

SB_CKN3

SB_CK3

SB_CKE_3

SB_CS_N_0

SB_CS_N_1

SB_CS_N_2

SB_CS_N_3

SB_ODT_0

SB_ODT_1

SB_ODT_2

SB_ODT_3

SB_BS_0

SB_BS_1

SB_BS_2

SB_RAS*

SB_WE*

SB_CAS*

SB_MA_0

SB_MA_1

SB_MA_2

SB_MA_3

SB_MA_4

SB_MA_5

SB_MA_6

SB_MA_7

SB_MA_8

SB_MA_9

SB_MA_10

SB_MA_11

SB_MA_12

SB_MA_13

SB_MA_14

SB_MA_15

SB_DQS_N_0

SB_DQS_N_1

SB_DQS_N_2

SB_DQS_N_3

SB_DQS_N_4

SB_DQS_N_5

SB_DQS_N_6

SB_DQS_N_7

SB_DQS_P_0

SB_DQS_P_1

SB_DQS_P_2

SB_DQS_P_3

SB_DQS_P_4

SB_DQS_P_5

SB_DQS_P_6

SB_DQS_P_7

CN4500

VSS

AG8

Y4

AA4

AF10

Y3

AA3

AG10

Y2

AA2

AG9

Y1

AA1

AF9

P4

R2

P3

P1

R4

R3

R1

P2

R7

P8

AA9

R10

R6

P6

P7

R8

Y5

Y10

AA5

Y7

AA6

Y6

AA7

Y8

AA10

R9

Y9

AF7

P9

AA8

AG7

AP18

AP11

AP5

AJ3

L3

H9

C8

C14

AP17

AP12

AP6

AK3

M3

H8

C9

C15

M_CLK_DDR2_DN

M_CLK_DDR2_DP

M_CKE2

M_CLK_DDR3_DN

M_CLK_DDR3_DP

M_CKE3

M_CS#2

M_CS#3

M_ODT2

M_ODT3

M_B_BS0

M_B_BS1

M_B_BS2

M_B_RAS#

M_B_WE#

M_B_CAS#

M_B_A<0>

M_B_A<1>

M_B_A<2>

M_B_A<3>

M_B_A<4>

M_B_A<5>

M_B_A<6>

M_B_A<7>

M_B_A<8>

M_B_A<9>

M_B_A<10>

M_B_A<11>

M_B_A<12>

M_B_A<13>

M_B_A<14>

M_B_A<15>

M_B_DQS0_DN

M_B_DQS1_DN

M_B_DQS2_DN

M_B_DQS3_DN

M_B_DQS4_DN

M_B_DQS5_DN

M_B_DQS6_DN

M_B_DQS7_DN

M_B_DQS0_DP

M_B_DQS1_DP

M_B_DQS2_DP

M_B_DQS3_DP

M_B_DQS4_DP

M_B_DQS5_DP

M_B_DQS6_DP

M_B_DQS7_DP

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

23

23

23

23

23

23

D

23

23

23

23

23

23

23

23

23

23

23

BI

23

BI

23

BI

23

BI

23

BI

23

BI

23

BI

23

BI

23

BI

23

BI

23

BI

23

BI

23

BI

23

BI

23

BI

23

BI

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

CC

B

LOTES_AZIF0012_P001B_947P

CN4500

6026B0231701

M3 : CHANNEL A DQ

18

IN

CPUDDR_WR_VREF1

R4549

8

R4552

0_5%_2 0_5%_2

2

G

2 1

1

CPUDDR_WR_VREF1_M

21

3

D S

Q4553

PMV56XN_DY

PCH_DDR_RST

16 18

IN

7 6

07dc0c1a02352f034a005270e0005460

25 34

18

CPUDDR_WR_VREF2

IN

1K_5%_2_DY1K_5%_2_DY

M3 : CHANNEL B DQ

R4554

0_5%_2

2

R4550

2 1

G

1

21

3

D S

Q4555

PMV56XN_DY PMV56XN_DY

PCH_DDR_RST

16 18

IN

P0V675M_VREF_HCPUDDR_WR_VREF2_M

20/20 mil

25 34

M3 : 2 CHANNEL CA

R4556

21

2

R4551

2 1

3

CPUDDR_CA_VREF1_M

D S

Q4663

G

1

1K_1%_2_DY

5 4

CHANGE by

PCH_DDR_RST

XXX

OUT

IN

22

16 18

DATE

25 34

21-OCT-2002

23

INVENTEC

TITLE

MODEL,PROJECT,FUNCTION

Block Diagram

DOC.NUMBER

CODE

SIZE

1310xxxxx-0-0

CS

A3

SHEET

of

7018

1

REV

A01

AA

Page 19

07dc0c1a02352f034a005270e0005460

8 7

6 5

4

3 2 1

CPU

LOCATION 4500-4699

VER.01_20120808

D

NA

CHECK! intel seems to disable CPU S3 power reduction.

P1V35

+

C4566

6010B0106701

C4568

2 1

330UF_2.5V

C4569

C4567

2 1

22uF_6.3V_5

PVCCIOA_OUT PVCCIO_OUTP1V05S_PCH

6010B0140601

PVCORE

B

C4633

2

R4570

2 1

OUT

OUT

OUT

VR_SVID_ALERT#

VR_SVID_CLK

VR_SVID_DATA

PVCCIO_OUT

R4505

R4589

11

11

11

1

+

470UF_2V

3

OPEN

0_5%_2_DY

R4573

0_5%_3

2 1

PVCCIO_OUT_R

PVCCIO2PCH_R

21

75_1%_2

21

130_1%_2

11

R4581

R4582

R4583

OUT

100_1%_2

VCCSENSE

2 1

2 1

2 1

P1V05S_PCH

close to CPU

P1V5S_DGPU

C6266

21

C6270

21

22UF_6.3V_5

C6267

21

22UF_6.3V_5

C6271

21

22UF_6.3V_5

C6268

21

22UF_6.3V_5

C6272

21

22UF_6.3V_5

C6269

21

22UF_6.3V_5

22UF_6.3V_5

C6273

21

22UF_6.3V_5

8

7 6

07dc0c1a02352f034a005270e0005460

2 1

2 1

R4586

10uF_6.3V_3

C4572

22uF_6.3V_5

PVCORE

43_1%_2

0_5%_2

0_5%_2

PV

C4571

2 1

2 1

2 1

150_1%_3

10uF_6.3V_3

22uF_6.3V_5_DY

PV

R4572

C4575

2 1

22uF_6.3V_5_DY

PVCORE

PV

close to CPU

R4594

2 1

SHORT_0402_5

H_CPU_SVIDALRT#

H_CPU_SVIDCLK

H_CPU_SVIDDAT

21

PVCORE

VCCSENSE_R

PWR_DEBUG#

CN4500

Haswell rPGA EDS

K27

RSVD

L27

RSVD

T27

RSVD

V27

RSVD

AB11

VDDQ

AB2

VDDQ

AB5

VDDQ

AB8

VDDQ

AE11

VDDQ

AE2

VDDQ

AE5

VDDQ

AE8

VDDQ

AH11

VDDQ

K11

VDDQ

N11

VDDQ

N8

VDDQ

T11

VDDQ

T2

VDDQ

T5

VDDQ

T8

VDDQ

W11

VDDQ

W2

VDDQ

W5

VDDQ

W8

VDDQ

N26

RSVD

K26

VCC

AL27

RSVD

AK27

RSVD

AL35

VCC_SENSE

E17

RSVD

AN35

VCCIO_OUT

A23

RSVD

F22

VCOMP_OUT

W32

RSVD

AL16

RSVD

J27

RSVD

AL13

RSVD

AM28

VIDALERT*

AM29

VIDSCLK

AL28

VIDSOUT

AP35

VSS

H27

PWR_DEBUG

AP34

VSS

AT35

RSVD_TP

AR35

RSVD_TP

AR32

IVR_ERROR

AL26

RSVD_TP

AT34

VSS

AL22

VSS

AT33

VSS

AM21

VSS

AM25

VSS

AM22

VSS

AM20

VSS

AM24

VSS

AL19

VSS

AM23

VSS

AT32

VSS

Y25

VCC

Y26

VCC

Y27

VCC

Y28

VCC

Y29

VCC

Y30

VCC

Y31

VCC

Y32

VCC

Y33

VCC

Y34

VCC

Y35

VCC

LOTES_AZIF0012_P001B_947P

5 4

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

AA26

AA28

AA34

AA30

AA32

AB26

AB29

AB25

AB27

AB28

AB30

AB31

AB33

AB34

AB32

AC26

AB35

AC28

AD25

AC30

AD28

AC32

AD31

AC34

AD34

AD26

AD27

AD29

AD30

AD32

AD33

AD35

AE26

AE32

AE28

AE30

AG28

AG34

AE34

AF25

AF26

AF27

AF28

AF29

AF30

AF31

AF32

AF33

AF34

AF35

AG26

AH26

AH29

AG30

AG32

AH32

AH35

AH25

AH27

AH28

AH30

AH31

AH33

AH34

AJ25

AJ26

AJ27

AJ28

AJ29

AJ30

AJ31

AJ32

AJ33

AJ34

AJ35

G25

H25

J25

K25

L25

M25

N25

P25

R25

T25

U25

U26

V25

V26

W26

W27

PVCORE

C4601

C4599

22uF_6.3V_5

2 1

C4600

22uF_6.3V_5

2 1

CHANGE by

2 1

22uF_6.3V_5

+

C4598

100UF_6.3V

C4604

22uF_6.3V_5

2 1

C4605

22uF_6.3V_5 22uF_6.3V_5

2 1

XXX

C4607

C4608

2 1

2 1

2 1

2 1

22uF_6.3V_5

22uF_6.3V_5

22uF_6.3V_5

22uF_6.3V_5

2 1

2 1

22uF_6.3V_5

C4620

C4619

C4614

C4613

C4626

C4628

2 1

2 1

22uF_6.3V_5

22uF_6.3V_5

22uF_6.3V_5

D

12

+

C4602

100UF_6.3V

C4609

22uF_6.3V_5

2 1

C4610