Inventec Phoenix10 Schematics

Sacramento 10

Phoenix 10

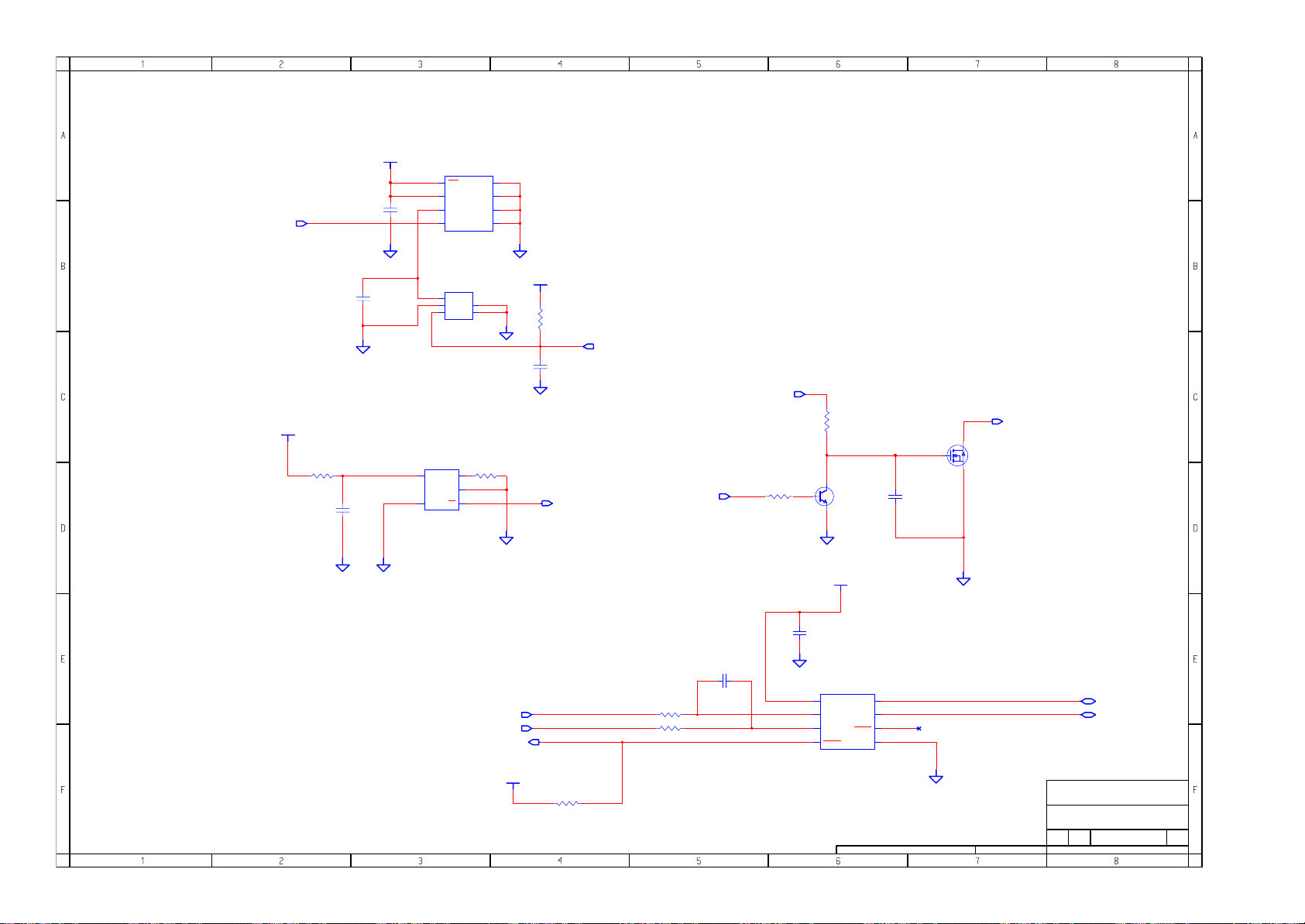

CS_BUILD

2008.02.29

DATE CHANGE NO.

REV

DRAWER

DESIGN

CHECK

RESPONSIBLE

SIZE =

FILE NAME :

XXXXXXXXXXXX

P/N

EE

3

XXXX-XXXXXX-XX

DATE

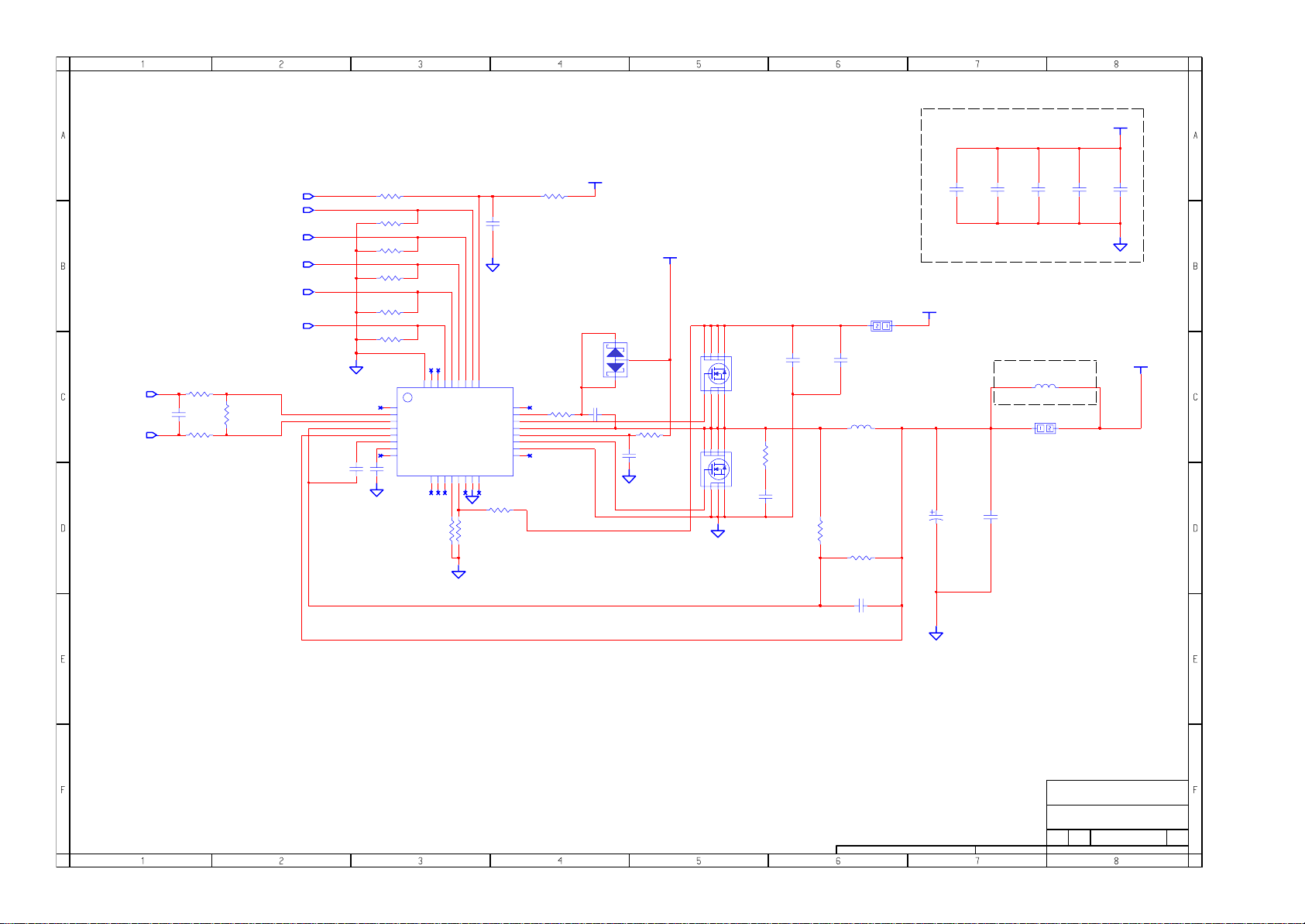

POWER

VER :

DATE

INVENTEC

TITLE

PS10

CODE

SIZE

A3

DOC. NUMBER

Model_No X01

CS

SHEET OF

REV

621

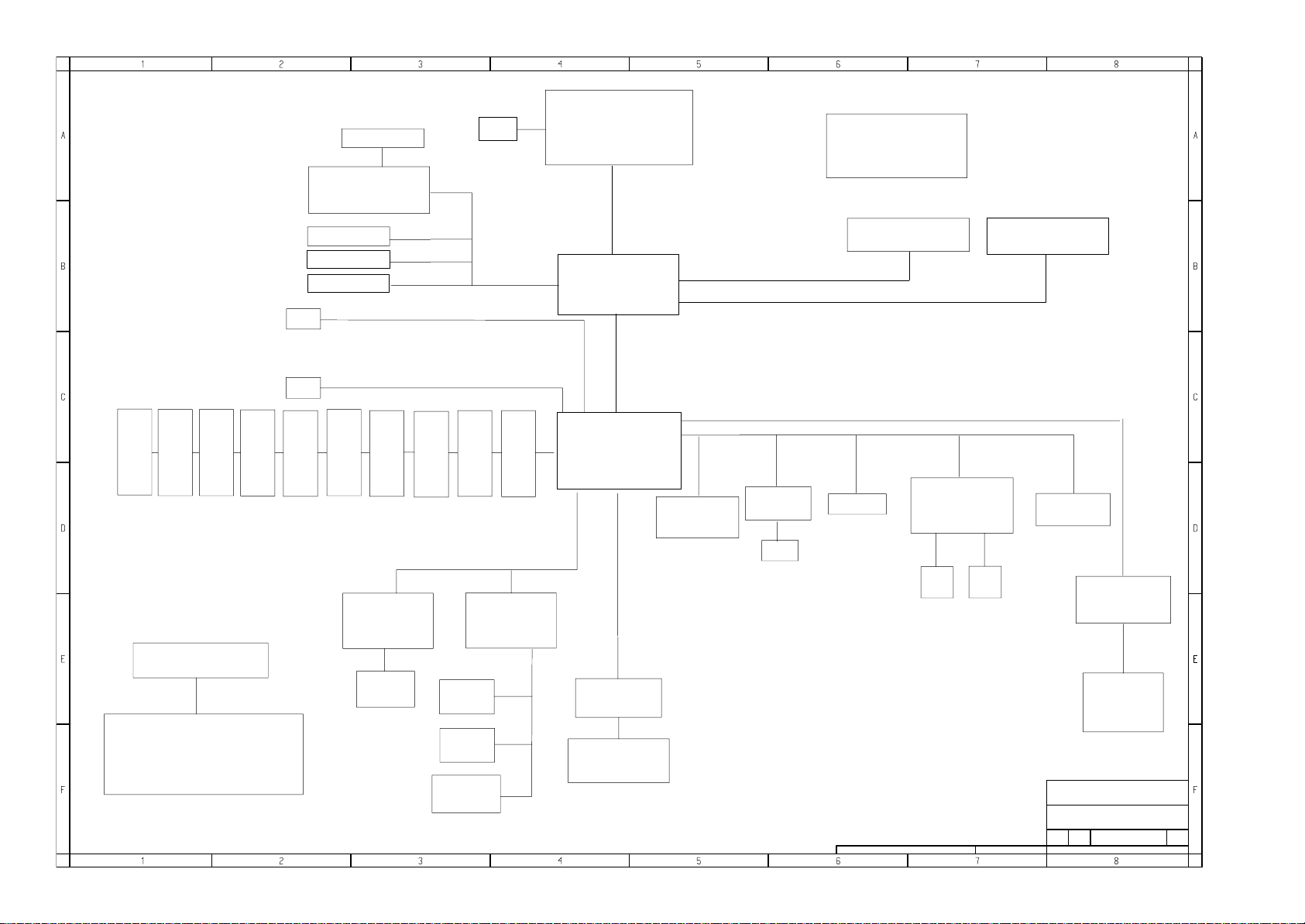

TABLE OF CONTENTS

PAGE

1.COVER PAGE

2.INDEX

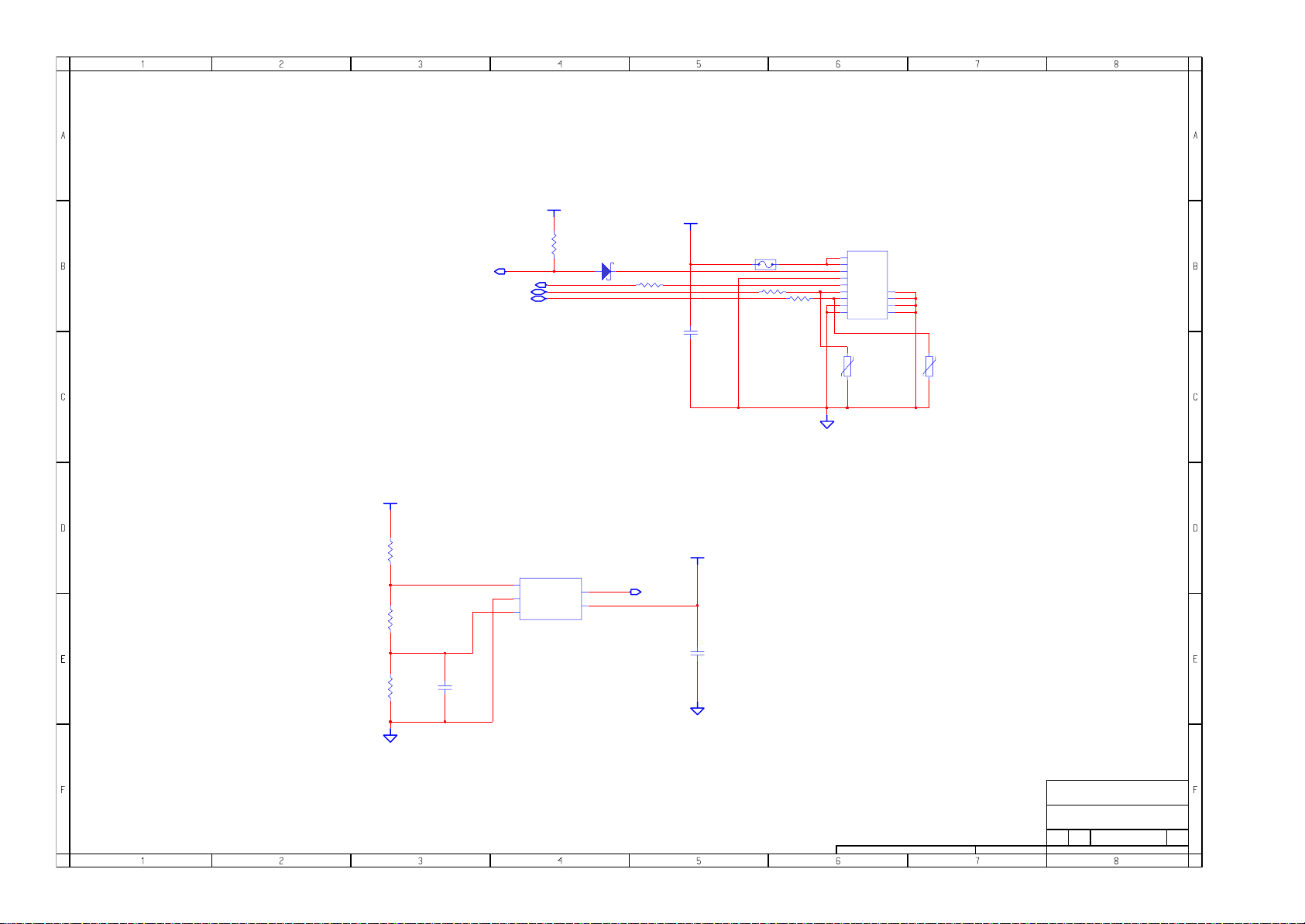

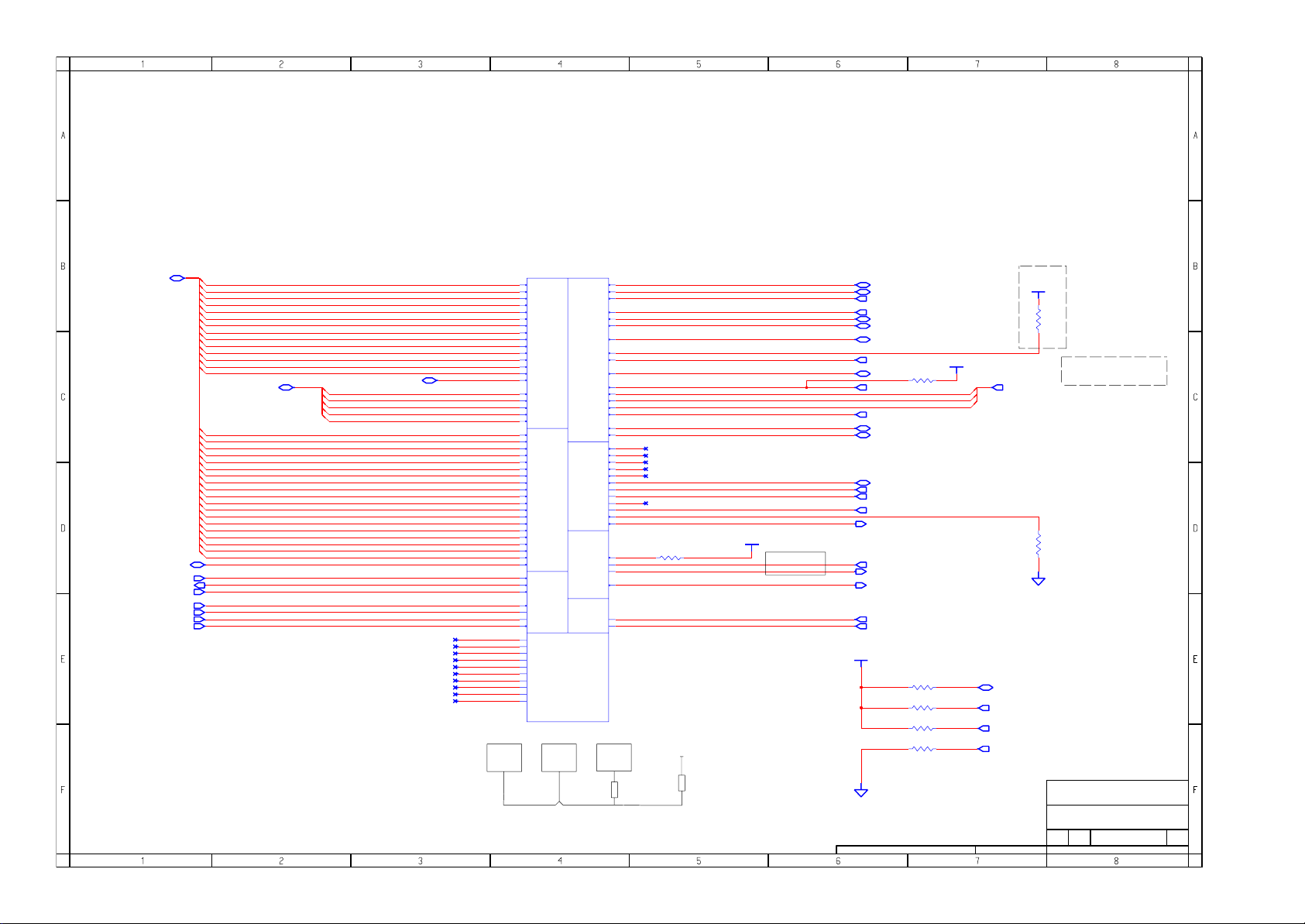

3.BLOCK DIAGRAM

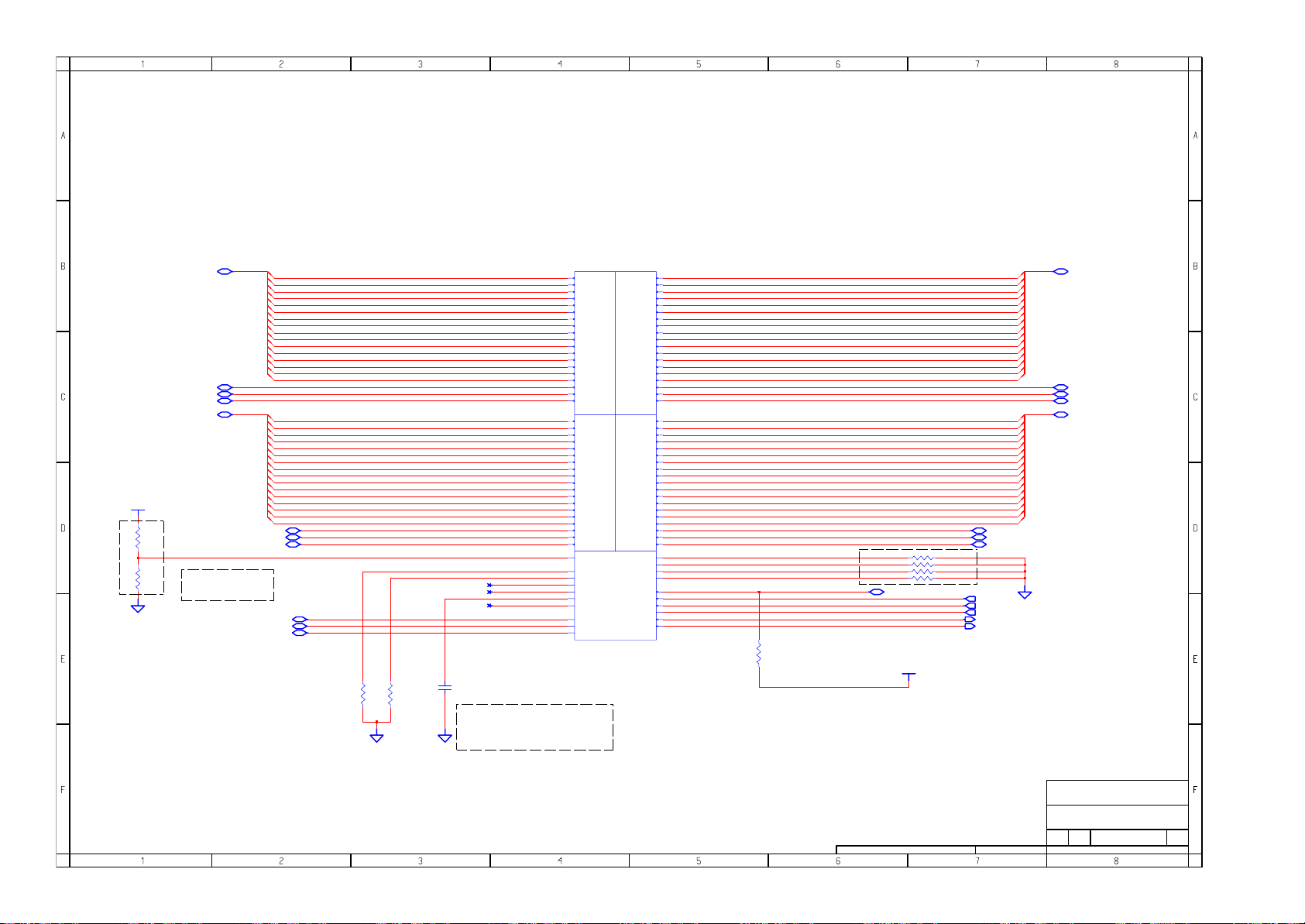

4.POWER SEQUENCE BLOCK

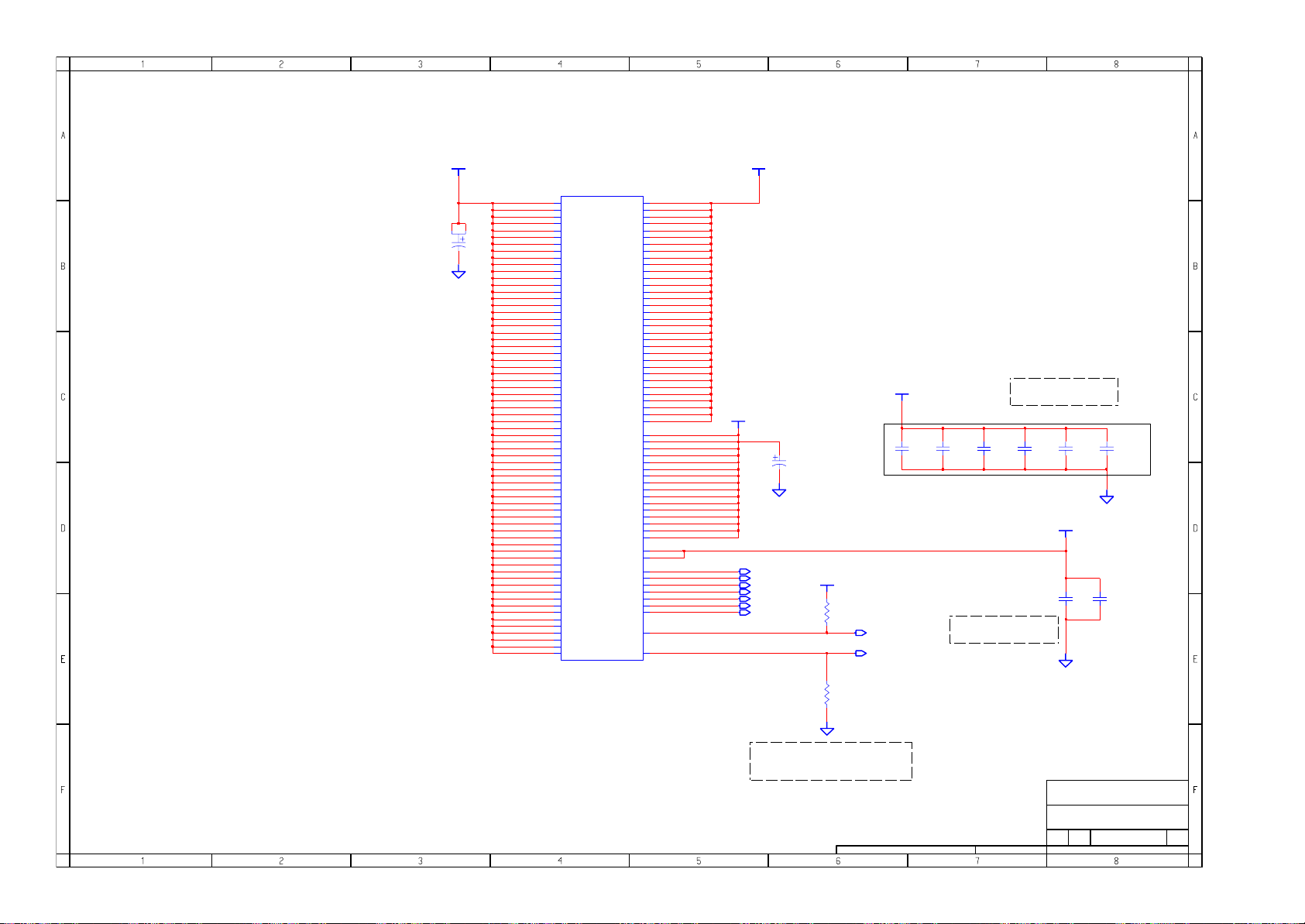

5-12.SYSTEM POWER

13.CLOCK GENERATOR

14- PENRYN-1

15- PENRYN-2

16- PENRYN-3

17- PENRYN-4

18.FAN & THERMAL CONTROLLER

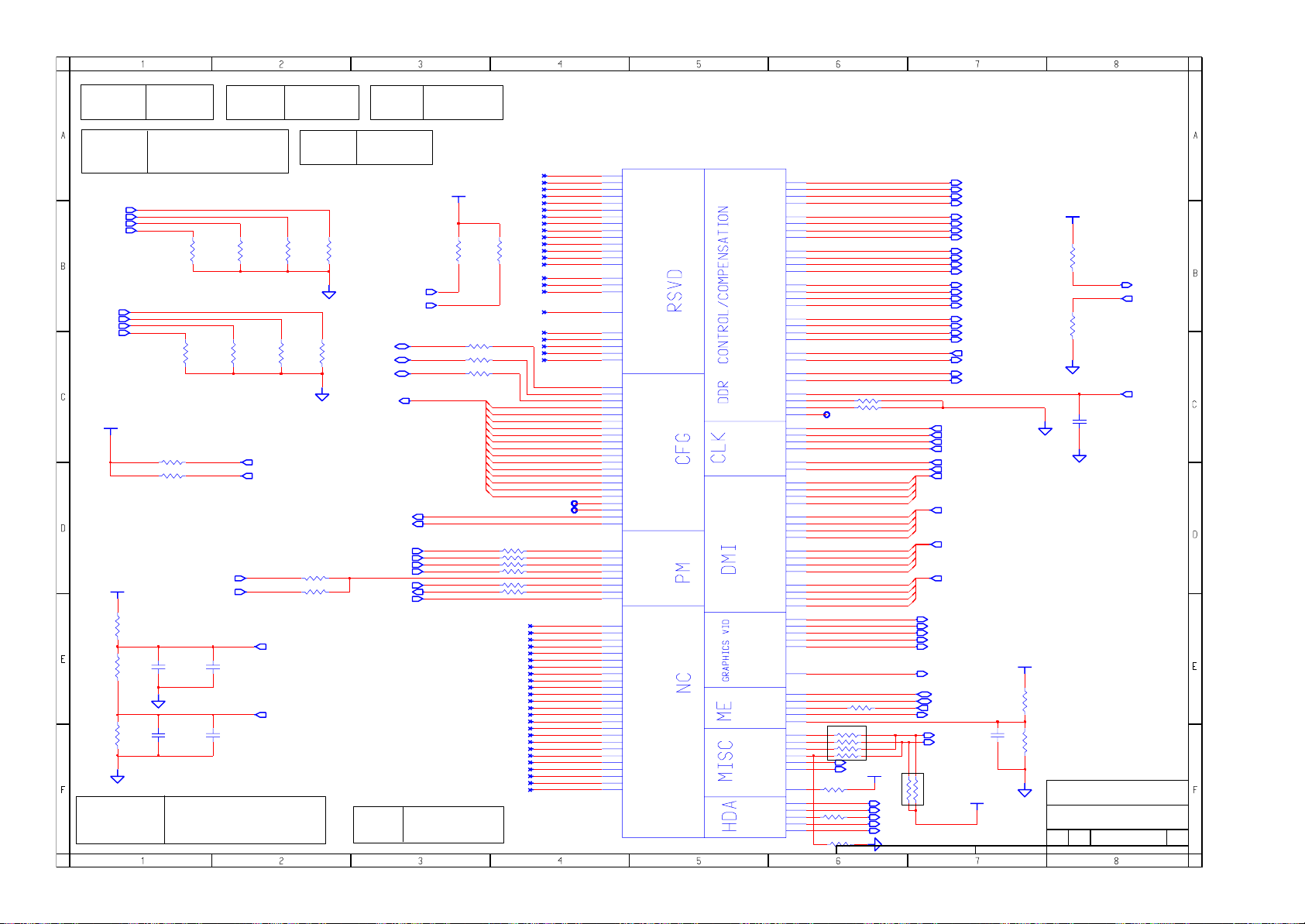

19- CANTIGA-1

20- CANTIGA-2

21- CANTIGA-3

22- CANTIGA-4

23- CANTIGA-5

24- CANTIGA-6

25- CANTIGA-7

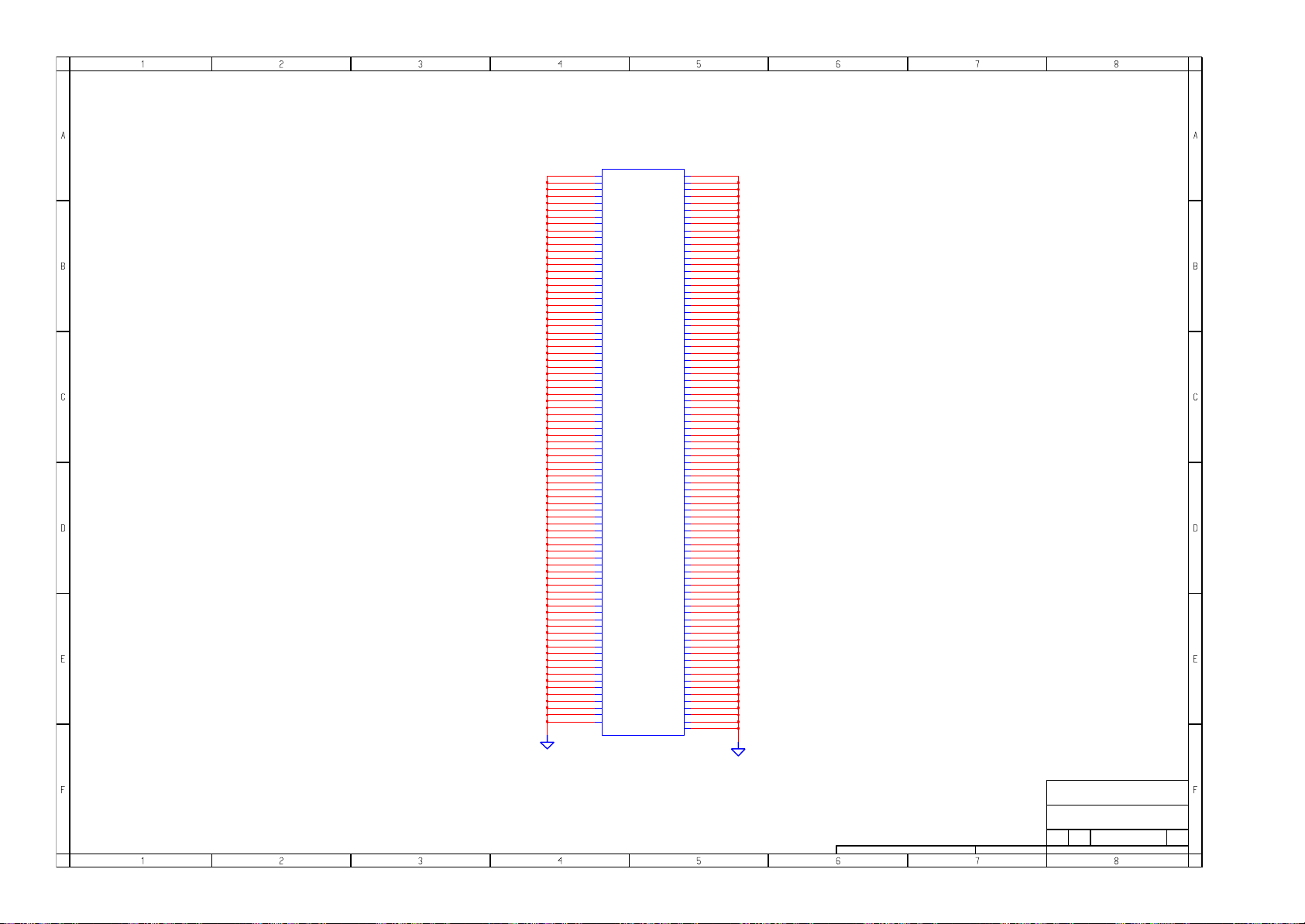

26.DDR2 DIMM0

27.DDR2 DIMM1

28.DDR DAMPING

29.MXM CONN

30.CRT CONN

31.S-VIDEO CONN

32.LCM CONN

PAGE

33- ICH9-1

34- ICH9-2

35- ICH9-3

36- ICH9-4

37- ICH9-5

38.SATA HDD1 CONN

39.ODD CONN

40.USB CONN

41.CAMERA CONN

42.BLUE TOOTH CONN

43.KBC

44.K/B & TP/B CONN

45.AZALIA CODEC

46.AUDIO AMP & MIC & HP

47.LAN CONTROLLER

48.RJ45 & TRANSFORMER

49.HDMI LEVEL SHIFTER

50.HDMI CONN

51.5 IN 1 CARD SLOT

52.PCMCIA CONTROLLER

53.PCMCIA CONN

PAGE

54.EXPRESS CARD CONN

55.ROBSON & WLAN

56.Broadcom

57.MDC 1.5 CONN

58.LED(M/B) & HOTKEY/B CONN

59.PICK BUTTON BOARD

60.KILL SWITCH& HALL SENSOR

61.DRILL HOLE

62.EMI

CHANGE by

Drawer_Name

24-Aug-2007

INVENTEC

TITLE

PS10

CODE

CS

SHEET

DOC. NUMBER

262

SIZE

A3

REV

X01Model_No

OF

HDMI CONN

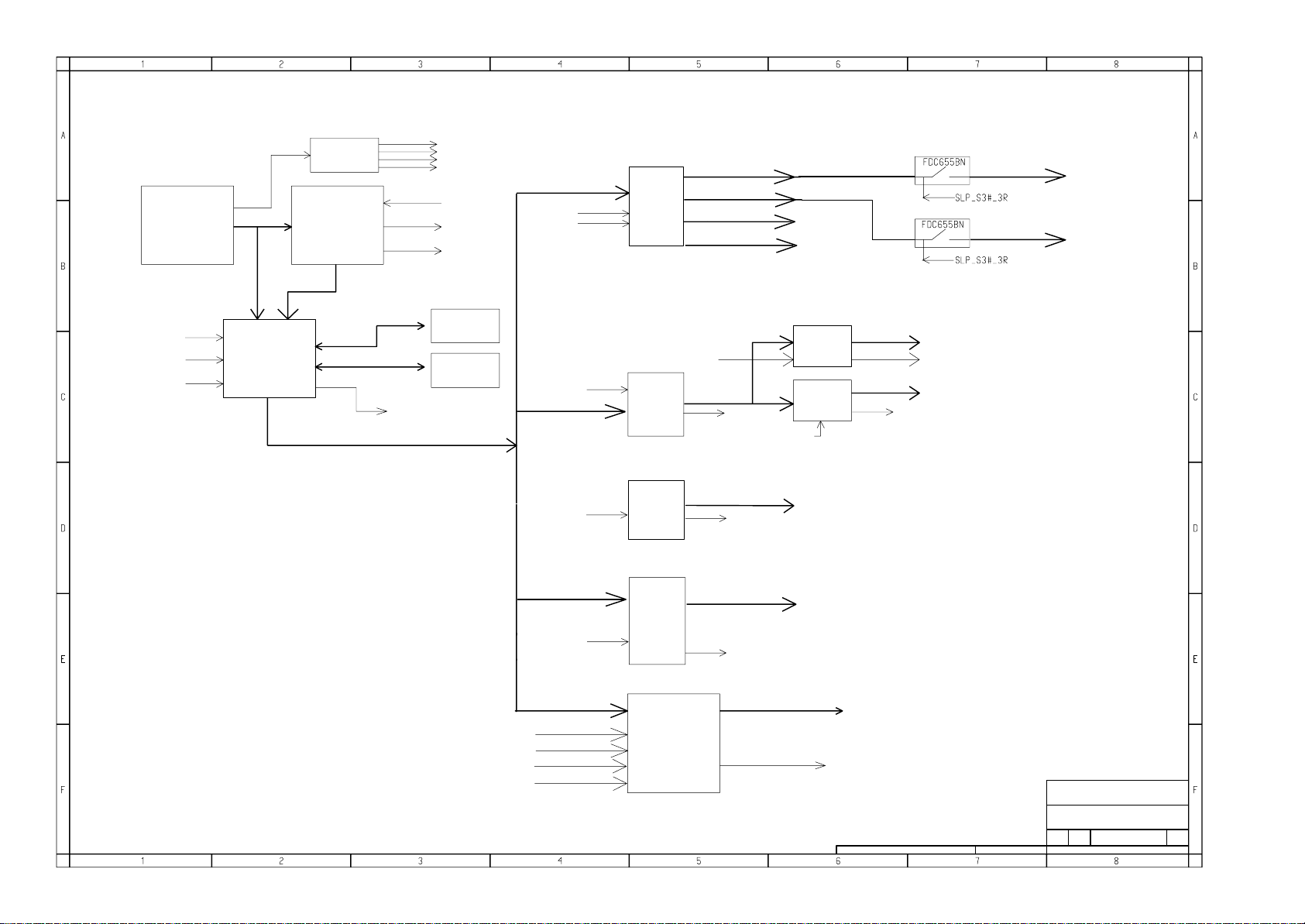

CH7318

HDMI LEVEL SHIFTER

S-video

LCM

CRT

HDD

ODD

SATA_0

SATA_5

XDP

Penryn

(uFCPGA)

FSB

677/800/1067

Cantiga

DMI

DDR2 Interface

DDR2 Interface

ICS9LPRS395

Clock generator

DDR II _SODIMM0

667/800 MHz

3.3V, PCI_Interface,33MHz

DDR II _SODIMM1

667/800 MHz

CONN

CONN

USB0

USB1

CONN

USB2

BATTERY

System Charger &

DC/DC System power

(IMVP-6

VR)

NC

USB3

USB4

NEW Card

USB5

HDDVD

MDC / Modem

Module 56K

RJ11

NC

USB6

USB8

USB7

CAMERA

1.5V, AZALIA

MIC

JACK

HP

JACK

SPEAKER

WLAN

Realtek

ALC 268

USB9

Card reader

ICH9-M

MINI CARD

3.3V, LPC_Interface,33MHz

WINBOND

WPCE775C

BIOS

SPI EEROM

Broadcom

Realtek LAN

RTL8102E

RJ45

NEWCARD

CHANGE by

MINI CARD

Wireless LAN

ANT

Drawer_Name

ANT

17-Sep-2007

MINI CARD

Robson

RICOH

R5C804

PCMCIA

CONN

INVENTEC

TITLE

PS10

CODE

CS

SHEET

DOC. NUMBER

SIZE

A3

REV

X01Model_No

OF

362

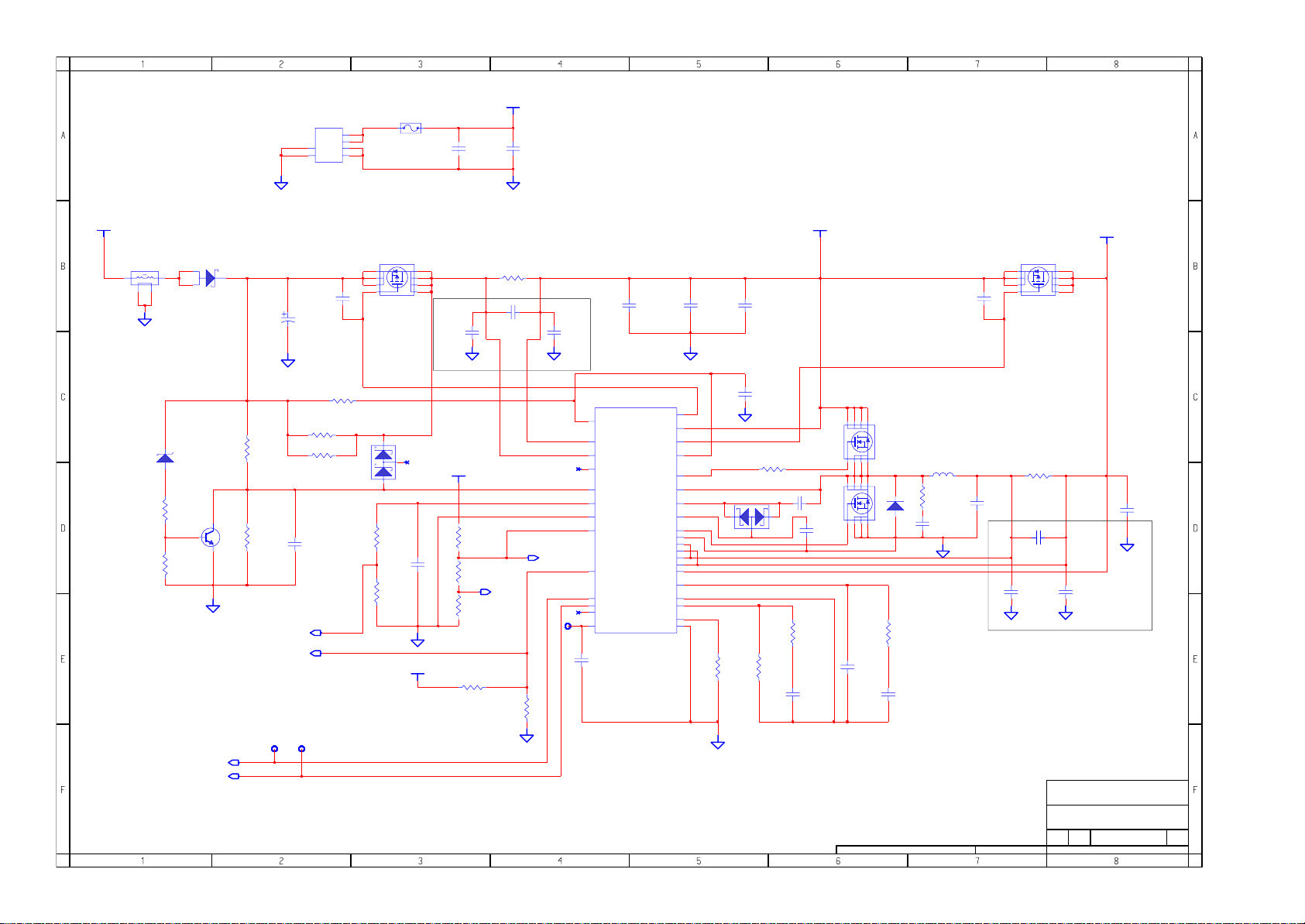

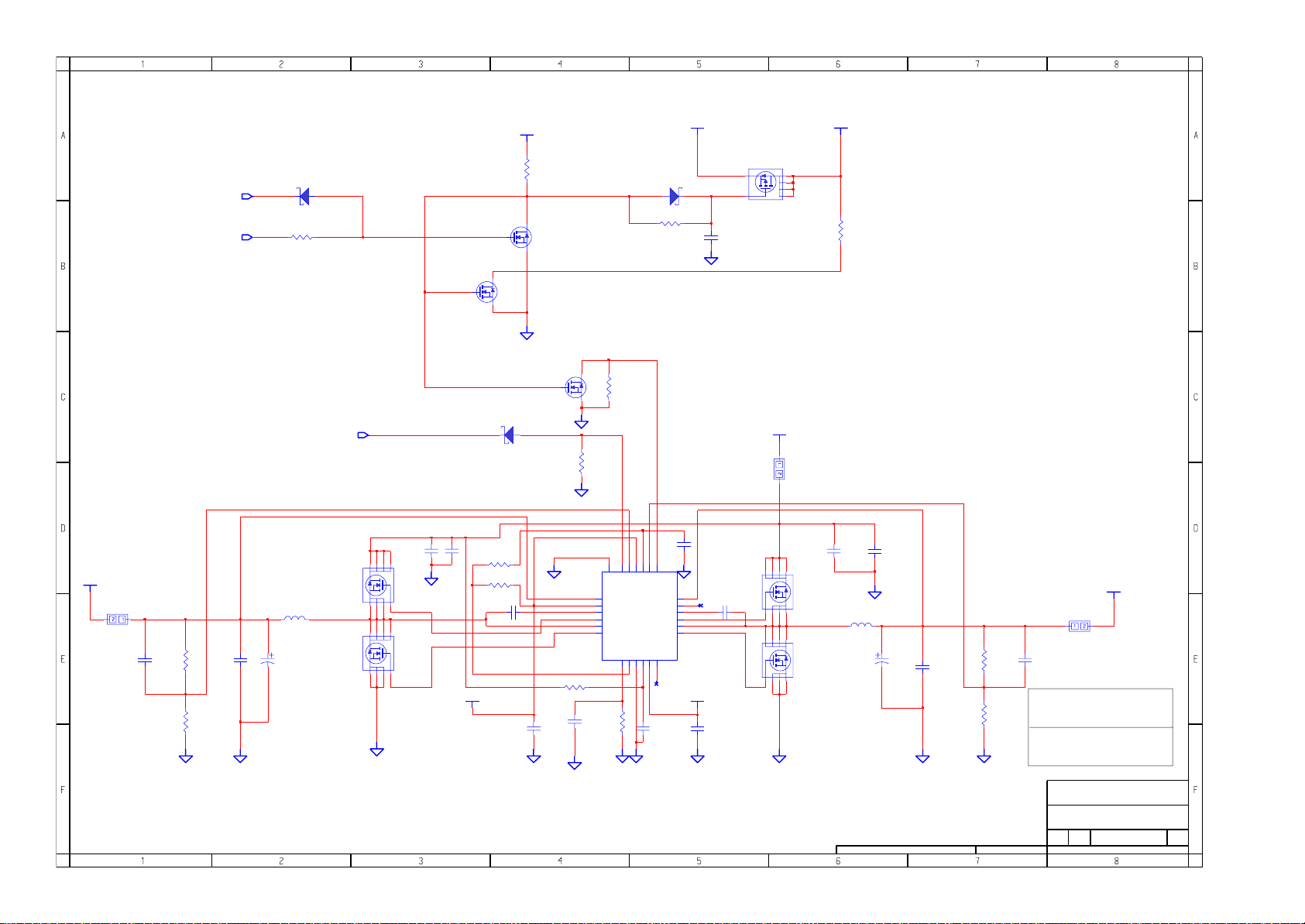

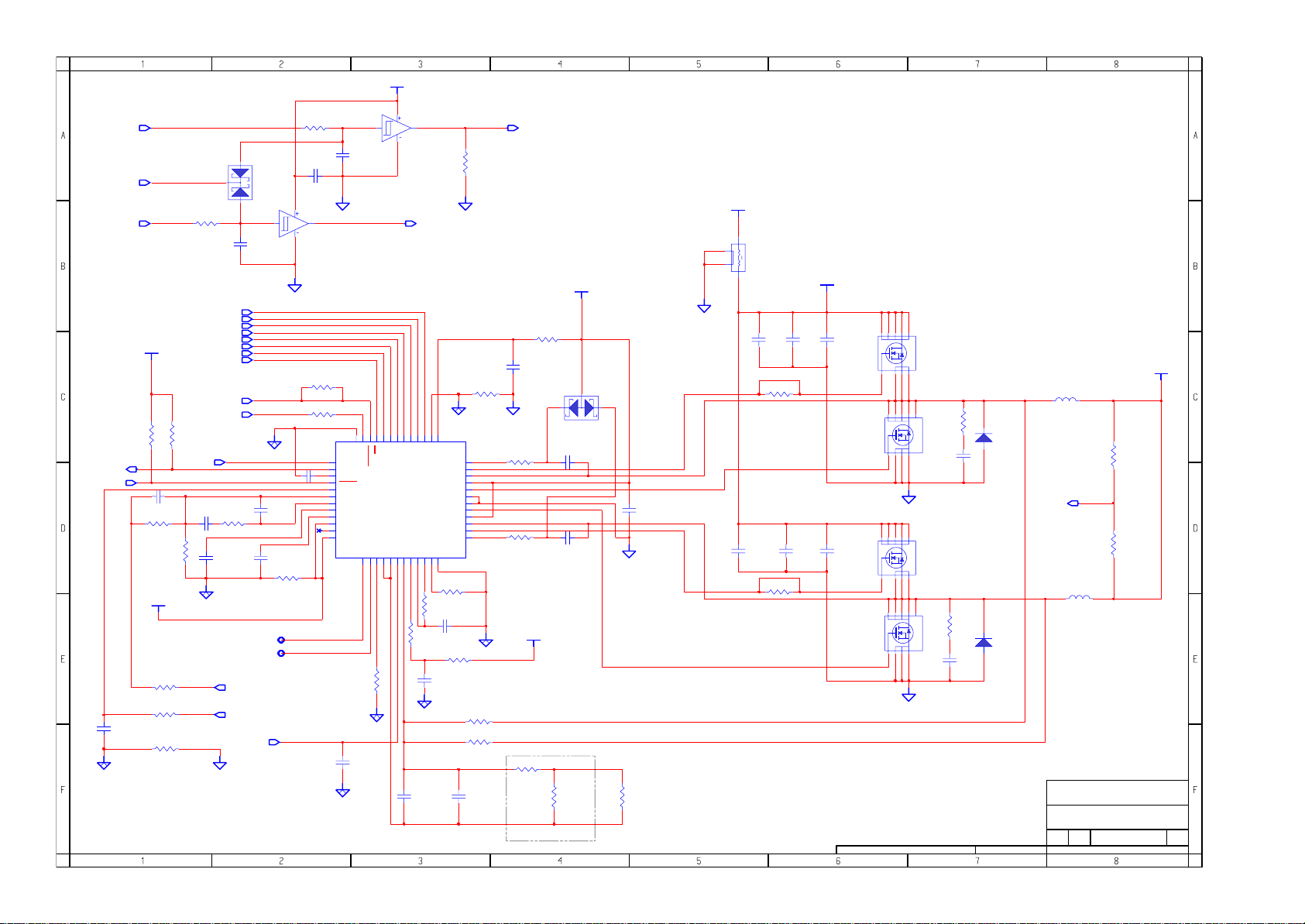

Adapter

(90W)

LIMIT_SIGNAL

+VBDC

OCP

Charger

(BQ24740)

ADP_EN

OCP_OC#

ADP_PS0

ADP_PS1

CHGCTRL_3

ADP_PRES

AC_AND_CHG

ADP_PRES

KBC_PW_ON

5/3.3V

(TPS51120)

+V5A

+V3A

+V5AL

+V3AL

+V5S

+V3S

BATSELB

AC_AND_CHG

CHGCTRL_3

Selector

(Discrete)

+VBATR

+VBATA

+VBATB SLP_S3#_3R

BATCON

Main Battery

Travel Battery

PWR_GOOD_3

PM_DPRSLPVR

PSI#

H_DPRSTP#

SLP_S4#_3R

SLP_S3#_3R

DFGT_VR_EN

IO POWER

(TPS51117)

IO POWER

(TPS51117)

GPU POWER

(ADP3209)

IMVP VI

(ADP3208)

+V1.8

+VCCP

+VGFX_CORE

V1.8_PG

VCCP_PG

VGFX_PG

SLP_S3#_3R

+VCC_CORE

LR

(G2997)

LR

(APL5913)

VR_PWRGD_CK505

CHANGE by

+V0.9S

M_VREF

+V1.5S

V1.5S_PG

Drawer_Name 24-Aug-2007

INVENTEC

TITLE

PS10

DOC. NUMBER

CODE REV

SIZE

A3

Model_No X01

CS

SHEET

OF

624

CN3

1

1

2

2

3

G

G1

3

4

G2

G

4

ACES_91302_0047L_1_4P

FUSE500

12

8A_125V

C504

1

10pF_50v

2

+VADPTR

5-

1

2

C505

0.1uF_50v

+VADPTR

5-

NFM60R30T222

ROHM_RLZ24 2

L500

12

34

D514

1

1

R521

1K_5%

2

1

MMBT3904

R523

10K_5%

2

D500

1

2

PDS1040S

1

B

Q507

EC_CLK

EC_DATA

3

R520

432K_1%

3

C

E

2

18-,43-

18-,43-

1

2

1

R522

33K_1%

2

1

2

ACPRES

CHG_EN

TP2052

0.01uF_50v12

C506

47uF_35v

C535

1

2

TP2053

C503

R537

12

10_5%

R547

12

4.7K_5%

R546

12

4.7K_5%

BAT54S_30V_0.2A

OPEN

43-

43-

D515

Q504

AM4825P_AP

1

S

2

3

4

G

2

3

1

1

R533

47K_5%

2

C533

1uF_10v

1

R531

100K_5%

2

8

D

7

6

5

1

2

+V5LA

5-,6-,7-,12-,18-,50-

C519

+V5LA

5-,6-,7-,12-,18-,50-

1

2

1

2

1

2

R535

1

100K_5%

1

2

R542

8.06K_1%

R544

39.2K_1%

43-

R541

22.6K_1%

R524

12

0.01_1%_1W

C536

12

0.1uF_25v

NEAR IC

BATT_IN

2

R536

200K_5%

+VBAT

6-,7-,8-,9-,10-,11-

Q500

1

S

2

3

0.01uF_50v12

L504

12

1

R525

4.7_5%

2

1

C521

2200pF_50v

2

C1

C510

1

2

10uF_25v_K_X5R

ACDRV#

BATDRV#

PVCC

HIDRV

BTST

REGN

LODRV

PGND

SYNP

SYNN

ISYNSET

C509

1

2

0.1uF_25v

2

23

SYS

24

32

30

29

PH

31

28

27

26

22

21

20

SRP

19

SRN

18

BAT

7

EAO

8

EAI

9

FBO

16

33

TML

C508

1

2

C520

1

20.1uF_25v

0.1uF_25v

10uF_25v_K_X5R

U502

12

VCC

3

ACN

4

ACP

6

BYPASS#

5

ACDET

11

VREF5

10

AGND

15

TS

6-

THRM1

1

CHGEN#

14

SCL

13

SDA

25

ALARM#

TP2040

17

IOUT

TI_BQ24721C_QFN_32P

C9491

OPEN

2

1

C507

1

2

10uF_25v_K_X5R

C537

1

4.7uF_25v

2

NEAR IC

12

D517

12

3

BAT54AW

1

1

R545

100K_5%

2

2

R6002

2.2_5%

C538

R532

200K_5%

12

1

R530

18K_5%

2

C531

1

2

100pF_50v

0.1uF_25v

C539

1

1uF_10v

2

G

41S23

G

4

C534

1

2

65

87

D

7

65

8

D

1S23

56pF_50v

Q508

FDS8884

PLC0755P_10uH_3.9A

Q510

FDS8884

D516

SSM34_3A40V_OPEN

21

1

R534

10K_5%

2

C532

1

1500pF_50v

2

AM4825P_AP

12

0.01_1%_1W

C545

0.1uF_25v

NEAR IC

C546

1

2

0.1uF_25v

G

R526

12

D

8

7

6

54

C544

1

0.22uF_25v

2

+VPACK

6-

C511

1

10uF_25v_K_X5R

2

2

INVENTEC

TITLE

PS10

SIZE

CODE DOC. NUMBER

A3

CHANGE by SHEET

Drawer_Name 24-Aug-2007

CS

Model_No X01

REV

OF

625

+VBAT

5-,7-,8-,9-,10-,11-

1

R102

1M_5%

2

1

R103

56.2K_1%

2

1

R104

180K_1%

2

+V3LA

7-,12-,18-,33-,40-,43-,50-,58-,60-

1

R502

47K_5%

CHENMKO_BAT54_3P_OPEN

43-

BAT_ID

BATT_DATA

BATT_CLK

C135

1

OPEN

2

2

5-

THRM1

4343-

U5

3

LTH

RESET#

2

GND

HTH

VCC

1

GMT_G680LT1_SOT23_5P

4

5

D505

13

7-,43-

+VPACK

12

1K_5%R543

C500

1000pF_50v

+V5AUXON

5-

LITTLEFUSE_R451015_15A_65V

1

2

+V5LA

5-,7-,12-,18-,50-

C134

1

2

0.1uF_10v

FUSE501

12

R966

12

12

33_1%

33_1%

R967

ALLTOP_C144P3_109A_L_9P

CN500

1

BATT+

2

BATT+

3

ID

4

B-I

5

TS

6

SMD

7

SMC

8

GND

9

GND

1

D5005

EZJZ0V500AA

2

G1

G

G2

G

G3

G

G4

G

1

D5006

EZJZ0V500AA

2

CHANGE by

Drawer_Name

7-Nov-2007

INVENTEC

TITLE

SELECT & BATTERY CONN

DOC. NUMBERSIZE

CODE

A3

Model_No X01

CS

SHEET

REV

OF

626

THRM_SHUTDWN#

EC_PW_ON

18-,43-

CHENMKO_BAT54_3P

R105

43-

12

10K_5%

D527

13

SSM3K7002FU

Q517

1

G

SSM3K7002FU

+V3A

8-,33-,34-,35-,36-,41-,43-,47-,54-,55-,58-,60-

1

2

5

63

1

R675

200_5%

2

D528

13

R669

12

100K_5%

+V3LA

C660

1

0.1uF_10v

2

4

S

TPC6104

Q19

D

G

+V5LA

5-,6-,7-,12-,18-,50-

1

R680

10K_5%

2

CHENMKO_BAT54_3P

Q519

3

D

G

1

S

2

3

D

S

2

6-,7-,12-,18-,33-,40-,43-,50-,58-,60-

+V3LA

6-,7-,12-,18-,33-,40-,43-,50-,58-,60-

PAD8

2

1

POWERPAD_2_0610

C675

OPEN

1

2

R678

6.8K_1%

1

2

1

R128

10K_1%

2

C708

1uF_6.3v

MPLC0730_3R3_5.7A

1

C157

1

2

2

330uF_6.3v

Q518

1

SSM3K7002FU

D536

13

CHENMKO_BAT54_3P

R677

12

0_5%

R676

12

OPEN

C710

12

0.1uF_25v

TI_TPS51125_QFN_24P

12

FDS8884

Q16

Q17

6-,43-

8765

D

8

D

S

123

765

G

41S23

G

4

4.7uF_25v

C153

10uF_25v_K_X5R

C150

1

1

2

2

+V5AUXON

L6

12

FDS6690AS

+V3LDO

C709

1

1uF_6.3v

2

D

G

S

R683

0_5%

C711

1

2

4.7uF_6.3v

3

2

1

R741

150K_1%

2

8

9

12

U511

R682

820K_5%

1

R129

150K_1%

2

25

TML

VO2

VREG3

DRVH2

LL2

6

VFB2

ENTRIP2

SKIPSEL

EN0

13

1

2

5

14

1

2

4

TONSEL

GND

15

3

2

1

VFB1

VREF

ENTRIP1

PGOOD

VBST1VBST2

DRVH1

DRVL1DRVL2

VCLK

VIN

VREG5

18

16

17

C681

2.2uF_25v

+VBAT

5-,6-,8-,9-,10-,11-

PAD7

POWERPAD_2_0610

C676

12

1uF_6.3v

8

765

D

Q14

C679

G

FDS8884

S

4

123

8765

D

Q13

G

FDS6690AS

0.1uF_25v

247

VO1

23

12

22

2110

2011

LL1

19

41S23

+V5LA

5-,6-,7-,12-,18-,50-

C680

1

10uF_6.3v

2

10uF_25v_K_X5R

10uF_25v_K_X5R

C151

1

2

330uF_6.3v

C152

1

2

MPLC0730_3R3_5.7A

L3

12

1

C133

2

1

2

1uF_6.3v

C677

1

R681

15.4K_1%

2

1

R679

10K_1%

2

C678

1

2

OPEN

SKIPSEL

TONSEL

+V5A

PAD4

POWERPAD_2_0610

>>VRE3 OR VRE5=OOA

>>VREF=ASKIP

>>GND=PWM

>>VRE5=365/460

>>VRE3=300/375

>>VREF=245/305

>>GND=200/250

8-,9-,10-,11-,12-,36-,40-,41-,45-,46-,58-

INVENTEC

TITLE

SYSTEM POWER(3V/5V/12V)

CHANGE by

DOC. NUMBER

CODE

SIZE

A3

CS

24-Aug-2007Drawer_Name

SHEET

762

REV

X01Model_No

OF

SLP_S5#_3R

8-,12-,34-,43-

R89

12

0_5%

7-,8-,9-,10-,11-,12-,36-,40-,41-,45-,46-,58-

C128

OPEN12

C111

2.2uF_6.3v

+V5A

1

2

R80

10_5%

1

2

C129

OPEN

U4

1

EN_PSV

2

TON

3

VOUT

4

V5FILT

5

VFB

6

PGOOD

7

GND

1

TI_TPS51117_QFN_14P

2

R91

2

274K_1%

VBST

DRVH

V5DRV

DRVL

PGND

+VBAT

5-,6-,7-,9-,10-,11-

PAD2

POWERPAD_2_0610

8

765

1

2.2_5%

15K_1%

C127

0.1uF_25v

12

C126

1

2.2uF_6.3v

2

R88

12

12

R87

14

13

12

LL

11

TRIP

10

9

8

15

TML

D

G

Q4

FDS8884

S

123

4

8765

D

G

41S23

Q7

FDS6690AS

1

2

C82

C83

1

2

4.7uF_25v

10uF_25v_K_X5R

12

MPLC0730_2R2_7.3A

8-,19-,23-,24-,26-,27-,62-

1

10uF_6.3v

2

C112

PAD5

POWERPAD_2_0610

L2

1

1

R92

14.3K_1%

R90

10K_1%

OPEN

C130

2

2

1

2

C110

220uF_2v_15mR_Panasonic

1

2

+V1.8

11-,12-,18-,30-,32-,34-,36-,38-,39-,41-,43-,44-,45-,50-,51-,52-,58-,62-

R126

SLP_S3#_3R

8-,11-,12-,34-,43-

12

OPEN

1

2

+V5S

1

2

C148

C149

2.2uF_6.3v

U6

6

VCNTL

7

POK

8

EN

VIN

9

5

VIN

3

VOUT

4

VOUT

2

FB

GND

1

ANPEC_APL5912_KAC_TRL_SOP_8P

OPEN

+V1.8

8-,19-,23-,24-,26-,27-,62-

C147

1

2

22uF_6.3v

1

2

C145

39pF_50v

SLP_S3_5R

1

R125

9.1K_1%

2

1

R124

10K_1%

2

12-

C146

1

2

22uF_6.3v

PAD6

POWERPAD_2_0610

C144

1

2

2.2uF_6.3v

SSM3K7002FU

+V1.5S

16-,24-,36-,45-,54-,55-,56-,62-

1

R123

200_5%

2

Q15

3

D

G

1

S

2

SLP_S5#_3R

SLP_S3#_3R

M_VREF

+V5A

8-,12-,34-,43-

8-,11-,12-,34-,43-

19-,26-,27-

7-,8-,9-,10-,11-,12-,36-,40-,41-,45-,46-,58-

U3

TML11VDDQSNS

10 2

VIN

9

S5

GND8PGND

7

S3

6

VTTREF

VLDOIN

VTTSNS

1

3

VTT

4

5

GMT_G2997F6U_MSOP10_10P

C105

C106

1

1

1uF_6.3v

2

2

0.1uF_10v

+V3A +V1.5A

7-,33-,34-,35-,36-,41-,43-,47-,54-,55-,58-,60- 12-,36-

U514

C693

1

1uF_6.3v

2

1

IN

3

SHDN#

5

OUT

4

SET

GND

2

GMT_G916T1Uf_SOT23_5_5P

CHANGE by

1

R711

2.1K_1%

2

1

R708

10K_1%

2

Drawer_Name

1

2

+V1.8

8-,19-,23-,24-,26-,27-,62-

C108

1

22uF_6.3v

2

C691

4.7uF_6.3v

24-Aug-2007

PAD3

POWERPAD_2_0610

C107

1

22uF_6.3v

2

INVENTEC

TITLE

PS10

SYSTEM POWER(+V1.8/+V1.25S)

CODE

A3

CS

SHEET

+V0.9S

28-,62-

DOC. NUMBERSIZE REV

OF

862

X01Model_No

7-,8-,10-,11-,12-,36-,40-,41-,45-,46-,58-

+V5A

+VBAT

5-,6-,7-,8-,10-,11-

PAD502

POWERPAD_2_0610

SLP_S3#_5R

12-

R561

12

100K_5%

VCCP_PG

+V3S

10-,11-,12-,13-,18-,19-,20-,24-,26-,27-,30-,32-,33-,34-,35-,36-,43-,44-,45-,46-,47-,49-,50-,51-,52-,54-,55-,56-,58-,62-

1

R574

10K_5%

2

11-

C552

1

0.1uF_10v

2

C564

2.2uF_6.3v

1

R564

10_5%

2

C553

1

OPEN

2

U505

1

EN_PSV

2

TON

3

VOUT

4

V5FILT

5

VFB

6

PGOOD

7

GND

1

TI_TPS51117_QFN_14P

2

2

274K_1%

1

VBST

DRVH

TRIP

V5DRV

DRVL

PGND

R571

LL

TML

5

8

76

D

G

Q515

FDS8884

12

R562

14

1

13

R962

12

1

11

10

9

8

15

C555

1

2.2uF_6.3v

2

R563

2

2.2_5%

2

15K_1%

0.1uF_25v

1

For EMI

2

C554

2.2_5%

S

4

123

8765

D

G

41S23

1

Q516

2

FDS6690AS

For EMI

1

R960

4.7_5%

2

C950

2200pF_50v

C556

1

2

10uF_25v_K_X5R

MPLC0730_2R2_7.3A

L510

12

4.12K_1%

10K_1%

R573

R572

1

2

1

2

1

OPEN

C563

2

C575

1

2

220uF_2v_15mR_Panasonic

1

10uF_6.3v

2

C565

PAD504

POWERPAD_2_0610

+VCCP

13-,14-,15-,16-,19-,20-,21-,23-,24-,33-,36-,62-

CHANGE by

Drawer_Name

24-Aug-2007

INVENTEC

TITLE

PS10

GRAPHIC POWER (+VGFX_CORE)

CODE

A3

CS

SHEET

OF

962

REVSIZE DOC. NUMBER

X01Model_No

VSS_AXG_SENSE

VCC_AXG_SENSE

23-

23-

R566

12

10K_1%

1

C557

10pF_50v

2

R568

12

10K_1%

1

R567

649K_1%

2

DFGT_VR_EN

DFGT_VID_0

DFGT_VID_1

DFGT_VID_2

DFGT_VID_3

DFGT_VID_4

1919-

19-

19-

19-

19-

C560

220pF_25v

1

2

R554

12

10K_1%

R551

12

OPEN

R550

12

OPEN

R555

12

OPEN

R552

12

OPEN

R565

12

OPEN

U504

1

NC

2

GSNS

3

VSNS

4

CSNS

5

VOUT

6

COMP

7

VDAC

8

NC

C561

1

2

0.1UF_16V

32

33

NC

TML-PAD

NC

9

R559

320K_1%

31

27

28

30

NC

VID229VID3

VID4

PMF10PMO

ILIM

OSC

11

12

13

14

1

1

R560

10K_1%

2

2

C548

1

2

OPEN

25

VID026VID1

SHDN

24

NC

23

BOOT

22

HGATE

21

PHASE

20

VCC

19

LGATE

18

GND

17

NC

NC

SKIP

PG

ST_PM6650_VFQPFN_32P

15

16

R558

12

220K_1%

OPEN

R553

2

1

R556

12

2.2_5%

+V3S

9-,11-,12-,13-,18-,19-,20-,24-,26-,27-,30-,32-,33-,34-,35-,36-,43-,44-,45-,46-,47-,49-,50-,51-,52-,54-,55-,56-,58-,62-

+V5A

7-,8-,9-,11-,12-,36-,40-,41-,45-,46-,58-

C549

1

2

0.1uF_25v

2

3

BAT54AW

1

12

C550

1

2

1uF_6.3v

R557

10_5%

D518

8

765

D

G

Q513

FDS8884

S

3

12

4

8D765

G

S

123

4

Q514

FDS6690AS

1

R1051

4.7_5%

2

C1020

1

2

2200pF_50v

1

2

C542

4.7uF_25v

PAD501

POWERPAD_2_0610

C551

1

2

10uF_25v_K_X5R

L507

12

MPLC0730_2R2_7.3A

1

R569

215K_1%

2

R570

12

150K_1%

1

0.1uF_16v_OPEN

+VBAT

5-,6-,7-,8-,9-,11-

1

C562

560uF_2.5v

2

C951

1

2

0.1uF_16v_OPEN

C558

1

10uF_6.3v

2

FOR EMI TEST

C953

C952

1

22

0.1uF_16v_OPEN

0.1uF_16v_OPEN

OPEN FOR EMI TEST

L539

12

FBM_11_451616_800A40T

PAD503

POWERPAD_2_0610

+VGFX_CORE

C954

1

2

0.1uF_16v_OPEN

10-,23-

C955

1

2

+VGFX_CORE

10-,23-

C559

12

1000pF_50v

INVENTEC

TITLE

PS10

SYSTEM POWER(+VCCP/+V1.5S)

CODE

SIZE

CHANGE by OF

Drawer_Name

24-Aug-2007

A3

CS

SHEET

DOC. NUMBER

10 62

REV

X01Model_No

SLP_S3#_3R

8-,12-,34-,43-

VR_PWRGD

VR_PWRGD

IMVP_CKEN#

C1005

1

2

1000pF_50v

VCOREGND

R577

9-

12

180K_1%

1

3

D523

BAT54C

2

R578

12

11-,18-,34-

+V3S

180K_1%

H_VID6

H_VID5

H_VID4

H_VID3

H_VID2

H_VID1

H_VID0

9-,10-,11-,12-,13-,18-,19-,20-,24-,26-,27-,30-,32-,33-,34-,35-,36-,43-,44-,45-,46-,47-,49-,50-,51-,52-,54-,55-,56-,58-,62-

PSI#

H_DPRSTP#

PM_DPRSLPVR

1

1

R1000

10K_5%

R1001

10K_5%

2

2

VCORE_EN

11-,18-,34-

12

C977

330pF_50v

12

R1003

1.65K_1%

R1004

432K_1%

+V5A

7-,8-,9-,10-,12-,36-,40-,41-,45-,46-,58-

R611

12

0_5%

R612

12

0_5%

R1007

12

OPEN

C1001

220pF_25v

1

1

2

2

VCOREGND

16-

16-

R1005

12

12

61.9K_1%

C1003

0.012uF_16v

C577

1

2

1uF_6.3v

11-,43-

VCCSENSE

VSSSENSE

CSREF

1616161616-

1616-

15-

15-,19-,33-

19-,34-

VCOREGND

1

18pF_50v

2

C10041

680pF_50v

2

C1002

2

12

100K_5%

12

C602

0.1uF_16v

5

U506

4

PHP_74LVC1G17_SOT753_5P

3

R1002

1

OPEN

R594

12

499_1%

12

C1000

4700pF_25v

R1006

TP2054

TP2055

11-

C1006

1000pF_50v

2

C578

1

2

1uF_6.3v

2

49

46

48

47

PSI

TML

1

EN

DPRSLP

DPRSTP

2

PWRGD

3

PGDELAY

4

CLKEN

5

FBRTN

6

FB

7

COMP

U508

8

SS

ADI_ADP3208_LFCSP_48P

9

ST

10

VARFREQ

11

VRTT

12

TTSEN

CLIM

PMON

PMONFS

15

13

14

1

R1008

115K_1%

2

VCOREGND

1

2

VCOREGND

+V3S

9-,10-,11-,12-,13-,18-,19-,20-,24-,26-,27-,30-,32-,33-,34-,35-,36-,43-,44-,45-,46-,47-,49-,50-,51-,52-,54-,55-,56-,58-,62-

5

U507

4

PHP_74LVC1G17_SOT753_5P

3

19-,34-

PM_PWROK

VCOREGND

43

42

41

40

39

VID1

VID2

CSCOMP

CSFEF19CSSUM

18

1

2

VID3

VID4

VID5

VID6

RAMP20RPM22RT

VRPM

23 38

21

2

R1010

80.6K_1%

1

2

R1011

274K_1%

1

1

C1008

2

1000pF_50v

VCOREGND

C1009

1000pF_50v

37

SP

VCC

DRVH1

PVCC1

DRVL1

PGND1

PGND2

DRVL2

PVCC2

DRVH2

GND

24

R1009

237K_1%

12

1000pF_50v

12

10K_5%

45

44

VID0

LLINE

17

16

1

2

36

BST1

35

34

SW1

33

32

31

30

29

28

27

SW2

26

25

BST2

12

C1007

R1012

12

105K_1%

12

105K_1%

1

C1010

1000pF_50v

2

11-,43-

R1090

10K_5%

R1050

12

0_5%

R1019

R1020

VCOREGND

R1013

R1014

VCORE_ENVCCP_PG

R1018

12

10_5%

C1011

1

2.2uF_6.3v

2

2.2_5%

2

1

12

2.2_5%

+VBAT_CPU

11-

R1015

12

115K_1%

+V5A

7-,8-,9-,10-,12-,36-,40-,41-,45-,46-,58-

D1000

3

1

BAT54A_30V_0.2A

C1012

12

0.1uF_25v

C1013

12

0.1uF_25v

2

R1016

76.8K_1%

1

2

1

2

FINE_TUNE

C1014

2.2uF_6.3v

1

R1017

220K_5%

2

+VBAT

5-,6-,7-,8-,9-,10-

1

L1

4

NFM60R30T222

3

2

1

2

10uF_25v_K_X5R

C88

1

2

10uF_25v_K_X5R

10uF_25v_K_X5R

C30

C31

1

2

R930

12

OPEN

10uF_25v_K_X5R

C89

1

2

R931

12

OPEN

+VBAT_CPU

11-

C29

1

2

0.01uF_50v

1

C90

2

0.01uF_50v

CHANGE by

4G321

G

4321

G

4S1

789

G

4

5

6789

Q9

SI7686DP_T1_E3

8765

9

D

Q10

FDMS8660S

23

2200pF_50v

56

Q8

SI7686DP_T1_E3

765

9

8

D

Q3

S

FDMS8660S

123

R674

4.7_5%

C674

1

2

1

2

1

1

2

1

2

4.7_5%

R627

1

C625

2200pF_50v

ETQP4LR36WFC_PANASONIC

D529

SSM34_3A40V2

ETQP4LR36WFC_PANASONIC

D525

SSM34_3A40V2

24-Aug-2007Drawer_Name

L517

1

2

2

R1021

10_1%

1

11-

CSREF

2

R1022

10_1%

1

L514

1

2

INVENTEC

TITLE

PS10

CPU POWER(VCC_CORE)

DOC. NUMBER

CODE

SIZE

A3

CS

SHEET

11 62

+VCC_CORE

OF

16-

REV

X01Model_No

+V3 +V3LA

57-,58-

+V3S

9-,10-,11-,13-,18-,19-,20-,24-,26-,27-,30-,32-,33-,34-,35-,36-,43-,44-,45-,46-,47-,49-,50-,51-,52-,54-,55-,56-,58-,62-

6-,7-,18-,33-,40-,43-,50-,58-,60-

8-,11-,12-,18-,30-,32-,34-,36-,38-,39-,41-,43-,44-,45-,50-,51-,52-,58-,62-

CHENMKO_BAT54_3P

SLP_S3#_5R

9-

5-,6-,7-,12-,18-,50-

R740

200_5%

D535

+V5S

1

2

+V5LA

Q18

4

1

S

D

2

5

3

6

1

2

1

3

D12

5-,6-,7-,12-,18-,50-

74ACT14MTC

14

1312

7

5-,6-,7-,12-,18-,50-

G

TPC6104

C159

1

680pF_50v

2

D13

3

1

CHENMKO_BAT54_3P

+V5LA

14

U8-B

7

+V5LA

1

R149

220K_5%

2

8-,11-,34-,43-

34

SLP_S3#_3R

1

C158

22uF_6.3v

2

R148

200_5%

CHENMKO_BAT54_3P

SLP_S5#_5R

1

12-

3

5-,6-,7-,12-,18-,50-

+V5LA

U8-F

74ACT14MTC

4

S

TPC6104

5-,6-,7-,12-,18-,50-

Q20

1

D

2

5

63

G

C175

1

2

680pF_50v

+V5LA

220K_5%

14

U8-D

98

7

74ACT14MTC

R739

220K_5%

12-

SLP_S5_3R

R738

1

C176

2

47uF_6.3v

2

1

2

1

1

2

1

2

R737

200_5%

C706

OPEN

2

R174

200_5%

1

3

D

S

2

SSM3K7002FU

D541

2

3

1

BAT54A_30V_0.2A

+V1.5A

Q511

8-,36-

8

1

D

S

7

2

3

6

5

4

G

AO4406

1

G

Q21

R548

12

12-

+V5A

7-,8-,9-,10-,11-,36-,40-,41-,45-,46-,58-

4

S

TPC6104

4

S

TPC6104

C125

12

680pF_50v

SLP_S3_5R

8-

SSM3K7002FU_OPEN

220K_5%

SLP_S5_3R

12-

+V5S

8-,11-,12-,18-,30-,32-,34-,36-,38-,39-,41-,43-,44-,45-,50-,51-,52-,58-,62-

Q11

1

D

2

5

63

G

Q12

1

D

2

5

63

G

2

R961

OPEN

1

3

D

G

1

S

Q538

2

8-

SLP_S5#_5R

SLP_S3_5R

C547

12

680pF_50v

1

Q512

SSM3K7002FU

+V1.5

57-

2

R549

200_5%

1

3

D

G

S

2

U8-A

74ACT14MTC

14

12

74ACT14MTC

7

U8-E

14

1110

7

C707

12

0.1uF_10v

U8-C

74ACT14MTC

14

56

8-,34-,43-

SLP_S5#_3R

7

INVENTEC

TITLE

PS10

POWER(SLEEP)

SIZE

CODE REV

CS

SHEETCHANGE by

DOC. NUMBER

12 62

12-Oct-2007Drawer_Name

A3

X01Model_No

OF

9-,13-,14-,15-,16-,19-,20-,21-,23-,24-,33-,36-,62-

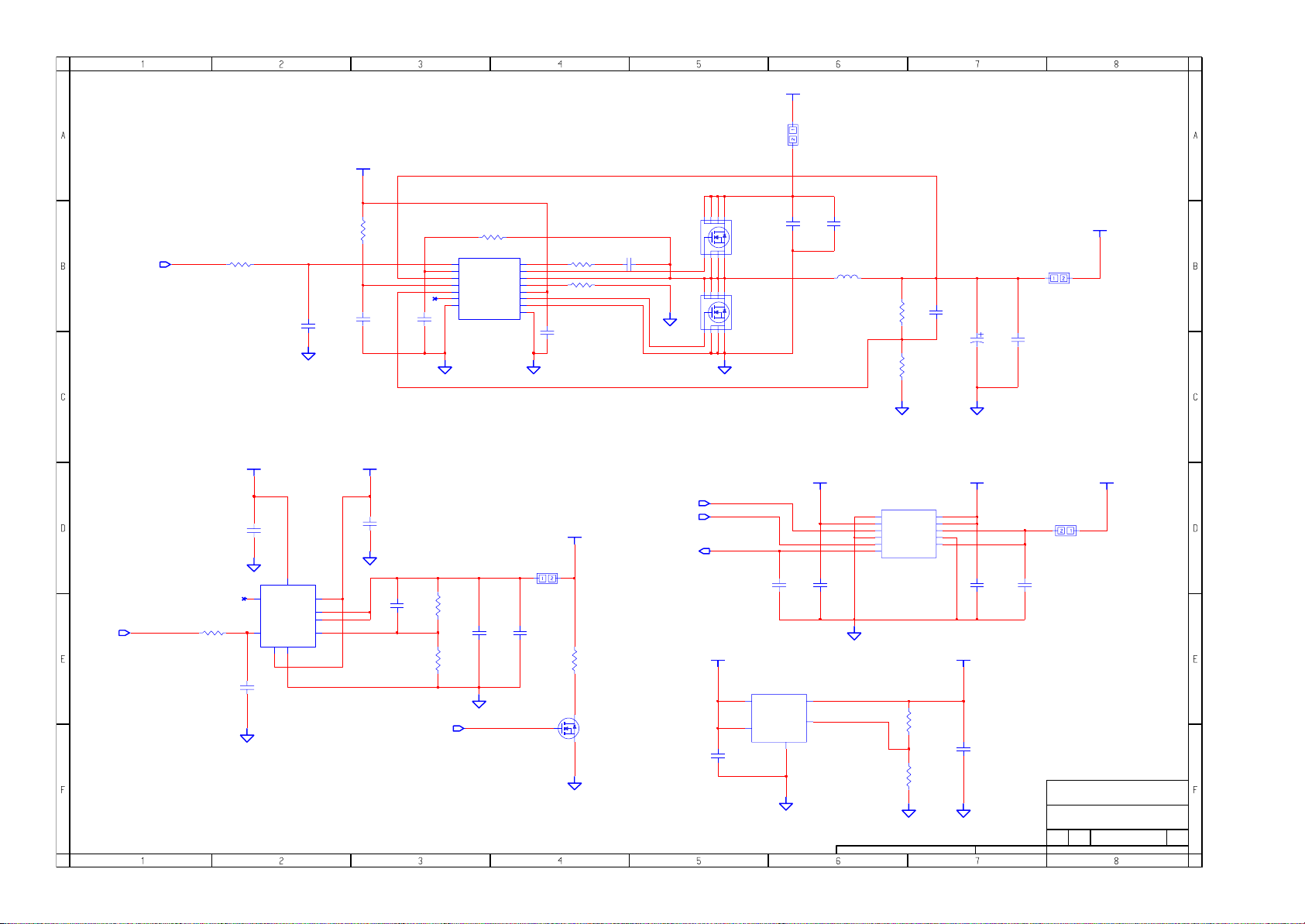

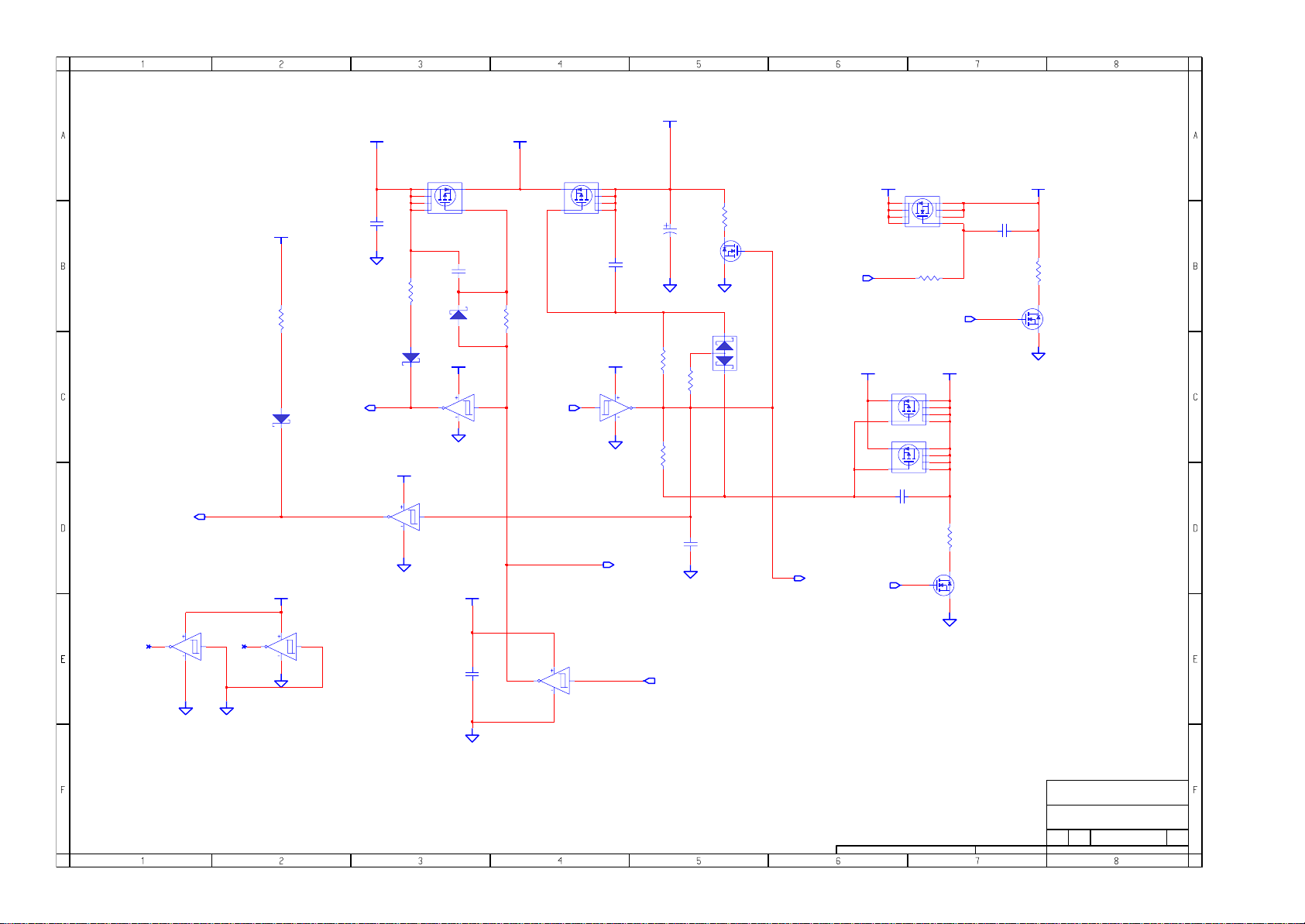

FSA

15-,1915-,19-

34-

FSB

1

1

0

1

CPU_BSEL1

CPU_BSEL2

CLK_R_SB14

*CLKREQ# pin controls SRC Table.

Byte5: bit6 =0(PWD)

SRC0

CR#_A

Byte5: bit7=0, disable CR#_A; 1,enable CR#_A

Byte5: bit2 =0(PWD)

SRC0

CR#_C

Byte5: bit3=0, disable CR#_C; 1,enable CR#_C

+VCCP

+VCCP_CLK_VDD

L4

BLM11A121S

1

9-,13-,14-,15-,16-,19-,20-,21-,23-,24-,33-,36-,62-

OPEN

R118

Layout note: All decoupling 0.1uF disperse closed to pin

2

C142

1

2

10uF_10v

1

R119

OPEN

2

1

10K_5%

12

R133

2

1

CLK_PWRGD

FSB CLOCK

FSC

FREQUENCY

0

0

000

667

800

1066 266

C143

1

2

10uF_10v

+VCCP

2

1

R132

2

33_5%

R117

OPEN

34-

HOST CLOCK

FREQUENCY

166

200

Byte5: bit6 =1

SRC2

Byte5: bit2 =1

SRC2

C720

C721

1

1

2

2

0.1uF_16v

0.1uF_16v

9-,13-,14-,15-,16-,19-,20-,21-,23-,24-,33-,36-,62-

CPU_BSEL0

RTS5158_48MHz

OPEN

R120

CLK_R_SB48

CLKREQ_R_SATA#

CLKREQ_R_MCH#

CLK_R_KBPCI

CLK_R_CBPCI

1

2

C140

33pF_50v

Please place close to CLKGEN within 500mils

CR#_B

CR#_D

C714

C719

1

2

0.1uF_16v

1

2

0.1uF_16v

1

2

C716

0.1uF_16v

+VCCP

1

R166

OPEN

2

R165

12

15-,19-

2.2K_5%

1

R163

OPEN

1, 0.5

4352-

OPEN

1

R784

34-

3419-

2

14.31818MHZ

1

2

51-

1

2

ICH_3S_SMCLK

ICH_3S_SMDATA

X1

30PPM

OPEN

12.1 ohm

R167

12

12.1_1%

R152

R153 1

R154

2

1

2

12MHz

48MHz

R162

12.1_1%

12

12

12

26-,27-,3426-,27-,34-

C141

33pF_50v

Byte5: bit4 =0(PWD)

SRC1

Byte5: bit5=0, disable CR#_B; 1,enable CR#_B

Byte5: bit0 =0(PWD)

SRC1

Byte5: bit1=0, disable CR#_D; 1,enable CR#_D

+V3S_CLK_VDD

+V3S

9-,10-,11-,12-,13-,18-,19-,20-,24-,26-,27-,30-,32-,33-,34-,35-,36-,43-,44-,45-,46-,47-,49-,50-,51-,52-,54-,55-,56-,58-,62-

Layout note: All decoupling 0.1uF disperse closed to pin

C717

1

2

0.1uF_16v

9-,10-,11-,12-,13-,18-,19-,20-,24-,26-,27-,30-,32-,33-,34-,35-,36-,43-,44-,45-,46-,47-,49-,50-,51-,52-,54-,55-,56-,58-,62-

+V3S

R782

R783

10K_5%

2

1

1

10K_5%

R781

2

10K_5%

475_1%

12

2

475_1%

33_5%

33_5%R155

2

1

R780

OPEN

2

1

CLK_SB48

CLKREQ_SATA#

CLKREQ_MCH#

CLK_KBPCI

CLK_CBPCI

CR#_E

Byte5: bit4 =1

SRC4

Byte5: bit0 =1

SRC4

CR#_F

CR#_G

CR#_H

L5

BLM11A121S

1

2

1

2

U7

26

VDDSRC_IO

45

VDDSRC_IO

36

VDDSRC_IO

12

VDD_IO

39

VDD_SRC

61

VDDREF

20

VDDPLL3_IO

49

VDDCPU_IO

9

VDD48

2

VDDPCI

55

VDDCPU

16

VDD_PLL3

10

USB_48MHZ_FSLA

57

FSLB_TEST_MODE

62

REF0_FSLC_TEST_SEL

CLK_NB14

1

PCI0_CR#_A

3

PCI1_CR#_B

4

PCI2_TME

5

SRC5_EN_PCI3

56

CK_PWRGD_PD#

64

SCLK

63

SDTAT

60

X1

59

X2

8

GNDPCI

11

GND48

15

GND_IO

19

GND_PLL3

23

GNDSRC

29

GNDSRC

42

GNDSRC

58

GNDREF

52

GNDCPU

REA_RTM875T_606_TSSOP_64P

PCI_STOP#_SRCT5

CPU_STOP#_SRCC5

CPUT2_ITP_SRCT8

CPUC2_ITP_SRCC8

SRCT11_CR#_H

SRCC11_CR#_G

SRCT7_CR#_F

SRCC7_CR#_E

PCI4_27M_Select

PCI_F5_ITP_EN

SRCT3_CR#_C

SRCC3_CR#_D

SRCT2_SATAT

SRCC2_SATAC

27MHz_NonSS_SRCT1_SE1

27MHz_SS_SRCC1_SE2

SRCT0_DOTT_96

SRCC0_DOTC_96

Byte6: bit7=0, disable CR#_E; 1,enable CR#_E

SRC6

Byte6: bit6=0, disable CR#_F; 1,enable CR#_F

SRC8

Byte6: bit5=0, disable CR#_G; 1,enable CR#_G

SRC9

Byte6: bit4=0, disable CR#_H; 1,enable CR#_H

SRC10

C155

10uF_10v

RESET#

CPUT1_F

CPUC1_F

CPUT0

CPUC0

SRCT10

SRCC10

SRCT9

SRCC9

SRCT6

SRCC6

SRCT4

SRCC4

C722

1

0.1uF_16v

2

48

38

37

CLK_R_NBCLK

51

CLK_R_NBCLK#

50

CLK_R_CPUBCLK

54

CLK_R_CPUBCLK#

53

CLK_R_PCIE_NCARD

47

CLK_R_PCIE_NCARD#

46

CLKREQ_NEWCARD#

33

CLKREQ_MINI2#

32

CLK_R_PCIE_ROBSON

34

CLK_R_PCIE_ROBSON#

35

CLK_R_PCIE_WLAN

30

CLK_R_PCIE_WLAN#

31

44

43

CLK_R_PCIE_SB

41

CLK_R_PCIE_SB#

40

6

CLK_ICHPCI

7

CLK_PEG_MCH

27

CLK_PEG_MCH#

28

CLK_R_PCIE_LAN

24

CLK_R_PCIE_LAN#

25

21

CLK_SATA1

CLK_SATA1#

22

CLKSS1_R_DREF

17

CLKSS1_R_DREF#

18

CLK_R_DREF

13

CLK_R_DREF#

14

9-,10-,11-,12-,13-,18-,19-,20-,24-,26-,27-,30-,32-,33-,34-,35-,36-,43-,44-,45-,46-,47-,49-,50-,51-,52-,54-,55-,56-,58-,62-

1

2

C715

0.1uF_16v

1

2

R160

2

10K_5%

C723

0.1uF_16v

C718

1

0.1uF_16v

2

CLK_WLAN

CHANGE by

9-,10-,11-,12-,13-,18-,19-,20-,24-,26-,27-,30-,32-,33-,34-,35-,36-,43-,44-,45-,46-,47-,49-,50-,51-,52-,54-,55-,56-,58-,62-

+V3S

1

1

R121

R122

OPEN

OPEN

2

2

475_1%

12

475_1%

12

33_5%

12

33_5%

9-,10-,11-,12-,13-,18-,19-,20-,24-,26-,27-,30-,32-,33-,34-,35-,36-,43-,44-,45-,46-,47-,49-,50-,51-,52-,54-,55-,56-,58-,62-

1

Drawer_Name

R157

2

1

OPEN

R156

2

1

10K_5%

27_Selet =0

LCD_SST 100MHZ

27_Selet =1

27MHZ non-spread clock

+V3S

7-Nov-2007

+V3S

1

1

R137

R136

10K_5%

10K_5%

2

2

34-

PCISTOP#_3

34-

CPUSTOP#_3

21-

CLK_R_NBCLK

21-

CLK_R_NBCLK#

14-

CLK_R_CPUBCLK

14-

CLK_R_CPUBCLK#

54-

CLK_R_PCIE_NCARD

54-

R134

R135

R15812

R159

CLK_R_PCIE_NCARD#

55-

CLKREQ_R_ROBSON#

55-

CLKREQ_R_WLAN#

55-

CLK_R_PCIE_ROBSON

55-

CLK_R_PCIE_ROBSON#

55-

CLK_R_PCIE_WLAN

55-

CLK_R_PCIE_WLAN#

56-

CLK_R_PCIE_HDDVD

56-

CLK_R_PCIE_HDDVD#

34-

CLK_R_PCIE_SB

34-

CLK_R_PCIE_SB#

55-

CLK_R_WLAN

35-

CLK_R_ICHPCI

19-

CLK_PEG_MCH

19-

CLK_PEG_MCH#

47-

CLK_R_PCIE_LAN

47-

CLK_R_PCIE_LAN#

33-

CLK_SATA1

33-

CLK_SATA1#

19-

CLKSS1_R_DREF

19-

CLKSS1_R_DREF#

19-

CLK_R_DREF

19-

CLK_R_DREF#

INVENTEC

TITLE

PS10

CLOCK_GENERATOR

SIZE

A3

CODE

CS

SHEET

DOC. NUMBER

OF

13 62

REV

X01Model_No

H_A#(35:3)

H_ADSTB#1

H_STPCLK#

H_A20M#

H_FERR#

H_IGNNE#

H_INTR

H_NMI

H_SMI#

21-

H_A#(3)

H_A#(4)

H_A#(5)

H_A#(6)

H_A#(7)

H_A#(8)

H_A#(9)

H_A#(10)

H_A#(11)

H_A#(12)

H_A#(13)

H_A#(14)

H_A#(15)

H_A#(16)

H_REQ#(4:0) H_RS#(2:0)

H_A#(17)

H_A#(18)

H_A#(19)

H_A#(20)

H_A#(21)

H_A#(22)

H_A#(23)

H_A#(24)

H_A#(25)

H_A#(26)

H_A#(27)

H_A#(28)

H_A#(29)

H_A#(30)

H_A#(31)

H_A#(32)

H_A#(33)

H_A#(34)

H_A#(35)

21-

333333-

33333333-

21-

H_REQ#(0)

H_REQ#(1)

H_REQ#(2)

H_REQ#(3)

H_REQ#(4)

H_ADSTB#0

21-

CN505-1

J4

A3#

L5

A4#

L4

A5#

K5

A6#

M3

A7#

N2

A8#

J1

A9#

N3

A10#

P5

A11#

P2

A12#

L2

A13#

P4

A14#

P1

A15#

R1

A16#

M1

ADSTB0#

K3

REQ0#

H2

REQ1#

K2

REQ2#

J3

REQ3#

L1

REQ4#

Y2

A17#

U5

A18#

R3

A19#

W6

A20#

U4

A21#

Y5

A22#

U1

A23#

R4

A24#

T5

A25#

T3

A26#

W2

A27#

W5

A28#

Y4

A29#

U2

A30#

V4

A31#

W3

A32#

AA4

A33#

AB2

A34#

AA3

A35#

V1

ADSTB1#

A6

A20M#

A5

FERR#

C4

IGNNE#

D5

STPCLK#

C6

LINT0

B4

LINT1

A3

SMI#

M4

RSVD01

N5

RSVD02

T2

RSVD03

V3

RSVD04

B2

RSVD05

C3

RSVD06

D2

RSVD07

D22

RSVD08

D3

RSVD09

F6

RSVD010

FOX_PZ4782K_274M_41_478P

GMCH

CPU

ADS#

BNR#

BPRI#

DEFER#

DRDY#

DBSY#

BR0#

IERR#

ADDR GROUP 0

INIT#

CONTROL

LOCK#

RESET#

RS0#

RS1#

RS2#

TRDY#

HIT#

HITM#

BPM0#

BPM1#

BPM2#

BPM3#

PRDY#

PREQ#

TCK

ADDR GROUP 1

TDO

TMS

XDP/ITP SIGNALS

TRST#

DBR#

THERMAL

PROCHOT#

THERMDA

THERMDC

THERMTRIP#

ICH

H CLK

BCLK0

BCLK1

RESERVED

H1

E2

G5

H5

F21

E1

F1

D20

B3

H4

C1

F3

F4

G3

G2

G6

E4

AD4

AD3

AD1

AC4

AC2

AC1

AC5

AA6

TDI

AB3

AB5

AB6

C20

+VCCP

10mils/10mils

ICH8

9-,13-,14-,15-,16-,19-,20-,21-,23-,24-,33-,36-,62-

12

R22

D21

A24

B25

C7

A22

A21

56_5%

+VCCP

21-

H_ADS#

21-

H_BNR#

21-

H_BPRI#

21-

H_DEFER#

21-

H_DRDY#

21-

H_DBSY#

21-

H_BREQ#0

33-

H_INIT#

21-

H_LOCK#

21-

H_CPURST#

21-

H_TRDY#

21-

H_HIT#

21-

H_HITM#

14-

H_BPM5_PREQ#

14-

H_TCK

14-

TDI_FLEX

14-

H_TMS

34-

XDP_DBRESET#

18-

H_THERMDA

18-

THERM_MINUS

18-,19-,33-

PM_THRMTRIP#

13-

CLK_R_CPUBCLK

13-

CLK_R_CPUBCLK#

+VCCP

9-,13-,14-,15-,16-,19-,20-,21-,23-,24-,33-,36-,62-

+VCCP

R97

12

OPEN

H_RS#(0)

H_RS#(1)

H_RS#(2)

R723

12

54.9_1%

R719

12

54.9_1%

R720

12

54.9_1%

R724

12

54.9_1%

+VCCP

9-,13-,14-,15-,16-,19-,20-,21-,23-,24-,33-,36-,62-

1

R21

56_5%

2

9-,13-,14-,15-,16-,19-,20-,21-,23-,24-,33-,36-,62-

21-

1

R721

54.9_1%

2

14-

H_BPM5_PREQ#

14-

TDI_FLEX

14-

H_TMS

14-

H_TCK

CLOSED TO CPU

51 ohm +/-1% pull-up to +VCCP

(VCCP) if ITP is implemented

PM_THRMTRIP# should be T at CPU

Drawer_Name

24-Aug-2007

INVENTEC

TITLE

PS10

MEROM-1

CODE

SIZE

A3

DOC. NUMBER

Model_No X01

CS

SHEETCHANGE by

REV

OF

6214

H_D#(63:0)

H_DSTBN#0

H_DSTBP#0

H_DINV#0

+VCCP

9-,13-,14-,15-,16-,19-,20-,21-,23-,24-,33-,36-,62-

1

R617

1K_1%

2

1

2

R618

2K_1%

GTLREF

Layout note: Zo=55 ohm,

0.5" max for GTLREF.

15-,21-

2121- 2121-

15-,21-

H_DSTBN#1

H_DSTBP#1

H_DINV#1

CPU_BSEL0

CPU_BSEL1

CPU_BSEL2

H_D#(0)

H_D#(1)

H_D#(2)

H_D#(3)

H_D#(4)

H_D#(5)

H_D#(6)

H_D#(7)

H_D#(8)

H_D#(9)

H_D#(10)

H_D#(11)

H_D#(12)

H_D#(13)

H_D#(14)

H_D#(15)

H_D#(16)

H_D#(17)

H_D#(18)

H_D#(19)

H_D#(20)

H_D#(21)

H_D#(22)

H_D#(23)

H_D#(24)

H_D#(25)

H_D#(26)

H_D#(27)

H_D#(28)

H_D#(29)

H_D#(30)

H_D#(31)

212121-

13-,1913-,19- 1113-,19-

1

R24

OPEN

2

1

2

R23

OPEN

C697

1

2

OPEN

Place C642(0.1uF_16V) close to the TEST4 pin.

Make sure TEST4 routing is reference

to GND and away from other noisy signals.

CN505-2

E22

D0#

F24

D1#

E26

D2#

G22

D3#

F23

D4#

G25

D5#

E25

D6#

E23

D7#

K24

D8#

G24

D9#

J24

D10#

J23

D11#

H22

D12#

F26

D13#

K22

D14#

H23

D15#

J26

DSTBN0#

H26

DSTBP0#

H25

DINV0#

N22

D16#

K25

D17#

P26

D18#

R23

D19#

L23

D20#

M24

D21#

L22

D22#

M23

D23#

P25

D24#

P23

D25#

P22

D26#

T24

D27#

R24

D28#

L25

D29#

T25

D30#

N25

D31#

L26

DSTBN1#

M26

DSTBP1#

N24

DINV1#

AD26

GTLREF

C23

TEST1

D25

TEST2

C24

TEST3

AF26

TEST4

AF1

TEST5

A26

TEST6

B22

BSEL0

B23

BSEL1

C21

BSEL2

FOX_PZ4782K_274M_41_478P

DATA GRP 2DATA GRP 3

DATA GRP 0

DSTBN2#

DSTBP2#

DATA GRP 1

DSTBN3#

DSTBP3#

MISC

DPRSTP#

PWRGOOD

DINV2#

DINV3#

COMP0

COMP1

COMP2

COMP3

DPSLP#

DPWR#

SLP#

Y22

D32#

AB24

D33#

V24

D34#

V26

D35#

V23

D36#

T22

D37#

U25

D38#

U23

D39#

Y25

D40#

W22

D41#

Y23

D42#

W24

D43#

W25

D44#

AA23

D45#

AA24

D46#

AB25

D47#

Y26

AA26

U22

AE24

D48#

AD24

D49#

AA21

D50#

AB22

D51#

AB21

D52#

AC26

D53#

AD20

D54#

AE22

D55#

AF23

D56#

AC25

D57#

AE21

D58#

AD21

D59#

AC22

D60#

AD23

D61#

AF22

D62#

AC23

D63#

AE25

AF24

AC20

R26

U26

AA1

Y1

E5

B5

D24

D6

D7

AE6

PSI#

1

2

R96

OPEN

11-,19-,33-

R718 27.4_1%

R717

H_DPRSTP#

+VCCP

H_D#(32)

H_D#(33)

H_D#(34)

H_D#(35)

H_D#(36)

H_D#(37)

H_D#(38)

H_D#(39)

H_D#(40)

H_D#(41)

H_D#(42)

H_D#(43)

H_D#(44)

H_D#(45)

H_D#(46)

H_D#(47)

H_D#(48)

H_D#(49)

H_D#(50)

H_D#(51)

H_D#(52)

H_D#(53)

H_D#(54)

H_D#(55)

H_D#(56)

H_D#(57)

H_D#(58)

H_D#(59)

H_D#(60)

H_D#(61)

H_D#(62)

H_D#(63)

21-

H_DSTBN#3

21-

H_DSTBP#3

21-

27.4_1%R605

54.9_1%R606

54.9_1%

33213321-

H_DINV#3

H_DPSLP#

H_DPWR#

H_PWRGD

H_CPUSLP#

PSI#

12

12

12

12

CLOSED TO CPU

9-,13-,14-,15-,16-,19-,20-,21-,23-,24-,33-,36-,62-

15-,21-

15-,21-

Comp[3:0] trace must list than 0.5 inch

Comp[0,2] Z0=27.4ohm

Comp[1,3] Z0=54.9ohm

21-

21-

H_D#(63:0)

H_DSTBN#2

H_DSTBP#2

H_DINV#2

H_D#(63:0)H_D#(63:0)

CHANGE by

Drawer_Name 29-Aug-2007

INVENTEC

TITLE

PS10

MEROM-2

SIZE

CODE

DOC. NUMBER

A3

Model_No X01

CS

SHEET

REV

OF

6215

900uF_2.5v

+VCC_CORE

11-,16-

1

3

+VCC_CORE

11-,16-

CN505-3

A7

VCC001

A9

VCC002

A10

VCC003

A12

VCC004

A13

VCC005

2

C91

A15

VCC006

A17

VCC007

A18

VCC008

A20

VCC009

B7

VCC010

B9

VCC011

B10

VCC012

B12

VCC013

B14

VCC014

B15

VCC015

B17

VCC016

B18

VCC017

B20

VCC018

C9

VCC019

C10

VCC020

C12

VCC021

C13

VCC022

C15

VCC023

C17

VCC024

C18

VCC025

D9

VCC026

D10

VCC027

D12

VCC028

D14

VCC029

D15

VCC030

D17

VCC031

D18

VCC032

E7

VCC033

E9

VCC034

E10

VCC035

E12

VCC036

E13

VCC037

E15

VCC038

E17

VCC039

E18

VCC040

E20

VCC041

F7

VCC042

F9

VCC043

F10

VCC044

F12

VCC045

F14

VCC046

F15

VCC047

F17

VCC048

F18

VCC049

F20

VCC050

AA7

VCC051

AA9

VCC052

AA10

VCC053

AA12

VCC054

AA13

VCC055

AA15

VCC056

AA17

VCC057

AA18

VCC058

AA20

VCC059

AB9

VCC060

AC10

VCC061

AB10

VCC062

AB12

VCC063

AB14

VCC064

AB15

VCC065

AB17

VCC066

AB18

VCC067

FOX_PZ4782K_274M_41_478P

VCC068

VCC069

VCC070

VCC071

VCC072

VCC073

VCC074

VCC075

VCC076

VCC077

VCC078

VCC079

VCC080

VCC081

VCC082

VCC083

VCC084

VCC085

VCC086

VCC087

VCC088

VCC089

VCC090

VCC091

VCC092

VCC093

VCC094

VCC095

VCC096

VCC097

VCC098

VCC099

VCC0100

VCCP01

VCCP02

VCCP03

VCCP04

VCCP05

VCCP06

VCCP07

VCCP08

VCCP09

VCCP10

VCCP11

VCCP12

VCCP13

VCCP14

VCCP15

VCCP16

VCCA01

VCCA02

VCCSENSE

VSSSENSE

AB20

AB7

AC7

AC9

AC12

AC13

AC15

AC17

AC18

AD7

AD9

AD10

AD12

AD14

AD15

AD17

AD18

AE9

AE10

AE12

AE13

AE15

AE17

AE18

AE20

AF9

AF10

AF12

AF14

AF15

AF17

AF18

AF20

G21

V6

J6

K6

M6

J21

K21

M21

N21

N6

R21

R6

T21

T6

V21

W21

B26

C26

AD6

VID0

AF5

VID1

AE5

VID2

AF4

VID3

AE3

VID4

AF3

VID5

AE2

VID6

AF7

AE7

+VCCP

9-,13-,14-,15-,16-,19-,20-,21-,23-,24-,33-,36-,62-

1

C641

2

220uF_2v_15mR_Panasonic

11-

H_VID0

11-

H_VID1

11-

H_VID2

11-

H_VID3

11-

H_VID4

11-

H_VID5

11-

H_VID6

+VCC_CORE

11-,16-

1

R667

100_1%

2

1

R666

100_1%

2

11-

11-

+VCCP

9-,13-,14-,15-,16-,19-,20-,21-,23-,24-,33-,36-,62-

C652

1

2

0.1uF_16v

VCCSENSE

VSSSENSE

C653

1

2

0.1uF_16v

LAYOUT NOTE:

PLACE C2461 NEAR PIN B26

PLACE THESE INSIDE SOCKET

CAVITY ON L8 (NORTH SIDE

SECONDARY)

C654

C622

1

1

2

2

0.1uF_16v

0.1uF_16v

8-,24-,36-,45-,54-,55-,56-,62-

0.01uF_16v

C601

1

2

+V1.5S

C623

0.1uF_16v

1

2

C624

1

2

0.1uF_16v

1

C600

10uF_6.3v

2

LAYOUT NOTE:

ROUTE VCCSENSE AND VSSSENSE TRACE AT

24.7 OHM WITH 50 MIL SPACEING

PLACE PU AND PD WITHIN I INCH OF CPU

CHANGE by SHEET

Drawer_Name 5-Nov-2007

INVENTEC

TITLE

PS10

MEROM-3

SIZE

CODE

DOC. NUMBER

A3

Model_No X01

CS

REV

OF

6216

CN505-4

A4

VSS001

A8

VSS002

A11

VSS003

A14

VSS004

A16

VSS005

A19

VSS006

A23

VSS007

AF2

VSS008

B6

VSS009

B8

VSS010

B11

VSS011

B13

VSS012

B16

VSS013

B19

VSS014

B21

VSS015

B24

VSS016

C5

VSS017

C8

VSS018

C11

VSS019

C14

VSS020

C16

VSS021

C19

VSS022

C2

VSS023

C22

VSS024

C25

VSS025

D1

VSS026

D4

VSS027

D8

VSS028

D11

VSS029

D13

VSS030

D16

VSS031

D19

VSS032

D23

VSS033

D26

VSS034

E3

VSS035

E6

VSS036

E8

VSS037

E11

VSS038

E14

VSS039

E16

VSS040

E19

VSS041

E21

VSS042

E24

VSS043

F5

VSS044

F8

VSS045

F11

VSS046

F13

VSS047

F16

VSS048

F19

VSS049

F2

VSS050

F22

VSS051

F25

VSS052

G4

VSS053

G1

VSS054

G23

VSS055

G26

VSS056

H3

VSS057

H6

VSS058

H21

VSS059

H24

VSS060

J2

VSS061

J5

VSS062

J22

VSS063

J25

VSS064

K1

VSS065

K4

VSS066

K23

VSS067

K26

VSS068

L3

VSS069

L6

VSS070

L21

VSS071

L24

VSS072

M2

VSS073

M5

VSS074

M22

VSS075

M25

VSS076

N1

VSS077

N4

VSS078

N23

VSS079

N26

VSS080

P3

VSS081

FOX_PZ4782K_274M_41_478P

VSS082

VSS083

VSS084

VSS085

VSS086

VSS087

VSS088

VSS089

VSS090

VSS091

VSS092

VSS093

VSS094

VSS095

VSS096

VSS097

VSS098

VSS099

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

VSS161

VSS162

VSS163

P6

P21

P24

R2

R5

R22

R25

T1

T4

T23

T26

U3

U6

U21

U24

V2

V5

V22

V25

W1

W4

W23

W26

Y3

Y6

Y21

Y24

AA2

AA5

AA8

AA11

AA14

AA16

AA19

AA22

AA25

AB1

AB4

AB8

AB11

AB13

AB16

AB19

AB23

AB26

AC3

AC6

AC8

AC11

AC14

AC16

AC19

AC21

AC24

AD2

AD5

AD8

AD11

AD13

AD16

AD19

AD22

AD25

AE1

AE4

AE8

AE11

AE14

AE16

AE19

AE23

AE26

A2

AF6

AF8

AF11

AF13

AF16

AF19

AF21

A25

AF25

CHANGE by

Drawer_Name 24-Aug-2007

INVENTEC

TITLE

PS10

MEROM-4

DOC. NUMBERSIZE

CODE

A3

Model_No X01

CS

SHEET

REV

OF

6217

+V5S

8-,11-,12-,30-,32-,34-,36-,38-,39-,41-,43-,44-,45-,50-,51-,52-,58-,62-

FAN1_DAC0_3

U501

1

FON

2

1

C2

2

2.2uF_10v

43-

VIN

3

VO

4

VSET

8

GND

7

GND

6

GND

5

GND

GMT_G995P1U_SOP8_8P

9-,10-,11-,12-,13-,19-,20-,24-,26-,27-,30-,32-,33-,34-,35-,36-,43-,44-,45-,46-,47-,49-,50-,51-,52-,54-,55-,56-,58-,62-

7-,18-,43-

+V3S

1

2

1

R1

10K_5%

2

C3

0.01uF_50v

+V5LA

5-,6-,7-,12-,50-

1

150_5%

0.1uF_10v

R673

C673

1

2

C530

2.2uF_10v

1

2

3

CN501

1

2

3

G

G1

G2

G

ACES_85205_0300N_3P

FAN CN

U513

R709

HYST OT

SET15VCC

GND

12

23.2K_1%

2

3

2

1

2

4

GMT_G708T1U_SOT23_5P

Thermal shoutdown at 88.5C +/-3C from 60C to 100C

RSET=0.0012*T - 0.9308*T+96.147

2

Hysteresis is 30C

H_THERMDA

THERM_MINUS

THRM_SHUTDWN#

6-,7-,12-,18-,33-,40-,43-,50-,58-,60-

14-

14-

7-,18-,43-

+V3LA

43-

FAN_TACH1

THRM_SHUTDWN#

2

1

R750

OPEN

R716

12

0_5%

12

PM_THRMTRIP#

0_5%

R715

R748

12

330_5%

2SC2411K

11-,34-

Q522

2

1

R751

2M_5%

2

3

C

B

E

1

1

2

VR_PWRGD

14-,19-,33-

+V3LA

6-,7-,12-,18-,33-,40-,43-,50-,58-,60-

1

C739

2

0.1uF_16v

C694

100pF_50v

12

Thermal Sensor For CPU

LAYOUT NOTES: PUT THE THERMAL SENSOR CLOSE TO CPU

U515

1

VDD

2

DP

3

4

THERM

SMSC_EMC1402_1_ACZL_MSOP_8P

SMCLK

SMDATA

ALERTDN

GND

8

7

6

5

CHANGE by

SSM3K7002FU

C740

OPEN

Drawer_Name

Q521

1

7-,18-,43-

THRM_SHUTDWN#

3

D

G

S

2

5-,43-

EC_CLK

5-,43-

EC_DATA

INVENTEC

TITLE

PS10

7-Nov-2007

THERMAL&FAN CONTROLLER

SIZE CODE

A3

Model_No X01

CS

SHEET

REVDOC. NUMBER

OF

6218

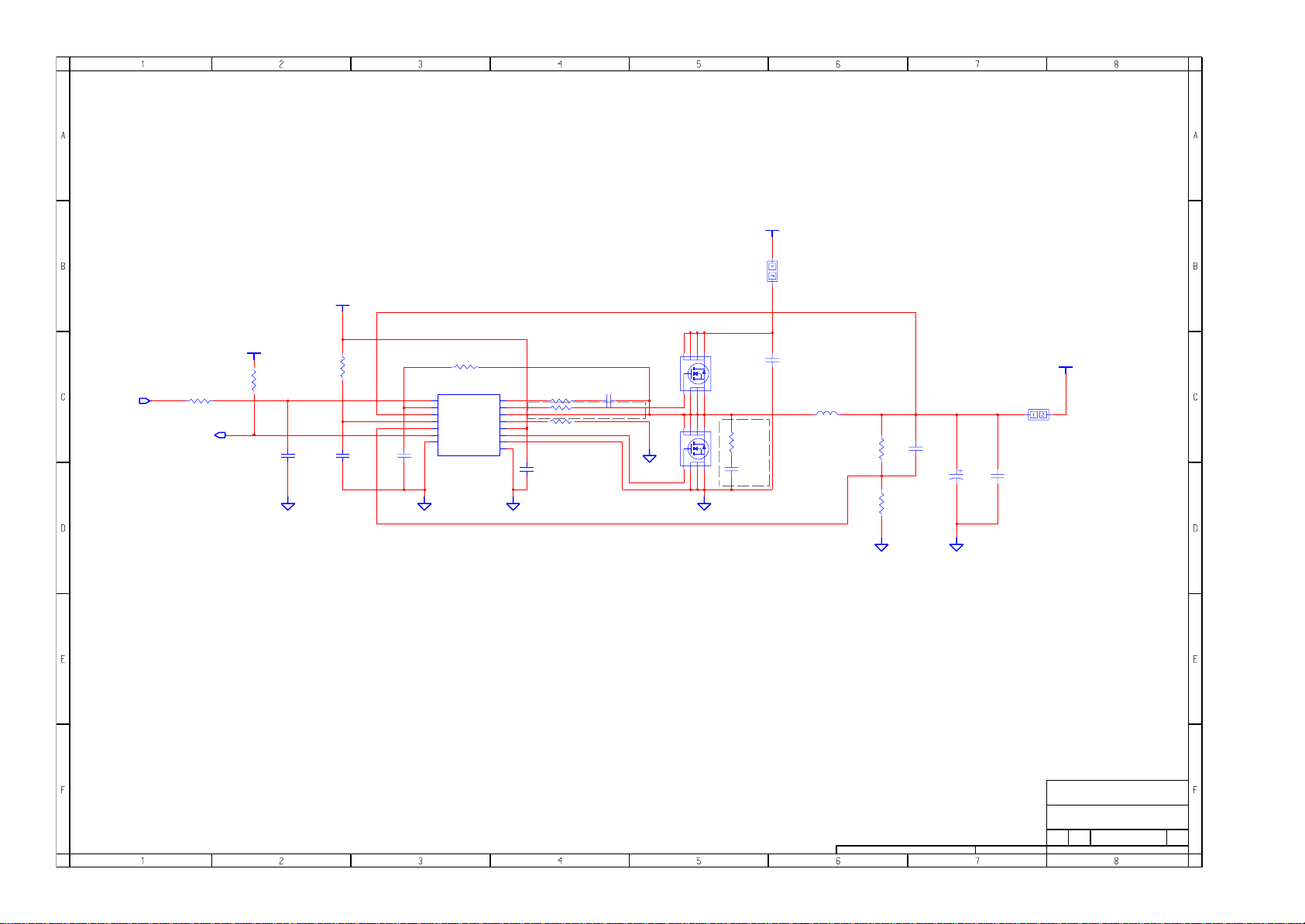

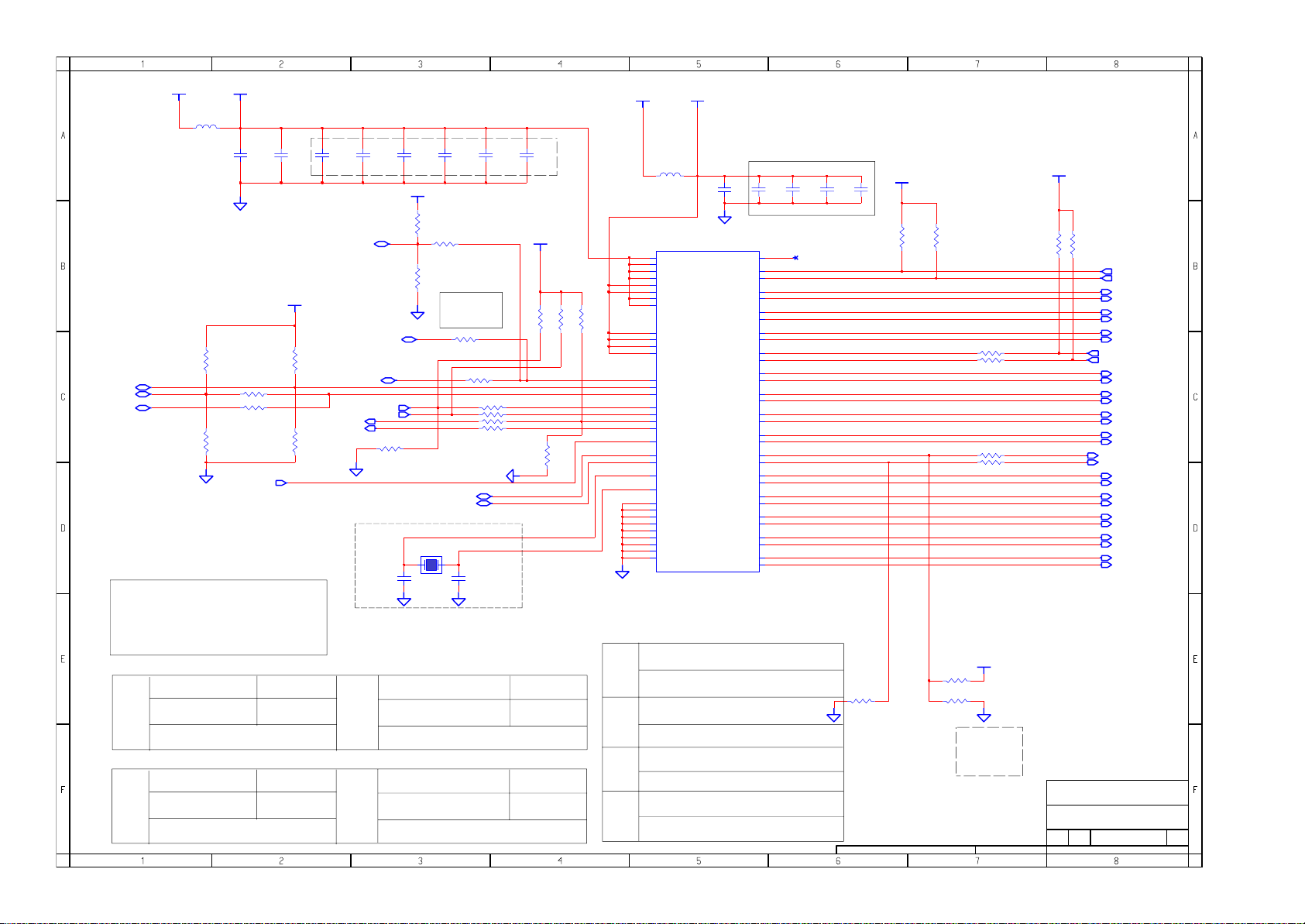

MCH_CFG(5)

MCH_CFG(13:12)

XOR/ALLZ

NOTE: CFG[2:0] STRP : 010b : 800 MT/S

MCH_CFG(5)

MCH_CFG(6)

MCH_CFG(7)

MCH_CFG(9)

MCH_CFG(10)

MCH_CFG(12)

MCH_CFG(13)

MCH_CFG(16)

LOW=DMIx2

HIGH=DMIx4

00=PARTIAL CLOCK GATING DISABLE

01=XOR MODE ENABLE

10=ALL-Z MODE ENABLE

11=NORMAL OPERATION

011b : 667 MT/S

19191919-

19191919-

1

2

R642

OPEN

1

R641

4.7K_5%

2

MCH_CFG(7)

(CPU Strap)

1

R640

OPEN

2

1

R624

OPEN

2

1

R625

OPEN

2

1

2

+V3S

9-,10-,11-,12-,13-,18-,19-,20-,24-,26-,27-,30-,32-,33-,34-,35-,36-,43-,44-,45-,46-,47-,49-,50-,51-,52-,54-,55-,56-,58-,62-

R700 10K_5%

+V1.8

8-,19-,23-,24-,26-,27-,62-

1

R658

1K_1%

2

1

R634

3K_1%

2

1

R635

1K_1%

2

MCH_CFG(20)

DIGITAL DISPLAY

PORT(SDVO/DP/iHDMI)

CONCURRENT WITH PCIE

12

12

10K_5%R701

VR_PWRGD_CK505

PM_PWROK

C629

1

2

1

2

1

2

0.01uF_16v

C630

1

2

0.01uF_16v

LOW=ONLY DIGITAL DISPLAY PORT

(SDVO/DP/iHDMI)OR PCIEIS OPERATIONAL

HIGH= DIGITAL DISPLAY PORT

(SDVO/DP/iHDMI)AND PCIE ARE OPERATING

VIA THE PEG PORT

C631

2.2uF_6.3v

C632

2.2uF_6.3v

PM_EXTTS#0_R

PM_EXTTS#1_R

34-

11-,19-,34-

19-

SM_RCOMP_VOH

19-

SM_RCOMP_VOL

LOW=RSVD

HIGH=Mobile CPU

MCH_CFG(16)

(FSB Dynamic

ODT)

1

R639

OPEN

OPEN

2

1

R643

OPEN

2

R686

0_5%_OPEN

12

12

R685

0_5%

MCH_CFG(9)

PCIE Graphics

Lane

LOW=Dynamic ODT

HIGH=Dynamic ODT

9-,10-,11-,12-,13-,18-,19-,20-,24-,26-,27-,30-,32-,33-,34-,35-,36-,43-,44-,45-,46-,47-,49-,50-,51-,52-,54-,55-,56-,58-,62-

CPU_BSEL0

CPU_BSEL1

CPU_BSEL2

MCH_CFG(17:3)

MCH_CFG(19)

MCH_CFG(20)

PM_SYNC#

H_DPRSTP#

PM_EXTTS#0

PM_EXTTS#1

PLT_RST#

PM_THRMTRIP#

PM_DPRSLPVR

MCH_CFG(19)

(DMI LANE

REVERSAL)

Disable

Enable

MCH_CFG(19)

MCH_CFG(20)

13-,15-

13-,15-

13-,15-

19-

LOW=NORMAL

HIGH=LANES REVERSED

LOW=Reverse Lane

HIGH=Normal operation

+V3S

1

R597R74

OPEN

2

19-

19-

R646

12

R647

12

R645

12

1919-

34-

R696 0_5%

11-,15-,33-

R622

2627-

R699 0_5%

35-,4314-,18-,3311-,34-

R596

R626

1

R644

OPEN

2

1K_5%

1K_5%

1K_5%

MCH_CFG(3)

MCH_CFG(4)

MCH_CFG(5)

MCH_CFG(6)

MCH_CFG(7)

MCH_CFG(8)

MCH_CFG(9)

MCH_CFG(10)

MCH_CFG(11)

MCH_CFG(12)

MCH_CFG(13)

MCH_CFG(14)

MCH_CFG(15)

MCH_CFG(16)

1

12

12

12

12

12

2

NOTE :

USE 4K-OHM RESISTOR WHEN INSTALLING

PULL-UP/PULL-DOWN RESISTOR ON ANY

MCH-CFG CONNECTION/PINS.

U509-2

M36

RSVD1

N36

RSVD2

R33

RSVD3

T33

RSVD4

AH9

RSVD5

AH10

RSVD6

AH12

RSVD7

AH13

RSVD8

K12

RSVD9

AL34

RSVD10

AK34

RSVD11

AN35

RSVD12

AM35

RSVD13

T24

RSVD14

B31

RSVD15

AJ6

RSVD16

M1

RSVD17

AY21

RSVD20

A47

RSVD21

BG23

RSVD22

BF23

RSVD23

BH18

RSVD24

BF18

RSVD25

T25

CFG_0

R25

CFG_1

P25

CFG_2

P20

CFG_3

P24

CFG_4

C25

CFG_5

N24

CFG_6

M24

CFG_7

E21

CFG_8

C23

CFG_9

C24

CFG_10

N21

CFG_11

P21

CFG_12

T21

CFG_13

R20

CFG_14

M20

CFG_15

L21

CFG_16

H21

0_5%

0_5%R698

100_5%

0_5%

PM_EXTTS#0_R

PM_EXTTS#1_R

TP2002

TP2001

P29

R28

T28

R29

N33

P32

AT40

AT11

T20

R32

BG48

BF48

BD48

BC48

BH47

BG47

BE47

BH46

BF46

BG45

BH44

BH43

BH6

BH5

BG4

BH3

BF3

BH2

BG2

BE2

BG1

BF1

BD1

BC1

B7

F1

CFG_17

CFG_18

CFG_19

CFG_20

PM_SYNC#

PM_DPRSTP#

PM_EXT_TS#_0

PM_EXT_TS#_1

PWROK

RSTIN#

THERMTRIP#

DPRSLPVR

NC_1

NC_2

NC_3

NC_4

NC_5

NC_6

NC_7

NC_8

NC_9

NC_10

NC_11

NC_12

NC_13

NC_14

NC_15

NC_16

NC_17

NC_18

NC_19

NC_20

NC_21

NC_22

NC_23

NC_24

NC_25

ITL_CANTIGA_GM_FCBGA_1329P

SA_CK_0

SA_CK_1

SB_CK_0

SB_CK_1

SA_CK#_0

SA_CK#_1

SB_CK#_0

SB_CK#_1

SA_CKE_0

SA_CKE_1

SB_CKE_0

SB_CKE_1

SA_CS#_0

SA_CS#_1

SB_CS#_0

SB_CS#_1

SA_ODT_0

SA_ODT_1

SB_ODT_0

SB_ODT_1

SM_RCOMP

SM_RCOMP#

SM_RCOMP_VOH

SM_RCOMP_VOL

SM_VREF

SM_PWROK

SM_REXT

SM_DRAMRST#

DPLL_REF_CLK

DPLL_REF_CLK#

DPLL_REF_SSCLK

DPLL_REF_SSCLK#

PEG_CLK

PEG_CLK#

DMI_RXN_0

DMI_RXN_1

DMI_RXN_2

DMI_RXN_3

DMI_RXP_0

DMI_RXP_1

DMI_RXP_2

DMI_RXP_3

DMI_TXN_0

DMI_TXN_1

DMI_TXN_2

DMI_TXN_3

DMI_TXP_0

DMI_TXP_1

DMI_TXP_2

DMI_TXP_3

GFX_VID_0

GFX_VID_1

GFX_VID_2

GFX_VID_3

GFX_VID_4

GFX_VR_EN

CL_CLK

CL_DATA

CL_PWROK

CL_RST#

CL_VREF

DDPC_CTRLCLK

DDPC_CTRLDATA

SDVO_CTRLCLK

SDVO_CTRLDATA

CLKREQ#

ICH_SYNC#

TSATN

HDA_BCLK

HDA_RST#

HDA_SDI

HDA_SDO

HDA_SYNC

AP24

AT21

AV24

AU20

AR24

AR21

AU24

AV20

BC28

AY28

AY36

BB36

BA17

AY16

AV16

AR13

BD17

AY17

BF15

AY13

BG22

BH21

BF28

BH28

AV42

AR36

BF17

BC36

B38

A38

E41

F41

F43

E43

AE41

AE37

AE47

AH39

AE40

AE38

AE48

AH40

AE35

AE43

AE46

AH42

AD35

AE44

AF46

AH43

B33

B32

G33

F33

E33

C34

AH37

AH36

AN36

AJ35

AH34

N28

OPEN

M28

OPEN

G36

0_5%

E36

0_5%

K36

H36

B12

B28

B30

B29

C29

A28

12

R86 0_5%

12

R636 499_1%

TP2000

DMI_TXN(0)

DMI_TXN(1)

DMI_TXN(2)

DMI_TXN(3)

DMI_TXP(0)

DMI_TXP(1)

DMI_TXP(2)

DMI_TXP(3)

DMI_RXN(0)

DMI_RXN(1)

DMI_RXN(2)

DMI_RXN(3)

DMI_RXP(0)

DMI_RXP(1)

DMI_RXP(2)

DMI_RXP(3)

12

R684

0_5%

CLOSE

12

R648

12

R649

12

R663

12

R664

13-

CLKREQ_R_MCH#

34-

MCH_ICH_SYNC#

+VCCP

56_5% R621

2

R672

12

33_1%

R929

9-,10-,11-,12-,13-,18-,19-,20-,24-,26-,27-,30-,32-,33-,34-,35-,36-,43-,44-,45-,46-,47-,49-,50-,51-,52-,54-,55-,56-,58-,62-

12

OPEN

R662

1

2.2K_5%

33-

HDA_BIT_CLK

33-

HDA_RST#

33-

HDA_SDIN3

33-

HDA_SDOUT

33-

HDA_SYNC

CHANGE by OF

26-,2826-,2827-,2827-,28-

26-,2826-,2827-,2827-,28-

26-,2826-,2827-,2827-,28-

13131313-

131334-

34-

34-

34-

10-

DFGT_VID_0

10-

DFGT_VID_1

10-

DFGT_VID_2

10-

DFGT_VID_3

10-

DFGT_VID_4

10-

DFGT_VR_EN

34-

CL_CLK0

34-

CL_DATA0

11-,19-,34-

PM_PWROK

34-

CL_RST#0

49-

TMDS_SCLK

49-

TMDS_SDATA

PM:OPEN

1

1

R665

2.2K_5%

2

2

9-,13-,14-,15-,16-,19-,20-,21-,23-,24-,33-,36-,62-

Drawer_Name

26-

MA_CLK_DDR1

26-

MA_CLK_DDR2

27-

MB_CLK_DDR1

27-

MB_CLK_DDR2

26-

MA_CLK_DDR1#

26-

MA_CLK_DDR2#

27-

MB_CLK_DDR1#

27-

MB_CLK_DDR2#

MA_CKE0

MA_CKE1

MB_CKE0

MB_CKE1

MA_CS0#

MA_CS1#

MB_CS0#

MB_CS1#

MA_ODT0

MA_ODT1

MB_ODT0

MB_ODT1

19-

SM_RCOMP

19-

SM_RCOMP#

19-

SM_RCOMP_VOH

19-

SM_RCOMP_VOL

CLK_R_DREF

CLK_R_DREF#

CLKSS1_R_DREF

CLKSS1_R_DREF#

CLK_PEG_MCH

CLK_PEG_MCH#

DMI_TXN(3:0)

DMI_TXP(3:0)

DMI_RXN(3:0)

DMI_RXP(3:0)

1

2

C683

0.1uF_16v

+V3S

24-Aug-2007

+V1.8

8-,19-,23-,24-,26-,27-,62-

12

R637

80.6_1%

12

R638

80.6_1%

C682

1

2

0.1uF_16v

+VCCP

9-,13-,14-,15-,16-,19-,20-,21-,23-,24-,33-,36-,62-

1

R688

1K_1%

2

12

R687

499_1%

INVENTEC

TITLE

PS10

CRESTLINE-1

SIZE

A3

CS

SHEET

19-

SM_RCOMP

19-

SM_RCOMP#

8-,26-,27-

M_VREF

DOC. NUMBERCODE

Model_No X01

6219

REV

Loading...

Loading...