Page 1

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

CA203

2012/10/26

2013/01/11

2013-ECO-000478

A

HalogenFree+RoHS2

3

A01

CS

C

1310A2546301-0-0

A

6050A2546301

Yang Danny

Yang Danny

CA203 Mother Board

Chang Jason

Chang Jason

Chang Jason

Chang Jason

Huang Martin

Huang Martin

2012/10/26

2012/10/26

2012/10/26

2012/10/26

2012/10/26

2012/10/26

2012/10/26

2012/10/26

42

1

THIS DRAWING AND SPECIFICATIONS, HEREIN, ARE THE PROPERTY OF INVENTEC

CORPORATION AND SHALL NOT BE REPODUCED, COPIED, OR USED IN WHOLE OR

IN PART AS THE BASIS FOR THE MANUFACTURE OR SALE OF ITEMS WITHOUT

WRITTEN PERMISSION, INVENTEC CORPORATION 2011 ALL RIGHT RESERVED

HSF Property :

DATE

CHANGE NO. REV

DRAWER

DESIGN

CHECK

RESPONSIBLE

SIZE =

FILE NAME :

P/N

DATEDATEEE POWER

INVENTEC

TITLE

SIZE CODE DOC. NUMBER REVVER :

SHEET OF

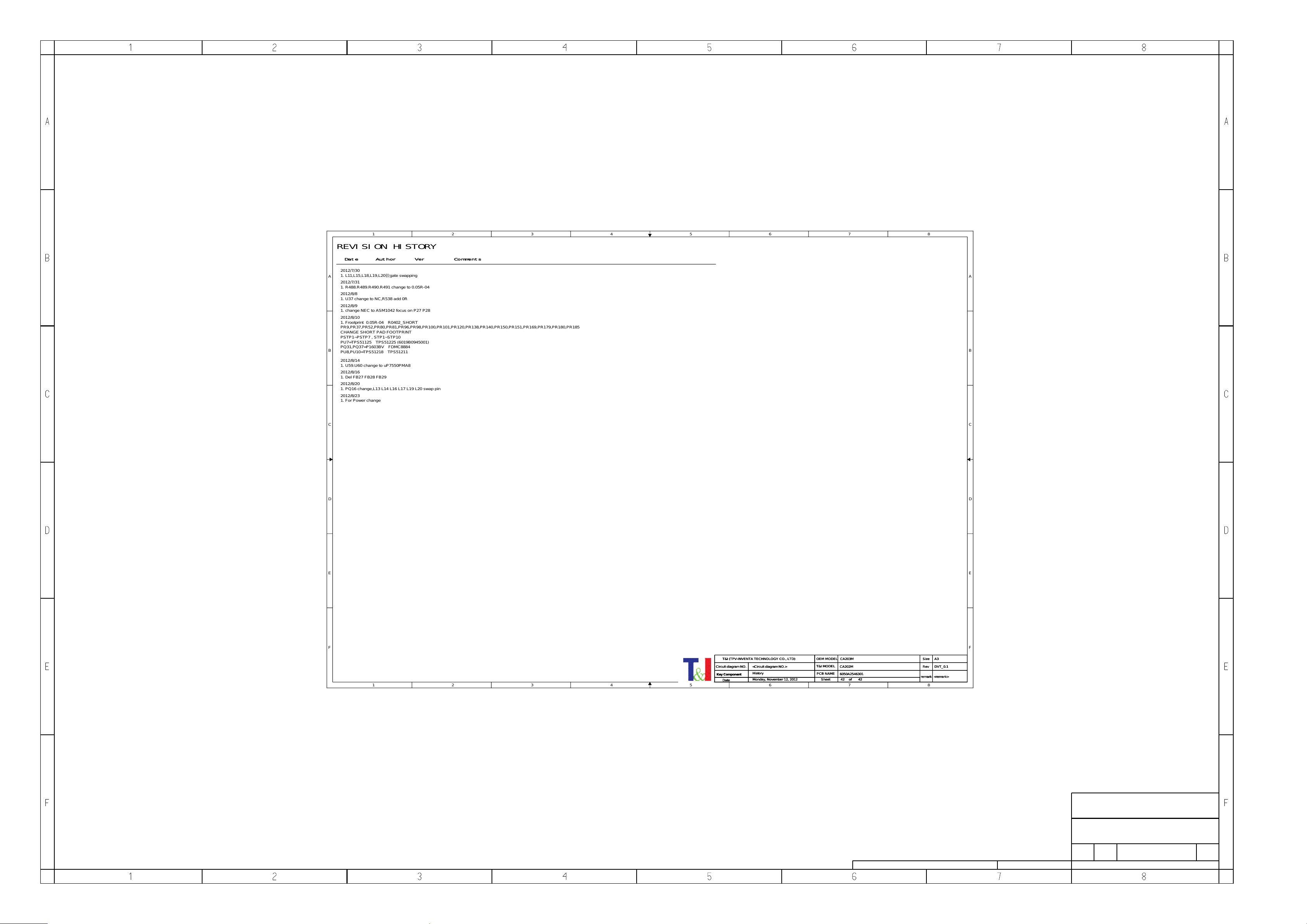

Page 2

1

1

2

2

3

3

4

4

5

5

6

6

7

7

8

8

A A

B B

C C

D D

E E

F F

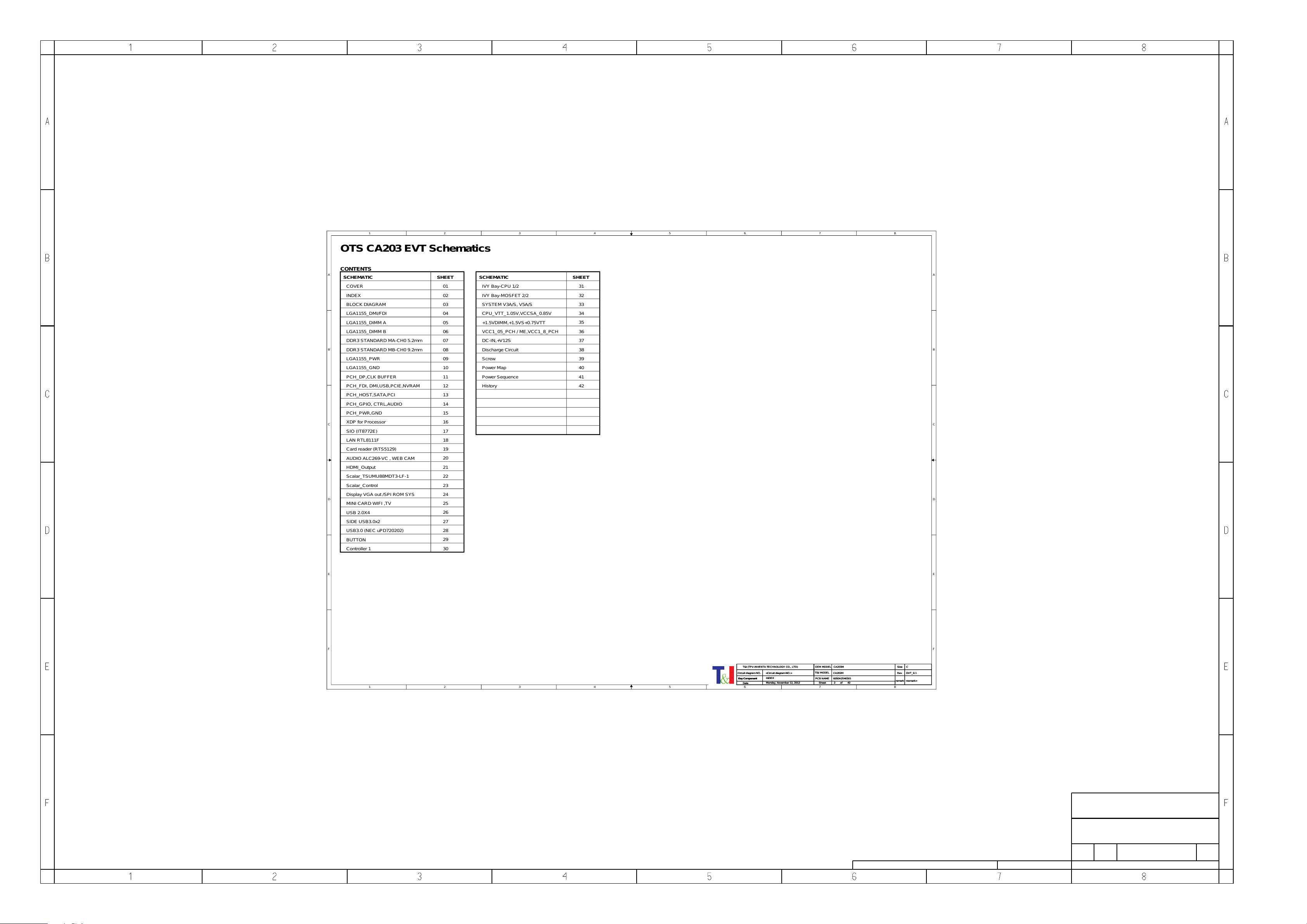

01

BLOCK DIAGRAM

SCHEMATIC

LGA1155_DMI/FDI

INDEX

CONTENTS

SHEET

LGA1155_DIMM A

LGA1155_PWR

DDR3 STANDARD MB-CH0 9.2mm

PCH_DP,CLK BUFFER

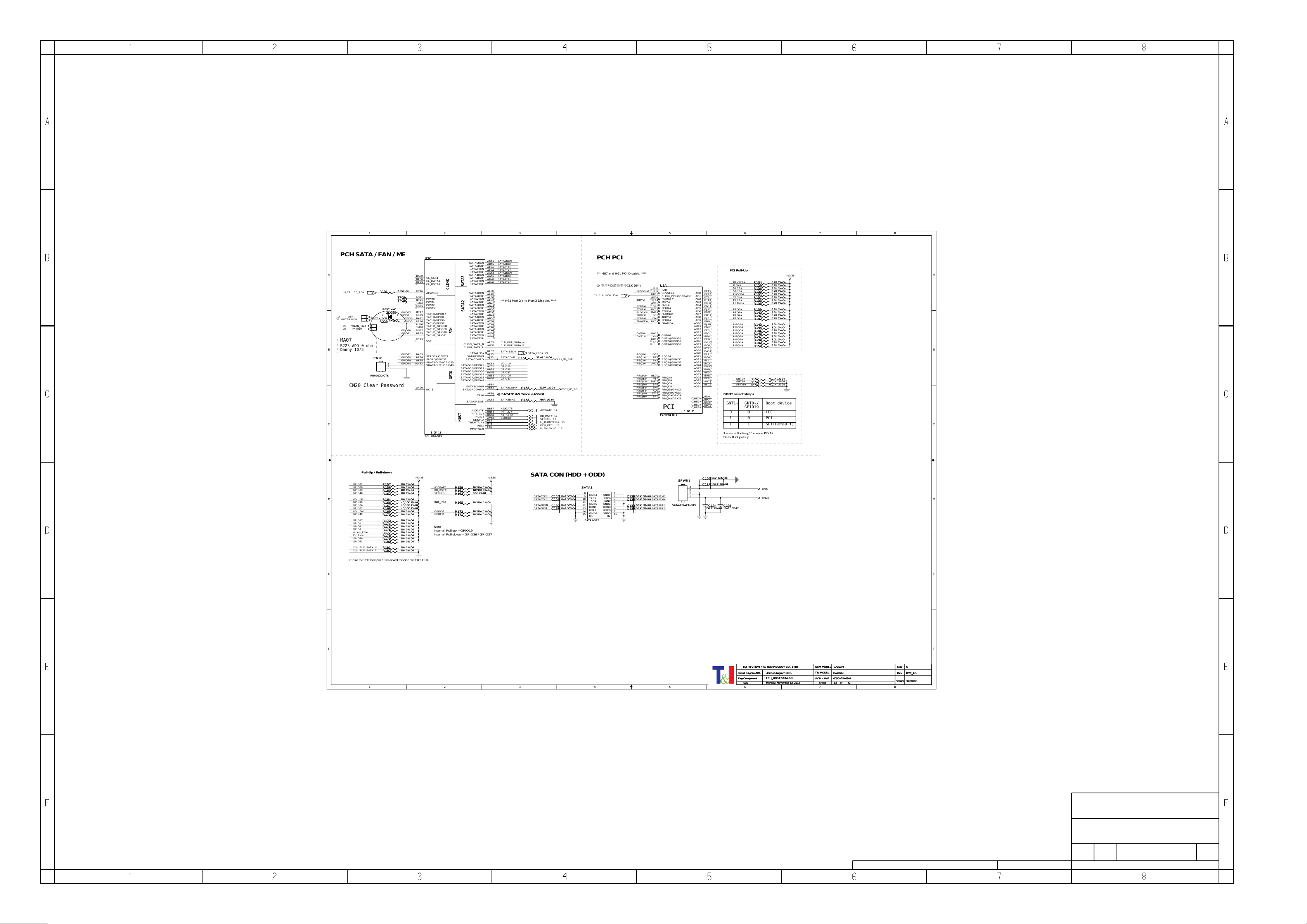

PCH_HOST,SATA,PCI

PCH_PWR,GND

OTS CA203 EVT Schematics

DDR3 STANDARD MA-CH0 5.2mm

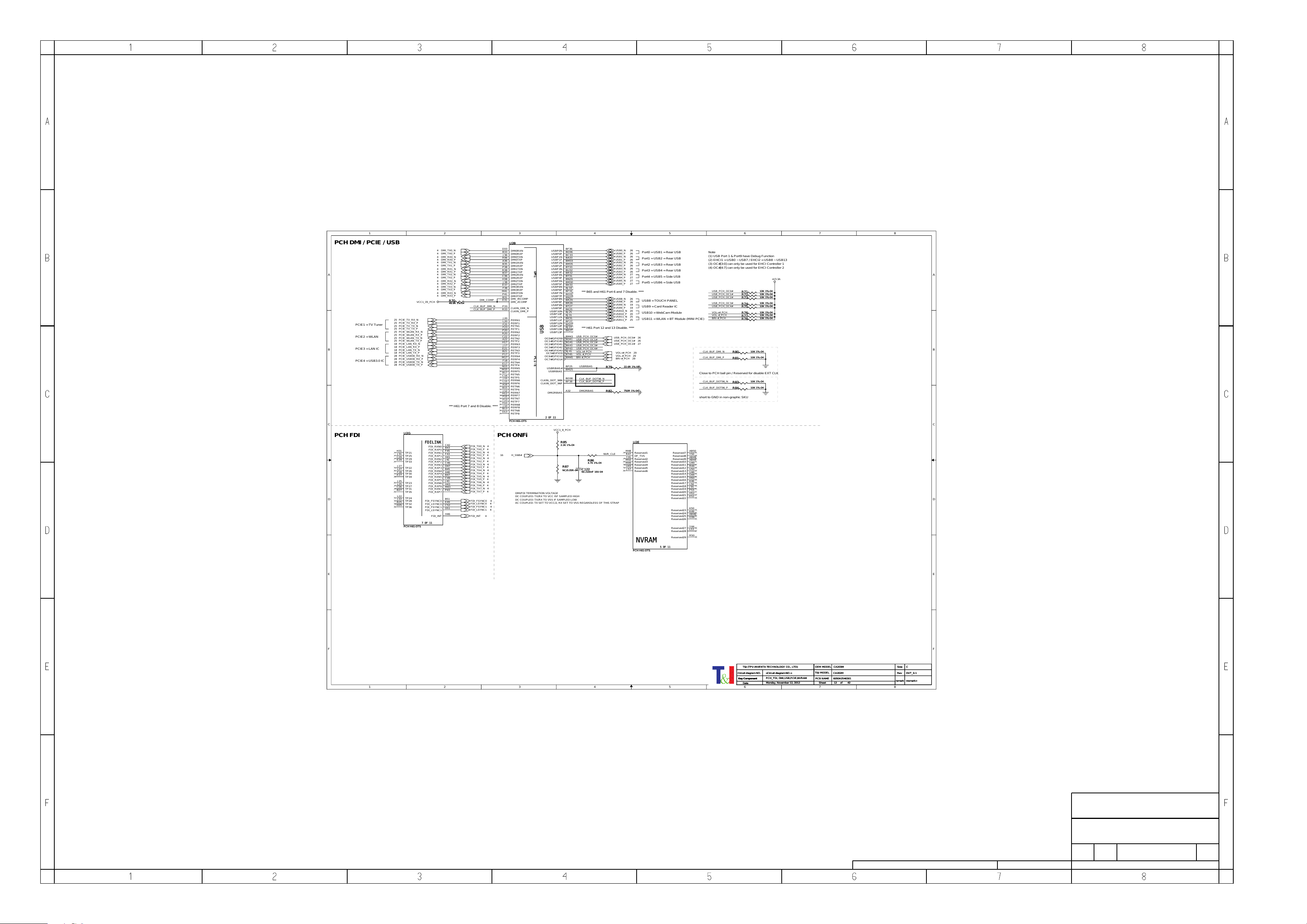

PCH_FDI, DMI,USB,PCIE,NVRAM

PCH_GPIO, CTRL,AUDIO

XDP for Processor

SIO (IT8772E)

LAN RTL8111F

SCHEMATIC SHEET

Card reader (RTS5129)

AUDIO ALC269-VC , WEB CAM

02

03

04

05

06

07

08

09

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

32

33

34

35

36

37

31

HDMI_Output

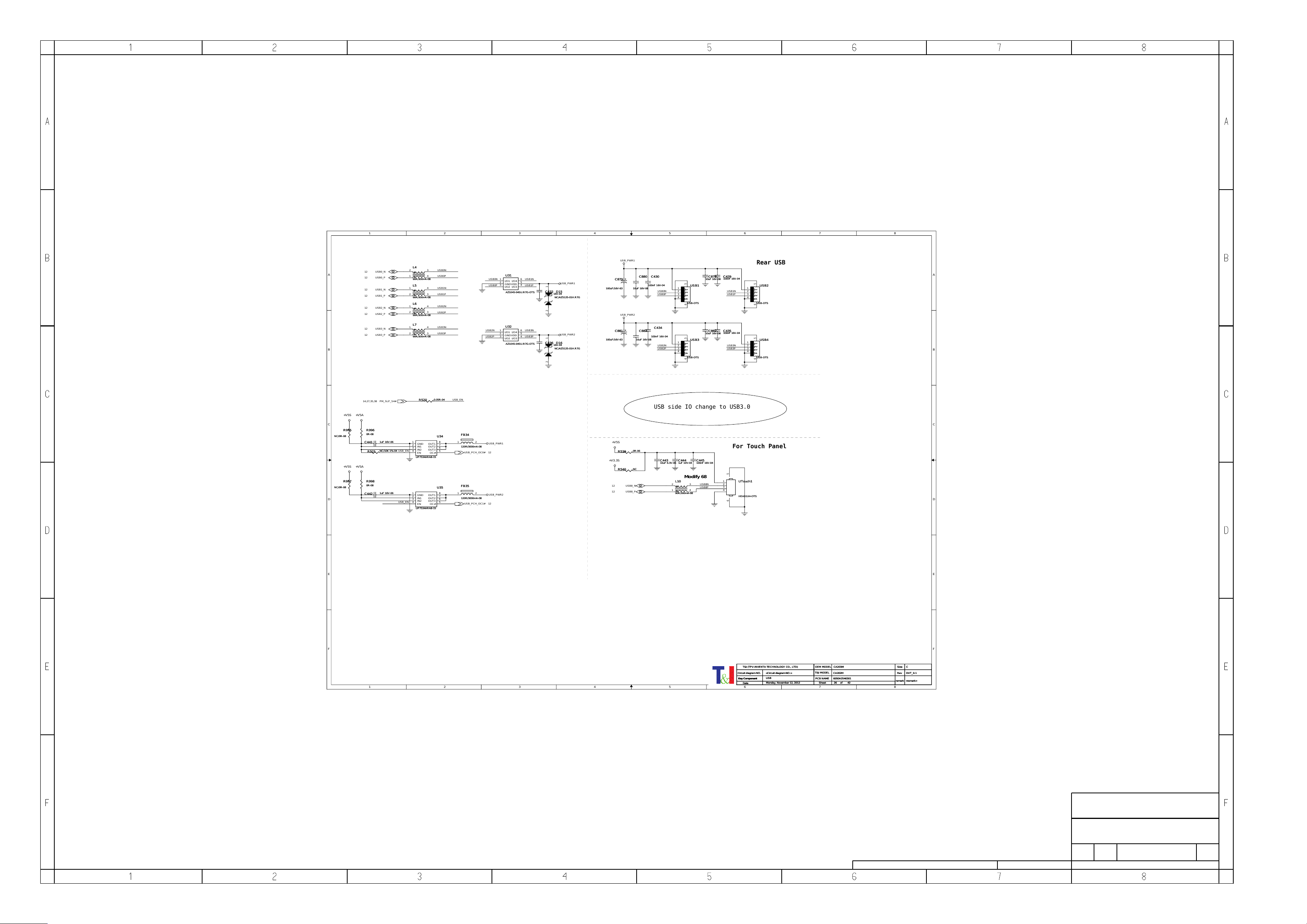

SIDE USB3.0x2

Scalar_TSUMU88MDT3-LF-1

Display VGA out /SPI ROM SYS

USB 2.0X4

MINI CARD WIFI ,TV

USB3.0 (NEC uPD720202)

Controller 1

BUTTON

VCC1_05_PCH / ME,VCC1_8_PCH

Discharge Circuit

DC-IN,+V12S

Power Sequence

Power Map

Screw

History

38

39

40

41

CPU_VTT_1.05V,VCCSA_0.85V

SYSTEM V3A/S, V5A/S

+1.5VDIMM,+1.5VS+0.75VTT

IVY Bay-MOSFET 2/2

Scalar_Control

LGA1155_GND

LGA1155_DIMM B

42

IVY Bay-CPU 1/2COVER

OEM MODEL

Size

Rev

Date

Sheet

of

T&I MODEL

PCB NAME

remark

T&I (TPV-INVENTA TECHNOLOGY CO., LTD)

Key Component

Circuit diagram NO. CA202M DVT_0.1

CA203M C

242Monday, November 12, 2012

6050A2546301

<remark>

INDEX

<Circuit diagram NO.>

OEM MODEL

Size

Rev

Date

Sheet

of

T&I MODEL

PCB NAME

remark

T&I (TPV-INVENTA TECHNOLOGY CO., LTD)

Key Component

Circuit diagram NO. CA202M DVT_0.1

CA203M C

242Monday, November 12, 2012

6050A2546301

<remark>

INDEX

<Circuit diagram NO.>

OEM MODEL

Size

Rev

Date

Sheet

of

T&I MODEL

PCB NAME

remark

T&I (TPV-INVENTA TECHNOLOGY CO., LTD)

Key Component

Circuit diagram NO. CA202M DVT_0.1

CA203M C

242Monday, November 12, 2012

6050A2546301

<remark>

INDEX

<Circuit diagram NO.>

Yang Danny

CA203 Mother Board

A3

CS

1310A2546301

A

42

2

INVENTEC

TITLE

SIZE CODE DOC. NUMBER REV

CHANGE by SHEET OF

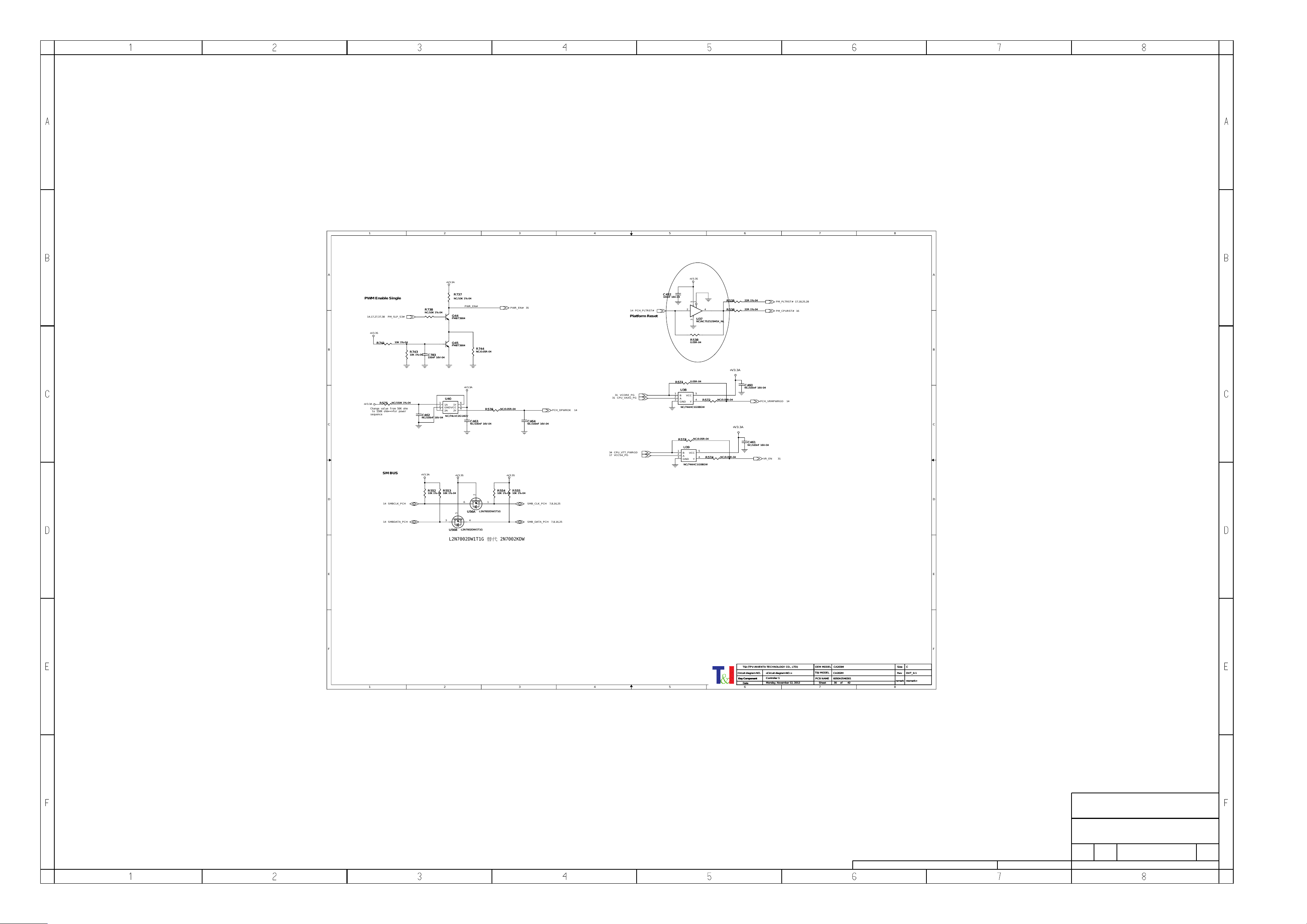

Page 3

1

1

2

2

3

3

4

4

5

5

6

6

7

7

8

8

A A

B B

C C

D D

E E

F F

SPI BIOS

SPI

LPC

SIO (IT8772E)

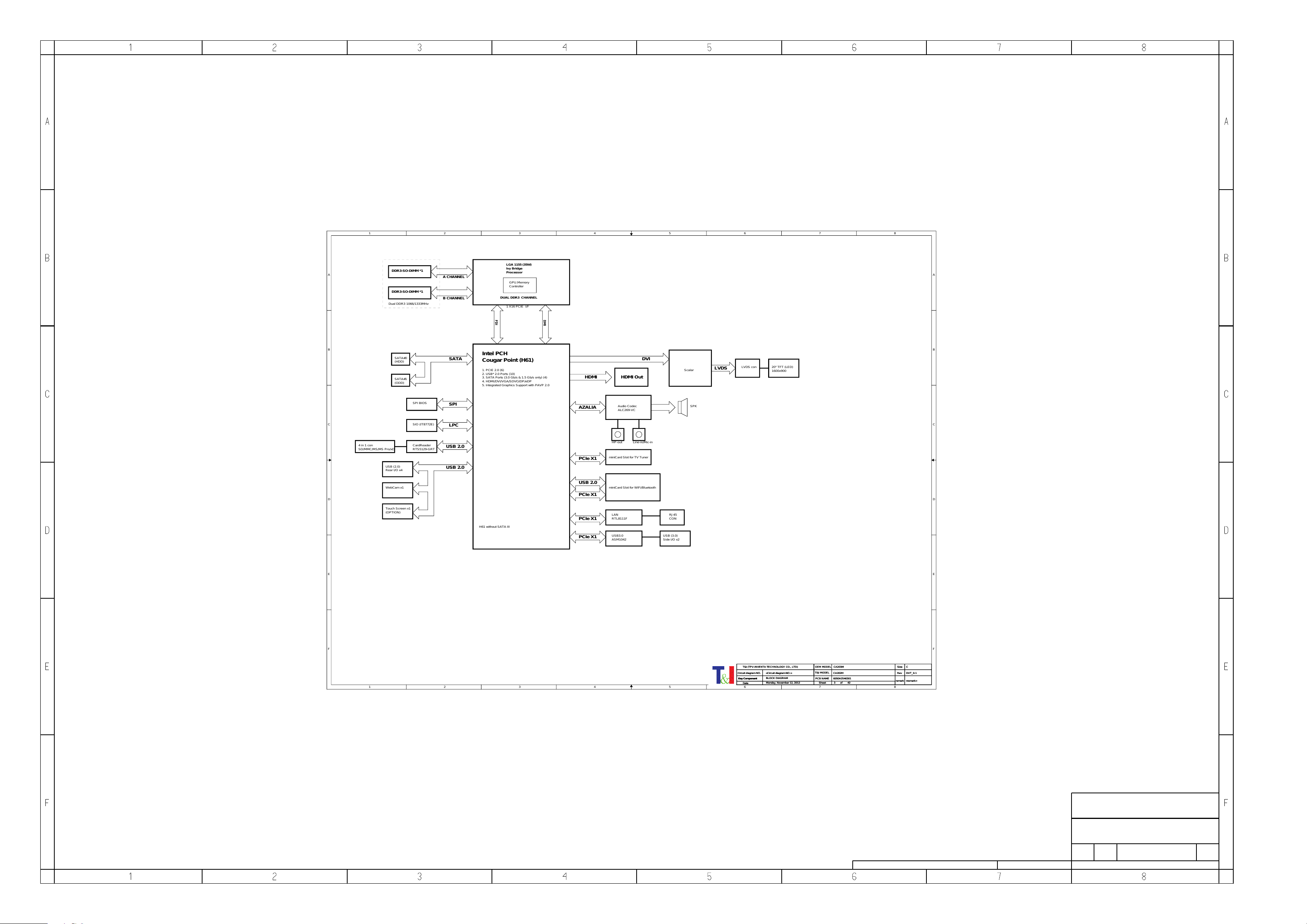

LGA 1155 (35W)

Ivy Bridge

Processor

GPU.Memory

Controller

DUAL DDR3 CHANNEL

1 X16 PCIE I/F

FDI

DMI

Intel PCH

Cougar Point (H61)

1. PCIE 2.0 (6)

2. USB* 2.0 Ports (10)

3. SATA Ports (3.0 Gb/s & 1.5 Gb/s only) (4)

4. HDMI/DVI/VGA/SDVO/DP/eDP

5. Integrated Graphics Support with PAVP 2.0

CardReader

RTS5129-GRT

4 in 1 con

SD/MMC/MS/MS Pro/xD

DDR3-SO-DIMM *1

DDR3-SO-DIMM *1

Dual DDR3 1066/1333MHz

A CHANNEL

B CHANNEL

miniCard Slot for TV Tuner

miniCard Slot for WiFi/Bluetooth

PCIe X1

USB 2.0

Audio Codec

ALC269-VC

AZALIA

Line-in/Mic-in

Scalar

SPK

DVI

HDMI HDMI Out

PCIe X1

USB 2.0

H61 without SATA III

HP-out

20" TFT (LED)

1600x900

LVDS

LVDS con

Touch Screen x1

(OPTION)

WebCam x1

USB 2.0

USB (2.0)

Rear I/O x4

SATA#0

(HDD)

SATA#1

(ODD)

SATA

RJ45

CON

LAN

RTL8111F

PCIe X1

PCIe X1

USB3.0

ASM1042

USB (3.0)

Side I/O x2

OEM MODEL

Size

Rev

Date

Sheet

of

T&I MODEL

PCB NAME

remark

T&I (TPV-INVENTA TECHNOLOGY CO., LTD)

Key Component

Circuit diagram NO. CA202M DVT_0.1

CA203M C

342Monday, November 12, 2012

6050A2546301

<remark>

BLOCK DIAGRAM

<Circuit diagram NO.>

OEM MODEL

Size

Rev

Date

Sheet

of

T&I MODEL

PCB NAME

remark

T&I (TPV-INVENTA TECHNOLOGY CO., LTD)

Key Component

Circuit diagram NO. CA202M DVT_0.1

CA203M C

342Monday, November 12, 2012

6050A2546301

<remark>

BLOCK DIAGRAM

<Circuit diagram NO.>

OEM MODEL

Size

Rev

Date

Sheet

of

T&I MODEL

PCB NAME

remark

T&I (TPV-INVENTA TECHNOLOGY CO., LTD)

Key Component

Circuit diagram NO. CA202M DVT_0.1

CA203M C

342Monday, November 12, 2012

6050A2546301

<remark>

BLOCK DIAGRAM

<Circuit diagram NO.>

Yang Danny

CA203 Mother Board

A3

CS

1310A2546301

A

42

3

INVENTEC

TITLE

SIZE CODE DOC. NUMBER REV

CHANGE by SHEET OF

Page 4

1

1

2

2

3

3

4

4

5

5

6

6

7

7

8

8

A A

B B

C C

D D

E E

F F

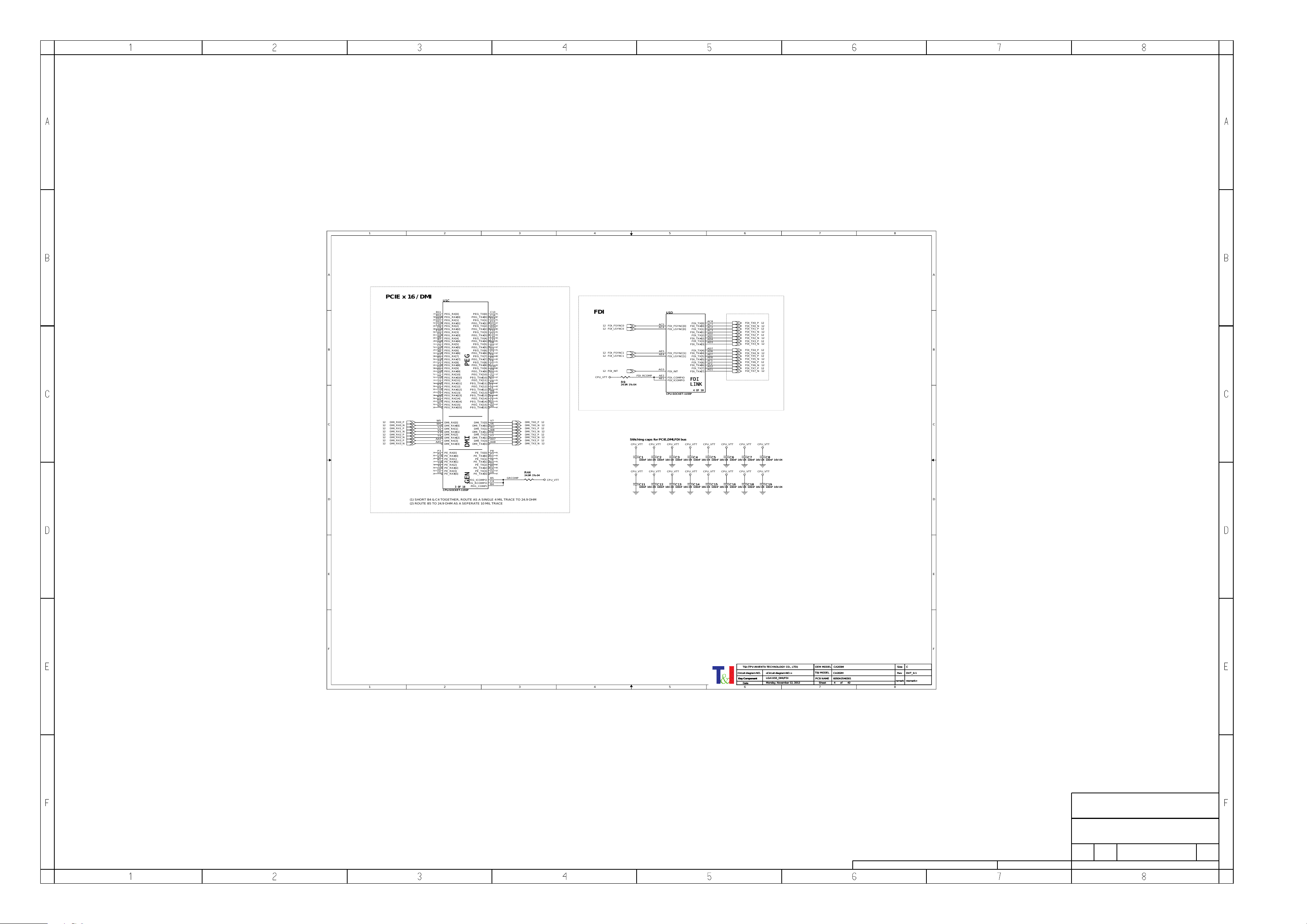

FDI

PCIE x 16 / DMI

Stitching caps for PCIE,DMI,FDI bus

(1) SHORT B4 & C4 TOGETHER, ROUTE AS A SINGLE 4 MIL TRACE TO 24.9 OHM

(2) ROUTE B5 TO 24.9 OHM AS A SEPERATE 10 MIL TRACE

FDI_RCOMP

GRCOMP

CPU_VTT

CPU_VTT

CPU_VTTCPU_VTT CPU_VTT

CPU_VTT CPU_VTTCPU_VTTCPU_VTT CPU_VTT CPU_VTT CPU_VTT

CPU_VTTCPU_VTT CPU_VTTCPU_VTT

CPU_VTT

CPU_VTT

FDI_FSYNC012

FDI_LSYNC012

FDI_TX0_P 12

FDI_TX1_P 12

FDI_INT12

FDI_TX2_P 12

FDI_TX3_P 12

FDI_TX2_N 12

FDI_TX3_N 12

FDI_TX0_N 12

FDI_TX1_N 12

FDI_TX4_P 12

FDI_TX5_P 12

FDI_TX6_P 12

FDI_TX7_P 12

FDI_TX6_N 12

FDI_TX7_N 12

FDI_TX4_N 12

FDI_TX5_N 12

FDI_FSYNC112

FDI_LSYNC112

DMI_TX0_N 12

DMI_TX1_N 12

DMI_TX1_P 12

DMI_TX2_N 12

DMI_TX2_P 12

DMI_TX3_N 12

DMI_TX3_P 12

DMI_TX0_P 12

DMI_RX0_N12

DMI_RX1_N12

DMI_RX1_P12

DMI_RX2_N12

DMI_RX2_P12

DMI_RX3_N12

DMI_RX3_P12

DMI_RX0_P12

OEM MODEL

Size

Rev

Date

Sheet

of

T&I MODEL

PCB NAME

remark

T&I (TPV-INVENTA TECHNOLOGY CO., LTD)

Key Component

Circuit diagram NO. CA202M DVT_0.1

CA203M C

442Monday, November 12, 2012

6050A2546301

<remark>

LGA1155_DMI/FDI

<Circuit diagram NO.>

OEM MODEL

Size

Rev

Date

Sheet

of

T&I MODEL

PCB NAME

remark

T&I (TPV-INVENTA TECHNOLOGY CO., LTD)

Key Component

Circuit diagram NO. CA202M DVT_0.1

CA203M C

442Monday, November 12, 2012

6050A2546301

<remark>

LGA1155_DMI/FDI

<Circuit diagram NO.>

OEM MODEL

Size

Rev

Date

Sheet

of

T&I MODEL

PCB NAME

remark

T&I (TPV-INVENTA TECHNOLOGY CO., LTD)

Key Component

Circuit diagram NO. CA202M DVT_0.1

CA203M C

442Monday, November 12, 2012

6050A2546301

<remark>

LGA1155_DMI/FDI

<Circuit diagram NO.>

C1

100nF 16V-04

C1

100nF 16V-04

C5

100nF 16V-04

C5

100nF 16V-04

C16

100nF 16V-04

C16

100nF 16V-04

C18

100nF 16V-04

C18

100nF 16V-04

C6

100nF 16V-04

C6

100nF 16V-04C7100nF 16V-04

C7

100nF 16V-04

R44

24.9R 1%-04

R44

24.9R 1%-04

4 OF 10

FDI

LINK

U1D

CPU-SOCKET-1155P

4 OF 10

FDI

LINK

U1D

CPU-SOCKET-1155P

FDI_FSYNC[0]

AC5

FDI_LSYNC[0]

AC4

FDI_FSYNC[1]

AE5

FDI_LSYNC[1]

AE4

FDI_INT

AG3

FDI_TX[0]

AC8

FDI_TX#[0]

AC7

FDI_TX[1]

AC2

FDI_TX#[1]

AC3

FDI_TX[2]

AD2

FDI_TX#[2]

AD1

FDI_TX[3]

AD4

FDI_TX#[3]

AD3

FDI_TX[4]

AD7

FDI_TX#[4]

AD6

FDI_TX[5]

AE7

FDI_TX#[5]

AE8

FDI_TX[6]

AF3

FDI_TX#[6]

AF2

FDI_TX[7]

AG2

FDI_TX#[7]

AG1

FDI_COMPIO

AE2

FDI_ICOMPO

AE1

C14

100nF 16V-04

C14

100nF 16V-04

C19

100nF 16V-04

C19

100nF 16V-04

3 OF 10

PEGDMIGEN

U1C

CPU-SOCKET-1155P

3 OF 10

PEGDMIGEN

U1C

CPU-SOCKET-1155P

PEG_RX[0]

B11

PEG_RX#[0]

B12

PEG_RX[1]

D12

PEG_RX#[1]

D11

PEG_RX[2]

C10

PEG_RX#[2]

C9

PEG_RX[3]

E10

PEG_RX#[3]

E9

PEG_RX[4]

B8

PEG_RX#[4]

B7

PEG_RX[5]

C6

PEG_RX#[5]

C5

PEG_RX[6]

A5

PEG_RX#[6]

A6

PEG_RX[7]

E2

PEG_RX#[7]

E1

PEG_RX[8]

F4

PEG_RX#[8]

F3

PEG_RX[9]

G2

PEG_RX#[9]

G1

PEG_RX[10]

H3

PEG_RX#[10]

H4

PEG_RX[11]

J1

PEG_RX#[11]

J2

PEG_RX[12]

K3

PEG_RX#[12]

K4

PEG_RX[13]

L1

PEG_RX#[13]

L2

PEG_RX[14]

M3

PEG_RX#[14]

M4

PEG_RX[15]

N1

PEG_RX#[15]

N2

DMI_RX[0]

W5

DMI_RX#[0]

W4

DMI_RX[1]

V3

DMI_RX#[1]

V4

DMI_RX[2]

Y3

DMI_RX#[2]

Y4

DMI_RX[3]

AA4

DMI_RX#[3]

AA5

PEG_TX[0]

C13

PEG_TX#[0]

C14

PEG_TX[1]

E14

PEG_TX#[1]

E13

PEG_TX[2]

G14

PEG_TX#[2]

G13

PEG_TX[3]

F12

PEG_TX#[3]

F11

PEG_TX[4]

J14

PEG_TX#[4]

J13

PEG_TX[5]

D8

PEG_TX#[5]

D7

PEG_TX[6]

D3

PEG_TX#[6]

C3

PEG_TX[7]

E6

PEG_TX#[7]

E5

PEG_TX[8]

F8

PEG_TX#[8]

F7

PEG_TX[9]

G10

PEG_TX#[9]

G9

PEG_TX[10]

G5

PEG_TX#[10]

G6

PEG_TX[11]

K7

PEG_TX#[11]

K8

PEG_TX[12]

J5

PEG_TX#[12]

J6

PEG_TX[13]

M8

PEG_TX#[13]

M7

PEG_TX[14]

L6

PEG_TX#[14]

L5

PEG_TX[15]

N5

PEG_TX#[15]

N6

DMI_TX[0]

V7

DMI_TX#[0]

V6

DMI_TX[1]

W7

DMI_TX#[1]

W8

DMI_TX[2]

Y6

DMI_TX#[2]

Y7

DMI_TX[3]

AA7

DMI_TX#[3]

AA8

PEG_COMPI

B4

PEG_ICOMPO

B5

PEG_RCOMPO

C4

PE_RX[0]

P3

PE_RX#[0]

P4

PE_RX[1]

R2

PE_RX#[1]

R1

PE_RX[2]

T4

PE_RX#[2]

T3

PE_RX[3]

U2

PE_RX#[3]

U1

PE_TX[0]

P8

PE_TX#[0]

P7

PE_TX[1]

T7

PE_TX#[1]

T8

PE_TX[2]

R6

PE_TX#[2]

R5

PE_TX[3]

U5

PE_TX#[3]

U6

C2

100nF 16V-04

C2

100nF 16V-04

C15

100nF 16V-04

C15

100nF 16V-04

R9

24.9R 1%-04

R9

24.9R 1%-04

C3

100nF 16V-04

C3

100nF 16V-04

C8

100nF 16V-04

C8

100nF 16V-04

C12

100nF 16V-04

C12

100nF 16V-04

C4

100nF 16V-04

C4

100nF 16V-04

C11

100nF 16V-04

C11

100nF 16V-04

C13

100nF 16V-04

C13

100nF 16V-04

Yang Danny

CA203 Mother Board

A3

CS

1310A2546301

A

42

4

INVENTEC

TITLE

SIZE CODE DOC. NUMBER REV

CHANGE by SHEET OF

Page 5

1

1

2

2

3

3

4

4

5

5

6

6

7

7

8

8

A A

B B

C C

D D

E E

F F

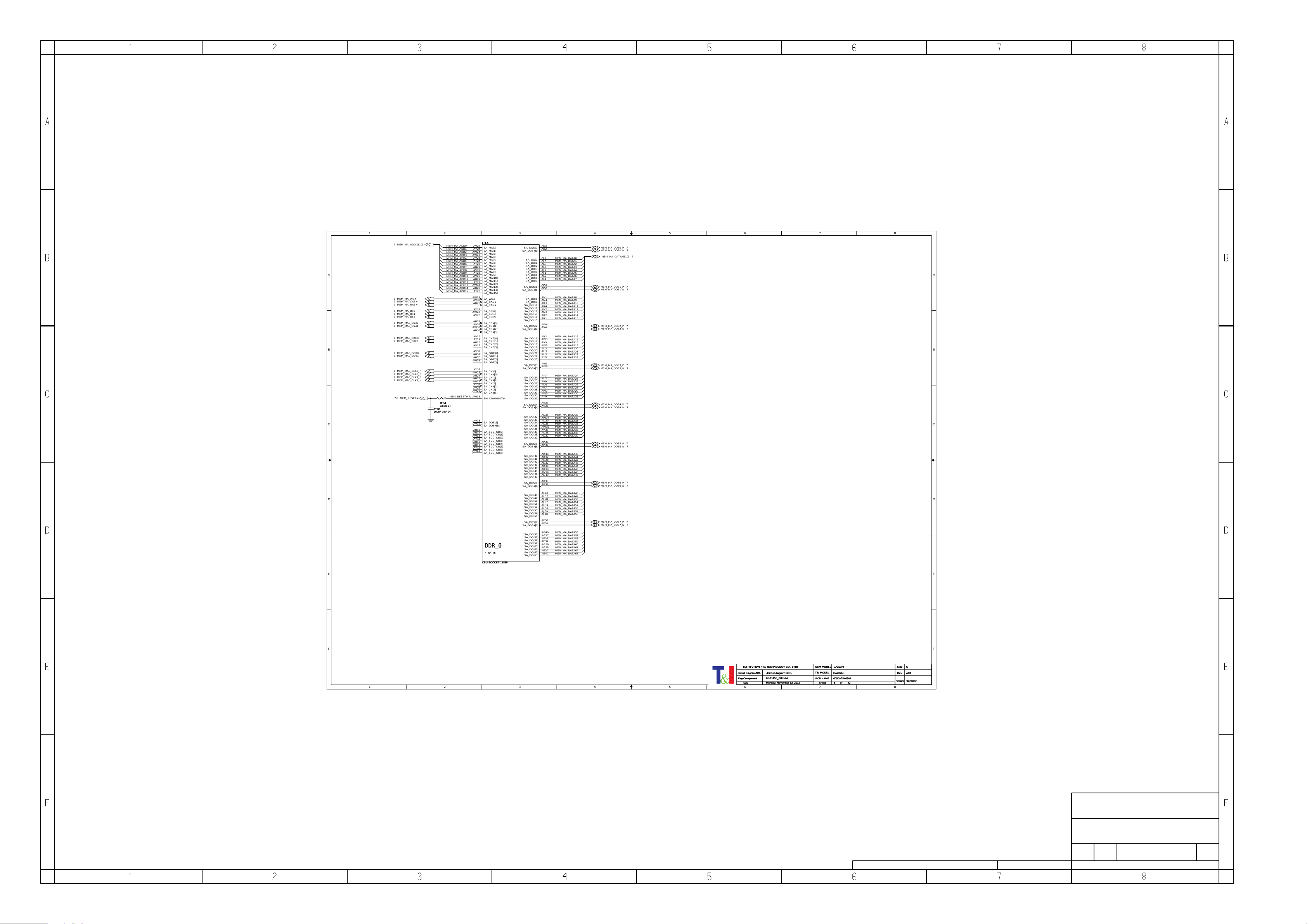

MEM_RESET#_R

MEM_MA_ADD13

MEM_MA_ADD9

MEM_MA_ADD5

MEM_MA_ADD2

MEM_MA_ADD10

MEM_MA_ADD6

MEM_MA_ADD3

MEM_MA_ADD14

MEM_MA_ADD0

MEM_MA_ADD11

MEM_MA_ADD7

MEM_MA_ADD15

MEM_MA_ADD12

MEM_MA_ADD4

MEM_MA_ADD1

MEM_MA_ADD8

MEM_MA_DATA0

MEM_MA_DATA5

MEM_MA_DATA2

MEM_MA_DATA3

MEM_MA_DATA6

MEM_MA_DATA7

MEM_MA_DATA1

MEM_MA_DATA4

MEM_MA_DATA8

MEM_MA_DATA13

MEM_MA_DATA10

MEM_MA_DATA11

MEM_MA_DATA14

MEM_MA_DATA15

MEM_MA_DATA9

MEM_MA_DATA12

MEM_MA_DATA16

MEM_MA_DATA21

MEM_MA_DATA18

MEM_MA_DATA19

MEM_MA_DATA22

MEM_MA_DATA23

MEM_MA_DATA17

MEM_MA_DATA20

MEM_MA_DATA24

MEM_MA_DATA29

MEM_MA_DATA26

MEM_MA_DATA27

MEM_MA_DATA30

MEM_MA_DATA31

MEM_MA_DATA25

MEM_MA_DATA28

MEM_MA_DATA32

MEM_MA_DATA37

MEM_MA_DATA34

MEM_MA_DATA35

MEM_MA_DATA38

MEM_MA_DATA39

MEM_MA_DATA33

MEM_MA_DATA36

MEM_MA_DATA40

MEM_MA_DATA45

MEM_MA_DATA42

MEM_MA_DATA43

MEM_MA_DATA46

MEM_MA_DATA47

MEM_MA_DATA41

MEM_MA_DATA44

MEM_MA_DATA48

MEM_MA_DATA53

MEM_MA_DATA50

MEM_MA_DATA51

MEM_MA_DATA54

MEM_MA_DATA55

MEM_MA_DATA49

MEM_MA_DATA52

MEM_MA_DATA56

MEM_MA_DATA61

MEM_MA_DATA58

MEM_MA_DATA59

MEM_MA_DATA62

MEM_MA_DATA63

MEM_MA_DATA57

MEM_MA_DATA60

MEM_MA_ADD[15..0]7

MEM_MA_DATA[63..0] 7

MEM_MA_DQS7_N 7

MEM_MA_DQS7_P 7

MEM_MA_DQS6_N 7

MEM_MA_DQS6_P 7

MEM_MA_DQS5_N 7

MEM_MA_DQS5_P 7

MEM_MA_DQS4_N 7

MEM_MA_DQS4_P 7

MEM_MA_DQS3_N 7

MEM_MA_DQS3_P 7

MEM_MA_DQS2_N 7

MEM_MA_DQS2_P 7

MEM_MA_DQS1_N 7

MEM_MA_DQS1_P 7

MEM_MA_DQS0_N 7

MEM_MA_DQS0_P 7

MEM_MA_WE#7

MEM_MA_CAS#7

MEM_MA_RAS#7

MEM_MA_BS07

MEM_MA_BS17

MEM_MA_BS27

MEM_RESET#7,8

MEM_MA0_CKE07

MEM_MA0_CKE17

MEM_MA0_ODT07

MEM_MA0_ODT17

MEM_MA0_CS#07

MEM_MA0_CS#17

MEM_MA0_CLK0_P7

MEM_MA0_CLK0_N7

MEM_MA0_CLK1_P7

MEM_MA0_CLK1_N7

OEM MODEL

Size

Rev

Date

Sheet

of

T&I MODEL

PCB NAME

remark

T&I (TPV-INVENTA TECHNOLOGY CO., LTD)

Key Component

Circuit diagram NO. CA202M AX1

CA203M C

542Monday, November 12, 2012

6050A2546301

<remark>

LGA1155_DIMM A

<Circuit diagram NO.>

OEM MODEL

Size

Rev

Date

Sheet

of

T&I MODEL

PCB NAME

remark

T&I (TPV-INVENTA TECHNOLOGY CO., LTD)

Key Component

Circuit diagram NO. CA202M AX1

CA203M C

542Monday, November 12, 2012

6050A2546301

<remark>

LGA1155_DIMM A

<Circuit diagram NO.>

OEM MODEL

Size

Rev

Date

Sheet

of

T&I MODEL

PCB NAME

remark

T&I (TPV-INVENTA TECHNOLOGY CO., LTD)

Key Component

Circuit diagram NO. CA202M AX1

CA203M C

542Monday, November 12, 2012

6050A2546301

<remark>

LGA1155_DIMM A

<Circuit diagram NO.>

DDR_0

1 OF 10

U1A

CPU-SOCKET-1155P

DDR_0

1 OF 10

U1A

CPU-SOCKET-1155P

SA_MA[0]

AV27

SA_MA[1]

AY24

SA_MA[2]

AW24

SA_MA[3]

AW23

SA_MA[4]

AV23

SA_MA[5]

AT24

SA_MA[6]

AT23

SA_MA[7]

AU22

SA_MA[8]

AV22

SA_MA[9]

AT22

SA_MA[10]

AV28

SA_MA[11]

AU21

SA_MA[12]

AT21

SA_MA[13]

AW32

SA_MA[14]

AU20

SA_MA[15]

AT20

SA_WE#

AW29

SA_CAS#

AV30

SA_RAS#

AU28

SA_BS[0]

AY29

SA_BS[1]

AW28

SA_BS[2]

AV20

SA_CS#[0]

AU29

SA_CS#[1]

AV32

SA_CS#[2]

AW30

SA_CS#[3]

AU33

SA_CKE[0]

AV19

SA_CKE[1]

AT19

SA_CKE[2]

AU18

SA_CKE[3]

AV18

SA_ODT[0]

AV31

SA_ODT[1]

AU32

SA_ODT[2]

AU30

SA_ODT[3]

AW33

SA_CK#[0]

AW25

SA_CK[1]

AU24

SA_CK#[1]

AU25

SA_CK[2]

AW27

SA_CK#[2]

AY27

SA_CK[3]

AV26

SA_CK#[3]

AW26

SA_CK[0]

AY25

SM_DRAMRST#

AW18

SA_DQS[8]

AV13

SA_DQS#[8]

AV12

SA_ECC_CB[0]

AU12

SA_ECC_CB[1]

AU14

SA_ECC_CB[2]

AW13

SA_ECC_CB[3]

AY13

SA_ECC_CB[4]

AU13

SA_ECC_CB[5]

AU11

SA_ECC_CB[6]

AY12

SA_ECC_CB[7]

AW12

SA_DQS[0]

AK3

SA_DQS#[0]

AK2

SA_DQ[0]

AJ3

SA_DQ[1]

AJ4

SA_DQ[2]

AL3

SA_DQ[3]

AL4

SA_DQ[4]

AJ2

SA_DQ[5]

AJ1

SA_DQ[6]

AL2

SA_DQ[7]

AL1

SA_DQS[1]

AP3

SA_DQS#[1]

AP2

SA_DQ[8]

AN1

SA_DQ[9]

AN4

SA_DQ[10]

AR3

SA_DQ[11]

AR4

SA_DQ[12]

AN2

SA_DQ[13]

AN3

SA_DQ[14]

AR2

SA_DQ[15]

AR1

SA_DQS[2]

AW4

SA_DQS#[2]

AV4

SA_DQ[16]

AV2

SA_DQ[17]

AW3

SA_DQ[18]

AV5

SA_DQ[19]

AW5

SA_DQ[20]

AU2

SA_DQ[21]

AU3

SA_DQ[22]

AU5

SA_DQ[23]

AY5

SA_DQS[3]

AV8

SA_DQS#[3]

AW8

SA_DQ[24]

AY7

SA_DQ[25]

AU7

SA_DQ[26]

AV9

SA_DQ[27]

AU9

SA_DQ[28]

AV7

SA_DQ[29]

AW7

SA_DQ[30]

AW9

SA_DQ[31]

AY9

SA_DQS[4]

AV37

SA_DQS#[4]

AV36

SA_DQ[32]

AU35

SA_DQ[33]

AW37

SA_DQ[34]

AU39

SA_DQ[35]

AU36

SA_DQ[36]

AW35

SA_DQ[37]

AY36

SA_DQ[38]

AU38

SA_DQ[39]

AU37

SA_DQS[5]

AP38

SA_DQS#[5]

AP39

SA_DQ[40]

AR40

SA_DQ[41]

AR37

SA_DQ[42]

AN38

SA_DQ[43]

AN37

SA_DQ[44]

AR39

SA_DQ[45]

AR38

SA_DQ[46]

AN39

SA_DQ[47]

AN40

SA_DQS[6]

AK38

SA_DQS#[6]

AK39

SA_DQ[48]

AL40

SA_DQ[49]

AL37

SA_DQ[50]

AJ38

SA_DQ[51]

AJ37

SA_DQ[52]

AL39

SA_DQ[53]

AL38

SA_DQ[54]

AJ39

SA_DQ[55]

AJ40

SA_DQS[7]

AF38

SA_DQS#[7]

AF39

SA_DQ[56]

AG40

SA_DQ[57]

AG37

SA_DQ[58]

AE38

SA_DQ[59]

AE37

SA_DQ[60]

AG39

SA_DQ[61]

AG38

SA_DQ[62]

AE39

SA_DQ[63]

AE40

R54

0.05R-04

R54

0.05R-04

C20

100nF 16V-04

C20

100nF 16V-04

Yang Danny

CA203 Mother Board

A3

CS

1310A2546301

A

42

5

INVENTEC

TITLE

SIZE CODE DOC. NUMBER REV

CHANGE by SHEET OF

Page 6

1

1

2

2

3

3

4

4

5

5

6

6

7

7

8

8

A A

B B

C C

D D

E E

F F

MEM_MB_DATA24

MEM_MB_DATA29

MEM_MB_DATA26

MEM_MB_DATA27

MEM_MB_DATA30

MEM_MB_DATA31

MEM_MB_DATA25

MEM_MB_DATA28

MEM_MB_DATA48

MEM_MB_DATA53

MEM_MB_DATA50

MEM_MB_DATA51

MEM_MB_DATA54

MEM_MB_DATA55

MEM_MB_DATA49

MEM_MB_DATA52

MEM_MB_DATA32

MEM_MB_DATA37

MEM_MB_DATA34

MEM_MB_DATA35

MEM_MB_DATA38

MEM_MB_DATA39

MEM_MB_DATA33

MEM_MB_DATA36

MEM_MB_DATA8

MEM_MB_DATA13

MEM_MB_DATA40

MEM_MB_DATA10

MEM_MB_DATA11

MEM_MB_DATA45

MEM_MB_DATA42

MEM_MB_DATA14

MEM_MB_DATA43

MEM_MB_DATA46

MEM_MB_DATA15

MEM_MB_DATA9

MEM_MB_DATA12

MEM_MB_DATA47

MEM_MB_DATA41

MEM_MB_DATA44

MEM_MB_DATA16

MEM_MB_DATA21

MEM_MB_DATA18

MEM_MB_DATA19

MEM_MB_DATA22

MEM_MB_DATA23

MEM_MB_DATA17

MEM_MB_DATA20

MEM_MB_DATA56

MEM_MB_DATA61

MEM_MB_DATA58

MEM_MB_DATA59

MEM_MB_DATA62

MEM_MB_DATA63

MEM_MB_DATA57

MEM_MB_DATA60

MEM_MB_DATA0

MEM_MB_DATA5

MEM_MB_DATA2

MEM_MB_DATA3

MEM_MB_DATA6

MEM_MB_DATA7

MEM_MB_DATA1

MEM_MB_DATA4

MEM_MB_ADD13

MEM_MB_ADD9

MEM_MB_ADD5

MEM_MB_ADD2

MEM_MB_ADD10

MEM_MB_ADD6

MEM_MB_ADD3

MEM_MB_ADD14

MEM_MB_ADD0

MEM_MB_ADD11

MEM_MB_ADD7

MEM_MB_ADD15

MEM_MB_ADD12

MEM_MB_ADD4

MEM_MB_ADD1

MEM_MB_ADD8

MEM_MB_BS08

MEM_MB0_CS#08

MEM_MB0_CS#18

MEM_MB0_ODT08

MEM_MB0_ODT18

MEM_MB0_CLK0_P8

MEM_MB0_CLK0_N8

MEM_MB0_CLK1_P8

MEM_MB0_CLK1_N8

MEM_MB0_CKE08

MEM_MB0_CKE18

MEM_MB_DATA[63..0] 8

MEM_MB_DQS1_N 8

MEM_MB_DQS1_P 8

MEM_MB_DQS4_N 8

MEM_MB_DQS4_P 8

MEM_MB_DQS7_N 8

MEM_MB_DQS7_P 8

MEM_MB_DQS0_N 8

MEM_MB_DQS0_P 8

MEM_MB_CAS#8

MEM_MB_RAS#8

MEM_MB_WE#8

MEM_MB_DQS3_N 8

MEM_MB_DQS3_P 8

MEM_MB_ADD[15..0]8

MEM_MB_DQS6_N 8

MEM_MB_DQS6_P 8

MEM_MB_DQS2_N 8

MEM_MB_DQS2_P 8

MEM_MB_DQS5_N 8

MEM_MB_DQS5_P 8

MEM_MB_BS18

MEM_MB_BS28

OEM MODEL

Size

Rev

Date

Sheet

of

T&I MODEL

PCB NAME

remark

T&I (TPV-INVENTA TECHNOLOGY CO., LTD)

Key Component

Circuit diagram NO. CA202M DVT_0.1

CA203M C

642Monday, November 12, 2012

6050A2546301

<remark>

LGA1155_DIMM B

<Circuit diagram NO.>

OEM MODEL

Size

Rev

Date

Sheet

of

T&I MODEL

PCB NAME

remark

T&I (TPV-INVENTA TECHNOLOGY CO., LTD)

Key Component

Circuit diagram NO. CA202M DVT_0.1

CA203M C

642Monday, November 12, 2012

6050A2546301

<remark>

LGA1155_DIMM B

<Circuit diagram NO.>

OEM MODEL

Size

Rev

Date

Sheet

of

T&I MODEL

PCB NAME

remark

T&I (TPV-INVENTA TECHNOLOGY CO., LTD)

Key Component

Circuit diagram NO. CA202M DVT_0.1

CA203M C

642Monday, November 12, 2012

6050A2546301

<remark>

LGA1155_DIMM B

<Circuit diagram NO.>

2 OF 10

DDR_1

U1B

CPU-SOCKET-1155P

2 OF 10

DDR_1

U1B

CPU-SOCKET-1155P

SB_MA[0]

AK24

SB_MA[1]

AM20

SB_MA[2]

AM19

SB_MA[3]

AK18

SB_MA[4]

AP19

SB_MA[5]

AP18

SB_MA[6]

AM18

SB_MA[7]

AL18

SB_MA[8]

AN18

SB_MA[9]

AY17

SB_MA[10]

AN23

SB_MA[11]

AU17

SB_MA[12]

AT18

SB_MA[13]

AR26

SB_MA[14]

AY16

SB_MA[15]

AV16

SB_BS[0]

AP23

SB_BS[1]

AM24

SB_BS[2]

AW17

SB_CS#[0]

AN25

SB_CS#[1]

AN26

SB_CS#[2]

AL25

SB_CS#[3]

AT26

SB_CKE[0]

AU16

SB_CKE[1]

AY15

SB_CKE[2]

AW15

SB_CKE[3]

AV15

SB_ODT[0]

AL26

SB_ODT[1]

AP26

SB_ODT[2]

AM26

SB_ODT[3]

AK26

SB_CK[0]

AL21

SB_CK#[0]

AL22

SB_CK[1]

AL20

SB_CK#[1]

AK20

SB_CK[2]

AL23

SB_CK#[2]

AM22

SB_CK[3]

AP21

SB_CK#[3]

AN21

SB_DQS[8]

AN16

SB_DQS#[8]

AN15

SB_ECC_CB[0]

AL16

SB_ECC_CB[1]

AM16

SB_ECC_CB[2]

AP16

SB_ECC_CB[3]

AR16

SB_ECC_CB[4]

AL15

SB_ECC_CB[5]

AM15

SB_ECC_CB[6]

AR15

SB_ECC_CB[7]

AP15

SB_DQS[0]

AH7

SB_DQS#[0]

AH6

SB_DQ[0]

AG7

SB_DQ[1]

AG8

SB_DQ[2]

AJ9

SB_DQ[3]

AJ8

SB_DQ[4]

AG5

SB_DQ[5]

AG6

SB_DQ[6]

AJ6

SB_DQ[7]

AJ7

SB_DQS[1]

AM8

SB_DQS#[1]

AL8

SB_DQ[8]

AL7

SB_DQ[9]

AM7

SB_DQ[10]

AM10

SB_DQ[11]

AL10

SB_DQ[12]

AL6

SB_DQ[13]

AM6

SB_DQ[14]

AL9

SB_DQ[15]

AM9

SB_DQS[2]

AR8

SB_DQS#[2]

AP8

SB_DQ[16]

AP7

SB_DQ[17]

AR7

SB_DQ[18]

AP10

SB_DQ[19]

AR10

SB_DQ[20]

AP6

SB_DQ[21]

AR6

SB_DQ[22]

AP9

SB_DQ[23]

AR9

SB_DQS[3]

AN13

SB_DQS#[3]

AN12

SB_DQ[24]

AM12

SB_DQ[25]

AM13

SB_DQ[26]

AR13

SB_DQ[27]

AP13

SB_DQ[28]

AL12

SB_DQ[29]

AL13

SB_DQ[30]

AR12

SB_DQ[31]

AP12

SB_DQS[4]

AN29

SB_DQ[32]

AR28

SB_DQ[33]

AR29

SB_DQ[34]

AL28

SB_DQ[35]

AL29

SB_DQ[36]

AP28

SB_DQ[37]

AP29

SB_DQ[38]

AM28

SB_DQ[39]

AM29

SB_DQS[5]

AP33

SB_DQS#[5]

AR33

SB_DQ[40]

AP32

SB_DQ[41]

AP31

SB_DQ[42]

AP35

SB_DQ[43]

AP34

SB_DQ[44]

AR32

SB_DQ[45]

AR31

SB_DQ[46]

AR35

SB_DQ[47]

AR34

SB_DQS[6]

AL33

SB_DQS#[6]

AM33

SB_DQ[48]

AM32

SB_DQ[49]

AM31

SB_DQ[50]

AL35

SB_DQ[51]

AL32

SB_DQ[52]

AM34

SB_DQ[53]

AL31

SB_DQ[54]

AM35

SB_DQ[55]

AL34

SB_DQS[7]

AG35

SB_DQS#[7]

AG34

SB_DQ[56]

AH35

SB_DQ[57]

AH34

SB_DQ[58]

AE34

SB_DQ[59]

AE35

SB_DQ[60]

AJ35

SB_DQ[61]

AJ34

SB_DQ[62]

AF33

SB_DQ[63]

AF35

SB_WE#

AR25

SB_CAS#

AK25

SB_RAS#

AP24

SB_DQS#[4]

AN28

Yang Danny

CA203 Mother Board

A3

CS

1310A2546301

A

42

6

INVENTEC

TITLE

SIZE CODE DOC. NUMBER REV

CHANGE by SHEET OF

Page 7

1

1

2

2

3

3

4

4

5

5

6

6

7

7

8

8

A A

B B

C C

D D

E E

F F

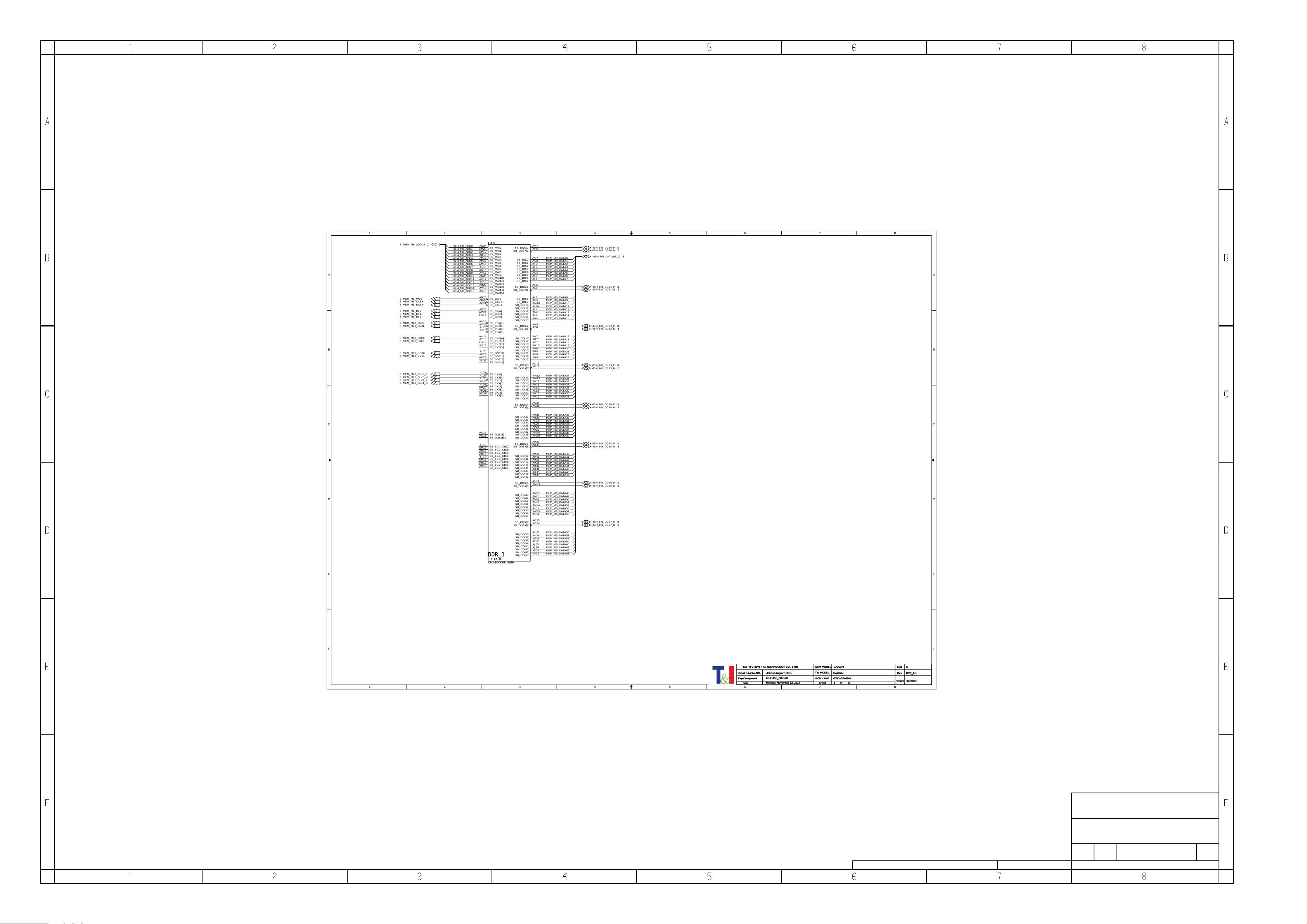

Channel A DIMM0 (5.2mm)

Address : 00

Close to Channel A DIMM0

Close to Channel A DIMM0

Modify 42

MEM_MA_DATA7

MEM_MA_DATA11

MEM_MA_DATA26

MEM_MA_DATA20

MEM_MA_ADD9

MEM_MA_ADD5

MEM_MA_DATA38

MEM_MA_DATA50

MEM_MA_DATA16

MEM_MA_ADD7

MEM_MA_DATA47

MEM_MA_DATA45

MEM_MA_DATA36

MEM_MA_ADD0

MEM_MA_DATA2

MEM_MA_DATA44

MEM_MA_DATA9

MEM_MA_DATA56

MEM_MA_DATA52

MEM_MA_DATA28

MEM_MA_DATA42

MEM_MA_DATA48

MEM_MA_ADD13

MEM_MA_DATA63

MEM_MA_ADD3

MEM_MA_DATA37

MEM_MA_DATA4

MEM_MA_DATA3

MEM_MA_DATA12

MEM_MA_DATA19

MEM_MA_ADD6

MEM_MA_DATA39

MEM_MA_DATA13

MEM_MA_DATA57

MEM_MA_DATA31

MEM_MA_DATA62

MEM_MA_ADD1

MEM_MA_DATA49

MEM_MA_DATA14

MEM_MA_DATA35

MEM_MA_DATA10

MEM_MA_DATA32

MEM_MA_DATA51

MEM_MA_ADD15

MEM_MA_DATA8

MEM_MA_DATA22

MEM_MA_DATA59

MEM_MA_DATA5

MEM_MA_DATA18

MEM_MA_DATA61

MEM_MA_DATA30

MEM_MA_DATA21

MEM_MA_DATA15

MEM_MA_DATA58

MEM_MA_DATA54

MEM_MA_DATA46

MEM_MA_ADD2

MEM_MA_DATA43

MEM_MA_DATA33

MEM_MA_DATA55

MEM_MA_DATA6

MEM_MA_DATA40

MEM_MA_DATA27

MEM_MA_ADD12

MEM_MA_DATA60

MEM_MA_DATA34

MEM_MA_DATA24

MEM_MA_DATA1

MEM_MA_DATA53

MEM_MA_DATA29

MEM_MA_DATA0

MEM_MA_ADD10

MEM_MA_ADD14

MEM_MA_ADD11

MEM_MA_DATA17

MEM_MA_ADD8

MEM_MA_DATA41

MEM_MA_DATA25

MEM_MA_DATA23

MEM_MA_ADD4

DIMM_A_SA0

DIMM_A_SA1

DIMM_A_SA0

DIMM_A_SA1

+0.75VTT

+1.5VDIMM

DIMM_DQ_VREF_A

DIMM_CA_VREF_A

+V3.3S

DIMM_DQ_VREF_A

+1.5VDIMM

+1.5VDIMM

DIMM_CA_VREF_A

+1.5VDIMM

+V3.3S+0.75VTT

+V3.3S

+V3.3S

MEM_MA_ADD[15..0]5

SMB_CLK_PCH8,16,25,30

SMB_DATA_PCH8,16,25,30

MEM_MA_CAS#5

MEM_MA_RAS#5

MEM_MA_WE#5

MEM_MA_DQS0_P5

MEM_MA_DQS1_P5

MEM_MA_DQS2_P5

MEM_MA_DQS3_P5

MEM_MA_DQS4_P5

MEM_MA_DQS5_P5

MEM_MA_DQS6_P5

MEM_MA_DQS7_P5

MEM_MA_DQS0_N5

MEM_MA_DQS1_N5

MEM_MA_DQS2_N5

MEM_MA_DQS3_N5

MEM_MA_DQS4_N5

MEM_MA_DQS5_N5

MEM_MA_DQS6_N5

MEM_MA_DQS7_N5

MEM_MA_DATA[63..0] 5

MEM_RESET#5,8

MEM_MA_BS05

MEM_MA_BS15

MEM_MA_BS25

VREF_DQA9

MEM_MA0_CS#05

MEM_MA0_CS#15

MEM_MA0_CKE05

MEM_MA0_CKE15

MEM_MA0_CLK0_P5

MEM_MA0_CLK1_N5

MEM_MA0_CLK1_P5

MEM_MA0_CLK0_N5

MEM_MA0_ODT05

MEM_MA0_ODT15

OEM MODEL

Size

Rev

Date

Sheet

of

T&I MODEL

PCB NAME

remark

T&I (TPV-INVENTA TECHNOLOGY CO., LTD)

Key Component

Circuit diagram NO. CA202M AX1

CA203M C

742Monday, November 12, 2012

6050A2546301

<remark>

DDR3 STANDARD MA-CH0 5.2mm

<Circuit diagram NO.>

OEM MODEL

Size

Rev

Date

Sheet

of

T&I MODEL

PCB NAME

remark

T&I (TPV-INVENTA TECHNOLOGY CO., LTD)

Key Component

Circuit diagram NO. CA202M AX1

CA203M C

742Monday, November 12, 2012

6050A2546301

<remark>

DDR3 STANDARD MA-CH0 5.2mm

<Circuit diagram NO.>

OEM MODEL

Size

Rev

Date

Sheet

of

T&I MODEL

PCB NAME

remark

T&I (TPV-INVENTA TECHNOLOGY CO., LTD)

Key Component

Circuit diagram NO. CA202M AX1

CA203M C

742Monday, November 12, 2012

6050A2546301

<remark>

DDR3 STANDARD MA-CH0 5.2mm

<Circuit diagram NO.>

CN1B

SOCKET240P-5.2-STD

CN1B

SOCKET240P-5.2-STD

VDD1

75

VDD2

76

VDD3

81

VDD4

82

VDD5

87

VDD6

88

VDD7

93

VDD8

94

VDD9

99

VDD10

100

VDD11

105

VDD12

106

VDDSPD

199

NC1

77

NC2

122

VTT1

203

VTT2

204

VSS31

138

VSS32

139

VSS33

144

VSS34

145

VSS35

150

VSS36

151

VSS37

155

VSS38

156

VSS39

161

VSS40

162

VSS41

167

VSS42

168

VSS43

172

VSS44

173

VSS45

178

VSS46

179

VSS47

184

VSS48

185

VSS49

189

VSS50

190

VSS51

195

VSS52

196

GND-S1

205

GND-S2

206

VDD13

111

VDD14

112

VDD15

117

VDD16

118

VDD17

123

VDD18

124

VREFDQ

1

VREFCA

126

VSS1

2

VSS2

3

VSS3

8

VSS4

9

VSS5

13

VSS6

14

VSS7

19

VSS8

20

VSS9

25

VSS10

26

VSS11

31

VSS12

32

VSS13

37

VSS14

38

VSS15

43

VSS16

44

VSS17

48

VSS18

49

VSS19

54

VSS20

55

VSS21

60

VSS22

61

VSS23

65

VSS24

66

VSS25

71

VSS26

72

VSS27

127

VSS28

128

VSS29

133

VSS30

134

EVENT#

198

RESET#

30

NCTEST

125

NC3

207

NC4

208

C77

100nF 16V-04

C77

100nF 16V-04

C87

100nF 16V-04

C87

100nF 16V-04

R61

0.05R-04

R61

0.05R-04

C70

100nF 16V-04

C70

100nF 16V-04

R56

1K 1%-04

R56

1K 1%-04

R62

1K 1%-04

R62

1K 1%-04

C92

180pF 50V-04

C92

180pF 50V-04

C91

100nF 16V-04

C91

100nF 16V-04

C88

100nF 16V-04

C88

100nF 16V-04

R60

1K 1%-04

R60

1K 1%-04

C85

10uF 6.3V-06

C85

10uF 6.3V-06

R58

1K 1%-04

R58

1K 1%-04

CN1A

SOCKET240P-5.2-STD

CN1A

SOCKET240P-5.2-STD

A0

98

A1

97

A2

96

A3

95

A4

92

A5

91

A6

90

A7

86

A8

89

A9

85

A10/AP

107

A11

84

A12/BC#

83

A13

119

A14

80

A15

78

BA0

109

BA1

108

S0#

114

CK0

101

CK0#

103

CK1

102

CK1#

104

CKE0

73

CKE1

74

CAS#

115

RAS#

110

WE#

113

SA0

197

SA1

201

SCL

202

SDA

200

ODT0

116

ODT1

120

DM0

11

DM1

28

DM2

46

DM3

63

DM4

136

DM5

153

DM6

170

DM7

187

DQS0

12

DQS1

29

DQS2

47

DQS3

64

DQS4

137

DQS5

154

DQS6

171

DQS7

188

DQS0#

10

DQS1#

27

DQS2#

45

DQS3#

62

DQS4#

135

DQS5#

152

DQS6#

169

DQS7#

186

DQ0

5

DQ1

7

DQ2

15

DQ3

17

DQ4

4

DQ5

6

DQ6

16

DQ7

18

DQ8

21

DQ9

23

DQ10

33

DQ11

35

DQ12

22

DQ13

24

DQ14

34

DQ15

36

DQ16

39

DQ17

41

DQ18

51

DQ19

53

DQ20

40

DQ21

42

DQ22

50

DQ23

52

DQ24

57

DQ25

59

DQ26

67

DQ27

69

DQ28

56

DQ29

58

DQ30

68

DQ31

70

DQ32

129

DQ33

131

DQ34

141

DQ35

143

DQ36

130

DQ37

132

DQ38

140

DQ39

142

DQ40

147

DQ41

149

DQ42

157

DQ43

159

DQ44

146

DQ45

148

DQ46

158

DQ47

160

DQ48

163

DQ49

165

DQ50

175

DQ51

177

DQ52

164

DQ53

166

DQ54

174

DQ55

176

DQ56

181

DQ57

183

DQ58

191

DQ59

193

DQ60

180

DQ61

182

DQ62

192

DQ63

194

BA2

79

S1#

121

C82

10uF 6.3V-06

C82

10uF 6.3V-06

C73

100nF 16V-04

C73

100nF 16V-04

C83

10uF 6.3V-06

C83

10uF 6.3V-06

C78

100nF 16V-04

C78

100nF 16V-04

C84

10uF 6.3V-06

C84

10uF 6.3V-06

C89

100nF 16V-04

C89

100nF 16V-04

C79

180pF 50V-04

C79

180pF 50V-04

C86

10uF 6.3V-06

C86

10uF 6.3V-06

C71

100nF 16V-04

C71

100nF 16V-04

C74

100nF 16V-04

C74

100nF 16V-04

R57

0.05R-04

R57

0.05R-04

R211

0.05R-04

R211

0.05R-04

C76

4.7uF 10V-06

C76

4.7uF 10V-06

C80

100nF 16V-04

C80

100nF 16V-04

R59

0.05R-04

R59

0.05R-04

C81

10pF 50V-04-OTS

C81

10pF 50V-04-OTS

R201

0.05R-04

R201

0.05R-04

R389

NC/0.05R-04

R389

NC/0.05R-04

C90

100nF 16V-04

C90

100nF 16V-04

R388

NC/0.05R-04

R388

NC/0.05R-04

C72

100nF 16V-04

C72

100nF 16V-04

C75

100nF 16V-04

C75

100nF 16V-04

Yang Danny

CA203 Mother Board

A3

CS

1310A2546301

A

42

7

INVENTEC

TITLE

SIZE CODE DOC. NUMBER REV

CHANGE by SHEET OF

Page 8

1

1

2

2

3

3

4

4

5

5

6

6

7

7

8

8

A A

B B

C C

D D

E E

F F

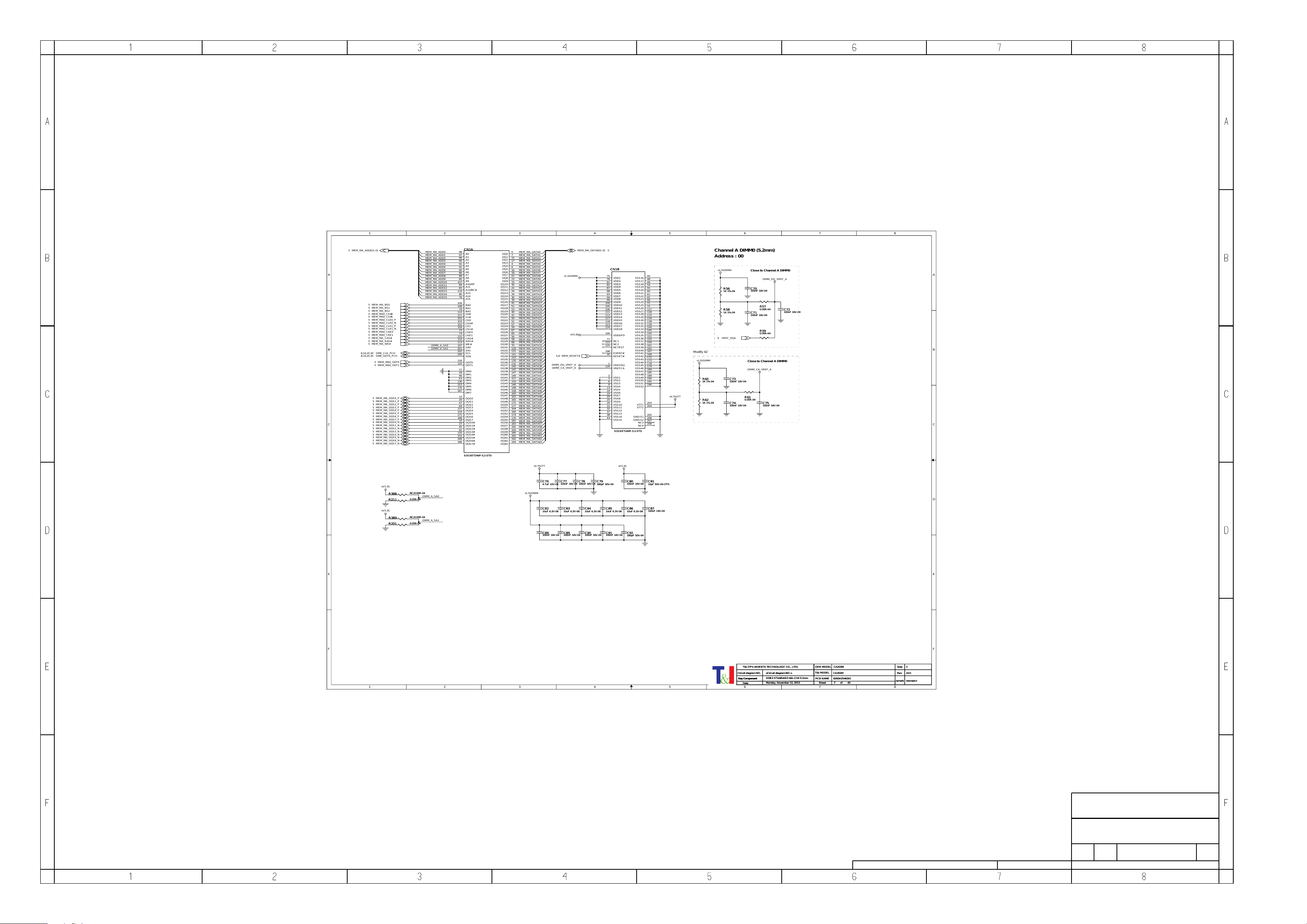

Close to Channel B DIMM0

Channel B DIMM0 (5.2mm)

Address : 10

Close to Channel B DIMM0

Modify 42

MEM_MB_ADD9

MEM_MB_ADD5

MEM_MB_ADD7

MEM_MB_ADD0

MEM_MB_ADD13

MEM_MB_ADD3

MEM_MB_ADD6

MEM_MB_ADD1

MEM_MB_ADD15

MEM_MB_ADD2

MEM_MB_ADD12

MEM_MB_ADD10

MEM_MB_ADD14

MEM_MB_ADD11

MEM_MB_ADD8

MEM_MB_ADD4

MEM_MB_DATA26

MEM_MB_DATA27

MEM_MB_DATA29

MEM_MB_DATA28

MEM_MB_DATA31

MEM_MB_DATA32

MEM_MB_DATA30

MEM_MB_DATA33

MEM_MB_DATA38

MEM_MB_DATA36

MEM_MB_DATA37

MEM_MB_DATA39

MEM_MB_DATA35

MEM_MB_DATA34

MEM_MB_DATA44

MEM_MB_DATA42

MEM_MB_DATA43

MEM_MB_DATA40

MEM_MB_DATA41

MEM_MB_DATA47

MEM_MB_DATA45

MEM_MB_DATA48

MEM_MB_DATA49

MEM_MB_DATA46

MEM_MB_DATA50

MEM_MB_DATA52

MEM_MB_DATA51

MEM_MB_DATA54

MEM_MB_DATA55

MEM_MB_DATA53

MEM_MB_DATA56

MEM_MB_DATA57

MEM_MB_DATA59

MEM_MB_DATA58

MEM_MB_DATA60

MEM_MB_DATA63

MEM_MB_DATA61

MEM_MB_DATA1

MEM_MB_DATA0

MEM_MB_DATA7

MEM_MB_DATA2

MEM_MB_DATA4

MEM_MB_DATA3

MEM_MB_DATA8

MEM_MB_DATA6

MEM_MB_DATA11

MEM_MB_DATA9

MEM_MB_DATA14

MEM_MB_DATA10

MEM_MB_DATA5

MEM_MB_DATA16

MEM_MB_DATA12

MEM_MB_DATA13

MEM_MB_DATA15

MEM_MB_DATA17

MEM_MB_DATA20

MEM_MB_DATA19

MEM_MB_DATA22

MEM_MB_DATA18

MEM_MB_DATA21

MEM_MB_DATA24

MEM_MB_DATA62

MEM_MB_DATA25

MEM_MB_DATA23

DIMM_B_SA0

DIMM_B_SA1

DIMM_B_SA0

DIMM_B_SA1

+0.75VTT

+1.5VDIMM

+V3.3S

DIMM_DQ_VREF_B

DIMM_CA_VREF_B

+1.5VDIMM

DIMM_CA_VREF_B

+1.5VDIMM

DIMM_DQ_VREF_B

+1.5VDIMM

+V3.3S+0.75VTT

+V3.3S

+V3.3S

MEM_MB_ADD[15..0]6

MEM_MB_CAS#6

MEM_MB_RAS#6

MEM_MB_WE#6

MEM_MB_DQS0_P6

MEM_MB_DQS1_P6

MEM_MB_DQS2_P6

MEM_MB_DQS3_P6

MEM_MB_DQS4_P6

MEM_MB_DQS5_P6

MEM_MB_DQS6_P6

MEM_MB_DQS7_P6

MEM_MB_DQS0_N6

MEM_MB_DQS1_N6

MEM_MB_DQS2_N6

MEM_MB_DQS3_N6

MEM_MB_DQS4_N6

MEM_MB_DQS5_N6

MEM_MB_DQS6_N6

MEM_MB_DQS7_N6

MEM_MB_DATA[63..0] 6

MEM_MB_BS06

MEM_MB_BS16

MEM_MB_BS26

MEM_RESET#5,7

SMB_CLK_PCH7,16,25,30

SMB_DATA_PCH7,16,25,30

VREF_DQB9

MEM_MB0_CLK0_N6

MEM_MB0_CS#06

MEM_MB0_CS#16

MEM_MB0_CLK0_P6

MEM_MB0_CLK1_N6

MEM_MB0_CKE06

MEM_MB0_CKE16

MEM_MB0_CLK1_P6

MEM_MB0_ODT06

MEM_MB0_ODT16

OEM MODEL

Size

Rev

Date

Sheet

of

T&I MODEL

PCB NAME

remark

T&I (TPV-INVENTA TECHNOLOGY CO., LTD)

Key Component

Circuit diagram NO. CA202M DVT_0.1

CA203M C

842Monday, November 12, 2012

6050A2546301

<remark>

DDR3 STANDARD MB-CH0 9.2mm

<Circuit diagram NO.>

OEM MODEL

Size

Rev

Date

Sheet

of

T&I MODEL

PCB NAME

remark

T&I (TPV-INVENTA TECHNOLOGY CO., LTD)

Key Component

Circuit diagram NO. CA202M DVT_0.1

CA203M C

842Monday, November 12, 2012

6050A2546301

<remark>

DDR3 STANDARD MB-CH0 9.2mm

<Circuit diagram NO.>

OEM MODEL

Size

Rev

Date

Sheet

of

T&I MODEL

PCB NAME

remark

T&I (TPV-INVENTA TECHNOLOGY CO., LTD)

Key Component

Circuit diagram NO. CA202M DVT_0.1

CA203M C

842Monday, November 12, 2012

6050A2546301

<remark>

DDR3 STANDARD MB-CH0 9.2mm

<Circuit diagram NO.>

C107

10uF 6.3V-06

C107

10uF 6.3V-06

R391

NC/0.05R-04

R391

NC/0.05R-04

C110

100nF 16V-04

C110

100nF 16V-04

R64

0.05R-04

R64

0.05R-04

R390

NC/0.05R-04

R390

NC/0.05R-04

C94

100nF 16V-04

C94

100nF 16V-04

C114

100nF 16V-04

C114

100nF 16V-04

C97

100nF 16V-04

C97

100nF 16V-04

C111

100nF 16V-04

C111

100nF 16V-04

CN2B

SOCKET240P-9.2-STD

CN2B

SOCKET240P-9.2-STD

VDD1

75

VDD2

76

VDD3

81

VDD4

82

VDD5

87

VDD6

88

VDD7

93

VDD8

94

VDD9

99

VDD10

100

VDD11

105

VDD12

106

VDDSPD

199

NC1

77

NC2

122

VTT1

203

VTT2

204

VSS31

138

VSS32

139

VSS33

144

VSS34

145

VSS35

150

VSS36

151

VSS37

155

VSS38

156

VSS39

161

VSS40

162

VSS41

167

VSS42

168

VSS43

172

VSS44

173

VSS45

178

VSS46

179

VSS47

184

VSS48

185

VSS49

189

VSS50

190

VSS51

195

VSS52

196

GND-S1

205

GND-S2

206

VDD13

111

VDD14

112

VDD15

117

VDD16

118

VDD17

123

VDD18

124

VREFDQ

1

VREFCA

126

VSS1

2

VSS2

3

VSS3

8

VSS4

9

VSS5

13

VSS6

14

VSS7

19

VSS8

20

VSS9

25

VSS10

26

VSS11

31

VSS12

32

VSS13

37

VSS14

38

VSS15

43

VSS16

44

VSS17

48

VSS18

49

VSS19

54

VSS20

55

VSS21

60

VSS22

61

VSS23

65

VSS24

66

VSS25

71

VSS26

72

VSS27

127

VSS28

128

VSS29

133

VSS30

134

EVENT#

198

RESET#

30

NCTEST

125

NC3

207

NC4

208

R66

0.05R-04

R66

0.05R-04

R187

0.05R-04

R187

0.05R-04

C99

4.7uF 10V-06

C99

4.7uF 10V-06

R135

0.05R-04

R135

0.05R-04

C113

100nF 16V-04

C113

100nF 16V-04

R67

1K 1%-04

R67

1K 1%-04

CN2A

SOCKET240P-9.2-STD

CN2A

SOCKET240P-9.2-STD

A0

98

A1

97

A2

96

A3

95

A4

92

A5

91

A6

90

A7

86

A8

89

A9

85

A10/AP

107

A11

84

A12/BC#

83

A13

119

A14

80

A15

78

BA0

109

BA1

108

S0#

114

CK0

101

CK0#

103

CK1

102

CK1#

104

CKE0

73

CKE1

74

CAS#

115

RAS#

110

WE#

113

SA0

197

SA1

201

SCL

202

SDA

200

ODT0

116

ODT1

120

DM0

11

DM1

28

DM2

46

DM3

63

DM4

136

DM5

153

DM6

170

DM7

187

DQS0

12

DQS1

29

DQS2

47

DQS3

64

DQS4

137

DQS5

154

DQS6

171

DQS7

188

DQS0#

10

DQS1#

27

DQS2#

45

DQS3#

62

DQS4#

135

DQS5#

152

DQS6#

169

DQS7#

186

DQ0

5

DQ1

7

DQ2

15

DQ3

17

DQ4

4

DQ5

6

DQ6

16

DQ7

18

DQ8

21

DQ9

23

DQ10

33

DQ11

35

DQ12

22

DQ13

24

DQ14

34

DQ15

36

DQ16

39

DQ17

41

DQ18

51

DQ19

53

DQ20

40

DQ21

42

DQ22

50

DQ23

52

DQ24

57

DQ25

59

DQ26

67

DQ27

69

DQ28

56

DQ29

58

DQ30

68

DQ31

70

DQ32

129

DQ33

131

DQ34

141

DQ35

143

DQ36

130

DQ37

132

DQ38

140

DQ39

142

DQ40

147

DQ41

149

DQ42

157

DQ43

159

DQ44

146

DQ45

148

DQ46

158

DQ47

160

DQ48

163

DQ49

165

DQ50

175

DQ51

177

DQ52

164

DQ53

166

DQ54

174

DQ55

176

DQ56

181

DQ57

183

DQ58

191

DQ59

193

DQ60

180

DQ61

182

DQ62

192

DQ63

194

BA2

79

S1#

121

C102

180pF 50V-04

C102

180pF 50V-04

C100

100nF 16V-04

C100

100nF 16V-04

R69

1K 1%-04

R69

1K 1%-04

R68

0.05R-04

R68

0.05R-04

R63

1K 1%-04

R63

1K 1%-04

C103

100nF 16V-04

C103

100nF 16V-04

C98

100nF 16V-04

C98

100nF 16V-04

C108

10uF 6.3V-06

C108

10uF 6.3V-06

C105

10uF 6.3V-06

C105

10uF 6.3V-06

R65

1K 1%-04

R65

1K 1%-04

C112

100nF 16V-04

C112

100nF 16V-04

C115

180pF 50V-04

C115

180pF 50V-04

C101

100nF 16V-04

C101

100nF 16V-04

C109

10uF 6.3V-06

C109

10uF 6.3V-06

C104

10pF 50V-04-OTS

C104

10pF 50V-04-OTS

C95

100nF 16V-04

C95

100nF 16V-04

C96

100nF 16V-04

C96

100nF 16V-04

C106

10uF 6.3V-06

C106

10uF 6.3V-06

C93

100nF 16V-04

C93

100nF 16V-04

Yang Danny

CA203 Mother Board

A3

CS

1310A2546301

A

42

8

INVENTEC

TITLE

SIZE CODE DOC. NUMBER REV

CHANGE by SHEET OF

Page 9

1

1

2

2

3

3

4

4

5

5

6

6

7

7

8

8

A A

B B

C C

D D

E E

F F

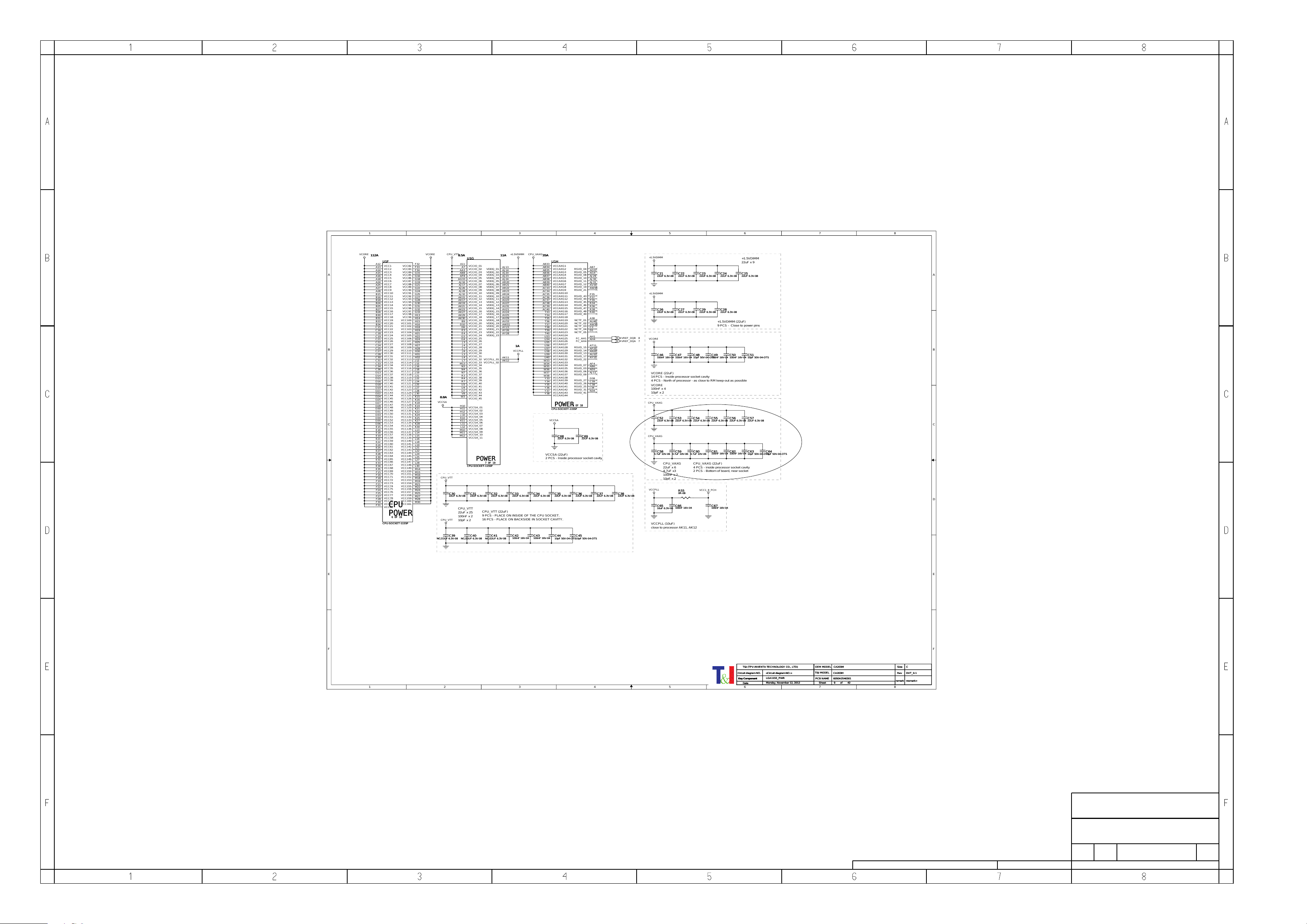

112A 35A8.5A

8.8A

1A

11A

CPU_VTT

22uF x 25

100nF x 2

10pF x 2

CPU_VTT (22uF)

9 PCS - PLACE ON INSIDE OF THE CPU SOCKET.

16 PCS - PLACE ON BACKSIDE IN SOCKET CAVITY.

+1.5VDIMM

22uF x 9

+1.5VDIMM (22uF)

9 PCS - Close to power pins

VCORE

100nF x 4

10pF x 2

VCORE (22uF)

14 PCS - Inside processor socket cavity

4 PCS - North of processor - as close to RM keep-out as possible

VCCPLL (10uF)

close to processor AK11, AK12

VCCSA (22uF)

2 PCS - Inside processor socket cavity

CPU_VAXG

22uF x 6

4.7uF x3

100nF x 2

10pF x 2

CPU_VAXG (22uF)

4 PCS - inside processor socket cavity

2 PCS - Bottom of board, near socket

+1.5VDIMM

VCCPLL

CPU_VTTVCOREVCORE CPU_VAXG

VCCSA

CPU_VTT

CPU_VTT

+1.5VDIMM

+1.5VDIMM

VCORE

VCCPLL

VCC1_8_PCH

VCCSA

CPU_VAXG

CPU_VAXG

VREF_DQB 8

VREF_DQA 7

OEM MODEL

Size

Rev

Date

Sheet

of

T&I MODEL

PCB NAME

remark

T&I (TPV-INVENTA TECHNOLOGY CO., LTD)

Key Component

Circuit diagram NO. CA203M DVT_0.1

CA203M C

942Monday, November 12, 2012

6050A2546301

<remark>

LGA1155_PWR

<Circuit diagram NO.>

OEM MODEL

Size

Rev

Date

Sheet

of

T&I MODEL

PCB NAME

remark

T&I (TPV-INVENTA TECHNOLOGY CO., LTD)

Key Component

Circuit diagram NO. CA203M DVT_0.1

CA203M C

942Monday, November 12, 2012

6050A2546301

<remark>

LGA1155_PWR

<Circuit diagram NO.>

OEM MODEL

Size

Rev

Date

Sheet

of

T&I MODEL

PCB NAME

remark

T&I (TPV-INVENTA TECHNOLOGY CO., LTD)

Key Component

Circuit diagram NO. CA203M DVT_0.1

CA203M C

942Monday, November 12, 2012

6050A2546301

<remark>

LGA1155_PWR

<Circuit diagram NO.>

C54

22UF 6.3V-08

C54

22UF 6.3V-08

C27

22UF 6.3V-08

C27

22UF 6.3V-08

C67

100nF 16V-04

C67

100nF 16V-04

POWER

7 OF 10

U1G

CPU-SOCKET-1155P

POWER

7 OF 10

U1G

CPU-SOCKET-1155P

VCCIO_01

A11

VCCIO_02

A7

VCCIO_03

AA3

VCCIO_04

AB8

VCCIO_05

AF8

VCCIO_06

AG33

VCCIO_07

AJ16

VCCIO_08

AJ17

VCCIO_09

AJ26

VCCIO_10

AJ28

VCCIO_11

AJ32

VCCIO_12

AK15

VCCIO_13

AK17

VCCIO_14

AK19

VCCIO_15

AK21

VCCIO_16

AK23

VCCIO_17

AK27

VCCIO_18

AK29

VCCIO_19

AK30

VCCIO_20

B9

VCCIO_21

D10

VCCIO_22

D6

VCCIO_23

E3

VCCIO_24

E4

VCCIO_25

G3

VCCIO_26

G4

VCCIO_27

J3

VCCIO_28

J4

VCCIO_29

J7

VCCIO_30

J8

VCCIO_31

L3

VCCIO_32

L4

VCCIO_33

L7

VCCIO_34

M13

VCCIO_35

N3

VCCIO_36

N4

VCCIO_37

N7

VCCIO_38

R3

VCCIO_39

R4

VCCIO_40

R7

VCCIO_41

U3

VCCIO_42

U4

VCCIO_43

U7

VCCIO_44

V8

VCCIO_45

W3

VCCSA_01

H10

VCCSA_02

H11

VCCSA_03

H12

VCCSA_04

J10

VCCSA_05

K10

VCCSA_06

K11

VCCSA_07

L11

VCCSA_08

L12

VCCSA_09

M10

VCCSA_10

M11

VCCSA_11

M12

VCCPLL_01

AK11

VDDQ_01

AJ13

VDDQ_02

AJ14

VDDQ_03

AJ20

VDDQ_04

AJ23

VDDQ_05

AJ24

VDDQ_06

AR20

VDDQ_07

AR21

VDDQ_08

AR22

VDDQ_09

AR23

VDDQ_10

AR24

VDDQ_11

AU19

VDDQ_12

AU23

VDDQ_13

AU27

VDDQ_14

AU31

VDDQ_15

AV21

VDDQ_16

AV24

VDDQ_17

AV25

VDDQ_18

AV29

VDDQ_19

AV33

VDDQ_20

AW31

VDDQ_21

AY23

VCCPLL_02

AK12

VDDQ_22

AY26

VDDQ_23

AY28

C48

10pF 50V-04-OTS

C48

10pF 50V-04-OTS

C41

NC/22UF 6.3V-08

C41

NC/22UF 6.3V-08

C32

22UF 6.3V-08

C32

22UF 6.3V-08

C68

22UF 6.3V-08

C68

22UF 6.3V-08

C63

10pF 50V-04-OTS

C63

10pF 50V-04-OTS

C50

100nF 16V-04

C50

100nF 16V-04

C37

22UF 6.3V-08

C37

22UF 6.3V-08

C66

100nF 16V-04

C66

100nF 16V-04

C69

22UF 6.3V-08

C69

22UF 6.3V-08

C21

22UF 6.3V-08

C21

22UF 6.3V-08

C31

22UF 6.3V-08

C31

22UF 6.3V-08

C22

22UF 6.3V-08

C22

22UF 6.3V-08

8 OF 10

POWER

U1H

CPU-SOCKET-1155P

8 OF 10

POWER

U1H

CPU-SOCKET-1155P

VCCAXG1

AB33

VCCAXG2

AB34

VCCAXG3

AB35

VCCAXG4

AB36

VCCAXG5

AB37

VCCAXG6

AB38

VCCAXG7

AB39

VCCAXG8

AB40

VCCAXG9

AC33

VCCAXG10

AC34

VCCAXG11

AC35

VCCAXG12

AC36

VCCAXG13

AC37

VCCAXG14

AC38

VCCAXG15

AC39

VCCAXG16

AC40

VCCAXG17

T33

VCCAXG18

T34

VCCAXG19

T35

VCCAXG20

T36

VCCAXG21

T37

VCCAXG22

T38

VCCAXG23

T39

VCCAXG24

T40

VCCAXG25

U33

VCCAXG26

U34

VCCAXG27

U35

VCCAXG28

U36

VCCAXG29

U37

VCCAXG30

U38

VCCAXG31

U39

VCCAXG32

U40

VCCAXG33

W33

VCCAXG34

W34

VCCAXG35

W35

VCCAXG36

W36

VCCAXG37

W37

VCCAXG38

W38

VCCAXG39

Y33

VCCAXG40

Y34

VCCAXG41

Y35

VCCAXG42

Y36

VCCAXG43

Y37

VCCAXG44

Y38

RSVD_04

AB7

RSVD_05

AD37

RSVD_08

AG4

RSVD_10

AJ29

RSVD_11

AJ30

RSVD_12

AJ31

RSVD_19

AV34

RSVD_21

AW34

RSVD_43

P35

RSVD_44

P37

RSVD_45

P39

RSVD_46

R34

RSVD_47

R36

RSVD_48

R38

RSVD_49

R40

NCTF_01

A38

NCTF_02

AU40

NCTF_03

AW38

NCTF_04

C2

NCTF_05

D1

FC_AH1

AH1

FC_AH4

AH4

RSVD_15

AT11

RSVD_14

AP20

RSVD_13

AN20

RSVD_17

AU10

RSVD_22

AY10

RSVD_07

AF4

RSVD_03

AB6

RSVD_06

AE6

RSVD_09

AJ11

RSVD_27

D38

RSVD_26

C39

RSVD_25

C38

RSVD_31

J34

RSVD_41

N34

C44

10pF 50V-04-OTS

C44

10pF 50V-04-OTS

C38

22UF 6.3V-08

C38

22UF 6.3V-08

C47

100nF 16V-04

C47

100nF 16V-04

C61

100nF 16V-04

C61

100nF 16V-04

C58

4.7uF 10V-06

C58

4.7uF 10V-06

CPU

POWER

6 OF 10

U1F

CPU-SOCKET-1155P

CPU

POWER

6 OF 10

U1F

CPU-SOCKET-1155P

VCC1

A12

VCC2

A13

VCC3

A14

VCC4

A15

VCC5

A16

VCC6

A18

VCC7

A24

VCC8

A25

VCC9

A27

VCC10

A28

VCC11

B15

VCC12

B16

VCC13

B18

VCC14

B24

VCC15

B25

VCC16

B27

VCC17

B28

VCC18

B30

VCC19

B31

VCC20

B33

VCC21

B34

VCC22

C15

VCC23

C16

VCC24

C18

VCC25

C19

VCC26

C21

VCC27

C22

VCC28

C24

VCC29

C25

VCC30

C27

VCC31

C28

VCC32

C30

VCC33

C31

VCC34

C33

VCC35

C34

VCC36

C36

VCC37

D13

VCC38

D14

VCC39

D15

VCC40

D16

VCC41

D18

VCC42

D19

VCC43

D21

VCC44

D22

VCC45

D24

VCC46

D25

VCC47

D27

VCC48

D28

VCC49

D30

VCC50

D31

VCC51

D33

VCC52

D34

VCC53

D35

VCC54

D36

VCC55

E15

VCC56

E16

VCC57

E18

VCC58

E19

VCC59

E21

VCC60

E22

VCC61

E24

VCC62

E25

VCC63

E27

VCC64

E28

VCC65

E30

VCC66

E31

VCC67

E33

VCC68

E34

VCC69

E35

VCC70

F15

VCC71

F16

VCC72

F18

VCC73

F19

VCC74

F21

VCC75

F22

VCC76

F24

VCC77

F25

VCC78

F27

VCC79

F28

VCC80

F30

VCC81

F31

VCC82

F32

VCC83

F33

VCC84

F34

VCC85

G15

VCC86

G16

VCC87

G18

VCC88

G19

VCC90

G22

VCC91

G24

VCC92

G25

VCC93

G27

VCC94

G28

VCC95

G30

VCC96

G31

VCC97

G32

VCC98

G33

VCC99

H13

VCC100

H14

VCC101

H15

VCC102

H16

VCC103

H18

VCC104

H19

VCC105

H21

VCC106

H22

VCC107

H24

VCC108

H25

VCC109

H27

VCC110

H28

VCC111

H30

VCC112

H31

VCC113

H32

VCC114

J12

VCC115

J15

VCC116

J16

VCC117

J18

VCC118

J19

VCC119

J21

VCC120

J22

VCC121

J24

VCC122

J25

VCC123

J27

VCC124

J28

VCC125

J30

VCC126

K15

VCC127

K16

VCC128

K18

VCC129

K19

VCC130

K21

VCC131

K22

VCC132

K24

VCC133

K25

VCC134

K27

VCC135

K28

VCC136

K30

VCC137

L13

VCC138

L14

VCC139

L15

VCC140

L16

VCC141

L18

VCC142

L19

VCC143

L21

VCC144

L22

VCC145

L24

VCC146

L25

VCC147

L27

VCC148

L28

VCC149

L30

VCC150

M14

VCC151

M15

VCC152

M16

VCC153

M18

VCC154

M19

VCC155

M21

VCC156

M22

VCC157

M24

VCC158

M25

VCC159

M27

VCC160

M28

VCC161

M30

VCC89

G21

C43

100nF 16V-04

C43

100nF 16V-04

C64

10pF 50V-04-OTS

C64

10pF 50V-04-OTS

C33

22UF 6.3V-08

C33

22UF 6.3V-08

C36

22UF 6.3V-08

C36

22UF 6.3V-08

C28

22UF 6.3V-08

C28

22UF 6.3V-08

C42

100nF 16V-04

C42

100nF 16V-04

C55

22UF 6.3V-08

C55

22UF 6.3V-08

C34

22UF 6.3V-08

C34

22UF 6.3V-08

C29

22UF 6.3V-08

C29

22UF 6.3V-08

C46

100nF 16V-04

C46

100nF 16V-04

C56

22UF 6.3V-08

C56

22UF 6.3V-08

C62

100nF 16V-04

C62

100nF 16V-04

C59

4.7uF 10V-06

C59

4.7uF 10V-06

C24

22UF 6.3V-08

C24

22UF 6.3V-08

C30

22UF 6.3V-08

C30

22UF 6.3V-08

C26

22UF 6.3V-08

C26

22UF 6.3V-08

C52

22UF 6.3V-08

C52

22UF 6.3V-08

C51

10pF 50V-04-OTS

C51

10pF 50V-04-OTS

C25

22UF 6.3V-08

C25

22UF 6.3V-08

C35

22UF 6.3V-08

C35

22UF 6.3V-08

C40

NC/22UF 6.3V-08

C40

NC/22UF 6.3V-08

C57

22UF 6.3V-08

C57

22UF 6.3V-08

C60

4.7uF 10V-06

C60

4.7uF 10V-06

C23

22UF 6.3V-08

C23

22UF 6.3V-08

C45

10pF 50V-04-OTS

C45

10pF 50V-04-OTS

R55

0R-08

R55

0R-08

C53

22UF 6.3V-08

C53

22UF 6.3V-08

C39

NC/22UF 6.3V-08

C39

NC/22UF 6.3V-08

C49

100nF 16V-04

C49

100nF 16V-04

C65

10uF 6.3V-06

C65

10uF 6.3V-06

Yang Danny

CA203 Mother Board

A3

CS

1310A2546301

A

42

9

INVENTEC

TITLE

SIZE CODE DOC. NUMBER REV

CHANGE by SHEET OF

Page 10

1

1

2

2

3

3

4

4

5

5

6

6

7

7

8

8

A A

B B

C C

D D

E E

F F

OEM MODEL

Size

Rev

Date

Sheet

of

T&I MODEL

PCB NAME

remark

T&I (TPV-INVENTA TECHNOLOGY CO., LTD)

Key Component

Circuit diagram NO. CA202M DVT_0.1

CA203M C

10 42Monday, November 12, 2012

6050A2546301

<remark>

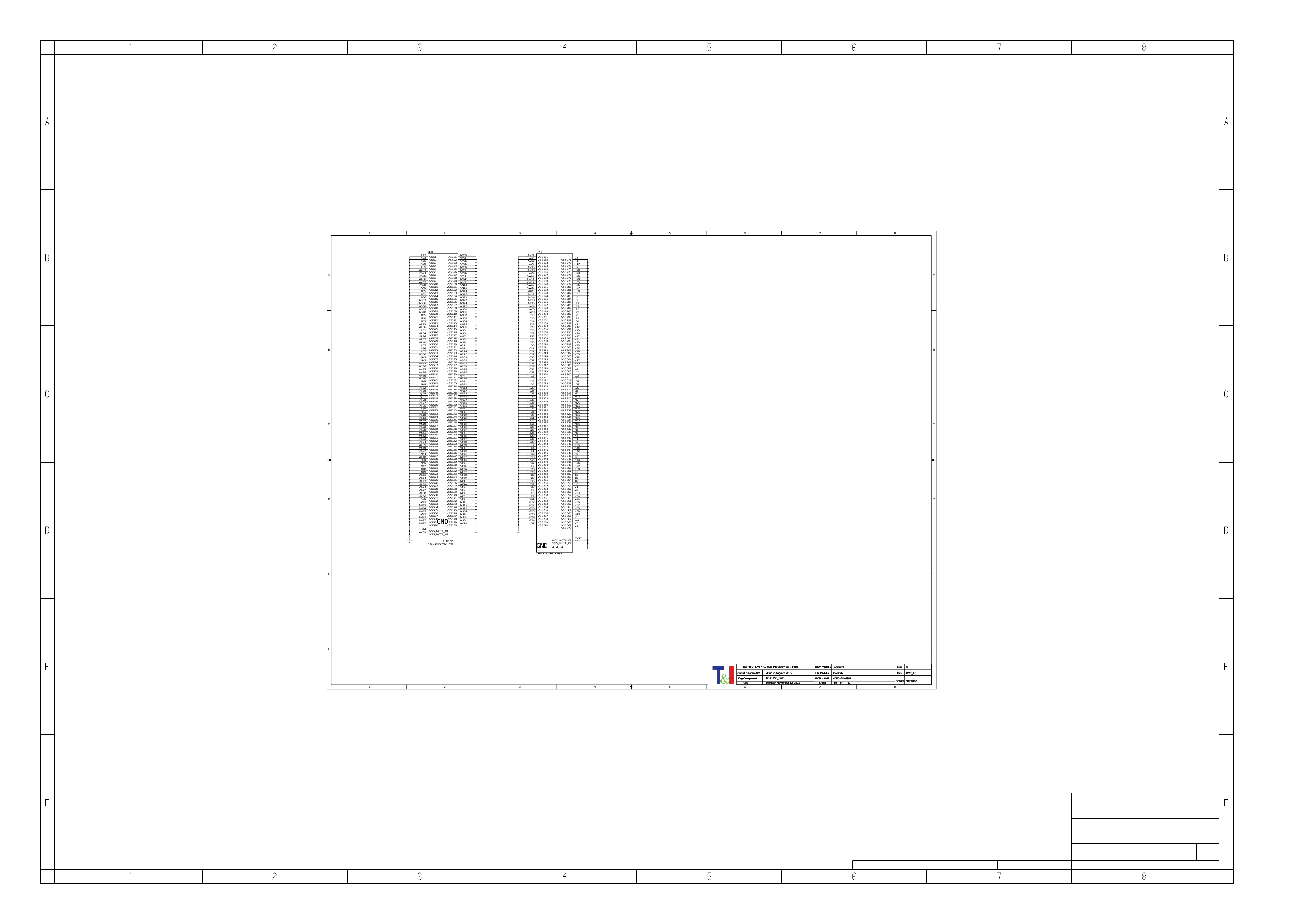

LGA1155_GND

<Circuit diagram NO.>

OEM MODEL

Size

Rev

Date

Sheet

of

T&I MODEL

PCB NAME

remark

T&I (TPV-INVENTA TECHNOLOGY CO., LTD)

Key Component

Circuit diagram NO. CA202M DVT_0.1

CA203M C

10 42Monday, November 12, 2012

6050A2546301

<remark>

LGA1155_GND

<Circuit diagram NO.>

OEM MODEL

Size

Rev

Date

Sheet

of

T&I MODEL

PCB NAME

remark

T&I (TPV-INVENTA TECHNOLOGY CO., LTD)

Key Component

Circuit diagram NO. CA202M DVT_0.1

CA203M C

10 42Monday, November 12, 2012

6050A2546301

<remark>

LGA1155_GND

<Circuit diagram NO.>

10 OF 10

GND

U1J

CPU-SOCKET-1155P

10 OF 10

GND

U1J

CPU-SOCKET-1155P

VSS181

AV11

VSS182

AV14

VSS183

AV17

VSS184

AV3

VSS185

AV35

VSS186

AV38

VSS187

AV6

VSS188

AW10

VSS189

AW11

VSS190

AW14

VSS191

AW16

VSS192

AW36

VSS193

AW6

VSS194

AY11

VSS195

AY14

VSS196

AY18

VSS197

AY35

VSS198

AY4

VSS199

AY6

VSS200

AY8

VSS201

B10

VSS202

B13

VSS203

B14

VSS204

B17

VSS205

B23

VSS206

B26

VSS207

B29

VSS208

B32

VSS209

B35

VSS210

B38

VSS211

B6

VSS212

C11

VSS213

C12

VSS214

C17

VSS215

C20

VSS216

C23

VSS217

C26

VSS218

C29

VSS219

C32

VSS220

C35

VSS221

C7

VSS222

C8

VSS223

D17

VSS224

D2

VSS225

D20

VSS226

D23

VSS227

D26

VSS228

D29

VSS229

D32

VSS230

D37

VSS231

D39

VSS232

D4

VSS233

D5

VSS234

D9

VSS235

E11

VSS236

E12

VSS237

E17

VSS238

E20

VSS239

E23

VSS240

E26

VSS241

E29

VSS242

E32

VSS243

E36

VSS244

E7

VSS245

E8

VSS246

F1

VSS247

F10

VSS248

F13

VSS249

F14

VSS250

F17

VSS251

F2

VSS252

F20

VSS253

F23

VSS254

F26

VSS255

F29

VSS256

F35

VSS257

F37

VSS258

F39

VSS259

F5

VSS260

F6

VSS261

F9

VSS262

G11

VSS263

G12

VSS264

G17

VSS265

G20

VSS266

G23

VSS267

G26

VSS268

G29

VSS269

G34

VSS270

G7

VSS271

G8

VSS272

H1

VSS273

H17

VSS274

H2

VSS275

H20

VSS276

H23

VSS277

H26

VSS278

H29

VSS279

H33

VSS280

H35

VSS281

H37

VSS294

K12

VSS295

K13

VSS296

K14

VSS297

K17

VSS299

K20

VSS300

K23

VSS301

K26

VSS302

K29

VSS303

K33

VSS304

K35

VSS305

K37

VSS306

K39

VSS307

K5

VSS308

K6

VSS309

L10

VSS310

L17

VSS311

L20

VSS314

L29

VSS315

L8

VSS317

M17

VSS318

M2

VSS320

M23

VSS321

M26

VSS322

M29

VSS333

M33

VSS334

M35

VSS336

M39

VSS337

M5

VSS339

M9

VSS340

N8

VSS341

P1

VSS342

P2

VSS344

P38

VSS345

P40

VSS346

P5

VSS347

P6

VSS348

R33

VSS349

R35

VSS352

R8

VSS353

T1

VSS354

T5

VSS355

T6

VSS356

U8

VSS357

V1

VSS358

V2

VSS359

V33

VSS360

V34

VSS_NCTF_04

B3

VCC_NCTF_03

AY37

VSS282

H39

VSS283

H5

VSS284

H6

VSS285

H9

VSS286

J11

VSS287

J17

VSS288

J20

VSS289

J23

VSS290

J26

VSS291

J29

VSS292

J32

VSS293

K1

VSS298

K2

VSS132

L23

VSS313

L26

VSS316

M1

VSS319

M20

VSS335

M37

VSS338

M6

VSS343

P36

VSS350

R37

VSS351

R39

VSS361

V35

VSS363

V37

VSS364

V38

VSS365

V39

VSS366

V40

VSS367

V5

VSS368

W6

VSS369

Y5

VSS370

Y8

VSS362

V36

GND

9 OF 10

U1I

CPU-SOCKET-1155P

GND

9 OF 10

U1I

CPU-SOCKET-1155P

VSS1

A17

VSS2

A23

VSS3

A26

VSS4

A29

VSS5

A35

VSS6

AA33

VSS7

AA34

VSS8

AA35

VSS9

AA36

VSS10

AA37

VSS11

AA38

VSS12

AA6

VSS13

AB5

VSS14

AC1

VSS15

AC6

VSS16

AD33

VSS17

AD36

VSS18

AD38

VSS19

AD39

VSS20

AD40

VSS21

AD5

VSS22

AD8

VSS23

AE3

VSS24

AE33

VSS25

AE36

VSS26

AF1

VSS27

AF34

VSS28

AF36

VSS33

AF7

VSS29

AF37

VSS30

AF40

VSS31

AF5

VSS32

AF6

VSS34

AG36

VSS35

AH2

VSS36

AH3

VSS37

AH33

VSS38

AH36

VSS39

AH37

VSS40

AH38

VSS41

AH39

VSS42

AH40

VSS43

AH5

VSS44

AH8

VSS45

AJ12

VSS46

AJ15

VSS47

AJ18

VSS48

AJ21

VSS49

AJ25

VSS50

AJ27

VSS52

AJ5

VSS53

AK1

VSS54

AK10

VSS55

AK13

VSS56

AK14

VSS57

AK16

VSS58

AK22

VSS59

AK28

VSS60

AK31

VSS61

AK32

VSS62

AK33

VSS63

AK34

VSS64

AK35

VSS65

AK36

VSS66

AK37

VSS67

AK4

VSS68

AK40

VSS69

AK5

VSS71

AK7

VSS72

AK8

VSS73

AK9

VSS74

AL11

VSS75

AL14

VSS76

AL17

VSS77

AL19

VSS70

AK6

VSS78

AL24

VSS80

AL30

VSS81

AL36

VSS82

AL5

VSS83

AM1

VSS84

AM11

VSS85

AM14

VSS86

AM17

VSS87

AM2

VSS89

AM23

VSS92

AM3

VSS94

AM36

VSS96

AM38

VSS97

AM39

VSS98

AM4

VSS100

AM5

VSS101

AN10

VSS102

AN11

VSS103

AN14

VSS104

AN17

VSS105

AN19

VSS107

AN24

VSS110

AN31

VSS112

AN33

VSS116

AN5

VSS117

AN6

VSS118

AN7

VSS120

AN9

VSS121

AP1

VSS122

AP11

VSS123

AP14

VSS124

AP17

VSS125

AP22

VSS126

AP25

VSS127

AP27

VSS128

AP30

VSS129

AP36

VSS130

AP37

VSS131

AP4

VSS132

AP40

VSS133

AP5

VSS134

AR11

VSS135

AR14

VSS136

AR17

VSS137

AR18

VSS138

AR19

VSS139

AR27

VSS140

AR30

VSS141

AR36

VSS142

AR5

VSS143

AT1

VSS144

AT10

VSS145

AT12

VSS146

AT13

VSS147

AT15

VSS148

AT16

VSS149

AT17

VSS150

AT2

VSS151

AT25

VSS152

AT27

VSS153

AT28

VSS154

AT29

VSS155

AT3

VSS156

AT30

VSS157

AT31

VSS158

AT32

VSS159

AT33

VSS160

AT34

VSS161

AT35

VSS162

AT36

VSS163

AT37

VSS164

AT38

VSS165

AT39

VSS166

AT4

VSS167

AT40

VSS168

AT5

VSS169

AT6

VSS170

AT7

VSS171

AT8

VSS172

AT9

VSS173

AU1

VSS174

AU15

VSS175

AU26

VSS176

AU34

VSS177

AU4

VSS178

AU6

VSS179

AU8

VSS180

AV10

VSS90

AM25

VSS79

AL27

VSS51

AJ36

VSS88

AM21

VSS91

AM27

VSS95

AM37

VSS93

AM30

VSS99

AM40

VSS106

AN22

VSS108

AN27

VSS109

AN30

VSS111

AN32

VSS113

AN34

VSS114

AN35

VSS115

AN36

VSS119

AN8

VSS_NCTF_01

A4

VSS_NCTF_02

AV39

Yang Danny

CA203 Mother Board

A3

CS

1310A2546301

A

42

10

INVENTEC

TITLE

SIZE CODE DOC. NUMBER REV

CHANGE by SHEET OF

Page 11

1

1

2

2

3

3

4

4

5

5

6

6

7

7

8

8

A A

B B

C C

D D

E E

F F

to processor 100MHz

Close to PCH ball pin /

Reserved for disable EXT CLK

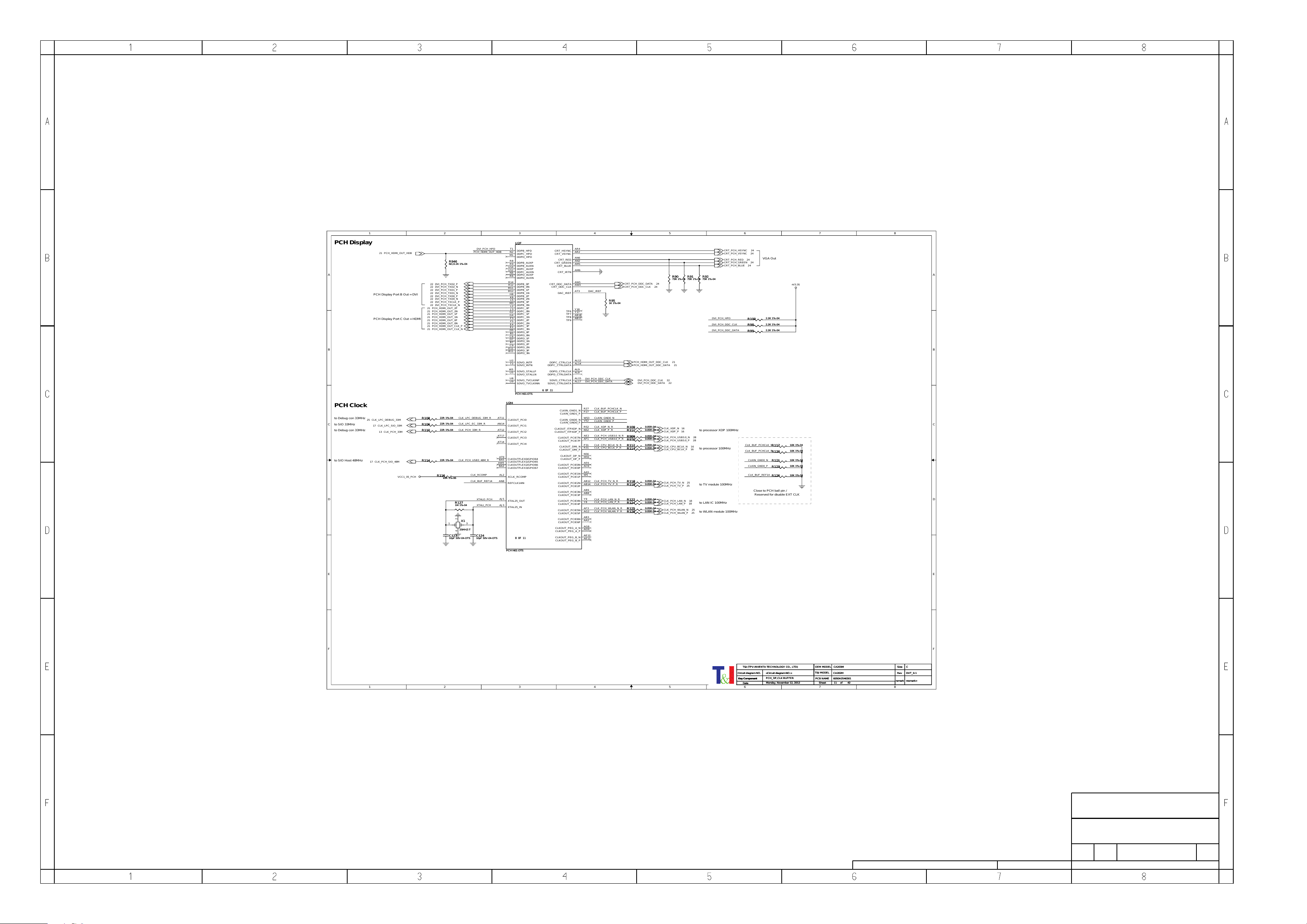

PCH Display

PCH Clock

to processor XDP 100MHz

PCH Display Port B Out = DVI

to WLAN module 100MHz

to TV module 100MHz

to LAN IC 100MHz

to Debug con 33MHz

to SIO 33MHz

to Debug con 33MHz

to SIO Host 48MHz

VGA Out

PCH Display Port C Out = HDMI

XTALO_PCH

XTALI_PCH

CLK_RCOMP

CLK_CPU_BCLK_N_R

CLK_CPU_BCLK_P_R

CLKIN_GND0_N

CLKIN_GND0_P

CLK_XDP_P_R

CLK_XDP_N_R

CLK_BUF_REF14

DAC_IREF

CLK_BUF_PCHCLK_N

CLK_BUF_PCHCLK_P

CLK_BUF_PCHCLK_N

CLK_BUF_PCHCLK_P

CLKIN_GND0_P

CLKIN_GND0_N

CLK_BUF_REF14

DVI_PCH_HPD

PCH_HDMI_OUT_HDB

DVI_PCH_DDC_CLK

DVI_PCH_DDC_DATA

CLK_PCH_33M_R

CLK_LPC_DEBUG_33M_R

CLK_PCH_WLAN_N_R

CLK_PCH_WLAN_P_R

CLK_PCH_TV_N_R

CLK_PCH_TV_P_R

CLK_LPC_EC_33M_R

DVI_PCH_DDC_CLK

DVI_PCH_DDC_DATA

CLK_PCH_LAN_N_R

CLK_PCH_LAN_P_R

CLK_PCH_USB3_48M_R

CLK_PCH_USB3.0_N_R

CLK_PCH_USB3.0_P_R

DVI_PCH_HPD

VCC1_05_PCH

+V3.3S

CLK_CPU_BCLK_N 16

CLK_CPU_BCLK_P 16

CLK_XDP_N 16

CLK_XDP_P 16

DVI_PCH_DDC_DATA 22

DVI_PCH_DDC_CLK 22

CLK_PCH_33M13

CLK_LPC_DEBUG_33M25

CLK_PCH_WLAN_N 25

CLK_PCH_WLAN_P 25

CLK_PCH_TV_N 25

CLK_PCH_TV_P 25

DVI_PCH_TXD2_N22

DVI_PCH_TXD2_P22

DVI_PCH_TXD1_N22

DVI_PCH_TXD1_P22

DVI_PCH_TXD0_N22

DVI_PCH_TXD0_P22

DVI_PCH_TXCLK_N22

DVI_PCH_TXCLK_P22

CRT_PCH_RED 24

CRT_PCH_GREEN 24

CRT_PCH_BLUE 24

CRT_PCH_DDC_DATA 24

CRT_PCH_DDC_CLK 24

CRT_PCH_HSYNC 24

CRT_PCH_VSYNC 24

CLK_LPC_SIO_33M17

CLK_PCH_LAN_N 18

CLK_PCH_LAN_P 18

CLK_PCH_SIO_48M17

PCH_HDMI_OUT_DDC_DATA 21

PCH_HDMI_OUT_DDC_CLK 21

PCH_HDMI_OUT_2P21

PCH_HDMI_OUT_2N21

PCH_HDMI_OUT_1P21

PCH_HDMI_OUT_1N21

PCH_HDMI_OUT_0P21

PCH_HDMI_OUT_0N21

PCH_HDMI_OUT_CLK_P21

PCH_HDMI_OUT_CLK_N21

PCH_HDMI_OUT_HDB21