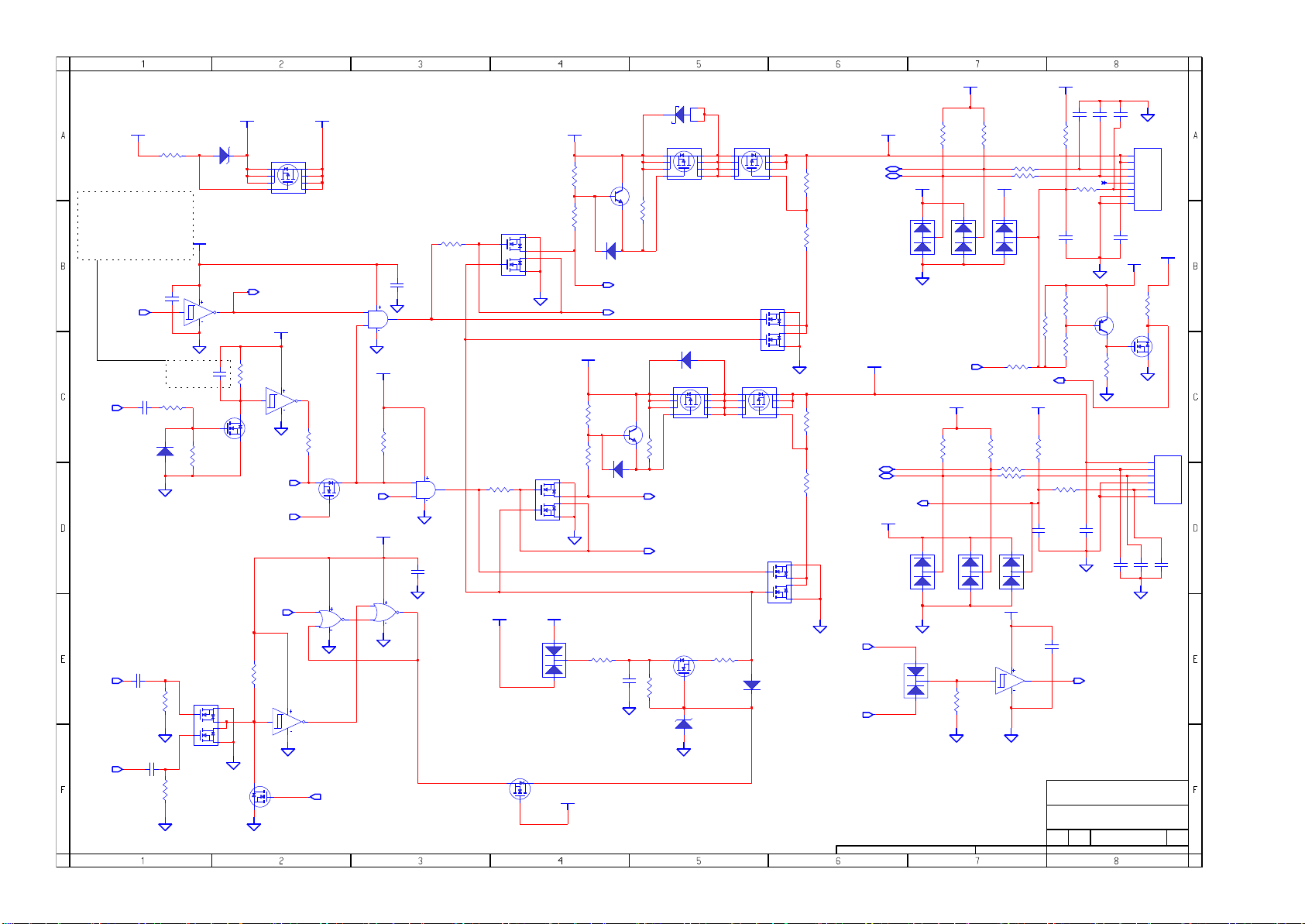

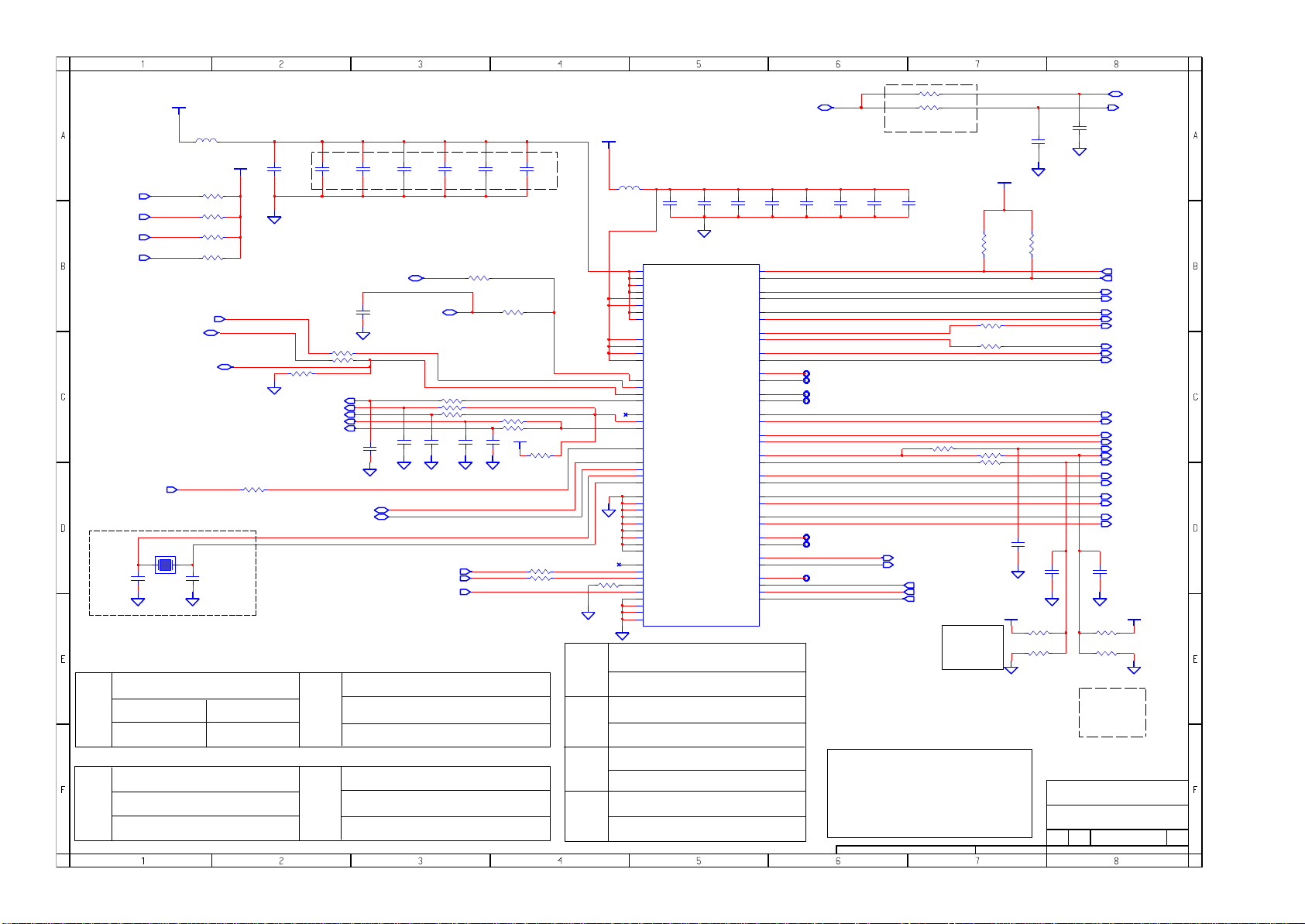

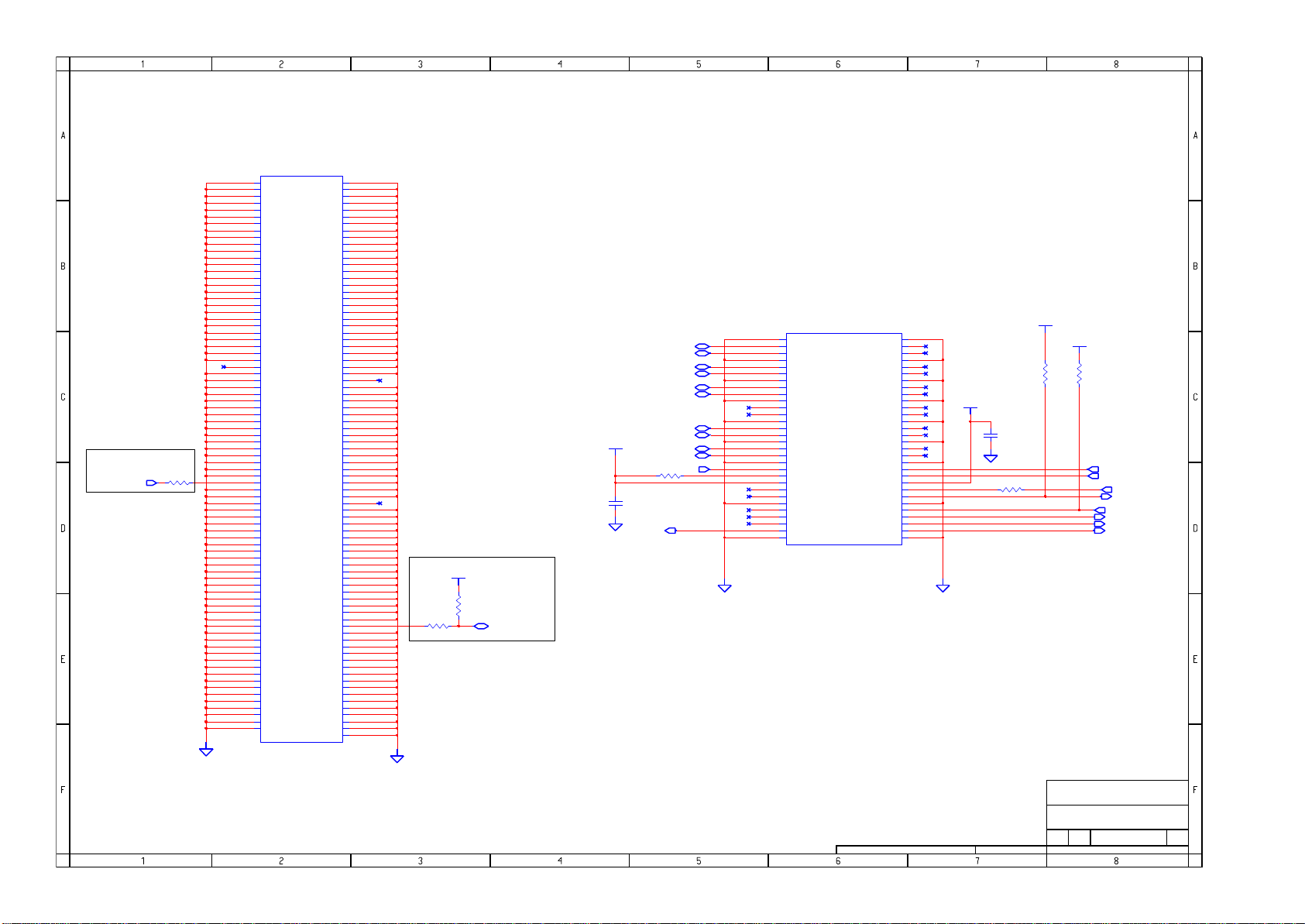

Page 1

ABSOLUT

MV2 Build

2008.07.22

DATE CHANGE NO. REV

DRAWER

DESIGN

CHECK

RESPONSIBLE

SIZE = 3

FILE NAME : XXXX-XXXXXX-XX

P/N XXXXXXXXXXXX

DATEDATEEE POWER

INVENTEC

TITLE

ABSOLUT

SIZE CODE DOC. NUMBER REVVER :

A3

CS

SHEET OF

161

A04Model_No

Page 2

TABLE OF CONTENTS

PAGE

5. DC& BATTERY CHARGER

6. SELECT & BATTERY CONN

7. SYSTEM POWER(3V/5V)

8. SYSTEM POWER(+V1.05M/+VCCP)

9. SYSTEM POWER(+V1.5/+V1.8)

10. CPU POWER(VCC_CORE)

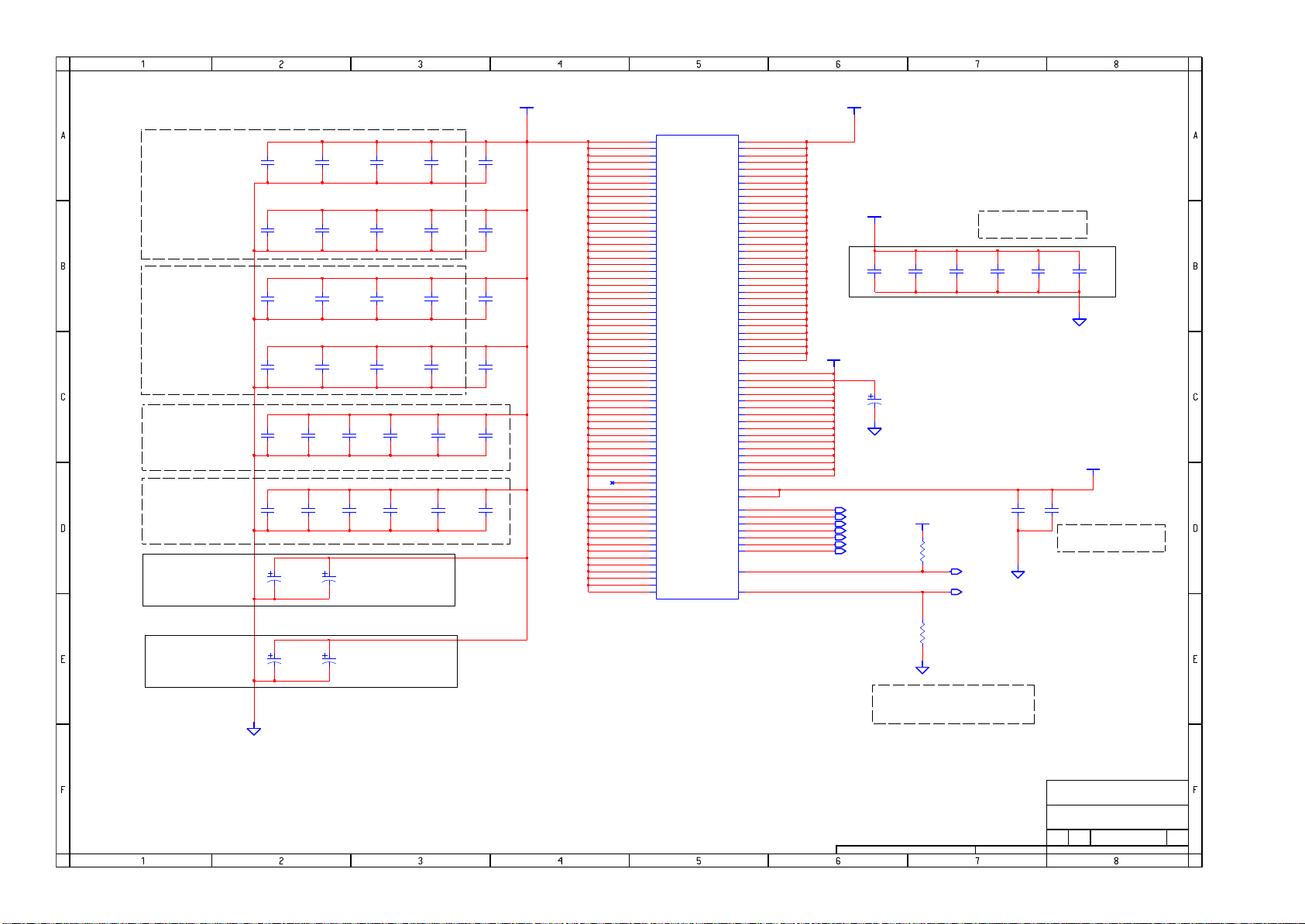

11. DDR TERMINATION VOLTAGE

12. POWER(SLEEP)

13. POWER(SEQUENCE)

14. CLOCK_GENERATOR

15. PENRYN-1

16. PENRYN-2

17. PENRYN-3

18. PENRYN-4

19. THERMAL / FAN CONTROLLER

20. CANTIGA-1

21. CANTIGA-2

22. CANTIGA-3

23. CANTIGA-4

24. CANTIGA-5

25. CANTIGA-6

26. CANTIGA-7

PAGE

30. MXM CNTR

31. VGA / LCM CNTR

32. HDMI CNTR

33. ICH9-1

34. ICH9-2

35. ICH9-3

36. ICH9-4

37. ICH9-5

38. KBC

39. SPI / Keyboard / Touchpad CNTR

40. Super I/O

41. AUDIO- 1

42. AUDIO- 2

43. AUDIO- 3

44. LAN- 1

45. LAN-2

46. CARDBUS CONTROLLER

47. HD PROTECTION / AMT ME / SATA HD&ODD CNTR

48. CAMERA / BLUETOOTH / FINGER PRINT / USB CNTR

49. WLAN CNTR

50. 1394 / NEW CARD & EXPRESS CARD CNTR

51. MDC CNTR / TPM V1.2

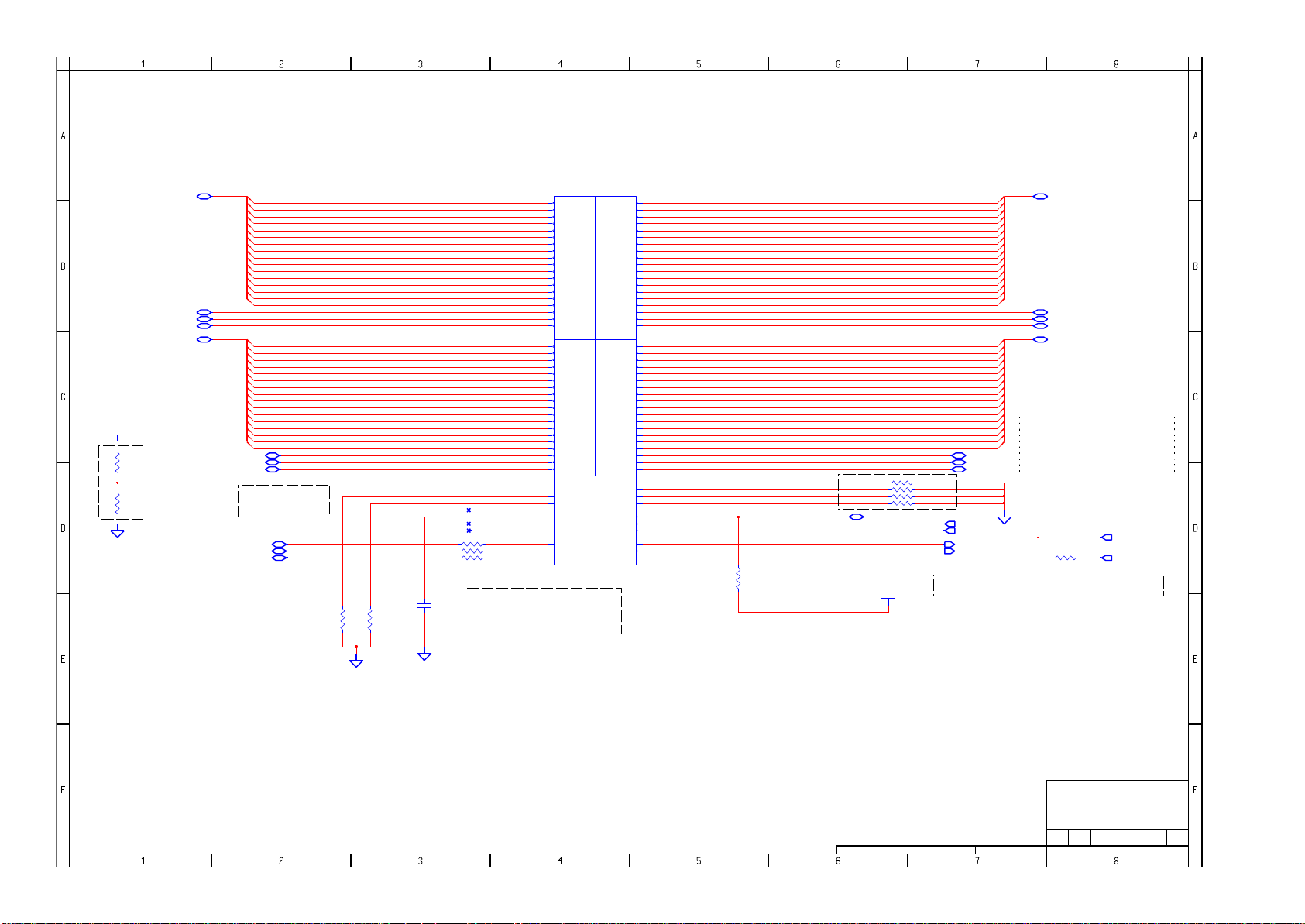

27. DDR2-DIMM0

28. DDR2-DIMM1

29. DDR2 Termination Res / Decoupling Cap

PAGE

52. DAUGHTER BOARD CNTRs

53. DOCKING CNTR

54. MAIN BOARD LEDs

55. MAIN BOARD SCREW HOLEs

56. DB- POWER BUTTON

57. DB- USB / ESATA

58. DB- MEDIA SOCKET A / AUDIO JACK

59. DB- MEDIA SOCKET B / AUDIO JACK

60. DB- FINGER PRINT

61. DB- ALS

CHANGE by

PUMA_CHEN

17-Jul-2008

INVENTEC

TITLE

ABSOLUT

CODE

CS

SHEET

DOC. NUMBER

261

SIZE

A3

REV

A04Model_No

OF

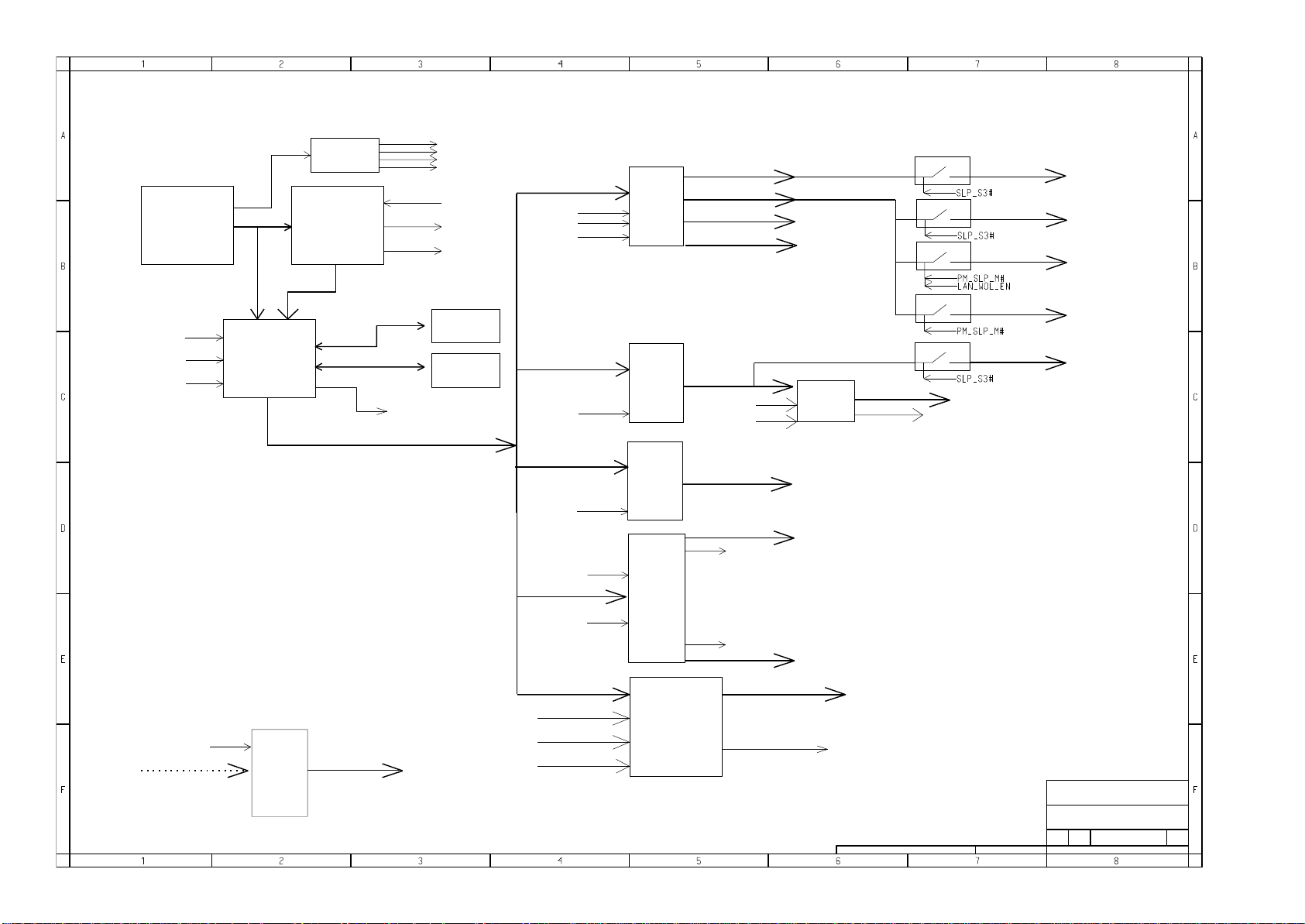

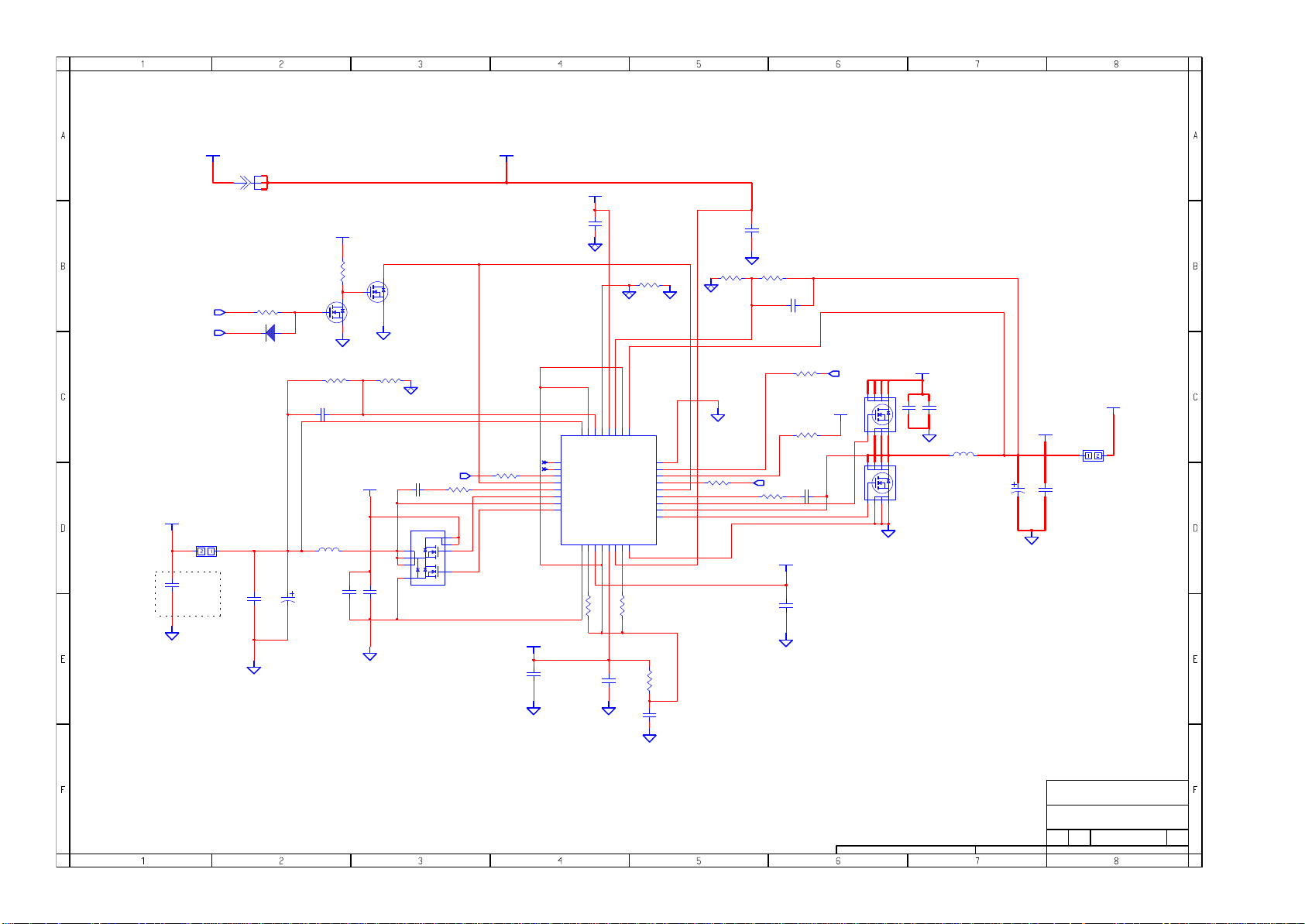

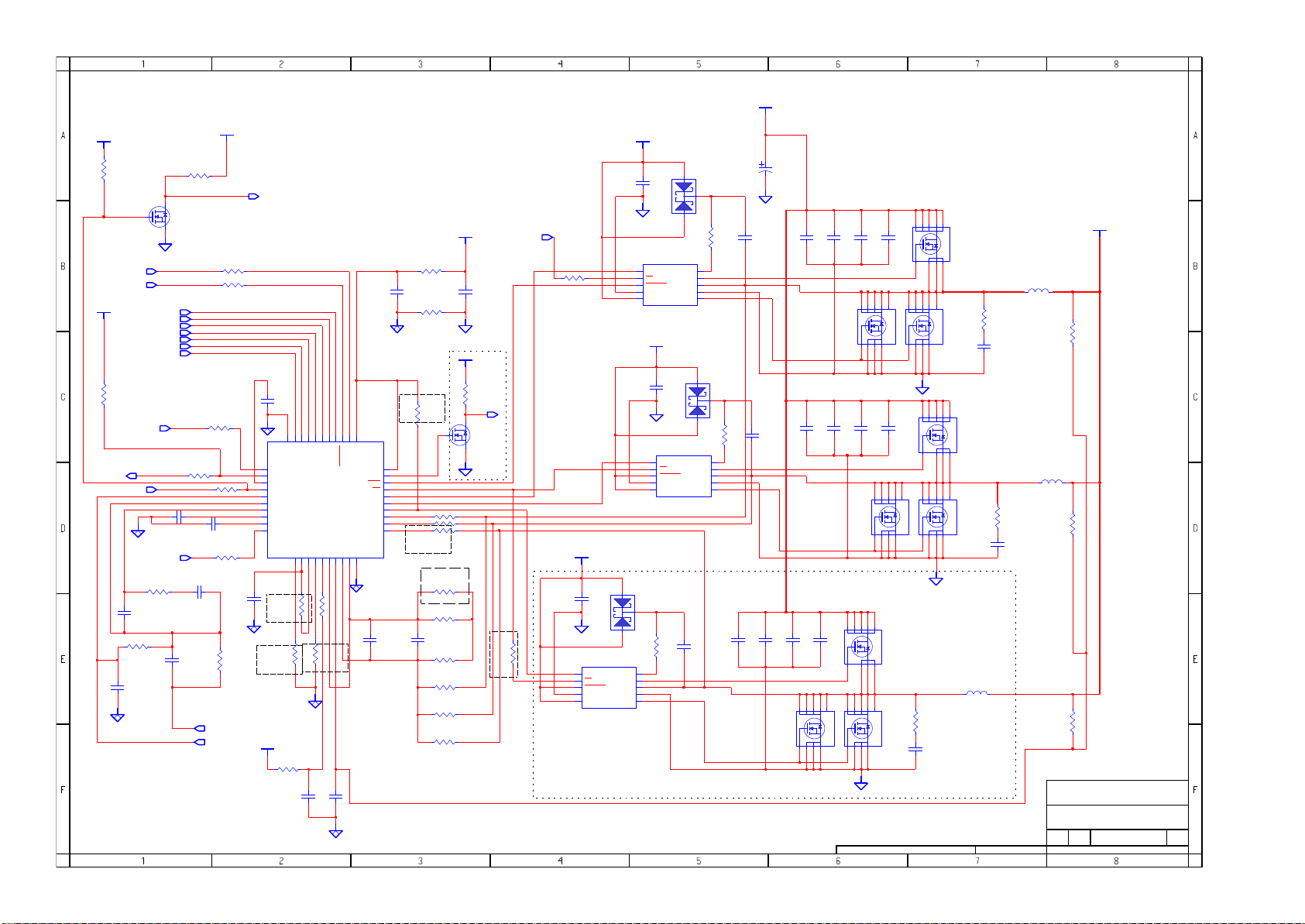

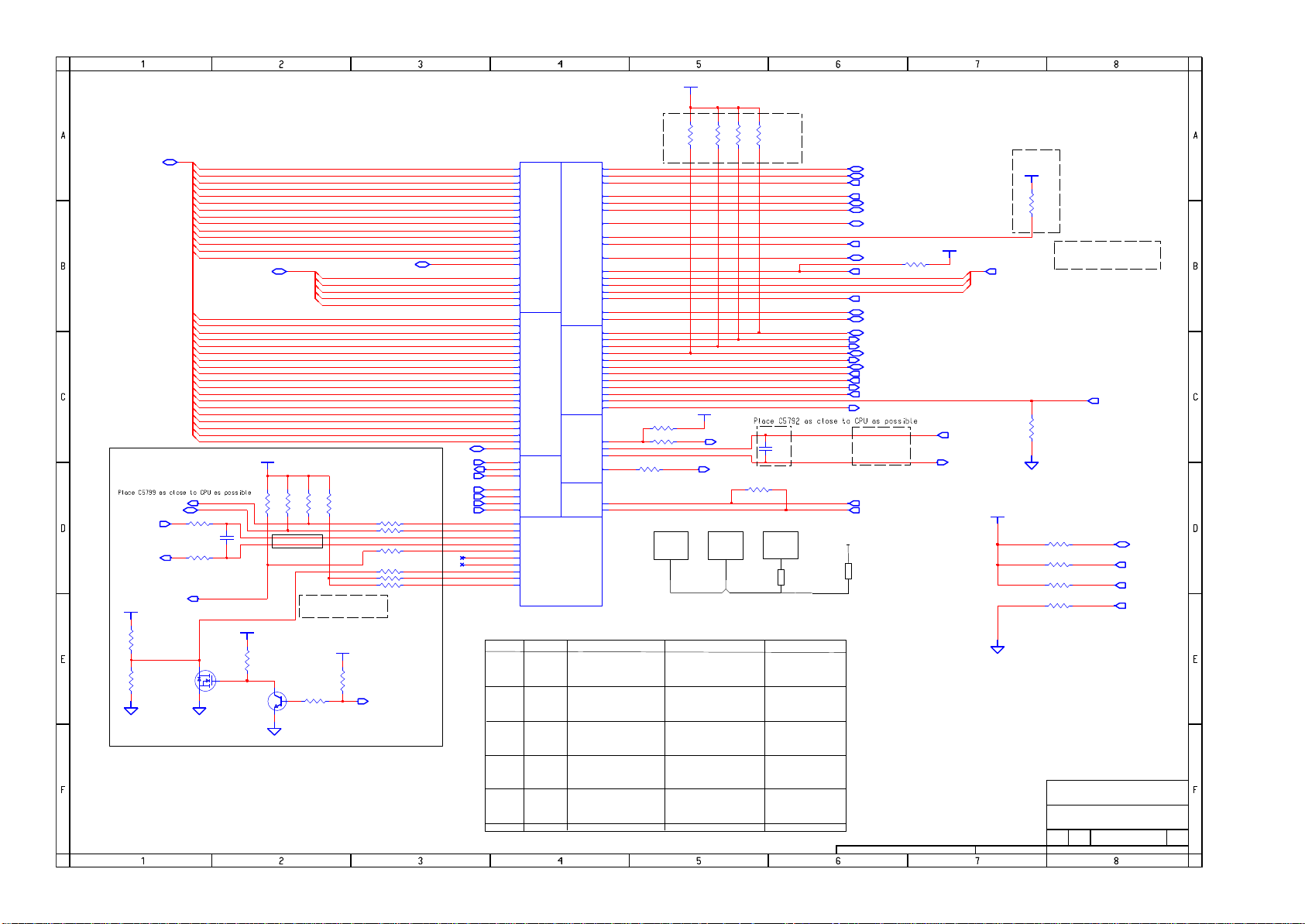

Page 3

HDMI

XDP

P18

P32

Penryn

(uFCPGA)

P15~18

ICS9LPRS397

Clock generator

P14

LCM

P31

CRT

P31

USB0

CONN A

P48

USB1

CONN B

P57

USB3

P57

PORT REPLICATOR

USB4

CONN C

USB11

CONN D

P57

Dock

P53

MXM III CNTR

(256MB)

USB5

USB10

USB6

CONN E

P57

Camera

P48

3.3V, 33MHz/Azalia

P48

USB9

53

P30

ODD

ESATA

USB7

Bluetooth

Dock

WWAN

P49

USB8

FIGER PRINT

P48

16X PCIE

SATA

P47

SATA

P57

FSB

Cantiga

PM

DMI

ICH9-M

PCI_EXPRESS

Giga-bit LAN

Intel Boza

P20~26

P33~37

P44

SPI

SATA

PCI_EXPRESS

MINI CARD

LPC

DDR2 Interface

DDR2 Interface

KBC1091

USB2 /PCI_EXPRESS

P38

HDD

P47

3.3V, PCI_Interface,33MHz

(WLAN)

P49

DDR II_SODIMM0

EEPROM

P39

EXPRESS

CARD

DDR II_SODIMM1

P27

P50

RICOH_R5C835

SMART

CARD

28

CARD BUS

P50

P46

1394

P50

BATTERY

P5~6

System Charger &

DC/DC System power

P7~13

MDC_1.5/Modem

Module 56K

P51

RJ11

AD_1984HD

RJ45

P41

TCPA

P51

Super I/O

47N217

Kahuna Lite2

KBC1091

P40

P38

7 IN 1

MEDIA SOCKET

P58

INVENTEC

TITLE

ABSOLUT

Block Diagram

DOC. NUMBER

CHANGE by

PUMA_CHEN

17-Jul-2008

SIZE

A3

CODE

CS

SHEET

361

REV

A04Model_No

OF

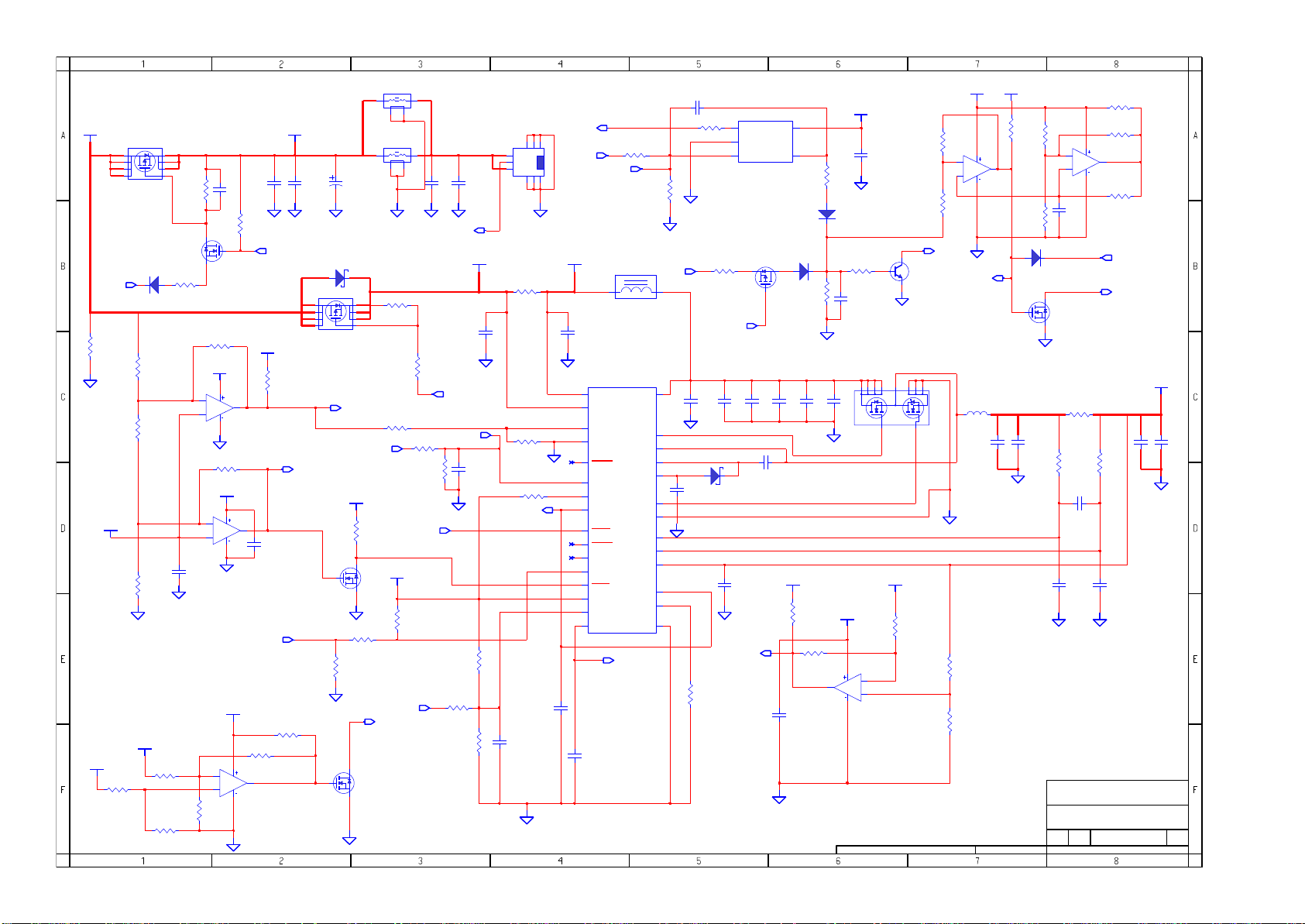

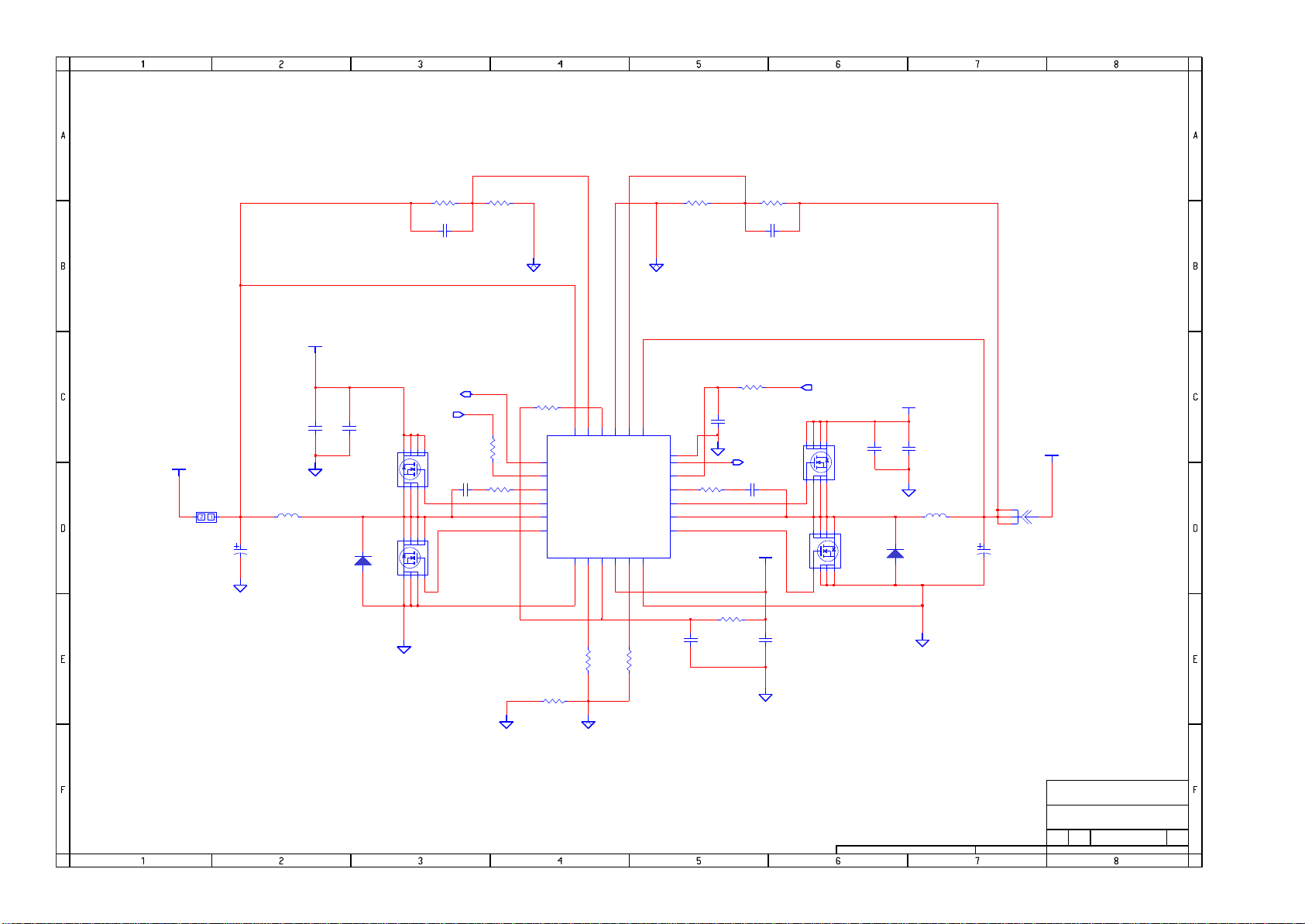

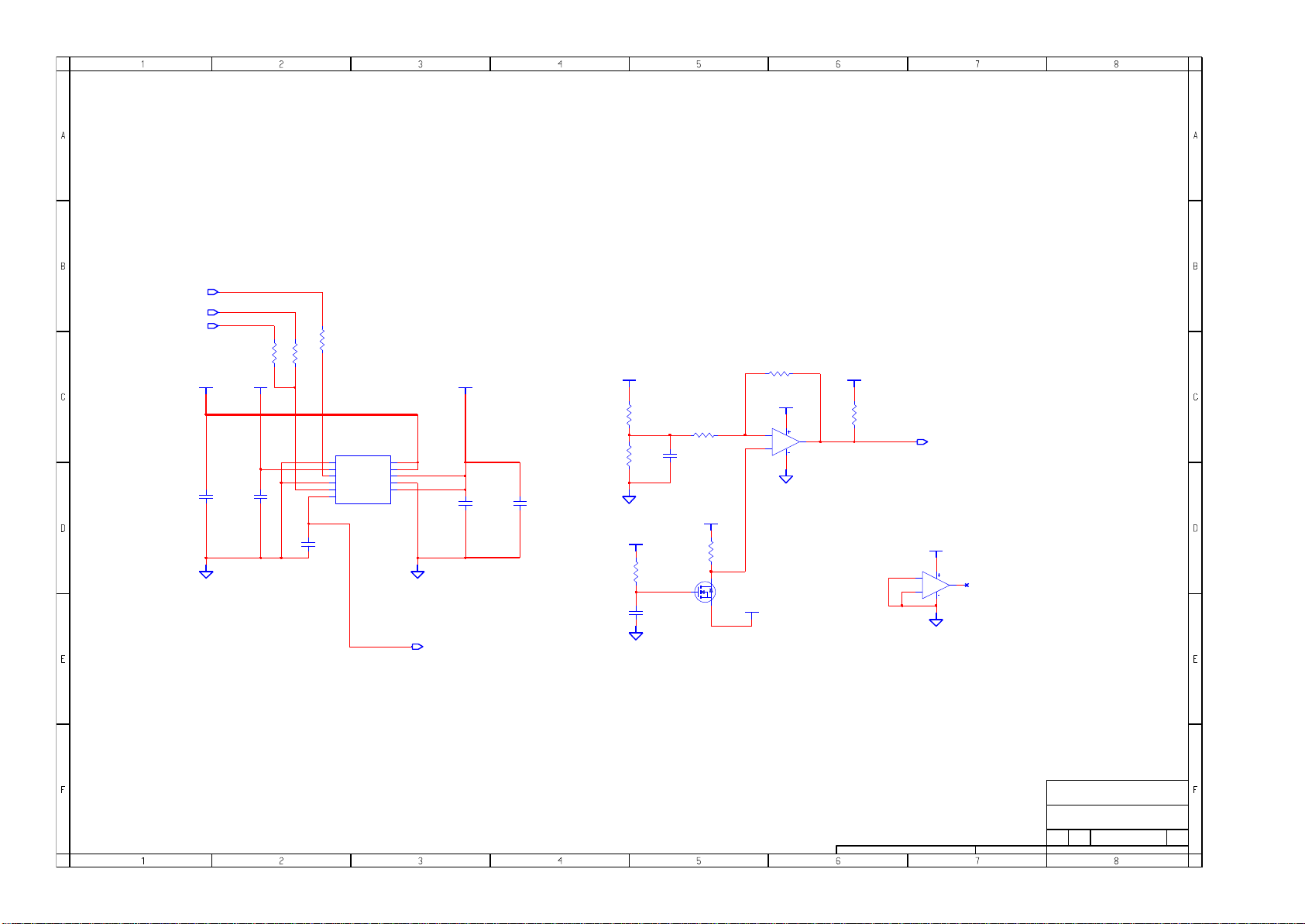

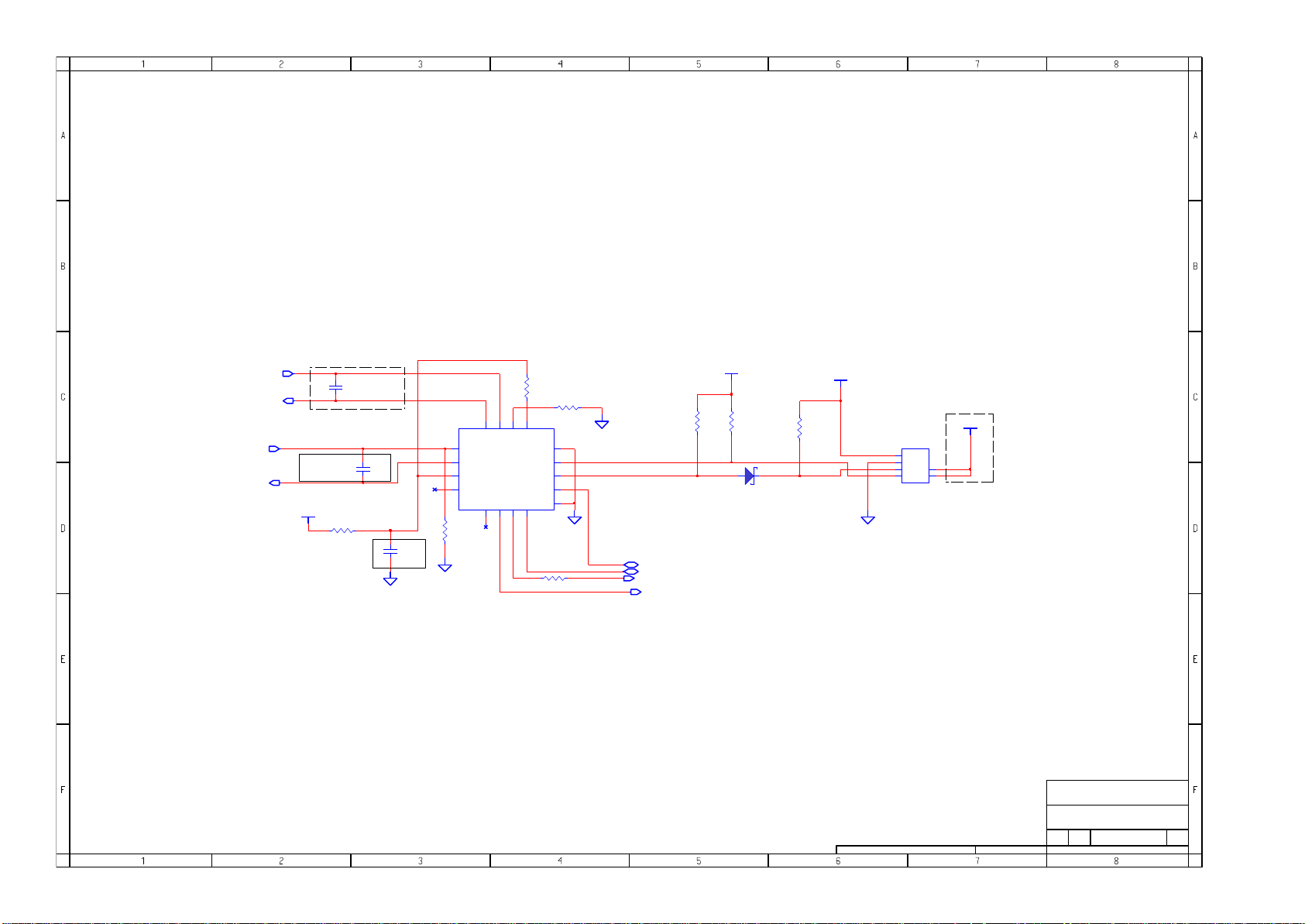

Page 4

Adapter

(90W)

LIMIT_SIGNAL

OCP

Charger

(BQ24740)

ADP_EN

OCP#

ADP_PS0

ADP_PS1

CHGCTRL_3

ADP_PRES

AC_AND_CHG

ADP_PRES

KBC_PW_ON

SLP_S3#_3R

5/3.3V

(TPS51120)

+V5A

+V3A

+V5AL

+V3AL

FDC655BN

FDC655BN

AO6409

+V5S

+V3S

+V3M

BATSELB

AC_AND_CHG

CHGCTRL_3

SLP_S3#

+VBAT

Selector

(Discrete)

+VBATR

VGA POWER

(MAX8760)

+VBDC

+VBATA

+VBATB

+VDD_CORE

BATCON

Main Battery

Travel Battery

PWR_GOOD_3

PM_DPRSLPVR

SLP_S4#_3R

SLP_S3#_3R

SLP_S3#_3R

PM_SLP_M#

PSI#

DDR2/1.8V

(TPS51117)

(TPS51117)

IO POWER

(TPS51124)

IMVP VI

(ADP3207)

+V1.8

SLP_S4#_3R

PM_SLP_M#

+V1.5S

+VCCP

VCCP_PG

V1.05M_PG

+V1.05M

+VCC_CORE

LR

(G2997F6U)

VGATE

CHANGE by

AO6409

FDC655BN

+V0.9

M_VREF

PUMA_CHEN 17-Jul-2008

+V3M_WOL

+V1.8S

INVENTEC

TITLE

ABSOLUT

SIZE

A3

DOC. NUMBER

CODE

Model_No A04

CS

SHEET

REV

OF

614

Page 5

+VADPBL

5-,6-

ADP_EN#

1

2

+VBDC

8

7

6

5

CHENKO_LL4148_2P

R39

15K_5%

2VREF

5-,7-,11-,13-

R5685

14.3K_1%

5-,6-

R5686

12

100K_1%

Q17

FDS6673BZ

D

S

G

D11

13-

1

R5696

100K_1%

2

1

R5674

8.25K_1%

2

1

2

+VADPBL

5-,6-

12

100K_1%

12

24K_1%

1

2

3

4

21

R5680

23.7K_1%

R64

R5697

220K_5%

Q16

2N7002W

R5698

100K_5%

C5582

1

2

0.22uF_16v

R5687

1

C68

1

2

0.1uF_16v

2

1

2

3

D

G

1

S

2

12

R5675

12

270K_5%

+V5AL

5-,6-,7-,11-,12-

8

5

U27-B

+

7

OUT

6

-

ON_LM393DR2G_SOP_8P

4

R5676

1M_5%

12

+V5AL

5-,6-,7-,11-,12-

8

U27-A

3

+

1

OUT

2

4

ON_LM393DR2G_SOP_8P

+V5AL

5-,6-,7-,11-,12-

8

3

+

OUT

2

-

TI_LMV393IDGKR_SOP_8P

1

4

2

+VADP

13-,53-

C186

C5564

1

1

2

2

10pF_50v

R5652

220K_5%

13-

BATCAL#

+V3AL

5-,6-,7-,11-,13-,33-,37-,38-,39-,47-,52-,54-

2

R5682

22K_5%

1

6-,13-,30-,38-

6-

AC_AND_CHG

1

C5590

0.1uF_16v

2

CELLS

38-

R5663

12

100K_5%

R5681

12

1M_5%

1

U5053-A

NFM60R30T222

NFM60R30T222

1

C189

2

33uF_25v

0.1uF_25v

D24

SSM14_1A40V

1

2

1

8

S

D

2

7

3

6

54

G

Q18

FDS6673BZ

ADP_PRES

CHGCTRL_3

6-,38-

+V3AL

5-,6-,7-,11-,13-,33-,37-,38-,39-,47-,52-,54-

2

R5658

10K_5%

1

5-,6-,7-,11-,13-,33-,37-,38-,39-,47-,52-,54-

3

D

1

G

S

Q5022

2

2N7002W

0_5%R5918

2

1

R6137

10K_5%

2

5-

3

D

G

1

Q5025

S

2N7002W

2

L5

12

3

4

L24

12

3

4

1

2

LIMIT_SIGNAL

6-

R41

2

1

47K_5%

1

R5660

4.7K_5%

2

5-

R5679

47K_5%

1

2

R5684

12

294K_1%

R5664

200K_1%

SLP_S3#_3R

7-,8-,9-,12-,13-,34-,38-,43-,50-,53-

+V3AL

1

R6138

10K_5%_OPEN

2

1

VCTRL_3

38-

ADPDRV#

FOX_JPD113E_LB106_7F_9P

C185

C5563

1

2

10pF_50v

0.1uF_25v

+VBAT

1

C89

1uF_25v

2

ADPDRV#

SRSET

5-

12

1

C5578

2

1uF_6.3v

PCSPKC#_3

R5668

453K_1%

2

R5659

422K_1%

12

R5667

1M_1%

2

DC JACK

JACK1

5-,13-,53-

1

1

1

2

789

1

9

POWER

2

ID

3

POWER

456

R115

0.01_1%_1W

12

1

R5657

300K_1%

1

BQREF

1uF_6.3v

C5577

1uF_6.3v

2

20K_5%R5651

C5583

+VBATR

1

2

2

5-

1

2

ICS

5-

5-

BQREF

U5043-3

7-,8-,9-,10-,12-,19-,30-,31-,38-

12

DE3518C_1127AS_R56N

C90

1uF_25v

U15

2

ACN

3

ACP

5

ACDET

9

AGND

13

EXTPWR

16

SRSET

6

ACSET

10

VREF

8

IADSLP

21

DPMDET

4

LPMD

20

CELLS

1

CHGEN

11

VDAC

12

VADJ

15

IADAPT

TI_BQ24740_QFN_28P

5-

1

C5579

100pF_50v

2

R5699

12

191K_1%

13-

R5653

105K_1%

LIMIT_SIGNAL

L2

PVCC

HIDRV

BTST

REGN

LODRV

PGND

SRP

SRN

BAT

LPREF

ISYNSET

PowerPad

ICS

5-,12-,13-,19-,30-,31-,32-,34-,36-,38-,39-,40-,41-,42-,43-,47-,48-,50-,53-

10-,12-,13-,14-,15-,18-,19-,20-,25-,26-,30-,31-,32-,33-,34-,35-,36-,37-,38-,40-,41-,46-,47-,48-,50-,51-,52-,54-

+V5S

3

+

OUT

12

OCP_OC

+V3S

2

80.6K_1%

13-

1

1

R5691

R5690

133K_1%

10K_5%

2

2

1

1

R5689

2

2

D5049

21

CHENKO_LL4148_2P

3

D

1

G

Q5097

S

2

7

+

OUT

6

-

C5589

0.027uF_10v

2N7002W

3

U5080-B

12

R5694

12

10K_5%

R5693

12

100K_5%

1

ON_LM339DR2G_SOP_14P

R5692

12

604K_1%

10-,13-,30-,38-

PWR_GOOD_3

34-

OCP_OC#

C5565

0.22uF_16v

1

2

5-,13-,53-

12

R5661

12

1

10K_5%

2

3

TI_LMV321IDBVR_SOT23_5P

R6047

12

100_5%

VBIAS

5-,12-,13-,19-,30-,31-,32-,34-,36-,38-,39-,40-,41-,42-,43-,47-,48-,50-,53-

U5078

1IN+

GND

1IN-

Q5035

BSS84_3P

2

S

G

1

13-

5

Vcc+

4

OUT

D5060

CHENKO_LL4148_2P

2

3

D

3.9K_1%

0.1uF_10v

1

R5700

2K_1%

2

2

D5059

CHENKO_LL4148_2P

1

1

1

R5701

1

2

2

+V5S

C5591

1

2

R5695

12

100K_5%

C5581

3900pF_16v

ON_LM339DR2G_SOP_14P

1

R5672

330K_5%

U5080-A

2

5

4

1

R5673

3.9K_5%

2

SRSET

5-

3

C

1

B

E

Q5093

2

D_MMST3904

OCP

C84

0.1uF_25v

28

1

1

2

C75

2

4.7uF_25v

26

25

PH

27

24

13

C77

1

2

23

22

19

18

17

7

14

29

1uF_10v

1

R5677

33K_5%

2

CHENMKO_BAT54_3P

1

2

C85

4.7uF_25v

D17

C91

0.1uF_25v

ALARM

0.1uF_16v

1

2

C76

12

0.1uF_16v

100K_5%

C5580

C86

4.7uF_25v

1

2

+V3AL

R5665

6-

1

2

C88

C87

4.7uF_25v

4.7uF_25v

1

2

4

2

3

1

2

Q1

Q65

FAIR_FDMS9620S_MLP_8P

5-,6-,7-,11-,13-,33-,37-,38-,39-,47-,52-,54-

1

+V5AL

2

5-,6-,7-,11-,12-

R5669

12

1M_5%

8

5

+

7

OUT

6

-

U5053-B

4

TI_LMV393IDGKR_SOP_8P

CHANGE by

9

10

1

2VREF

5-,7-,11-,13-

567

Q2

8

1

R5662

10K_5%

2

93.1K_1%

20K_1%

PUMA_CHEN

R65

R5670

1

2

1

2

L30

PCMB0603T_8R2MS

12

1

C193

4.7uF_25v

2

C194

4.7uF_25v

17-Jul-2008

+VBDC

R116

0.01_1%_1W

12

1

2

R5655

0_5%

1

R5654

0_5%

2

C92

0.033uF_16v

2

1

1

2

C196

4.7uF_25v

1

2

C195

4.7uF_25v

5-,6-

1

2

Kevin sense

2

1uF_25v

1uF_25v

C94

C93

1

1

2

INVENTEC

TITLE

ABSOLUT

DC &BATTERY CHARGER

SIZE

CODE

A3

CS

SHEET OF

DOC. NUMBER

Model_No A04

REV

615

Page 6

+VADPBL

5-

20080201

HP’s comment

must use X7R/X5R

can not use Y5V/Z5U

This cap is used for timing

C5596

0.1uF_16v

6-,38-

BATSELB

C5594

1000pF_50v

1

2

CHGCTRL_3

BATSELB#

5-,38-

CHENKO_LL4148_2P

1000pF_50v

6-

6-,38-

BATSELB

D5080

C5593

2

1

R5704

22K_5%

C5595

1000pF_50v

2

1

R5705

22K_5%

3K_5%

R5703

12

1K_5%

RLZ18C

+V3AL

5-,6-,7-,11-,13-,33-,37-,38-,39-,47-,52-,54-

1

5

U5048-A

2

16

TC7PA14FU

2

C5597

0.047uF_10v

1

1

R5706

470K_5%

2

2

1

U3001

S1

2

2

G1

D1

D2

5

G2

S2

2N7002DW

1

2

2

R40

12

D25

1

2

1

1

6

3

4

+VBAT

1

6-

1

R5707

470K_5%

2

3

D

G

S

2

2N7002W

AC_AND_CHG

5-

Q9002

1

S

2

3

4

G

AM4825P_AP

BATSELB#

+V3AL

5-,6-,7-,11-,13-,33-,37-,38-,39-,47-,52-,54-

U5082

5

74HC1G14GV

2

3

Q73

ADP_PRES

TC7W02FU

5-

ALARM

1

R5708

47K_5%

2

5

U5048-B

3

2

Q5134

3

D

5-,6-,13-,30-,38-

1

G

S

2

2N7002W

+VBDC

8

D

7

6

5

4

1

R5709

10K_5%

2

2N7002W

2

5-

5-,6-,13-,30-,38-

U5067-A

1

2

4

TC7PA14FU

5-,6-

Q5013

3

S

D

BATSELB

G

1

TC7W02FU

8

4

ADP_PRES

1

2

8

1

2

U5017-A

4

TC7W08FU

+V3AL

5-,6-,7-,11-,13-,33-,37-,38-,39-,47-,52-,54-

1

R5710

220K_5%

2

6-,38-

+V3AL

5-,6-,7-,11-,13-,33-,37-,38-,39-,47-,52-,54-

U5067-B

8

5

6

7

4

C5598

0.1uF_16v

7

3

5

6

1

2

12

10K_5%

U5017-B

8

TC7W08FU

4

C5599

0.1uF_16v

R5711

3

R5712

1

10K_5%

U19

S1

2

G1

D1

D2

5

G2

S2

2N7002DW

2

6-

DAN202K

Q24

2N7002W

2

S

1

6

3

4

2

5

2N7002DW

D13

3

D

G

1

+VBDC

5-,6-

1

R5713

D_MMST3904

470K_5%

2

2

R5714

10K_5%

1

+VBDC

R5715

470K_5%

R5716

10K_5%

U16

1

S1

G1

6

D1

3

D2

G2

4

S2

+VBATB+VBATA

6-

1

3

2

+V3AL

5-,6-,7-,11-,13-,33-,37-,38-,39-,47-,52-,54-

Q41

3

C

1

B

E

2

D32

21

CHENKO_LL4148_2P

CFET_A#

6-,13-

CFET_A

5-,6-

1

Q31

D_MMST3904

2

C

1

B

E

2

D26

1

21

CHENKO_LL4148_2P

R42

12

100_5%

1

C78

2

0.1uF_25v

PDS540_5A_40V

3

D5061

1

2

3

AM4825P_AP

1

R5718

470K_5%

2

SSM34_3A40V

1

2

3

4

AM4825P_AP

3

1

R5719

2

470K_5%

2

CFET_B#

6-

CFET_B

Q23

2N7002W

1

R5720

1.5M_5%

2

S

D27

3

Q66

D

Q32

S

G

1

1

2

1

D

G

21

G

2

S

D20

UDZW7.5B2

8

7

6

54

8

D

7

6

5

R5721

12

0_5%

8

7

6

5

Q67

1

S

D

2

3

4

G

AM4825P_AP

U44

1

S1

2

G1

6

D1

3

D2

5

G2

4

S2

2N7002DW

Q33

8

1

S

D

7

2

6

3

54

G

AM4825P_AP

U13

1

S1

2

G1

6

D1

3

D2

5

G2

4

S2

2N7002DW

D19

2

CHENKO_LL4148_2P

1

SDA_MAIN

1

R5722

SCL_MAIN

470K_5%

2

5-,6-,7-,11-,13-,33-,37-,38-,39-,47-,52-,54-

1

R5723

4.7K_5%

2

CHENMKO_BAV99

+VBATB

1

R5724

470K_5%

2

SDA_MBAY

1

SCL_MBAY

R5725

4.7K_5%

2

CHENMKO_BAV99

CFET_A

CFET_B

+VBATA

R5727

10K_5%

6-

3838-

+V3AL +V5AL

1

D33

2

CHENMKO_BAV99

6-

5A_200mil

R5726

10K_5%

3838-

THM_TRAVEL#

+V3AL

6-,13-

DAN202K

38-

5-,6-,7-,11-,13-,33-,37-,38-,39-,47-,52-,54-

1

D28

2

CHENMKO_BAV99

1

D21

3

2

6-

PUMA_CHEN

+V3AL

5-,6-,7-,11-,13-,33-,37-,38-,39-,47-,52-,54-

1

1

R5730

10K_5%

2

2

1

3

3

D30

2

CHENMKO_BAV99

13-

OCP_ADJ

5-,6-,7-,11-,13-,33-,37-,38-,39-,47-,52-,54-

100_5%

100_5%

1

2

1

2

1

3

2

D29

R5728

1

3

2

2

220K_5%

17-Jul-2008

5-,6-,7-,11-,13-,33-,37-,38-,39-,47-,52-,54-

+V3AL

100pF_50v

C202

1

2

1

R6048

100K_5%

2

R43 100_5%

12

100_5%

12

R45

5-,6-,7-,11-,12-

1

3

D31

2

R6052

1

294K_1%

THM_MAIN#

R5729

10K_5%

12

12

1

D22

3

2

CHENMKO_BAV99

+V3AL

5-,6-,7-,11-,13-,33-,37-,38-,39-,47-,52-,54-

5

3

U14

1

R5734

1K_5%

ALLTOP_C144M6_108A5_L_8P

C5785

1

2

470pF_50v_OPEN

1

R6050

100K_1%

1

2

1

2

MMBT3906

69.8K_1% R6049

R6051

2

150K_1%

2

38-

+V3AL+V3AL

5-,6-,7-,11-,13-,33-,37-,38-,39-,47-,52-,54-

1

R5731

100K_5%

2

R680

R681

12

R5732

1K_5%

470pF_50v

C5601

1

2

C96

0.1uF_25v

C5602

1

2

0.1uF_16v

4

38-

TI_SN74LVC1G17DCKR_SC70_5P

INVENTEC

TITLE

ABSOLUT

SELECT & BATTERY CONN

CODE

SIZE DOC. NUMBER

A3

CS

SHEETCHANGE by

100pF_50v

100pF_50v

C204

C203

1

1

2

2

CN34

MAIN BATT

1

1

2

2

3

3

4

4

5

5

2

6

6

7

7

8

8

1

C200

0.1uF_25v

2

+V3AL

+V5AL

5-,6-,7-,11-,12-

1

R6053

100K_5%

2

2

E

1

B

Q45

C

Q46

2N7002W

3

3

D

1

G

S

1

2

R6054

220K_5%

2

TRAVEL BATT

SYN_200263MS006G114ZT_6P

1

2

C205

100pF_50v

CN6

1

1

2

2

3

3

4

4

5

5

6

6

1

1

1

2

2

2

C206

100pF_50v

100pF_50v

BATCON

OF

661

5-,6-,7-,11-,13-,33-,37-,38-,39-,47-,52-,54-

C207

REV

A04Model_No

Page 7

+VBATR

5-,8-,9-,10-,12-,19-,30-,31-,38-

PAD5000

POWERPAD_4A

330K_5%

KBC_PW_ON

VCC1_POR#_3

10-,12-,13-,31-,34-,35-,36-,44-,45-,48-,49-,50-,51-,53-,54-

+V3A

38-

11-,38-

PAD2

POWERPAD_2_0610

C428

1

2

1000pF_50v

EMI needed

C5722

1uF_10v

1

2

For power test

3

4

R9058

1

1N4148

D7003

330K_5%

2

21

C422

SLF7055T_4R7N5R1

1

4.7uF_25v

C5364

R9037

1

17.4K_1%

L3032

2

C5648

330uF_4v

+V5AL

G

R516

OPEN

12

5-,6-,7-,11-,12-

1

2

3

D

2N7002W

S

2

12

1

1

2

1

G

Q9006

+VBATP

7-

1

2

3

D

S

2

R517

7.32K_1%

C5678

4.7uF_25v

Q9004

2N7002W

12

51120GND

C9044

0.1uF_25v

Q5103

5

6

7

4

RSMRST#

12

D1

S1_D2

S2

FDS6900AS

R5770

12

4.7_5%

1

2

G1

8

G2

3

7-,34-,38-

+VBATP

7-

R5981

0_5%

12

+V5AL

1

2

1000pF_50v

10

11

12

13

14

15

16

U5023

R521

12K_1%

5-,6-,7-,11-,12-

C5265

10uF_6.3v

9

C383

EN5

EN3

PGOOD2

EN2

VBST2

DRVH2

LL2

DRVL2

2VREF

5-,7-,11-,13-

1

2

51120GND

7

8

VO2

VFB2

COMP2

CS2

VREG3

PGND2

18

17

1

2

6

19

12

51120GND

2

5

4

3

1

VO1

GND

VFB1

VREF2

COMP1

SKIPSEL

TONSEL

PGOOD1

VBST1

DRVH1

DRVL1

CS1

VREG5

VIN

V5FILT

PGND1

23

21

22

20

24

TI_TPS51120_QFN_32P

1

R522

7.87K_1%

2

C4231

0.1uF_16v

2

R54

0_5%

EN1

LL1

1

2

33

32

31

30

29

28

27

26

25

1

R523

10_5%

2

C426

1uF_6.3v

R469

12

7.32K_1%

51120GND

12

R473

0_5%

1

C5118

4.7uF_25v

2

R468

12

30K_1%

C382

5-,8-,9-,12-,13-,34-,38-,43-,50-,53-

7-,34-,38-

RSMRST#

R5656

1

4.7_5%

OPEN

12

R471

2

1

PCSPKC#_3

0_5%

FDS8884

2VREF

5-,7-,11-,13-

R472

1

2

0_5%

0.1uF_25vC5062

2

12

+V3AL

5-,6-,11-,13-,33-,37-,38-,39-,47-,52-,54-

1

C5684

10uF_6.3v

2

SLP_S3#_3R

Q5090

G

4S123

G

4

8765

D

C5085

4.7uF_25v

8765

D

Q5020

FDS6690AS

S

123

+VBATP

7-

C5418

1

1

2

2

4.7uF_25v

SLF10155T_4R7N6R2

L609

12

C5566

220uF_6.3v_OSCON

8-,9-,10-,11-,12-,13-,31-,36-,48-,52-

+V5A

MAX5V

PAD3

6A_200mil

POWERPAD_2_0610

1

C5569

1

1uF_10v

2

2

CHANGE by

INVENTEC

TITLE

ABSOLUT

SYSTEM POWER(3V/5V)

SIZE

CODE

CS

SHEET

DOC. NUMBER

761

17-Jul-2008PUMA_CHEN

A3

REV

A04Model_No

OF

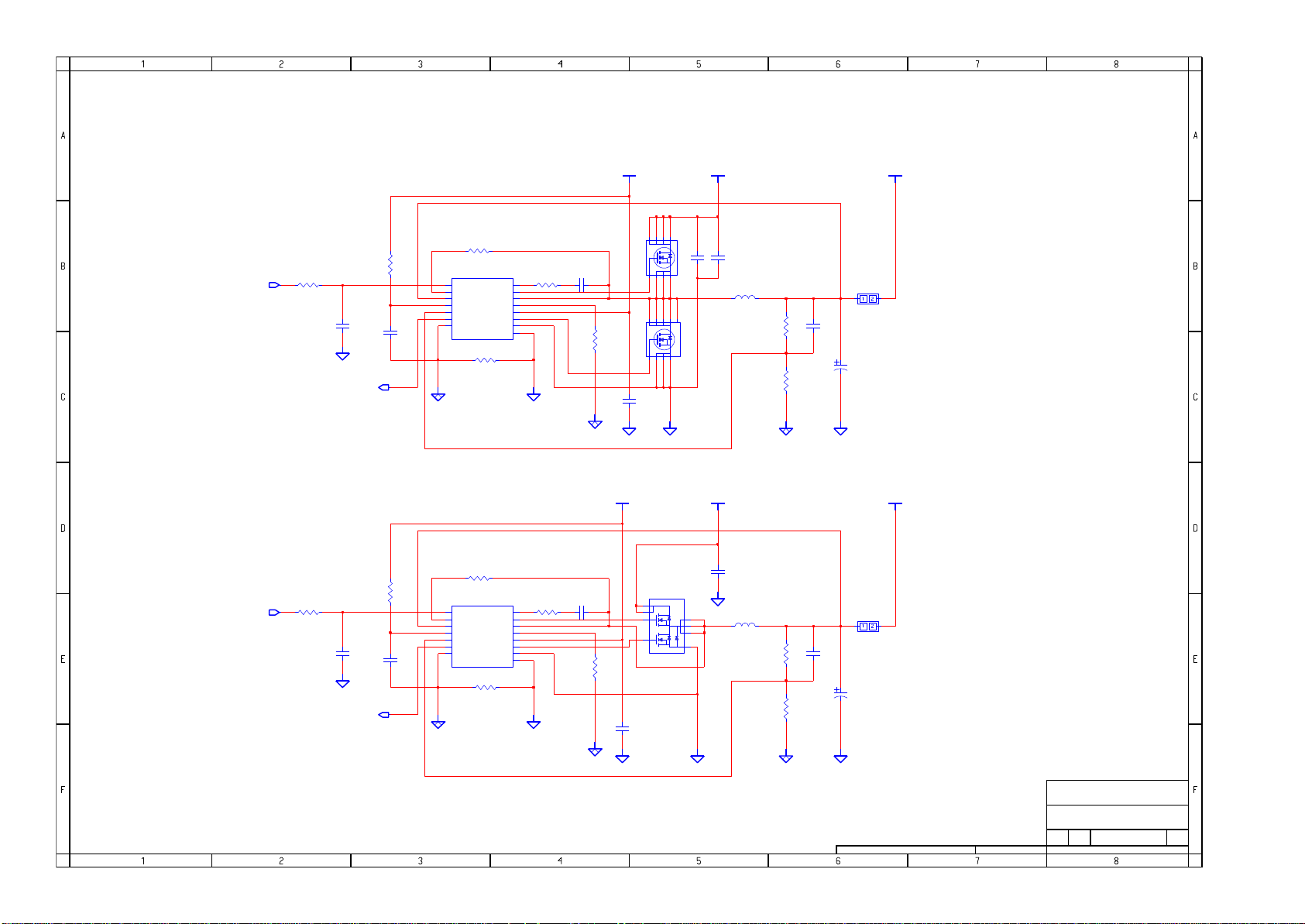

Page 8

R5341

12

20K_1%

C387

12

OPEN

R1

12

51K_1%

R2

12

51K_1%

R5688

12

20K_1%

C385

2

1

OPEN

10-,15-,16-,17-,18-,20-,22-,25-,33-,36-

+VCCP

POWERPAD_2_0610

330uF_2v_15mR_Panasonic

PAD5

C5244

PCMB104E_2R2MS

1

2

+VBATR

5-,7-,8-,9-,10-,12-,19-,30-,31-,38-

1

C5558

2

4.7uF_25v

L12

12

SSM34_3A40V_OPEN

1

2

D5071

C5559

4.7uF_25v

Q5141

FDS8884

Q5137

FDS6676AS

1

2

VCCP_PG

5-,7-,9-,12-,13-,34-,38-,43-,50-,53-

SLP_S3#_3R

8

5

76

D

G

765

3

C6

4

G

4

S

123

8

D

S

12

51124GND

13-

PCSPKC#_3

1

R864

0_5%

2

0.1uF_16v

12

12

R6 4.7_5%

TI_TPS51124RGER_QFN_24P

1

OPEN

51124GND

C13

4.7uF_6.3v

11-,12-,34-,38-

PM_SLP_M#

G

41S23

G

4

8765

D

123

Q5142

FDS8884

8D765

4.7uF_25v

Q5140

FDS6676AS

S

C5561

1

2

+VBATR

5-,7-,8-,9-,10-,12-,19-,30-,31-,38-

C5560

1

2

4.7uF_25v

L13

12

PCMB104E_2R2MS

D5056

1

SSM34_3A40V_OPEN

2

+V1.05M

PAD6

3

4

POWERPAD_4A

1

C5604

330uF_2v_15mR_Panasonic

2

14-,20-,21-,24-,25-

R700

2

1

R13

2

GND

V5IN

3

16

2

VO1

VFB1

PGOOD1

TRIP1

PGND1

17

1

R5789

8.87K_1%

2

1

VBST1

DRVH1

DRVL1

18

U5

GND

EN1

LL1

25

24

23

22

21

20

19

7-,9-,10-,11-,12-,13-,31-,36-,48-,52-

1

2

4

5

6

VO2

VFB2

2

PGND2

13

51124GND

TONSEL

TRIP2

V5FILT

14

1

R5650

8.87K_1%

2

15

7

PGOOD2

8

EN2

9

VBST2

10

DRVH2

11

LL2

12

DRVL2

R11

1

0_5%

1

C633

OPEN

2

13-

R7

12

4.7_5%

R12

12

10_5%

C12

1uF_6.3v

0_5%

V1.05M_PG

C7

12

0.1uF_16v

+V5A

1

2

CHANGE by

CHANGE by

CHANGE by

PUMA_CHEN

INVENTEC

INVENTEC

INVENTEC

TITLE

TITLE

TITLE

ABSOLUT

ABSOLUT

ABSOLUT

ABSOLUT

SYSTEM POWER(+V1.05M/+VCCP)

SYSTEM POWER(+V1.05M/+VCCP)

SYSTEM POWER(+V1.05M/+VCCP)

SYSTEM POWER(+V1.05M/+VCCP)

SIZE

CODE

SIZE

A3

A3

A3

17-Jul-2008PUMA_CHEN

17-Jul-2008PUMA_CHEN

17-Jul-2008PUMA_CHEN

A3

CODE

CODESIZE

CS

CS

CS

CS

SHEET

SHEET

SHEET

DOC. NUMBER REV

DOC. NUMBEROFREV

DOC. NUMBER

861

861

861

861

REV

A04Model_No

A04Model_No

A04Model_No

A04Model_No

OF

OF

Page 9

SLP_S4#_3R

11-,34-

R5349

1

0_5%

+V5A

7-,8-,9-,10-,11-,12-,13-,31-,36-,48-,52-

R5344

1

R66

10_5%

C5347

OPEN

V1.8_PG

1

2

2

C5134

1uF_6.3v

13-

2

1

2

12

232K_1%

U5058

1

EN_PSV

2

TON

3

VOUT

4

V5FILT

5

VFB

6

PGOOD

7

GND

TI_TPS51117_QFN_14P

51117GND

VBST

DRVH

LL

TRIP

V5DRV

DRVL

PGND

TML

R67

12

0_5%

G

C5616

R77

2

1

14

13

12

11

10

9

8

15

4.7_5%

12

0.1uF_16v

1

2

R5347

6.04K_1%

41

G

4

1

C5350

2

1uF_6.3v

51117GND

8765

23

8D765

123

Q5027

FDS8884

D

11

2

S

9

S

Q5024

FDMS8660S

+VBATR

5-,7-,8-,9-,10-,12-,19-,30-,31-,38-

C5620

4.7uF_25v

C5623

4.7uF_25v

2

L3007

12

PCMB104E_2R2MS

R5350

43.2K_1%

R68

30.1K_1%

51117GND

1

C5351

1

OPEN

2

2

1

1

2

2

+V1.8

11-,12-,20-,24-,25-,27-,28-

PAD4

POWERPAD_2_0610

C5588

330uF_2v_15mR_Panasonic

PCSPKC#_3

5-,7-,8-,12-,13-,34-,38-,43-,50-,53-

SLP_S3#_3R

R5591

12

0_5%

1

C5507

OPEN

2

V1.5S_PG

1

2

1

R83

10_5%

2

C5702

1uF_6.3v

13-

R5590

12

232K_1%

U32

1

EN_PSV

2

TON

3

VOUT

4

V5FILT

5

VFB

6

PGOOD

7

GND

TI_TPS51117_QFN_14P

51117GND

VBST

DRVH

LL

TRIP

V5DRV

DRVL

PGND

TML

R86

12

0_5%

14

13

12

11

10

9

8

15

C5575

R82

12

4.7_5%

0.1uF_16v

R5595

10.5K_1%

12

51117GND

+V5A

7-,8-,9-,10-,11-,12-,13-,31-,36-,48-,52-

1

2

8

3

1

2

1

2

C5511

1uF_6.3v

FDS6900AS

Q5130

D1

G1

G2

5

S1_D2

6

7

4

S2

+VBATR

5-,7-,8-,9-,10-,12-,19-,30-,31-,38-

C5574

4.7uF_25v

1

2

L14

12

PCMC063T_2R2MN

30.9K_1%

30.1K_1%

R5599

R87

51117GND

+V1.5S

12-,17-,25-,30-,36-,49-,50-

PAD7

1

2

C5509

OPEN

POWERPAD_2_0610

1

C114

220uF_2.5v

2

CHANGE by

PUMA_CHEN

INVENTEC

INVENTEC

TITLE

TITLE

ABSOLUT

ABSOLUT

SYSTEM POWER(+V1.5/+V1.8)

SYSTEM POWER(+V1.5/+V1.8)

CODE

SIZE

SIZE

A3

A3

CS

CS

SHEET

17-Jul-2008PUMA_CHEN

961

961

REVDOC. NUMBERDOC. NUMBERCODE

REV

A04Model_No

A04Model_No

OFSHEETCHANGE by OF

1

2

1

2

Page 10

R302

1

10K_5%

R5229

R5230

17171717171717-

R9070

0_5%

12

0_5%_OPEN

R5227

0.012uF_16v

12

470pF_50v

20-,34-

C5271

12

220pF_25v

1

R5231

1.65K_1%

2

17-

17-

+V3S

5-,10-,12-,13-,14-,15-,18-,19-,20-,25-,26-,30-,31-,32-,33-,34-,35-,36-,37-,38-,40-,41-,46-,47-,48-,50-,51-,52-,54-

2

34-

VR_PWRGD

12

0_5%

12

0_5%

0.0047uF_50v

12

R5226

0_5%

12

CPU_SINGNAL_GROUND

12

C5272

12

R5228

12

499_1%

1000pF_50v

1

2

C180

1

EN

2

PWRGD

3

PGDELAY

4

CLKEN

5

FBRYN

6

FB

7

COMP

8

SS

9

STSET

10

DPRSLP

C5273

1

R5234

*

2

63.4K_1%

3ph=63.4K

CPU_SINGNAL_GROUND

*

R5233

140K_1%

3ph=150K

CPU_SINGNAL_GROUND

41

40

38

37

TML

VID0

VID139VID2

VID336VID4

U41

ADI_ADP3207_LFCSP_40P

VRPM

ILIMIT

RRPM

RT

12

11

13

14

1

2

1

*

2

3ph=150K

VCCSENSE

VSSSENSE

+VBATR

5-,7-,8-,9-,10-,12-,19-,30-,31-,38-

R5232

12

1K_5%

C5275

1000pF_50v

1

2

CPU_SINGNAL_GROUND

+V3A

7-,12-,13-,31-,34-,35-,36-,44-,45-,48-,49-,50-,51-,53-,54-

12

47K_5%

R301

Q301

3

D

G

1

S

2

SSM3K7002F

16-

PSI#

20-,34-,38-

16-,20-,33-

H_VID6

H_VID5

H_VID4

H_VID3

H_VID2

H_VID1

H_VID0

14-,34-

5-,10-,13-,30-,38-

H_DPRSTP#

5-,10-,12-,13-,14-,15-,18-,19-,20-,25-,26-,30-,31-,32-,33-,34-,35-,36-,37-,38-,40-,41-,46-,47-,48-,50-,51-,52-,54-

+V3S

1

R30

1K_5%_OPEN

2

PWR_GOOD_3

PM_PWROK

CLK_PWRGD

C5269

CPU_SINGNAL_GROUND

PM_DPRSLPVR

R31

12

33K_1%

C5268

1

2

18pF_50v

R5224

12

261K_1%

C5270

330pF_50v

C52

1

1000pF_50v

2

CPU_SINGNAL_GROUND

VID535VID6

LLSET

RAMPADJ

16

15

1

R5236

324K_1%

2

1

R5235

150K_1%

2

1

2

34

17

CPU_SINGNAL_GROUND

32

33

31

PSI

VCC

DPRSTP

TTSENSE

VRTT

DCM

OD

PWM1

PWM2

PWM3

SW1

SW2

SW3

GND

CSCOMP

CSREF

CSSUM

20

19

18

CPU_SINGNAL_GROUND

C5277

1

1000pF_50v

2

C5276

1000pF_50v

1

2

30

29

28

27

26

25

24

23

22

21

C181

1uF_10v

*

3ph=OPEN

R5240

R5241

R5242

0_5%

3ph=0ohm

C5280

1

1000pF_50v

2

R108

12

10_5%

R34

12

0_5%

1

R5239

OPEN

2

1

12

1

12

*

NTC of 220K

R101

12

220K_5%

R28

12

73.2K_1%

R5245

12

140K_1%

R33

12

110K_1%

R32

12

110K_1%

R29

*

12

110K_1%

+V5A

PWR_GOOD_3

7-,8-,9-,10-,11-,12-,13-,31-,36-,48-,52-

C182

1

1uF_10v

2

20070926

+VCCP

8-,15-,16-,17-,18-,20-,22-,25-,33-,36-

1

R6089

68_5%

2

CPU_PROCHOT#

15-

3

D

Q5144

G

2N7002W

S

2

0_5%

2

0_5%

0_5%

R176

5-,10-,13-,30-,38-

4.7uF_6.3v

12

+V5A

7-,8-,9-,10-,11-,12-,13-,31-,36-,48-,52-

C51

1

2

4.7uF_6.3v

BAT54C_30V_0.2A

U40

1

R5251

12

0_5%

IN

2

SD

3

DRVLSD

4

CROWBAR

5

VCC

ADI_ADP3419_RM_MSOP_10P

C5760

4.7uF_6.3v

BAT54C_30V_0.2A

ADI_ADP3419_RM_MSOP_10P

+V5A

7-,8-,9-,10-,11-,12-,13-,31-,36-,48-,52-

C4

BAT54C_30V_0.2A

ADI_ADP3419_RM_MSOP_10P

1

2

U4

1

2

3

4

5

IN

SD

DRVLSD

CROWBAR

VCC

1

3

2

D5

4.7_5%

10

BST

9

DRVH

8

SW

7

GND

6

DRVL

3ph install

1

3

2

D10

10

BST

9

DRVH

8

SW

7

GND

6

DRVL

+V5A

7-,8-,9-,10-,11-,12-,13-,31-,36-,48-,52-

1

1

2

D5051

3

2

4.7_5%

U34

1

IN

BST

2

SD

DRVH

3

DRVLSD

CROWBAR

VCC

R5

1

2

GND

DRVL

C5285

1

2

0.22uF_16v

SW

4

5

1

R107

4.7_5%

2

1

2

10

9

8

7

6

C5028

4.7uF_25v

R88

1

2

1

2

+VBATR

1

2

C5286

0.22uF_16v

1

C5288

0.22uF_16v

2

C5027

4.7uF_25v

1

2

FDMS8660S

5-,7-,8-,9-,10-,12-,19-,30-,31-,38-

C5547

100uF_25v

1

2

C47

4.7uF_25v

1

2

C50

4.7uF_25v

FDMS8660S

C5761

4.7uF_25v

4.7uF_25v

1

1

2

2

C5026

4.7uF_25v

1

1

2

2

C5025

0.01uF_50v

8

765

D

G

Q78

4

1S2

3

Q60

C9

Q51

FDMS8660S

G

9

G

CHANGE by

C179

4.7uF_25v

1

1

2

2

0.01uF_50v

765

G

4

3

C3

4.7uF_25v

1

1

2

2

0.01uF_50v

G

9

567

8

Q5076

432

1

8

765

9

D

4

1S2

3

Q77

FDMS8660S_OPEN

9

G

C173

4321

8

9

D

G

1S2

4

3

G

C116

43

9

8D7654

G

S

123

SI7686DP_T1_E3

1

R4

20_5%

2

1

C5

1000pF_50v

2

LAYOUT NOTES: C1779 C502 C503 PIN2 CONNECT TO Q14 , Q18 GND

5678

Q15

SI7686DP_T1_E3

8

765

9

D

1S2

Q61

FDMS8660S_OPEN

C1780 C532 C531 PIN2 CONNECT TO Q16 , Q20 GND

+VCC_CORE

17-

L23

ETQP4LR36WFC_PANASONIC

1

R106

20_5%

2

1

C174

1000pF_50v

2

12

1

R5858

10_5%

2

56789

Q1

SI7686DP_T1_E3

21

L22

7654

8

9

D

S

123

Q52

FDMS8660S_OPEN

ETQP4LR36WFC_PANASONIC

ETQP4LR36WFC_PANASONIC

1

R10

20_5%

2

C10

1

1000pF_50v

2

L15

12

12

1

R5859

10_5%

2

1

R5860

10_5%

2

INVENTEC

TITLE

ABSOLUT

CPU POWER(VCC_CORE)

CODE

CS

SHEET

DOC. NUMBER

10 61

SIZE

17-Jul-2008PUMA_CHEN

A3

REV

A04Model_No

OF

Page 11

SLP_S4#_3R

PM_SLP_M#

SLP_S4#_3R

9-,12-,20-,24-,25-,27-,28-

9-,34-

8-,12-,34-,38-

9-,34-

R6045

OPEN

+V1.8 +V0.9

1

2

+V5A

7-,8-,9-,10-,12-,13-,31-,36-,48-,52-

C132

10uF_6.3v

1

2

C129

1uF_6.3v

R181

0_5%

R5005

1

0_5%

1

1

2

2

2

10 2

9

7

6

GMT_G2997F6U_MSOP10_10P

1

C5136

0.1uF_10v

2

U38

TML11VDDQSNS

VIN

VLDOIN

S5

GND8PGND

VTTSNS

S3

VTTREF

1

3

VTT

4

5

1

2

NOTE: DDR2 REGULATOR

20-,27-,28-

M_VREF

13-,29-

C136

10uF_6.3v

C9018

1

2

10uF_6.3v

+V3AL

5-,6-,7-,11-,13-,33-,37-,38-,39-,47-,52-,54-

23.7K_1%

R9048

51.1K_1%

R9050

+V5AL

100K_5%

R9052

12

0.1uF_16v

C9045

12

12

5-,6-,7-,11-,12-

12

1

2200pF_50v

2

1M_5%

SSM3K7002F

R9049

12

23.7K_1%

C9046

+V5AL

R9051

Q9005

D

G

1

S

5-,6-,7-,11-,12-

12

3

2

2VREF

5-,7-,13-

R9047

12

1M_5%

+V5AL

5-,6-,7-,11-,12-

8

3

+

1

OUT

2

-

ON_LM393DR2G_SOP_8P

4

U9004-A

+V3AL

5-,6-,7-,11-,13-,33-,37-,38-,39-,47-,52-,54-

12

10K_5%

R9046

7-,38-

5

6

VCC1_POR#_3

+V5AL

5-,6-,7-,11-,12-

8

+

7

OUT

-

ON_LM393DR2G_SOP_8P

4

U9004-B

CHANGE by

INVENTEC

TITLE

ABSOLUT

DDR TERMINATION VOLTAGE

CODE

CS

DOC. NUMBER

OFSHEET

11 61

REV

A04Model_No

SIZE

17-Jul-2008PUMA_CHEN

A3

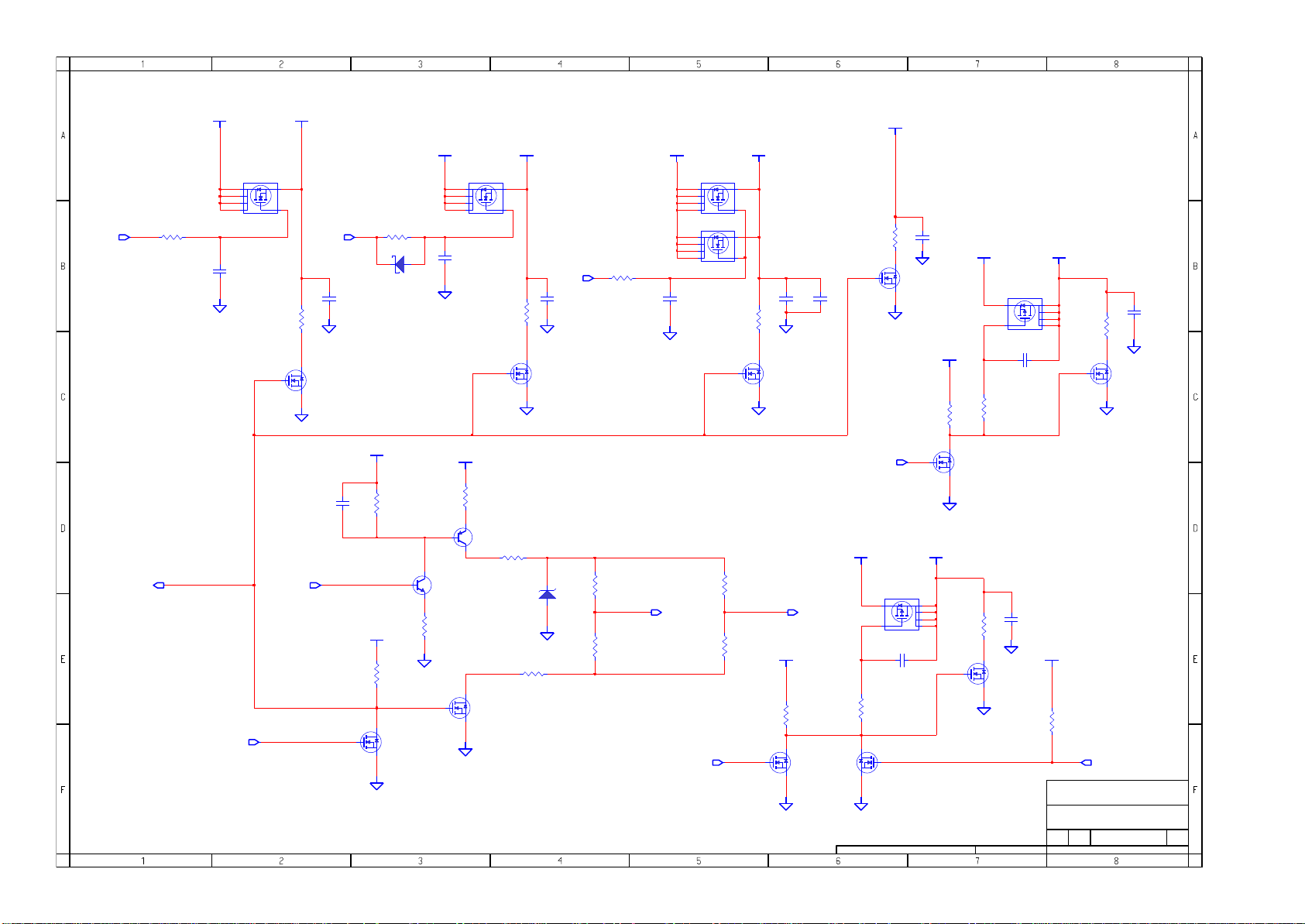

Page 12

7-,8-,9-,10-,11-,13-,31-,36-,48-,52-

R5263

105K_1%

12

12-

SLP_S3_3R

32-

+V5A

Q5110

6

D

5

2

1

G

FDC655BN

C5501

1

2

0.01uF_16v

5-,7-,8-,9-,12-,13-,34-,38-,43-,50-,53-

SLP_S3#_3R

+V5S

5-,13-,19-,30-,31-,32-,34-,36-,38-,39-,40-,41-,42-,43-,47-,48-,50-,53-

7-,10-,12-,13-,31-,34-,35-,36-,44-,45-,48-,49-,50-,51-,53-,54-

4

S

3

12-

GATE_3SGATE_5S

CHENMKO_BAT54_3P

1

C5570

10uF_6.3v

2

1

R69

100_5%

2

Q5098

3

D

1

G

S

2

SSM3K7002F

+VBATR

1

C5304

0.033uF_16v_OPEN

SLP_S3#_3R

5-,7-,8-,9-,12-,13-,34-,38-,43-,50-,53-

7-,10-,12-,13-,31-,34-,35-,36-,44-,45-,48-,49-,50-,51-,53-,54-

2

PCSPKC#_3

SSM3K7002F

+V3A

Q29

D

G

1

S

R5268

120K_1%

12

D5083

13

5-,7-,8-,9-,10-,19-,30-,31-,38-

1

R5265

47K_5%

2

3

C

1

B

E

Q9001

2

1

2

1

R5266

100K_5%

2

SSM3K7002F

3

2

5-,10-,13-,14-,15-,18-,19-,20-,25-,26-,30-,31-,32-,33-,34-,35-,36-,37-,38-,40-,41-,46-,47-,48-,50-,51-,52-,54-

Q5105

D

G

SSM3K7002F

R5269

2.7K_5%

Q22

MMBT3906

+V3S

4

S

R80

47_5%

Q5106

D

G

1

S

R5270

12

0_5%

R5271

12

1K_5%

9-,11-,20-,24-,25-,27-,28-

R5356

120K_1%

12

12-

GATE_5S

1

C5622

1

2

10uF_6.3v

2

3

2

1

R5272

1

2

D18

RLZ18C

0_5%

2

1

R5273

0_5%

2

+V3A

6

5

2

13

FDC655BN

C5697

1

2

0.01uF_16v

+VBATR

5-,7-,8-,9-,10-,19-,30-,31-,38-

E

1

B

C

MMBT3904

R5267

130K_1%

Q30

D

G

1

S

1

2

2

3

3

2

1

2

12-

+V1.8

Q7

6

D

5

2

1

G

FDC655BN

Q8

6

D

5

2

13

G

FDC655BN

C19

0.047uF_16v_OPEN

8-,11-,12-,34-,38-

PM_SLP_M#

4

S

3

4

S

R19

100_5%

G

1

SSM3K7002F

1

R5275

0_5%

2

1

R5276

0_5%

2

SSM3K7002F

+V1.8S

Q9

13-,30-,52-

1

2

3

D

S

2

1

1

2

12-

+V5AL

5-,6-,7-,11-,12-

Q3

G

10uF_6.3v

1

2

3

D

S

2

C20

GATE_3SGATE_5S

R476

47K_5%

+V1.5S

9-,17-,25-,30-,36-,49-,50-

1

Q12

1

G

1

G

4

S

FDC638P

C390

2

3

D

S

2

SSM3K7002F

Q5

G

12

OPEN

1

2

R391

47K_5%

+V3M_WOL

1

D

2

5

63

C9095

10uF_6.3v

+V5AL

5-,6-,7-,11-,12-

Q13

D

1

G

S

34-,36-,44-,45-

SSM3K7002F

7-,10-,12-,13-,31-,34-,35-,36-,44-,45-,48-,49-,50-,51-,53-,54-

+V3A

Q10

4

D

S

3

G

FDC638P

C329

12

OPEN

1

1

R392

330K_5%

2

2

3

2

C16

1

R14

47_5%

1

2

10uF_6.3v

2

Q2

3

D

1

G

S

2

+V3M

13-,14-,20-,27-,28-,34-

1

2

5

6

R23

47_5%

SSM3K7002F

7-,10-,12-,13-,31-,34-,35-,36-,44-,45-,48-,49-,50-,51-,53-,54-

+V3A

1

R18

100K_5%

2

34-,38-

R22

100_5%

SSM3K7002F

C9106

1

2

OPEN

8-,11-,12-,34-,38-

PM_SLP_M#

7-,10-,12-,13-,31-,34-,35-,36-,44-,45-,48-,49-,50-,51-,53-,54-

+V3A

1

R475

2

330K_5%

Q4

3

D

S

2

SSM3K7002F

INVENTEC

TITLE

ABSOLUT

POWER(SLEEP)

SIZE

A3

CS

CHANGE by OF

PUMA_CHEN 17-Jul-2008

SHEET

C36

1

1

2

2

Q11

3

D

G

1

S

2

LAN_WOL_EN

DOC. NUMBER

Model_No A04

10uF_6.3v

REVCODE

6112

Page 13

VCCP_PG

V1.5S_PG

5-,7-,8-,9-,12-,13-,34-,38-,43-,50-,53-

SLP_S3#_3R

M_PWROK

12

13-,20-,34-

CHENKO_LL4148_2P

+V1.8S

12-,30-,52-

5-,10-,12-,13-,14-,15-,18-,19-,20-,25-,26-,30-,31-,32-,33-,34-,35-,36-,37-,38-,40-,41-,46-,47-,48-,50-,51-,52-,54-

5-,12-,13-,19-,30-,31-,32-,34-,36-,38-,39-,40-,41-,42-,43-,47-,48-,50-,53-

+V0.9

11-,29-

+V3M

12-,14-,20-,27-,28-,34-

+V3S

5-,10-,12-,13-,14-,15-,18-,19-,20-,25-,26-,30-,31-,32-,33-,34-,35-,36-,37-,38-,40-,41-,46-,47-,48-,50-,51-,52-,54-

1

R5367

71.5K_1%

2

OCP_OC

1

R5368

21K_1%

2

1

R5366

3.48K_1%

2

V1.8_PG

V1.05M_PG

C5362

1uF_6.3v

R5358

12

5-

47K_5%

+V3S

+V5S

9-

1

2

R5359

12

470K_5%

9-

R857

1K_5%

D7

21

8-

R6068

12

43.2K_1%

R5982

12

158K_1%

C5363

1

2

0.1uF_16v

10K_5%

R5601

12

10K_5%

D8

21

CHENKO_LL4148_2P

10K_5%

2

1

R6030

R8

12

130K_1%

R9

12

237K_1%

R3

12

365K_1%

R5985 10K_5%

12

10K_5%R5983

12

1

C277

1

2

1000pF_50v

2

5-,12-,13-,19-,30-,31-,32-,34-,36-,38-,39-,40-,41-,42-,43-,47-,48-,50-,53-

+V5S

R5365

12

10K_5%

ON_LM339DR2G_SOP_14P

R5364

12

21K_1%

R294

12

8-

R289

12

20K_5%

1

R293

60.4K_1%

2

C299

1000pF_50v

12

R285

20K_5%

R254

499K_1%

R5361

12

1M_5%

3

U5054-B

7

+

1

OUT

6

12

R5363

12

1M_5%

3

U5054-A

5

+

2

OUT

4

-

ON_LM339DR2G_SOP_14P

12

C278

1000pF_50v

1

2

5-,10-,12-,13-,14-,15-,18-,19-,20-,25-,26-,30-,31-,32-,33-,34-,35-,36-,37-,38-,40-,41-,46-,47-,48-,50-,51-,52-,54-

+V3S

2VREF

R256

12

30.1K_1%

1

2

1

R5989

44.2K_1%

2

7-,8-,9-,10-,11-,12-,13-,31-,36-,48-,52-

1

R5360

10K_5%

2

38-

ADP_PS0

OLD_DOCK_DET

1

R5362

10K_5%

2

38-

220K_5%

ADP_PS1

110K_1%

R6056

R6057

5-,7-,11-

R290

12

1M_5%

+V5A

7-,8-,9-,10-,11-,12-,13-,31-,36-,48-,52-

U6-A

8

3

+

1

OUT

2

-

ON_LM393DR2G_SOP_8P

4

R287

12

1M_5%

+V5A

U6-B

8

5

+

7

OUT

6

-

ON_LM393DR2G_SOP_8P

4

LIMIT_SIGNAL

5-

13-

R6058

3

1

511K_1%

1

2

3

2

D

1

G

2N7002W

S

1

2

2

1

2

U5043-3

BSS138

2

G

D

Q37

Q38

C279

0.1uF_16v

5-,13-,53-

R5369

47K_5%

S

1

1

ADP_PRES

1

2

+V3A

7-,10-,12-,31-,34-,35-,36-,44-,45-,48-,49-,50-,51-,53-,54-

1

2

5-,53-

+VADP

Q21

MMBT3906

2

E

1

1

2

1

R5370

200K_5%

2

53-

ACOCP_EN#

CFET_A

150K_5%

2

BSS138

G

6-

D

S

OCP_ADJ

3

Q39

5-,6-,30-,38-

R257

10K_5%

5-,10-,30-,38-

R255

3.3K_5%

13-,20-,34-

1

R5371

210K_1%

2

D12

1

2

CHENKO_LL4148_2P

3

C

B

13-

6-

1

R6059

2

3

D

1

G

2N7002W

S

2

PWR_GOOD_3

M_PWROK

1

R5372

69.8K_1%

2

OLD_DOCK_DET

1

R5373

14.7K_1%

2

Q40

R9040

12

100_5%

R5375

12

1M_5%

+VADP

+VADP

5-,13-,53-

1

R5376

45.3K_1%

2

1

R6055

20K_1%

2

5-,13-,53-

1

R5377

51.1K_1%

2

1

R5378

10K_1%

2

+VADP

5-,13-,53-

1

R9038

34K_1%

2

1

R9039

20K_1%

2

+VADP

5-,13-,53-

1

R9042

30.1K_1%

2

1

R9043

10K_1%

2

R9044

12

1M_5%

ON_LM393DR2G_SOP_8P

R5379

12

1M_5%

ON_LM393DR2G_SOP_8P

5-

VBIAS

R9041

12

1M_5%

8

U9003-A

3

+

1

OUT

2

-

ON_LM393DR2G_SOP_8P

4

8

U9003-B

5

+

OUT

6

-

ON_LM393DR2G_SOP_8P

4

8

U12-A

3

+

1

OUT

2

4

1

7

2

CHENKO_LL4148_2P

8

U12-B

5

+

OUT

6

4

+V3AL

5-,6-,7-,11-,13-,33-,37-,38-,39-,47-,52-,54-

1

R9045

10K_5%

1

R5381

10K_5%

2

38-

+VADP

21

ADP_EN#

2

ADP_ID

5-,13-,53-

1

2

1

2

R5382

220K_5%

R5383

220K_5%

7

5-,6-,7-,11-,13-,33-,37-,38-,39-,47-,52-,54-

R5380

47K_5%

D16

5-

17-Jul-2008PUMA_CHEN

38-

ADP_ID2

+V3AL

5-,7-,8-,9-,12-,13-,34-,38-,43-,50-,53-

1

R5384

47K_5%

2

3

D

Q20

G

1

2N7002W

S

2

+VADP

5-,13-,53-

R6155

12

1_5%

1

C74

1uF_25v

2

PCSPKC#_3

SLP_S3#_3R

5-

3

R5385

12

100K_5%

C

1

B

E

MMBT3904

2

INVENTEC

TITLE

ABSOLUT

POWER(SEQUENCE)

SIZE CODE

A3

DOC. NUMBER

CS

SHEETCHANGE by OF

13 61

Q19

38-

BATCAL#

ADP_EN

REV

A04Model_No

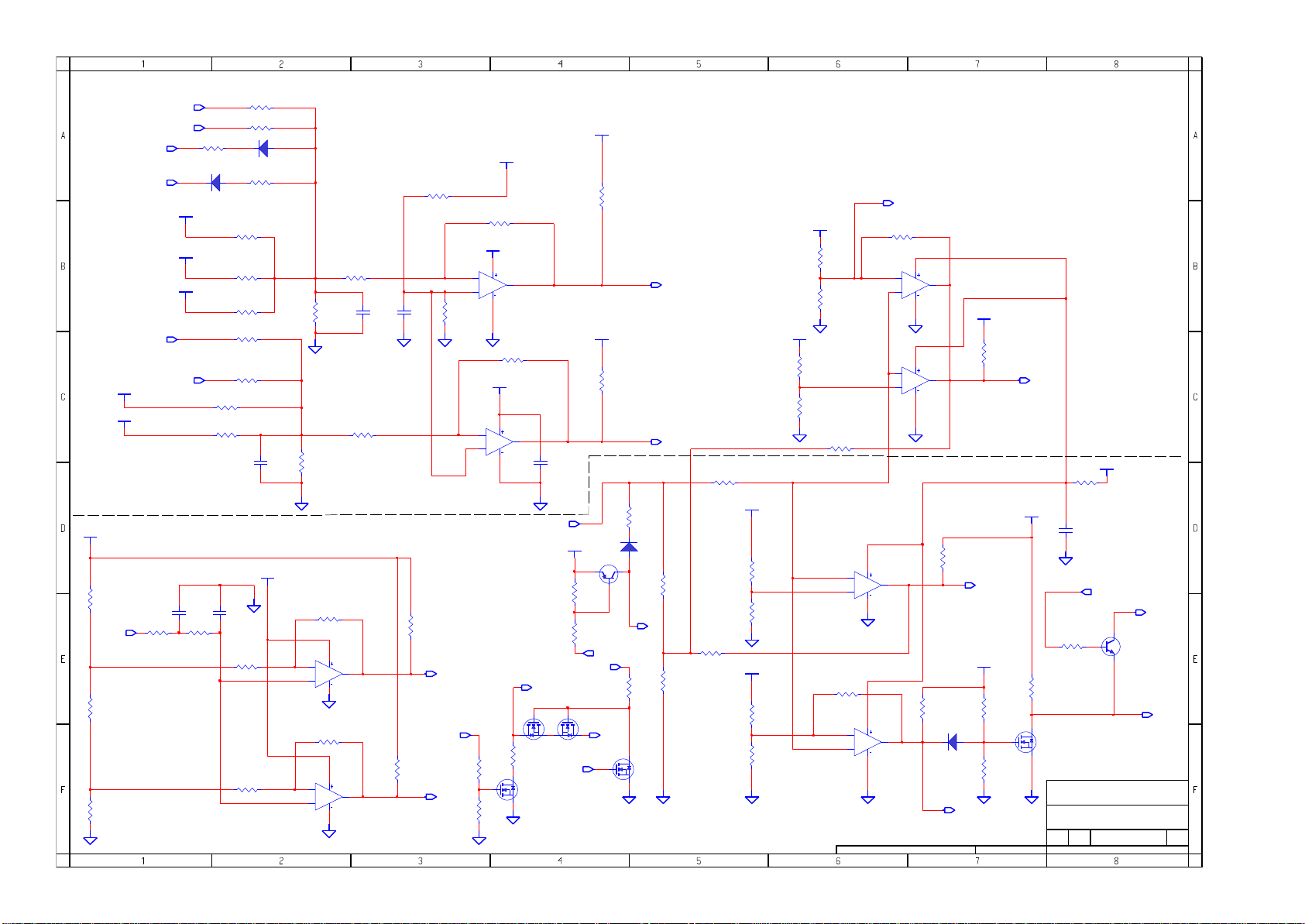

Page 14

+V1.05M

8-,20-,21-,24-,25-

L16

BLM18AG471SN1D

1

2

+V3M

12-,13-,14-,20-,27-,28-,34-

R5809

2

CPU_BSEL1

CPU_BSEL2

CLK_3S_REF

X6

30PPM

10-,34-

2

1

2

1

10K_5%

R5810

12

10K_5%

R5811

2

1

10K_5%

R5812

12

10K_5%

16-,20-

16-,20-

14-

C5309

33pF_50v

CLKREQ#_EXP

CLKREQ_MINI2#

CLKREQ_MINI1#

CPPE#

CLK_PWRGD

C5307

33pF_50v

14-,50-

14-,49-

14-

14-,53-

14.31818MHZ

1

1

2

Please place close to CLKGEN within 500mils

*CLKREQ# pin controls SRC Table.

Byte5:bit7=0, disable CR#_A; 1, enable CR#_A

CR#_A

Byte5: bit6 =0(PWD)

SRC0

Byte5:bit4=0(PWD), disable CR#_4 ; 1, enable CR#_4

CR#_4

SRC4

Byte5: bit6 =1

Layout note: All decoupling 0.1uF disperse closed to pin

1

2

C5762

10uF_6.3v

1

0.1uF_16v

2

C5311

1

2

C5313

0.1uF_16v

1

2

CPU_BSEL0

C5312

1

CLK_R3S_ICH48

2

22pF_50v

R89

0_5%

12

12

R6002 10K_5%

12

10K_5%

R5279

3446513840-

C5717

5.6pF_50v

ICH_3M_SMCLK

ICH_3M_SMDATA

1

1

2

2

5-,10-,12-,13-,14-,15-,18-,19-,20-,25-,26-,30-,31-,32-,33-,34-,35-,36-,37-,38-,40-,41-,46-,47-,48-,50-,51-,52-,54-

27-,28-,3427-,28-,34-

CLKREQ_R_MCH#

CLKREQ_R_SATA#

R5567

1

0_5%

CLK_R3S_ICH14

CLK_R3S_CBPCI

CLK_R3S_KBPCI

CLK_R3S_SIOPCI

2

CLK_R3S_TPM

Byte5:bit5=0(PWD), disable CR#_3 ; 1, enable CR#_3

CR#_3

SRC2

SRC3

Byte5:bit3=0(PWD), disable CR#_6 ; 1, enable CR#_6

CR#_6

SRC6

C5314

1

0.1uF_16v

2

16-,20-

12

R5880

12

R5288

R5289

1

C5316

C5315

5.6pF_50v

5.6pF_50v

2

CLKREQ#_EXP

C5317

0.1uF_16v

34-

1

2

R6001

12

2.2K_5%

33_5%

22_1%

22_1%12

C5318

5.6pF_50v

2034-

14-,50-

C5319

0.1uF_16v

12

12

12

C5320

1

5.6pF_50v

2

R6169

R81

C5321

1

0.1uF_16v

2

CLK_3S_CBPCI

+V3S

R5296

12

10K_5%

12

12

22_5%

22_1%

1

2

R5291

R5292

R5293 22_1%

CLK_3S_SIOPCI

475_1%

475_1%

CR#_7

CR#_9

CR#_10

CR#_11

CLK_3S_REF

+V3M

12-,13-,14-,20-,27-,28-,34-

Layout note: All decoupling 0.1uF disperse closed to pin

L3008

BLM18AG471SN1D

1

R6086

12

1K_5%

2

C5041

1

2

10uF_6.3v

U33

62

VDDSRC_IO

52

VDDSRC_IO

38

VDDSRC_IO

23

VDD96_IO

55

VDDSRC

6

VDDREF

31

VDDPLL3_IO

66

VDDCPU_IO

CPUC2_ITP_LPR_SRCC8_LPR

19

12

72

27

20

13

14

15

10

18

22

26

30

42

59

69

34

11

65

37

41

73

74

75

76

CPUT2_ITP_LPR_SRCT8_LPR

VDD48

VDDPCI

VDDCPU

VDDPLL3

USB_48MHZ_FSLA

2

FSLB_TEST_MODE

7

FSLC_TEST_SEL_REF0

8

REF1

PCI1

PCI2_TME

PCI3

1

CK_PWRGD_PD#

SCLK

9

SDATA

5

X1

4

X2

GNDPCI

GND48

GND

SRCT2_LPR_SATAT_LPR

GND

SRCC2_LPR_SATAC_LPR

GNDSRC

GNDSRC

GNDCPU

27MHz_NonSS_SRCT1_LPR_SE1

3

GNDREF

27MHz_SS_SRCC1_LPR_SE2

GNDSRC

SRCT0_LPR_DOTT_96_LPR

NC

SRCC0_LPR_DOTC_96_LPR

CR#7

CR#A

CR#3

CR#4

TML-PAD

TML-PAD

TML-PAD

TML-PAD

ICS_ICS9LPRS397_MLF_72P

1

2

C5232

10uF_6.3v

CPUT1_LPR_F

CPUC1_LPR_F

CPUT0_LPR_F

CPUC0_LPR_F

PCI4_27_Select

PCI_F5_ITP_EN

PCI_STOP#

CPU_STOP#

SRCT11_LPR

SRCC11_LPF

SRCT10_LPR

SRCC10_LPR

SRCT9_LPR

SRCC9_LPR

SRCT7_LPR

SRCC7_LPR

SRCT6_LPR

SRCC6_LPR

SRCT4_LPR

SRCC4_LPR

SRCT3_LPR

SRCC3_LPR

C5325

C5324

1

2

0.1uF_16v

54

53

68

67

71

70

63

64

48

47

50

51

44

45

61

60

57

56

16

17

39

40

35

36

32

33

28

29

24

25

4321

CR#9

46

CR#11

49

CR#10

58

CR#6

5-,10-,12-,13-,14-,15-,18-,19-,20-,25-,26-,30-,31-,32-,33-,34-,35-,36-,37-,38-,40-,41-,46-,47-,48-,50-,51-,52-,54-

1

2

0.1uF_16v

CLK_XDP#

CLK_XDP

CLK_3S_KBPCI

CLK_3S_ICHPCI

1

2

0.1uF_16v

C5326

TP1057

TP1058

TP1

TP2

TP1040

TP1041

TP1055

Byte5:bit2=0(PWD), disable CR#_7 ; 1, enable CR#_7

SRC7

Byte5:bit1=0(PWD), disable CR#_9 ; 1, enable CR#_9

SRC9

Byte5:bit0=0(PWD), disable CR#_10 ; 1, enable CR#_10

SRC10

Byte5:bit7=0(PWD), disable CR#_11 ; 1, enable CR#_11

SRC11

12

14-

R5300

R5301

15_5%

12

15_5%

LAYOUT NOTES : THE R5300 , R5301 CLOSED TO U33

C5327

1

2

0.1uF_16v

FSA

0

0

CHANGE by

12-,13-,14-,20-,27-,28-,34-

C5329

C5328

1

1

2

2

0.1uF_16v

0.1uF_16v

10K_5%_OPEN

22_5%

30-

CLK_R_PEG_REF

30-

CLK_R_PEG_REF#

14-,49-

CLKREQ_MINI2#

14-

CLKREQ_MINI1#

14-,53-

CPPE#

ITP_EN =0

SRC8/SRC8#

ITP_EN =1

ITP/ITP#

5-,10-,12-,13-,14-,15-,18-,19-,20-,25-,26-,30-,31-,32-,33-,34-,35-,36-,37-,38-,40-,41-,46-,47-,48-,50-,51-,52-,54-

FSB

FSC

FSB CLOCK

FREQUENCY

0

1

0

0

800

1066

PUMA_CHEN 17-Jul-2008

12

0_5%

0_5%

22_5%

33_5%

R90

R5321

+V3M

1

2

12

12

R5322

12

R5313

C5720

5.6pF_50v

HOST CLOCK

FREQUENCY

200

266

C5716

5.6pF_50v

R5557

R5556

12

1

2

1

C5308

5.6pF_50v

2

1

2

1

R91

2

10K_5%_OPEN

C5719

1

2

5.6pF_50v

R5913

12

10K_5%

R5912

12

OPEN

27_Selet =0

LCD_SST 100MHZ

27_Selet =1

27MHZ non-spread clock

INVENTEC

TITLE

ABSOLUT

CLOCK_GENERATOR

SIZE

CODE

A3

CS

SHEET

38-

CLK_R3S_KBC14

40-

CLK_R3S_SIO14

34-

PCISTOP#_3

34-

CPUSTOP#_3

22-

CLK_R_MCHBCLK

22-

CLK_R_MCHBCLK#

15-

CLK_R_CPUBCLK

15-

CLK_R_CPUBCLK#

18-

CLK_R_XDP#

18-

CLK_R_XDP

49-

CLK_R_PCIE_MINI2

49-

CLK_R_PCIE_MINI2#

20-

CLK_PEG_MCH

20-

CLK_PEG_MCH#

53-

CLK_R_DOCK_REF

53-

CLK_R_DOCK_REF#

49-

CLK_R3S_MINICARD

38-

CLK_R3S_DEBUG

35-

CLK_R3S_ICHPCI

50-

CLK_R_PCIE_EXP

50-

CLK_R_PCIE_EXP#

34-

CLK_R_PCIE_ICH

34-

CLK_R_PCIE_ICH#

33-

CLK_R_SATA1

33-

CLK_R_SATA1#

C5718

1

2

5.6pF_50v

+V3S+V3S

R5336

12

10K_5%

R5909

2

1

OPEN

DOC. NUMBER

Model_No A04

OF

REV

6114

Page 15

8-,10-,15-,16-,17-,18-,20-,22-,25-,33-,36-

1

R6124

1K_1%

2

1

R6128

1.74K_1%

2

22-

H_A#(3)

H_A#(4)

H_A#(5)

H_A#(6)

H_A#(7)

H_A#(8)

H_A#(9)

H_A#(10)

H_A#(11)

H_A#(12)

H_A#(13)

H_A#(14)

H_A#(15)

H_A#(16)

H_REQ#(4:0) H_RS#(2:0)

H_A#(17)

H_A#(18)

H_A#(19)

H_A#(20)

H_A#(21)

H_A#(22)

H_A#(23)

H_A#(24)

H_A#(25)

H_A#(26)

H_A#(27)

H_A#(28)

H_A#(29)

H_A#(30)

H_A#(31)

H_A#(32)

H_A#(33)

H_A#(34)

H_A#(35)

8-,10-,15-,16-,17-,18-,20-,22-,25-,33-,36-

1818-

19-

2

1

R61090_5%_OPEN

R6110

19-

1

2

0_5%_OPEN

12

C5799

OPEN

18-

5-,10-,12-,13-,14-,18-,19-,20-,25-,26-,30-,31-,32-,33-,34-,35-,36-,37-,38-,40-,41-,46-,47-,48-,50-,51-,52-,54-

+V3S

Q5146

3

D

1

G

S

2

BSS138

MMBT3904

+VCCP

1

R6127

100K_5%

2

R6103

1

2

51_5%_OPEN

10mils/10mils

Q5147

3

C

B

E

2

22-

1

R6104

1

2

51_5%_OPEN

H_REQ#(0)

H_REQ#(1)

H_REQ#(2)

H_REQ#(3)

H_REQ#(4)

R6106

R6105

1

1

2

2

51_5%_OPEN

51_5%_OPEN

R9174

R6112 0_5%_OPEN

R9175

Layout note: Zo=55 ohm

0.5" max for GTLREF_2

8-,10-,15-,16-,17-,18-,20-,22-,25-,33-,36-

+VCCP

1

R6126

10K_5%

2

R6125

12

10K_5%

18-

H_ADSTB#0

0_5%_OPENR6107

12

12

0_5%_OPENR6108

12

0_5%_OPENR6111

12

12

12

0_5%_OPEN

GTLREF_CONTROL

0_5%

H_A#(35:3)

H_BPM1_XDP#_B

H_BPM0_XDP#_B

H_THERMDA_2

THERM_MINUS_2

H_BPM2_XDP#_B

+VCCP

For QC CPU: Install R6109 and R6110

For QC CPU: Un-install R6109 and R6110

22-

H_ADSTB#1

H_A20M#

H_FERR#

H_IGNNE#

H_STPCLK#

H_INTR

H_NMI

H_SMI#

8-,10-,15-,16-,17-,18-,20-,22-,25-,33-,36-

CN22-1

J4

A3#

L5

A4#

L4

A5#

K5

A6#

M3

A7#

N2

A8#

J1

A9#

N3

A10#

P5

A11#

P2

A12#

L2

A13#

ADDR GROUP 0

P4

A14#

P1

A15#

R1

A16#

M1

ADSTB0#

K3

REQ0#

H2

REQ1#

K2

REQ2#

J3

REQ3#

L1

REQ4#

Y2

A17#

U5

A18#

R3

A19#

W6

A20#

U4

A21#

Y5

A22#

U1

A23#

R4

A24#

T5

A25#

T3

A26#

ADDR GROUP 1

W2

A27#

W5

A28#

Y4

A29#

U2

A30#

V4

A31#

W3

A32#

AA4

A33#

AB2

A34#

AA3

A35#

V1

22-

ADSTB1#

33-

A6

A20M#

A5

33-

FERR#

C4

33-

IGNNE#

33333333-

ICH

D5

STPCLK#

C6

LINT0

B4

LINT1

A3

SMI#

M4

RSVD01

N5

RESERVED

RSVD02

T2

RSVD03

V3

RSVD04

B2

RSVD05

C3

RSVD06

D2

RSVD07

D22

RSVD08

D3

RSVD09

F6

RSVD010

H1

ADS#

E2

BNR#

G5

BPRI#

H5

DEFER#

F21

DRDY#

E1

DBSY#

F1

BR0#

D20

IERR#

B3

INIT#

CONTROL

H4

LOCK#

C1

RESET#

F3

RS0#

F4

RS1#

G3

RS2#

G2

TRDY#

G6

HIT#

E4

HITM#

AD4

BPM0#

AD3

BPM1#

AD1

BPM2#

AC4

BPM3#

AC2

PRDY#

AC1

PREQ#

AC5

TCK

AA6

TDI

AB3

TDO

AB5

TMS

AB6

XDP/ITP SIGNALS

TRST#

C20

DBR#

THERMAL

D21

PROCHOT#

A24

THERMDA

B25

THERMDC

C7

THERMTRIP#

H CLK

A22

BCLK0

A21

BCLK1

8-,10-,15-,16-,17-,18-,20-,22-,25-,33-,36-

FOX_PZ4782K_274M_41_478P

REF DES

Q5146

Q5147

R6103

R6104

R6105

R6106

R6107

R6108

R6109

R6110

R6111

R6112

R6119

R6121

R6124

R6125

R6126

R6127

R6128

R6129

R6130

R6131

R6132

R6133

R9174

R9175

Debug Support with QC ES1

Value

BSS138

MMBT3904 Install

51

51

51

51

0

0

0

0

0

0

0

0

1K,1%

10K,5%

10K,5%

100K,5%

1.74K,1%

51

51

51

51

51

0

0

Install

Install

Install

Install

Install

Install

Install

Install

Install

Install

Install

Install

Install

Install

Install

Install

Install

Install

Install

Install

Install

Install

Install

Install

Install

Install

+VCCP

R6132

1

2

51_5%_OPEN

+VCCP

68_5%R95

12

R6166

1

R9171

12

0_5%

0_5%_OPEN

2

19-,20-,30-,33-

10-

PM_THRMTRIP#

GMCH

PM_THRMTRIP# should be T at CPU

Debug Support with QC ES2 No Debug Port Support

Install

Install

Open

Open

Open

Install

Open

Open

Install

Install

Open

Install

Open

Install

Install

Install

Install

Install

Install

Install

Install

Install

Install

Open

Install

Install

R6131

1

2

51_5%_OPEN

CPU_PROCHOT#

CPU

Populate for QC CPU

R6130

R6129

1

1

2

2

51_5%_OPEN

51_5%_OPEN

C5792

1

2

OPEN

R9189

12

100_1%

ICH9

Install

Open

Open

Open

Open

Open

Open

Install

Install

Open

Open

Open

Install

Install

Install

Install

Install

Install

Open

Open

Open

Open

Open

Install

Open

222222-

222222-

22-

33-

22-

18-,22-

22-

2222-

1818181818-

15-,1815-,1815-,18-

18-

15-,18-

18-,34-

1414-

+VCCP

CHANGE by

CHANGE by

H_ADS#

H_BNR#

H_BPRI#

H_DEFER#

H_DRDY#

H_DBSY#

H_BREQ#0

H_INIT#

H_LOCK#

H_CPURST#

H_TRDY#

H_HIT#

H_HITM#

H_BPM0_XDP#

H_BPM1_XDP#

H_BPM2_XDP#

H_BPM3_XDP#

H_BPM4_PRDY#

H_BPM5_PREQ#

H_TCK

TDI_FLEX

H_TDO

H_TMS

XDP_DBRESET#

10mils/10mils

CLK_R_CPUBCLK

CLK_R_CPUBCLK#

+VCCP

8-,10-,15-,16-,17-,18-,20-,22-,25-,33-,36-

R5520

12

OPEN

19-

19-

PUMA_CHEN 17-Jul-2008

PUMA_CHEN

22-

H_RS#(0)

H_RS#(1)

H_RS#(2)

H_THERMDA

THERM_MINUS

+VCCP

8-,10-,15-,16-,17-,18-,20-,22-,25-,33-,36-

17-Jul-2008

+VCCP

8-,10-,15-,16-,17-,18-,20-,22-,25-,33-,36-

1

R190

51_5%

CLOSED TO CPU

2

51 ohm +/-1% pull-up to +VCCP

(VCCP) if ITP is implemented

18-

1

R5568

51_5%

2

R5569

12

51_5%

R5570

12

51_5%

R5571

12

51_5%

R5572

12

51_5%

INVENTEC

INVENTEC

TITLE

TITLE

ABSOLUT

ABSOLUT

PENRYN-1

PENRYN-1

SIZESIZE

CODE

CODE DOC. NUMBER

A3

A3

CS

CS

SHEET

SHEET OF

H_TRST#

15-,18-

H_BPM5_PREQ#

15-,18-

TDI_FLEX

15-,18-

H_TMS

15-,18-

H_TCK

DOC. NUMBER

Model_No A04

Model_No A04

OF

6115

6115

REV

REV

Page 16

H_D#(63:0)

H_DSTBN#0

H_DSTBP#0

H_DINV#0

H_D#(63:0)

+VCCP

8-,10-,15-,16-,17-,18-,20-,22-,25-,33-,36-

1

R5031

1K_1%

2

GTLREF

1

R5032

2K_1%

2

16-,22-

222222-

16-,22-

H_DSTBN#1

H_DSTBP#1

H_DINV#1

Layout note: Zo=55 ohm,

0.5" max for GTLREF.

CPU_BSEL0

CPU_BSEL1

CPU_BSEL2

CN22-2

H_D#(0)

H_D#(1)

H_D#(2)

H_D#(3)

H_D#(4)

H_D#(5)

H_D#(6)

H_D#(7)

H_D#(8)

H_D#(9)

H_D#(10)

H_D#(11)

H_D#(12)

H_D#(13)

H_D#(14)

H_D#(15)

H_D#(16)

H_D#(17)

H_D#(18)

H_D#(19)

H_D#(20)

H_D#(21)

H_D#(22)

H_D#(23)

H_D#(24)

H_D#(25)

H_D#(26)

H_D#(27)

H_D#(28)

H_D#(29)

H_D#(30)

H_D#(31)

222222-

14-,2014-,2014-,20-

1

2

R5037

OPEN

1

2

R5038

OPEN

0_5%

0_5%

0_5%

C5611

1

2

OPEN

R5921

2

1

12

R311

R5994

12

Place C5611(0.1uF_16V) close to the TEST4 pin.

Make sure TEST4 routing is reference

to GND and away from other noisy signals.

E22

D0#

F24

D1#

E26

D2#

G22

D3#

F23

D4#

G25

D5#

E25

D6#

E23

D7#

K24

D8#

G24

DATA GRP 0

D9#

J24

D10#

J23

D11#

H22

D12#

F26

D13#

K22

D14#

H23

D15#

J26

DSTBN0#

H26

DSTBP0#

H25

DINV0#

N22

D16#

K25

D17#

P26

D18#

R23

D19#

L23

D20#

M24

D21#

L22

D22#

M23

D23#

P25

D24#

P23

D25#

P22

DATA GRP 1

D26#

T24

D27#

R24

D28#

L25

D29#

T25

D30#

N25

D31#

L26

DSTBN1#

M26

DSTBP1#

N24

DINV1#

AD26

GTLREF

C23

TEST1

D25

TEST2

C24

TEST3

MISC

AF26

TEST4

AF1

TEST5

A26

TEST6

B22

BSEL0

B23

BSEL1

C21

BSEL2

FOX_PZ4782K_274M_41_478P

D32#

D33#

D34#

D35#

D36#

D37#

D38#

D39#

D40#

DATA GRP 2DATA GRP 3

D41#

D42#

D43#

D44#

D45#

D46#

D47#

DSTBN2#

DSTBP2#

DINV2#

D48#

D49#

D50#

D51#

D52#

D53#

D54#

D55#

D56#

D57#

D58#

D59#

D60#

D61#

D62#

D63#

DSTBN3#

DSTBP3#

DINV3#

COMP0

COMP1

COMP2

COMP3

DPRSTP#

DPSLP#

DPWR#

PWRGOOD

SLP#

PSI#

Y22

AB24

V24

V26

V23

T22

U25

U23

Y25

W22

Y23

W24

W25

AA23

AA24

AB25

Y26

AA26

U22

AE24

AD24

AA21

AB22

AB21

AC26

AD20

AE22

AF23

AC25

AE21

AD21

AC22

AD23

AF22

AC23

AE25

AF24

AC20

R26

U26

AA1

Y1

E5

B5

D24

D6

D7

AE6

1

2

R5039

OPEN

10-,20-,33-

H_D#(32)

H_D#(33)

H_D#(34)

H_D#(35)

H_D#(36)

H_D#(37)

H_D#(38)

H_D#(39)

H_D#(40)

H_D#(41)

H_D#(42)

H_D#(43)

H_D#(44)

H_D#(45)

H_D#(46)

H_D#(47)

H_D#(48)

H_D#(49)

H_D#(50)

H_D#(51)

H_D#(52)

H_D#(53)

H_D#(54)

H_D#(55)

H_D#(56)

H_D#(57)

H_D#(58)

H_D#(59)

H_D#(60)

H_D#(61)

H_D#(62)

H_D#(63)

12

R5033 24.9_1%

12

R5034 49.9_1%

12

R5035 24.9_1%

12

R5036

H_DPRSTP#

49.9_1%

CLOSED TO CPU

+VCCP

8-,10-,15-,16-,17-,18-,20-,22-,25-,33-,36-

22-

H_DSTBN#3

22-

H_DSTBP#3

22-

H_DINV#3

33-

H_DPSLP#

22-

H_DPWR#

22-

H_CPUSLP#

10-

PSI#

Place series resistor (R5040= 1K ohm) on H_PWRGD_XDP without stub

16-,22-

H_D#(63:0)

22-

H_DSTBN#2

22-

H_DSTBP#2

22-

H_DINV#2

16-,22-

H_D#(63:0)

Layout note:

Comp0,2 connect with Zo=27.4ohm, make

trace length shorter than o.5" .

Comp1,3 connect with Zo=55ohm, make

trace length shorter than 0.5" .

33-

R5040

12

1K_5%

H_PWRGD

18-

H_PWRGD_XDP

CHANGE by

PUMA_CHEN 17-Jul-2008PUMA_CHEN

INVENTEC

INVENTEC

TITLE

TITLE

ABSOLUT

ABSOLUT

PENRYN-2

PENRYN-2

DOC. NUMBER

CODE

CODE

SIZE

A3

A3

Model_No A04

CS

CS

SHEETCHANGE by

SHEET

16 61

REV

REVSIZE DOC. NUMBER

A04Model_No

OF

OF

6116

Page 17

PLACE THESE INSIDE SOCKET

CAVITY ON L8 (NORTH SIDE

SECONDARY)

PLACE THESE INSIDE SOCKET

CAVITY ON L8 (SOUTH SIDE