intersil X80010, X80011, X80012, X80013 DATA SHEET

查询X80010供应商

®

X80010, X80011, X80012, X80013

PRELIMINARY

Data Sheet January 13, 2005

Penta-Power Sequence Controller

with Hot swap and System Management

The X80010, X80011, X80012, X80013 contain three major

functions: a power sequencing controller, a hotswap

controller, and systems management support.

The power sequencer controller time sequences up to five

DC/DC modules. The device allows various DC/DC power

sequencing configurations, either parallel or relay modes.

The power good, enable, and voltage good signals provide

for flexible DC/DC timing configurations. Each voltage

enable signal has a built-in delay while additional delay can

be added with simple external passive components.

The hot swap controller allows a board to be safely inserted

and removed from a live backplane without turning off the

main power supply. The X80010 family of devices offers a

modular, power distribution approach by providing flexibility

to solve the hotswap and power sequencing issues for

insertion, operations, and extraction. Hardshort Detection

and Retry with Delay, Noise filtering, Insertion Overcurrent

Bypass, and Gate Current selection are some of the

integrated features of the device. During insertion, the gate

of an external power MOSFET is clamped low to suppress

contact bounce. The undervoltage/overvoltage circuits and

the power on reset circuitry suppress the gate turn on until

the mechanical bounce has ended. The X80010 turns on the

gate with a user set slew rate to limit the inrush current and

incorporates an electronic circuit breaker set by a sense

resistor. After the load is successfully charged, the PWRGD

signal is asserted; indicating that the device is ready to

power sequence the DC/DC power bricks.

FN8149.0

Features

• Integrates Three Major Functions

- Power Sequencing

- Hot Swap Controller

- System Management Functions

• Penta-Power Sequencing

- Sequence up to 5 DC/DC converters.

- Four independent voltage enable pins

- Four time delay circuits

- Soft Power Sequencing - MRC pin restarts sequence

without power cycling.

• Hot Swap Controller

- Programmable overvoltage and undervoltage protection

- Undervoltage lockout for battery/redundant supplies

- Electronic circuit breaker - Overcurrent Detection and

Gate Shut-off

- Overcurrent limit during Insertion

- Hardshort retry with retry failure flag

- Selectable gate current using IGQ pins (10, 70, 150µA)

- MRH pin controls board insertion/extraction.

- Typically operates from -30V to -80V. Tolerates

transients to -200V (limited by external components)

• System Management

- Reset output, with delay, holds off host until all supplies

are good

- Host control of reinsertion with MRH input

- Host control of resequencing using MRC input

• Available packages

- 32-lead Quad No-Lead Frame (QFN)

Systems management function provides a reset signal

indicating that the power good and all the voltage good

signals are active. The reset signal is asserted after a wait

state delay. This signal is used to coordinate the hotswap

and DC/DC module latencies during power up to avoid

"power hang up". In addition, the CPU host can initiate soft

insertion or DC voltage module re-sequencing.

1

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 321-724-7143

Applications

• -48V Hot Swap Power Backplane/Distribution Central

Office, Ethernet for VOIP

• Card Insertion Detection

• Power Sequencing DC/DC/Power Bricks

• IP Phone Applications

• Databus Power Interfacing

• Custom Industrial Power Backplanes

• Distributed Power Systems

| Intersil (and design) is a registered trademark of Intersil Americas Inc.

All other trademarks mentioned are the property of their respective owners.

Copyright Intersil Americas Inc. 2005. All Rights Reserved

Pinout

QFN package

(Top view)

GQ0

I

MRH

I

32

V

RGO

NA1

V4GOOD

EN4

V3GOOD

EN3

V2GOOD

EN2 817

1

2

3

4

(7mm x 7mm)

5

6

7

91011121314

EE

DD

V

V

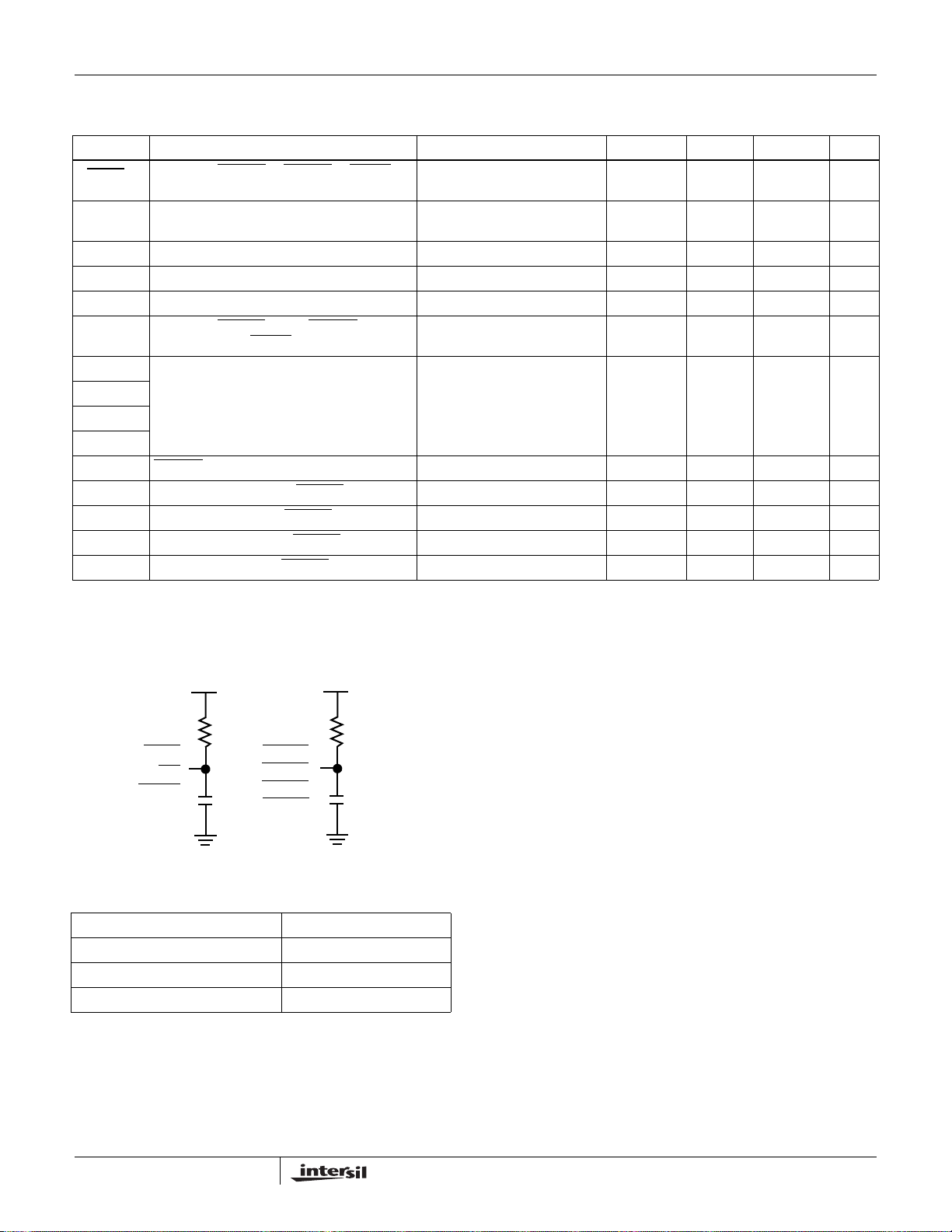

Ordering Information

X80010, X80011, X80012, X80013

GQ1

PWRGD

UV/OV

V

SENSE

EE

V

FAR

BA TT-ON

NC

262728293031

GATE

25

15

16

NA1

DRAIN

24

23

22

21

20

19

18

NA1

NC

MRC

NA1

RESET

V1GOOD

EN1

NA2

NA2

RETRY

DELAY

(ms)

I

GATE

(µA)

T

DELAY

(ms)

t

POR

(ms)

TEMP RANGE

(°C)

MARK

ORDER

NUMBER

OV

(V)

UV1

(V)

UV2

(V)

t

NF

(us)

V

OC

(mV)

V

OCI

(mV)

OVER

CURRENT

RETRY

X80010Q32I 74.9 42.4 33.2 5 50 150 Always 100 50 100 100 -40 to 85 80010I

X80011Q32I 68.0 42.4 33.2 5 50 150 Always 100 50 100 100 -40 to 85 80011I

X80012Q32I 74.9 42.4 33.2 5 50 150 5 retries 100 50 100 100 -40 to 85 80012I

X80013Q32I 68.0 42.4 33.2 5 50 150 5 retries 100 50 100 100 -40 to 85 80013I

Typical Application

BackPlane

-48V

RTN

-48V

R5

30k

1%

12V

R4

182k

1%

R6

10k

1%

4.7V

X80010, X80011,

X80012, X80013

OV=71V

V

UV/OV

UV=37V

V

DD

V

SENSE

EE

0.1uF

Rs

0.02Ω

5%

IRFR120

GATE

Q1

PWRGD

V1GOOD

V2GOOD

V3GOOD

DRAIN

100

EN1

EN2

EN3

4.7K

3.3n

100K

DC/DC

Module

1

ON/OFF

DC/DC

Module

2

ON/OFF

V1

DC/DC

Module

3

ON/OFF

V2

DC/DC

Module

4

ON/OFF

V3

PAR T

V4

2

FN8149.0

January 13, 2005

X80010, X80011, X80012, X80013

Absolute Maximum Ratings Recommended Operating Conditions

Temperature under bias . . . . . . . . . . . . . . . . . . . . . –65°C to +135°C

Storage temperature . . . . . . . . . . . . . . . . . . . . . . . –65°C to +150°C

Voltage on given pin (Hot Side Functions):

V

ov/uv pin

SENSE pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 400mV + V

VEE pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -80V

DRAIN pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48V + V

PWRGD pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7V + V

GATE pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . VDD + V

FAR pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7V + V

MRH pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5.5V + V

BATT_ON pin. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5.5V + V

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5.5V + V

EE

EE

EE

EE

EE

EE

EE

EE

Voltage on given pin (Cold Side Functions):

ENi

pins (i = 1 to 4) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5V

ViGOOD

RESET pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5.5V + V

MRC pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5.5V + V

IGQ1 and IGQ0 pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5.5V + V

VDD pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14V + V

D.C. output current. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5mA

pins (i = 1 to 4) . . . . . . . . . . . . . . . . . . . . . . . . . 5.5V + V

EE

EE

EE

EE

EE

Lead temperature (soldering, 10 seconds) . . . . . . . . . . . . . . .300°C

CAUTION: Stresses above those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress rating only; functional

operation of the device (at these or any other conditions above those listed in the operational sections of this specification) is not implied. Exposure to absolute maximum

rating conditions for extended periods may affect device reliability.

Temperature Range (Industrial) . . . . . . . . . . . . . . . . . . -40°C to 85°C

Supply Voltage (V

) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12V

DD

Electrical Specifications (Standard Settings)

Over the recommended operating conditions unless otherwise specified.

SYMBOL PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

DC CHARACTERISTICS

V

I

V

I

RGO

I

GATE

V

GATE

V

V

V

I

V

V

DD

RGO

PGA

IHB

ILB

I

LO

IL

IH

Supply Operating Range 10 12 14 V

DD

Supply Current 2.5 5 mA

Regulated 5V output I

V

current output 50 µA

RGO

Gate Pin Current Gate Drive On,

External Gate Drive (Slew Rate Control) I

Power Good Threshold

(PWRGD

High to Low)

= 10µA 4.5 6.0

RGO

46.2 52.5 58.8 µA

V

= VEE,

GATE

V

= V

SENSE

- VEE = 3V

V

GATE

V

SENSE-VEE

= 50µA VDD-1 V

GATE

Referenced to V

V

< V

UV1

(sourcing)

EE

= 0.1V (sinking)

EE

< V

UV/OV

9mA

0.9 1 1.1 V

OV

Voltage Input High (BATT_ON) VEE + 4 VEE + 5 V

Voltage Input Low (BATT_ON) VEE + 2 V

Input Leakage Current (MRH, MRC) VIL = GND to V

LI

Output Leakage Current

(V1GOOD

RESET

(3)

Input LOW Voltage (MRH, MRC, IGQ0, IGQ1) -0.5 + V

(3)

Input HIGH Voltage (MRH, MRC, IGQ0, IGQ1) (VEE + 5) x

, V2GOOD, V3GOOD, V4GOOD,

)

All ENi

= V

CC

for i = 1 to 4 10 µA

RGO

EE

0.7

DD

10 µA

(VEE + 5) x

0.3

(VEE + 5) +

0.5

V

V

V

3

FN8149.0

January 13, 2005

X80010, X80011, X80012, X80013

Electrical Specifications (Standard Settings)

Over the recommended operating conditions unless otherwise specified. (Continued)

SYMBOL PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

V

Output LOW Voltage

OL

(RESET, RESET

V3GOOD

(1)

C

OUT

Output Capacitance

(RESET

, V1GOOD, V2GOOD, V3GOOD,

V4GOOD

(1)

C

IN

V

V

OCI

V

OVR

V

OVH

V

UV1H

V

UV1F

V

UV2H

V

UV2F

V

DRAINF

V

DRAINR

V

TRIP1

V

TRIP2

V

TRIP3

V

TRIP4

OC

Input Capacitance (MRH, MRC) VIN = 0V 6 pF

Over-current threshold VOC = V

Over-current threshold (Insertion) VOC = V

Overvoltage threshold (rising)

Overvoltage hysteresis Referenced to V

Undervoltage 1 hysteresis Referenced to V

Undervoltage 1 threshold (falling) 2.16 2.21 2.26 V

Undervoltage 2 hysteresis Referenced to V

Undervoltage 2 threshold (falling) 1.68 1.73 1.78 V

Drain sense voltage threshold

(falling)

Drain sense voltage threshold

(rising)

EN1 Trip Point Voltage Referenced to V

EN2 Trip Point Voltage Referenced to V

EN3 Trip Point Voltage Referenced to V

EN4 Trip Point Voltage Referenced to V

AC CHARACTERISTICS

t

FOC

t

FUV

t

FOV

t

VFR

t

BATT_ON

t

MRC

t

MRH

t

MRCE

t

MRCD

t

MRHE

t

MRHD

Sense High to Gate Low 1.5 2.5 3.5 µs

Under Voltage conditions to Gate Low 0.5 1.0 1.5 µs

Overvoltage Conditions to Gate Low 1.0 1.5 2 µs

Overvoltage/undervoltage failure recovery time

to Gate =1V.

Delay BATT_ON Valid 100 ns

Minimum time high for reset valid on the MRC

pin

Minimum time high for reset valid on the MRH

pin

Delay from MRC enable to PWRGD HIGH No Load 1.0 1.6 µs

Delay from MRC disable to PWRGD LOW Gate is On, No Load 200 400 µs

Delay from MRH enable to Gate Pin LOW I

Delay from MRH disable to GATE reaching 1V I

, V1GOOD, V2GOOD,

, V4GOOD, FAR, PWRGD)

, FAR)

X80010, X80012

X80011, X80013

I

= 4.0mA

OL

(V

+ 2.7 to VEE + 5.5V)

EE

I

= 2.0mA

OL

(V

+ 2.7 to VEE + 3.6V)

EE

V

= 0V 8 pF

OUT

SENSE

PWRGD = HIGH

SENSE

- V

- V

EE

EE

45 50 55 mV

135 150 165 mV

Initial Power Up condition

Referenced to V

BATT-ON = V

BATT-ON = V

Referenced to V

Referenced to V

EE

EE

EE

EE

EE

RGO

EE

EE

EE

EE

EE

EE

VDD does not drop below 3V, No

3.85

3.49

3.90

3.54

12 18 24 mV

12 18 24 mV

12 18 24 mV

0.9 1 1.1 V

1.2 1.3 1.4 V

2.25 2.5 2.75 V

2.25 2.5 2.75 V

2.25 2.5 2.75 V

2.25 2.5 2.75 V

1.2 1.6 2 µs

other failure conditions.

5 µs

5 µs

= 60µA, No Load 1.0 1.6 2.4 µs

GATE

= 60µA, No Load 1.8 2.6 µs

GATE

V

+ 0.4 V

EE

3.95

3.59

V

4

FN8149.0

January 13, 2005

X80010, X80011, X80012, X80013

Electrical Specifications (Standard Settings)

Over the recommended operating conditions unless otherwise specified. (Continued)

SYMBOL PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

t

RESET_E

t

QC

t

SC_RETRY

t

NF

t

DPOR

t

SPOR

t

DELAY1

t

DELAY2

t

DELAY3

t

DELAY4

t

TO

t

PDHLPG

t

PDLHPG

t

PGHLPG

t

PGLHPG

NOTE:

1. This parameter is based on characterization data.

Delay from PWRGD or ViGOOD to RESET

1 µs

valid LOW

Delay from IGQ1 and IGQ0 to valid Gate pin

1 µs

current

Delay between Retries 85 100 115 ms

Noise Filter for Overcurrent 4.5 5 5.5 µs

Device Delay before Gate assertion 45 50 55 ms

Delay after PWRGD and all ViGOOD signals

are active before RESET

assertion

Power Sequencing Time Delay

85 100 115 ms

85 100 115 ms

TiD1 = 0; TiD0 = 0

ViGOOD turn off time 50 ns

(1)

Delay from Drain good to PWRGD LOW Gate = V

(1)

Delay from Drain fail to PWRGD HIGH Gate = V

(1)

Delay from Gate good to PWRGD LOW Drain = V

(1)

Delay from Gate fail to PWRGD HIGH Drain = V

DD

DD

EE

EE

1 µs

1 µs

1 µs

1 µs

Equivalent A.C. Output Load Circuit

5V

4.6kΩ

,

30pF

RESET

FAR

PWRGD

5V

4.6kΩ

30pF

V1GOOD,

V2GOOD,

V3GOOD

V4GOOD

A.C. Test Conditions

Input pulse levels VCC x 0.1 to VCC x 0.9

Input rise and fall times 10ns

Input and output timing levels V

Output load Standard output load

CC

x 0.5

5

FN8149.0

January 13, 2005

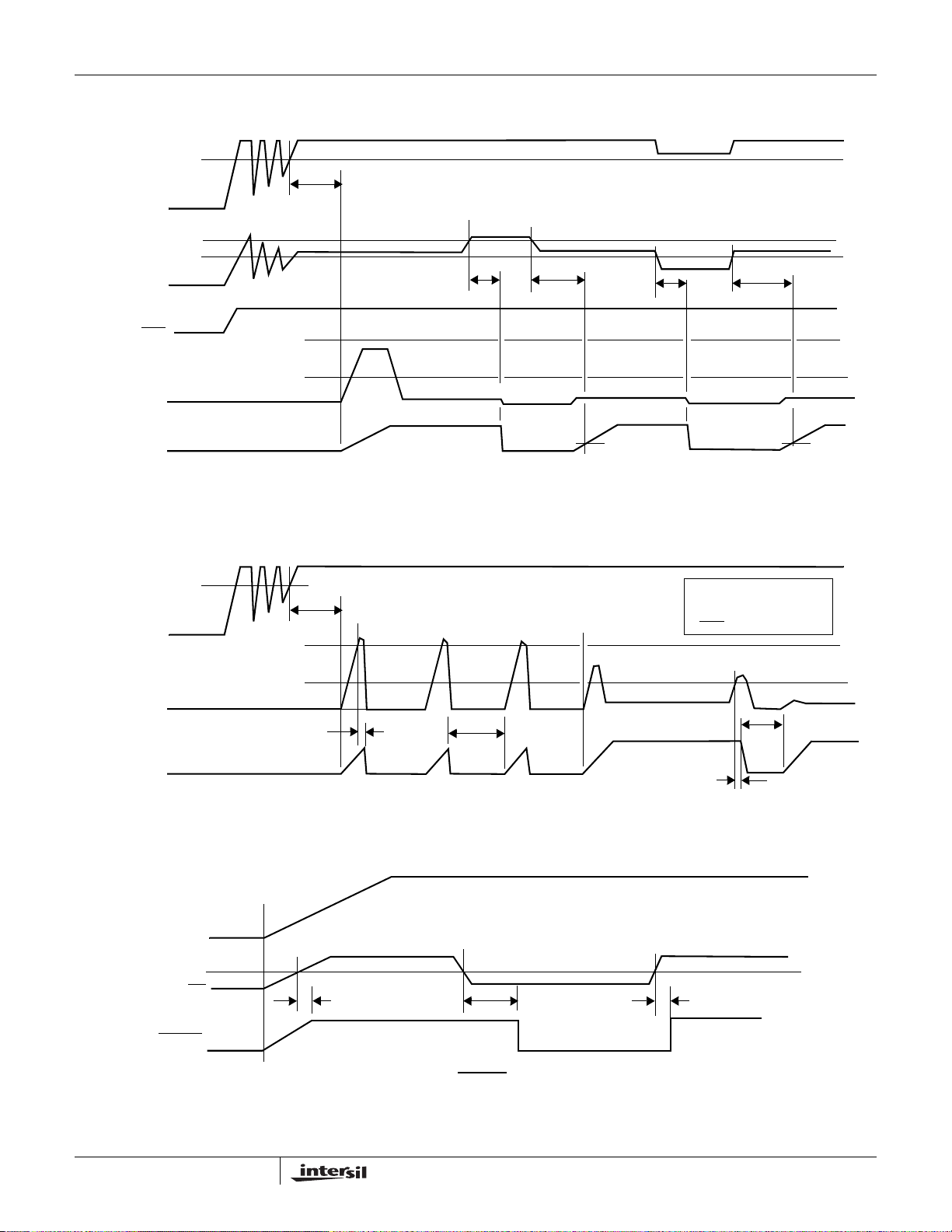

V

UV/OV

VDD

X80010, X80011, X80012, X80013

V

TH

t

DPOR

V

OV

V

UV

t

FOV

t

VFR

t

FUV

t

VFR

MRH

SENSE

GATE

VDD

SENSE

GATE

V

OCI

V

OC

1V 1V

FIGURE 1. OVERVOLTAGE/UNDERVOLTAGE GATE TIMING

V

TH

t

DPOR

Always Retry

< V

V

UV

UV/OV < VOV

MRH = HIGH

V

OCI

V

OC

t

t

FOC

t

SC_RETRY

t

FOC

SC_RETRY

FIGURE 2. OVERCURRENT GATE TIMING

VDD

V

TRIPi

ENi

ViGOOD

Initial

Power-up

6

t

TO

t

DELAYi

Enable DC/DC supply

t

TO

i = 1, 2, 3, 4

FIGURE 3. ViGOOD TIMINGS

FN8149.0

January 13, 2005

MRH

t

MRH

X80010, X80011, X80012, X80013

MRC

t

MRC

GATE

t

MRHE

FIGURE 4. MANUAL RESET (HOT SIDE) MRH

V

DRAIN

V

GATE

PWRGD

ENi

V1GOOD

V2GOOD

1V

t

DHLPG

t

GLHPG

t

MRHD

t

DELAY1

t

DELAY2

PWRGD

t

MRCE

FIGURE 5. MANUAL RESET (COLD SIDE) MRC

t

DLHPG

t

GHLPG

t

MRCD

V3GOOD

V4GOOD

RESET

t

DELAY3

t

DELAY4

t

SPOR

FIGURE 6. RESET TIMINGS

PWRGD or

any ENi LOW to HIGH

(1st occurance)

t

RESET_E

7

FN8149.0

January 13, 2005

X80010, X80011, X80012, X80013

Typical Performance Characteristics

52.000

51.000

50.000

49.000

48.000

47.000

INRUSH CURRENT LIMIT (mV)

46.000

-55 -40 -25 -10 5 20 35 50 65 80 95 110 125

TEMPERATURE

FIGURE 7. OVER CURRENT THRESHOLD vs

TEMPERATURE

3.92

3.91

3.90

3.89

3.88

3.87

OV THRESHOLD (V)

3.86

3.85

-55 -40 -25 -10 5 20 35 50 65 80 95 110 125

TEMPERATURE

Rising

Falling

FIGURE 9. OVERVOLTAGE THRESHOLD vs TEMPERATURE

1.780

1.770

1.760

1.750

1.740

1.730

1.720

1.710

1.700

1.690

UNDER VOLTAGE 2 THRESHOLD (V)

-55 -40 -25 -10 5 20 35 50 65 80 95 110 125

TEMPERATURE

FIGURE 8. UNDERVOLTAGE 2 THRESHOLD vs

TEMPERATURE

2.515

2.510

2.505

2.500

2.495

2.490

2.485

ENi THRESHOLD (V)

2.480

2.475

-55 -40 -25 -10 5 20 35 50 65 80 95 110 125

TEMPERATURE

FIGURE 10. ENi

THRESHOLD vs TEMPERATURE

Rising

Falling

2.250

2.240

2.230

2.220

2.210

2.200

UNDER VOLTAGE 1 THRESHOLD (V)

2.190

-55 -40 -25 -10 5 20 35 50 65 80 95 110 125

TEMPERATURE

FIGURE 11. UNDERVOLTAGE 1 THRESHOLD vs

TEMPERATURE

8

Rising

Falling

200

160

120

80

GATE CURRENT (µA)

40

0

-55 -40 -25 -10 5 20 35 50 65 80 95 110 125

TEMPERATURE

FIGURE 12. I

(SOURCE) vs TEMPERATURE

GATE

150µA

70µA

50µA

10µA

FN8149.0

January 13, 2005