Intersil MCTV65P100F1, MCTA65P100F113 Datasheet

CAUTION: These devices are sensitive to electrostatic discharge. Users should follow proper ESD Handling Procedures.

Copyright

© Harris Corporation 1999

2-13

Semiconductor

MCTV65P100F1,

MCTA65P100F1

65A, 1000V

P-Type MOS Controlled Thyristor (MCT)

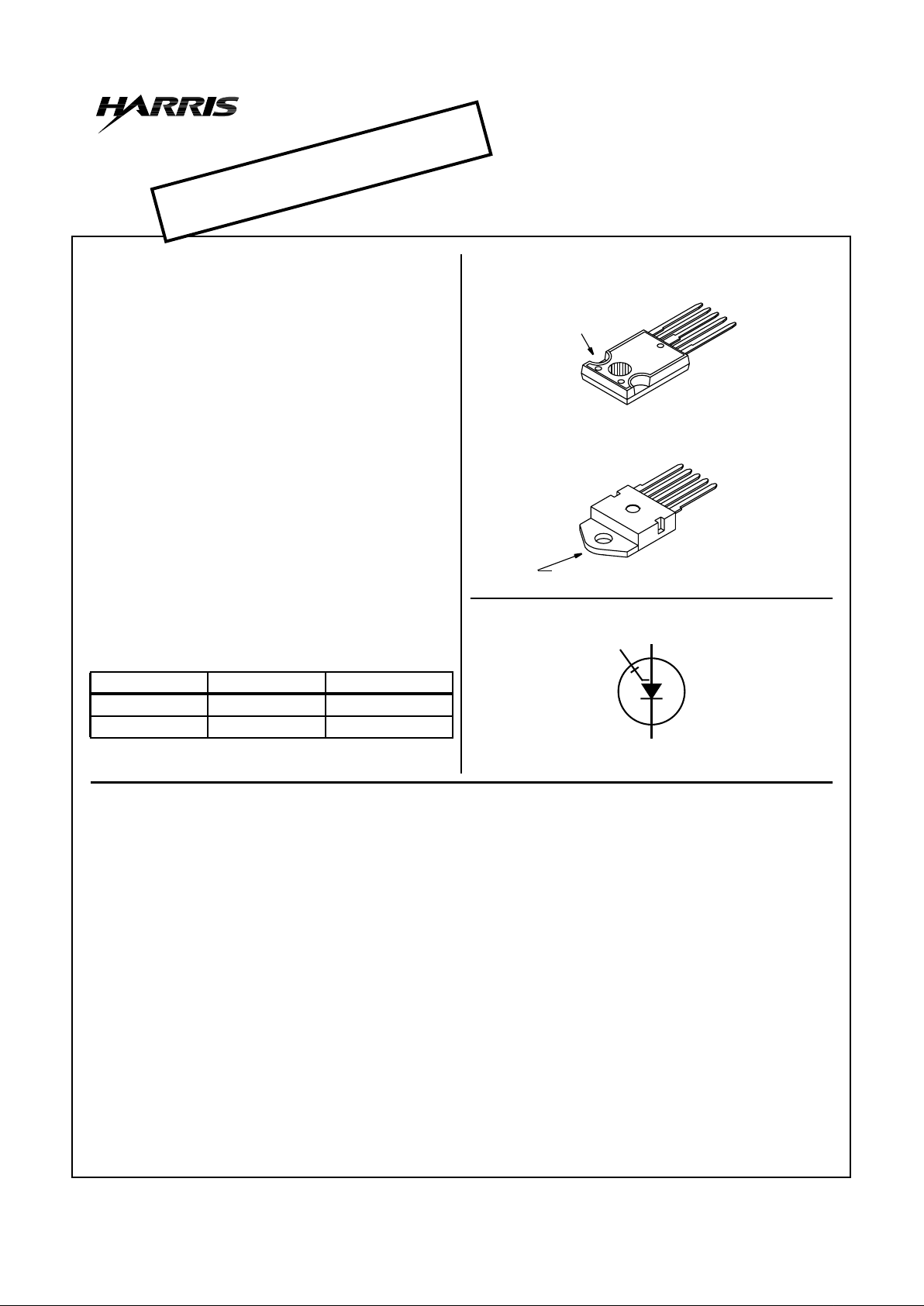

Package

JEDEC STYLE TO-247

JEDEC MO-093AA (5-LEAD TO-218)

Symbol

GATE

GATE RETURN

CATHODE

ANODE

ANODE

CATHODE (FLANGE)

CATHODE (FLANGE)

GATE

GATE RETURN

CATHODE

ANODE

ANODE

G

A

K

Features

• 65A, -1000V

•V

TM

≤ -1.4V at I = 65A and +150oC

• 2000A Surge Current Capability

• 2000A/µs di/dt Capability

• MOS Insulated Gate Control

• 100A Gate T urn-Off Capability at +150

o

C

Description

The MCT is an MOS Controlled Thyristor designed for switching

currents on and off by negative and positive voltage control of an

insulated MOS gate. It is designed for use in motor controls,

inverters, line switches and other power s witching applications .

The MCT is especially suited for resonant (zero voltage or zero

current switching) applications. The SCR like forward drop

greatly reduces conduction power loss.

MCTs allow the control of high power circuits with very small

amounts of input energy. They feature the high peak current

capability common to SCR type thyristors, and operate at junction temperatures up to +150

o

C with active switching.

Formerly TA9900.

PART NUMBER INFORMATION

PART NUMBER PACKAGE BRAND

MCTV65P100F1 TO-247 M65P100F1

MCTA65P100F1 MO-093AA M65P100F1

NOTE: When ordering, use the entire part number.

April 1999

Absolute Maximum Ratings T

C

= +25oC, Unless Otherwise Specified

MCTV65P100F1

MCTA65P100F1 UNITS

Peak Off-State Voltage (See Figure 11). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . V

DRM

-1000 V

Peak Reverse Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . V

RRM

+5 V

Continuous Cathode Current (See Figure 2)

TC = +25oC (Package Limited) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

TC = +90oC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

I

K25

I

K90

85

65

A

A

Non-Repetitive Peak Cathode Current (Note 1). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . I

TSM

2000 A

Peak Controllable Current (See Figure 10) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . I

TC

100 A

Gate-Anode Voltage (Continuous) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . V

GA

±20 V

Gate-Anode Voltage (Peak) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . V

GA

±25 V

Rate of Change of Voltage. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . dv/dt See Figure 11

Rate of Change of Current . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . di/dt 2000 A/µs

Maximum Power Dissipation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . P

T

208 W

Linear Derating Factor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1.67 W/oC

Operating and Storage Temperature . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . TJ, T

STG

-55 to +150

o

C

Maximum Lead Temperature for Soldering . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

(0.063" (1.6mm) from case for 10s)

T

L

260

o

C

NOTE:

1. Maximum Pulse Width of 200µs (Half Sine) Assume TJ (Initial) = +90oC and TJ (Final) = TJ (Max) = +150oC

File Number 3516.5

PART WITHDRAWN

PROCESS OBSOLETE - NO NEW DESIGNS

2-14

Specifications MCTV65P100F1, MCTA65P100F1

Electrical Specifications T

C

= +25oC Unless Otherwise Specified

PARAMETER SYMBOL TEST CONDITIONS MIN TYP MAX UNITS

Peak Off-State

Blocking Current

I

DRM

VKA = -1000V,

VGA = +18V

TC = +150oC- - 3 mA

TC = +25oC - - 100 µA

Peak Reverse

Blocking Current

I

RRM

VKA = +5V,

VGA = +18V

TC = +150oC- - 4 mA

TC = +25oC - - 100 µA

On-State Voltage V

TM

IK = I

K90

,

VGA = -10V

TC = +150oC - - 1.4 V

TC = +25oC - - 1.5 V

Gate-Anode

Leakage Current

I

GAS

VGA = ±20V - - 200 nA

Input Capacitance C

ISS

VKA = -20V, TJ = +25oC

VGA = +18V

-10-nF

Current Turn-On

Delay Time

t

D(ON)I

L = 200µH, IK = I

K90

= 65A

RG = 1Ω, VGA = +18V, -7V

TJ = +125oC

VKA = -400V

- 120 - ns

Current Rise Time t

RI

- 160 - ns

Current Turn-Off

Delay Time

t

D(OFF)I

- 750 - ns

Current Fall Time t

FI

- 1.45 1.9 µs

Turn-Off Energy E

OFF

-18-mJ

Thermal Resistance R

θJC

- 0.5 0.6

o

C/W

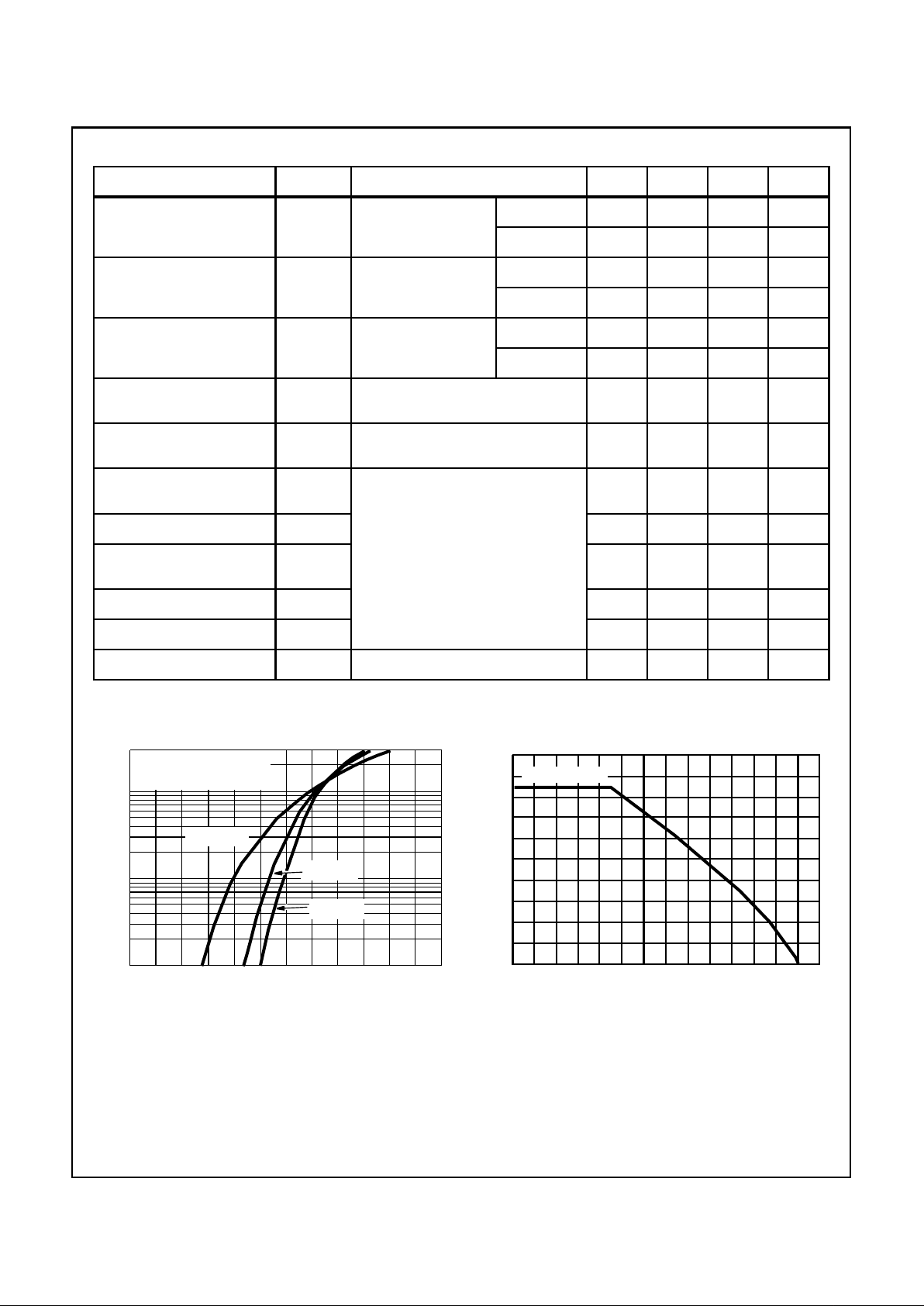

Typical Performance Curves

FIGURE 1. CATHODE CURRENT vs SATURATION VOLTAGE

(TYPICAL)

FIGURE 2. MAXIMUM CONTINUOUS CATHODE CURRENT

100

10

1

0.0 0.2 0.4 0.6 0.8 1.0 1.2 1.4 1.6 1.8 2.0

V

TM

, CATHODE VOLTAGE (V)

2.2 2.4

PULSE TEST

PULSE DURATION = 250µs

DUTY CYCLE < 2%

TJ = +150oC

TJ = +25oC

TJ = -40oC

I

K

, CATHODE CURRENT (A)

100

90

80

70

60

50

40

30

20

10

0

20 30 40 50 60 70 80 90 100 110 120 130 140 150

T

C

, CASE TEMPERATURE (oC)

160

PACKAGE LIMIT

I

K

, DC CATHODE CURRENT (A)

Loading...

Loading...