®

ISL97656

Data Sheet April 23, 2009

Integrated 4A Switch PWM Step-Up

Regulator

The ISL97656 is a high frequency, high efficiency step-up

voltage regulator operated at constant frequency PWM

mode. With an internal 4.0A, 120mΩ MOSFET, it can deliver

up to 2A output current at over 90% efficiency. The

selectable 640kHz and 1.2MHz allows smaller inductors and

faster transient response. An external compensation pin

gives the user greater flexibility in setting frequency

compensation allowing the use of low ESR Ceramic output

capacitors.

When shut down, it draws <1µA of current and can operate

down to 2.3V input supply. These features along with

1.2MHz switching frequency makes it an ideal device for

portable equipment and TFT-LCD displays.

The ISL97656 is available in a 10 Ld TDFN package with a

maximum height of 1.1mm. The device is specified for

operation over the full -40°C to +85°C temperature range.

FN6439.3

Features

• >90% Efficiency

• 4.0A, 120mΩ Power MOSFET

• 2.3V to 6.0V Input

• Up to 24V Output

• 640kHz/1.2MHz Switching Frequency Selection

• Adjustable Soft-Start

• Internal Thermal Protection

• 0.8mm Max Height 10 Ld TDFN Package

• Pb-Free (RoHS Compliant)

• Halogen Free

Applications

• TFT-L CD Di sp l ays

• DSL Modems

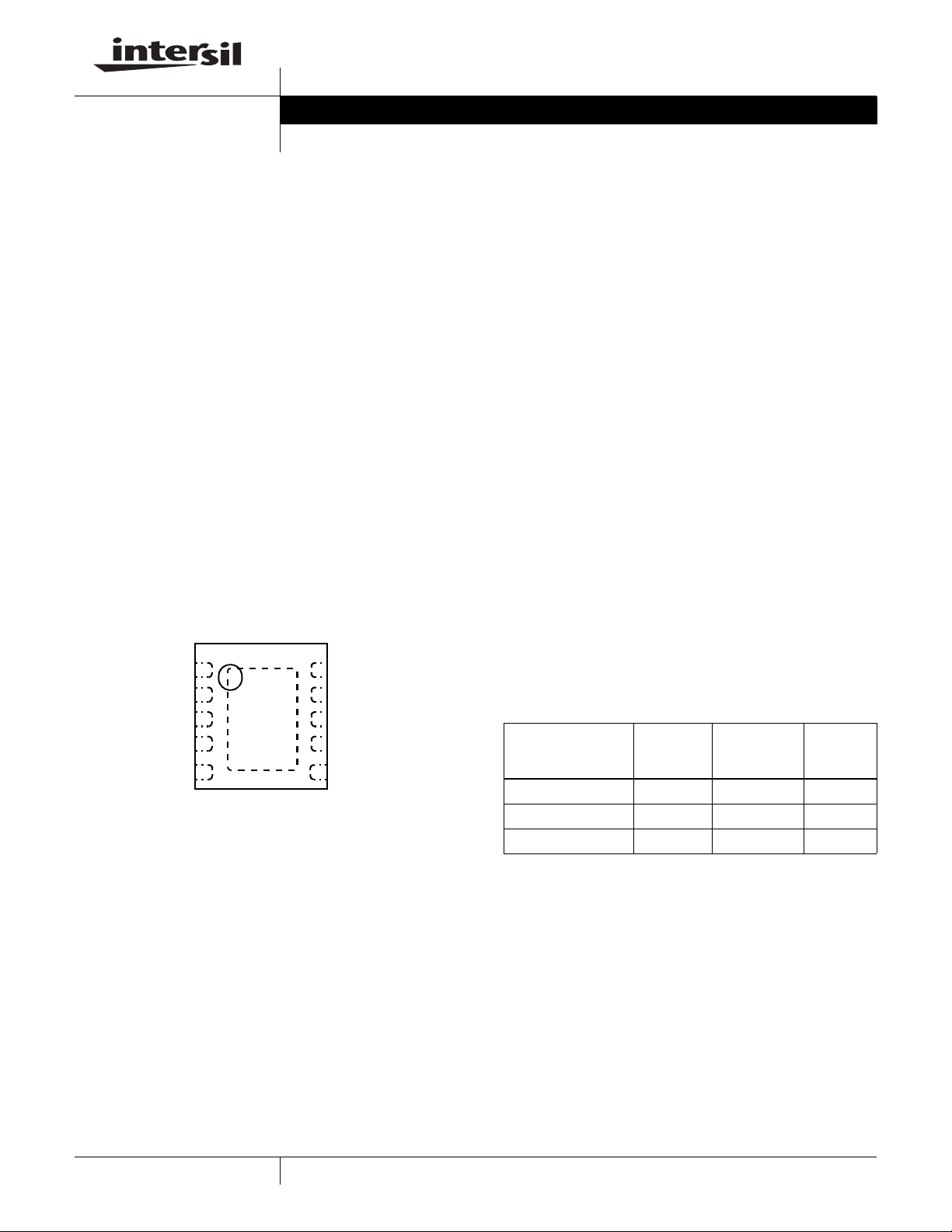

Pinout

COMP

FB

EN

GND

GND

ISL97656

(10 LD TDFN)

TOP VIEW

1

2

3

4

5

• PCMCIA Cards

• Digital Cameras

• GSM/CDMA Phones

• Portable Equipment

SS

10

9

FREQ

8

IN

7

LX

LX

6

• Handheld Devices

Ordering Information

PART

NUMBER

(Note)

ISL97656IRTZ 656Z 10 Ld TDFN L10.3x3B

ISL97656IRTZ-T* 656Z 10 Ld TDFN L10.3x3B

ISL97656IRTZ-TK* 656Z 10 Ld TDFN L10.3x3B

*Please refer to TB347 for details on reel specifications.

NOTE: These Intersil Pb-free plastic packaged products employ

special Pb-free material sets, molding compounds/die attach

materials, and 100% matte tin plate plus anneal (e3 termination

finish, which is RoHS compliant and compatible with both SnPb and

Pb-free soldering operations). Intersil Pb-free products are MSL

classified at Pb-free peak reflow temperatures that meet or exceed

the Pb-free requirements of IPC/JEDEC J STD-020.

PART

MARKING

PACKAGE

(Pb-Free)

PKG.

DWG. #

1

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 1-888-468-3774

| Intersil (and design) is a registered trademark of Intersil Americas Inc.

Copyright Intersil Americas Inc. 2007, 2008, 2009. All Rights Reserved

All other trademarks mentioned are the property of their respective owners.

ISL97656

Absolute Maximum Ratings (T

LX to GND . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .26V

IN to GND . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6.5V

COMP, FB, EN, SS, FREQ to GND. . . . . . . . . . .-0.3V to (IN +0.3V)

= +25°C) Thermal Information

A

Thermal Resistance (Typical) θ

10 Ld 3x3 TDFN Package (Notes 1, 2) 53 3

Operating Ambient Temperature . . . . . . . . . . . . . . . .-40°C to +85°C

(°C/W) θJC (°C/W)

JA

Operating Junction Temperature . . . . . . . . . . . . . . . . . . . . . .+135°C

Storage Temperature. . . . . . . . . . . . . . . . . . . . . . . .-65°C to +150°C

Pb-free reflow profile . . . . . . . . . . . . . . . . . . . . . . . . . .see link below

http://www.intersil.com/pbfree/Pb-FreeReflow.asp

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and

result in failures not covered by warranty.

NOTES:

is measured with the component mounted on a high effective thermal conductivity test board in free air. See Tech Brief TB379 for details.

1. θ

JA

2. For θ

IMPORTANT NOTE: All parameters having Min/Max specifications are guaranteed. Typical values are for information purposes only. Unless otherwise noted, all tests

are at the specified temperature and are pulsed tests, therefore: T

Electrical Specifications V

, the “case temp” location is the center of the exposed metal pad on the package underside.

JC

= TC = T

= 3V, V

IN

OUT

J

= 12V, I

A

= 0mA, FREQ = GND, TA = -40°C to +85°C, unless otherwise specified.

OUT

Parameters with MIN and/or MAX limits are 100% tested at +25°C, unless otherwise specified. Temperature

limits established by characterization and are not production tested.

PARAMETER DESCRIPTION CONDITIONS MIN TYP MAX UNIT

I

Q1

I

Q2

I

Q3

V

I

B-FB

FB

Quiescent Current - Shutdown EN = 0V 0.1 5 µA

Quiescent Current - Not Switching EN = IN, FB = 1.3V 0.7 mA

Quiescent Current - Switching EN = IN, FB = 1.0V 3 5 mA

Feedback Voltage 1.22 1.24 1.26 V

Feedback Input Bias Current 0.01 0.5 µA

IN Input Voltage Range 2.3 6.0 V

D

- 640kHz Maximum Duty Cycle FREQ = 0V 85 92 %

MAX

D

- 1.2MHz Maximum Duty Cycle FREQ = IN 85 90 %

MAX

I

LIM

I

EN

r

DS(ON)

I

LX-LEAK

ΔV

/ΔVINLine Regulation 2.3V < VIN < 5.5V, V

OUT

ΔV

/ΔI

OUT

F

OSC1

F

OSC2

V

IL

V

IH

G

M

IN

-ON

Current Limit - Max Peak Input Current 3.8 4.0 5.1 A

Shutdown Input Bias Current EN = 0V 0.01 0.5 µA

Switch ON Resistance IN = 2.7V, ILX = 1A 0.12 Ω

Switch Leakage Current VSW = 27V 0.01 3 µA

= 12V 0.2 %

OUT

Load Regulation VIN = 3.3V , V

OUT

= 12V , IO = 30mA to 200mA 0.3 %

OUT

Switching Frequency Accuracy FREQ = 0V 500 640 740 kHz

Switching Frequency Accuracy FREQ = IN 1000 1220 1500 kHz

EN, FREQ Input Low Level 0.5 V

EN, FREQ Input High Level 1.5 V

Error Amp Tranconductance ΔI = 5µA 70 130 250 1µ/Ω

IN UVLO On Threshold 2.00 2.38 2.57 V

HYS IN UVLO hysteresis 50 mV

I

SS

Soft-Start Charge Current 2.5 4.5 7.5 µA

OTP Over-Temperature Protection 150 °C

2

FN6439.3

April 23, 2009

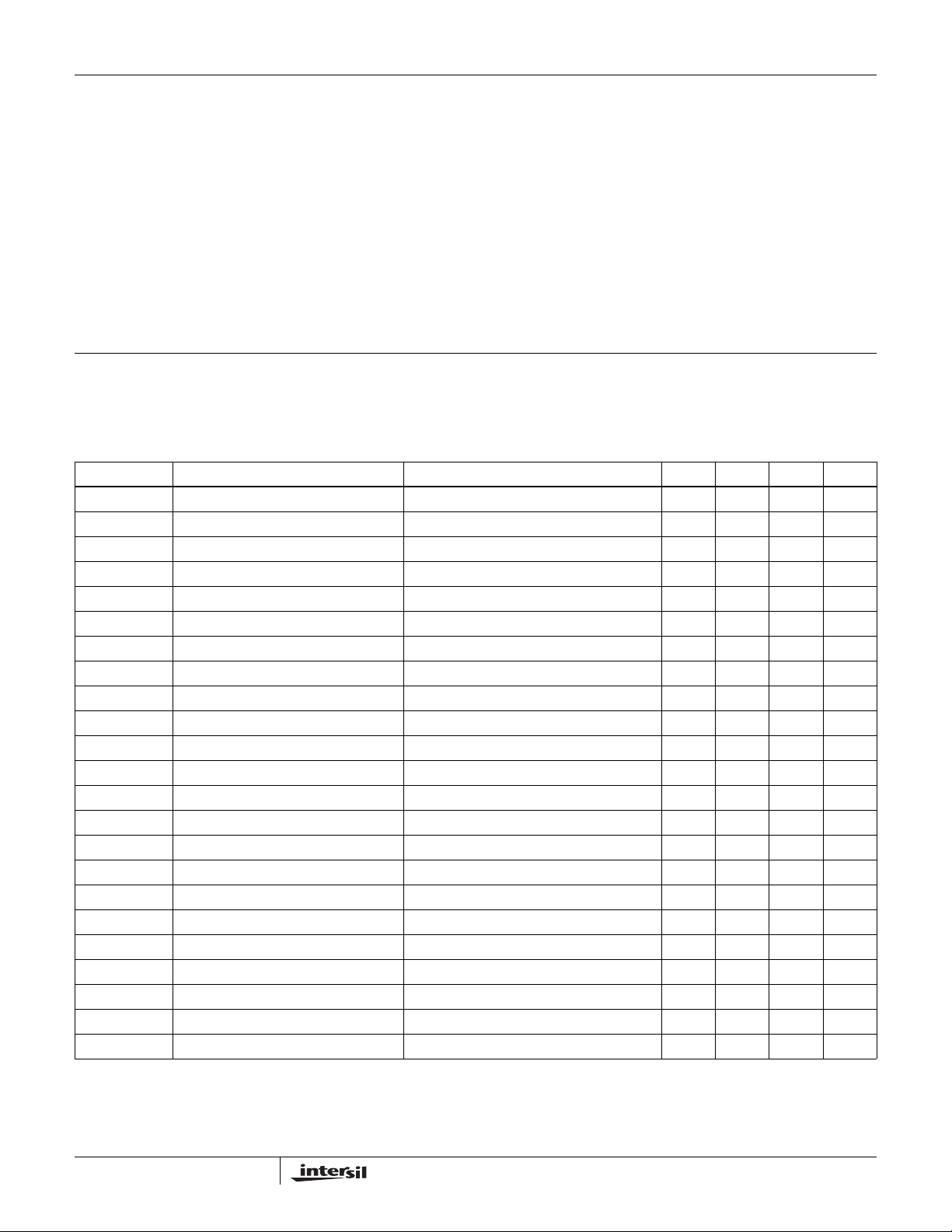

Block Diagram

ISL97656

EN SS

SHUTDOWN

AND START -UP

CONTROL

IN

REFERENCE

GENERATOR

COMPARATOR

COMP

FREQ

OSCILLATOR

CURRENT

SENSE

GM

AMPLIFIER

PWM LOGIC

CONTROLLER

Pin Descriptions

PIN NUMBER PIN NAME DESCRIPTION

FET

DRIVER

LX

GND

FB

1 COMP Compensation pin. Output of the internal error amplifier. Capacitor and resistor from COMP pin to ground.

2 FB Voltage feedback pin. Internal reference is 1.24V nominal. Connect a resistor divider from V

V

= 1.24V (1 + R1/R2). See “Typical Application Circuit”.

OUT

3 EN Shutdown control pin. Pull EN low to turn off the device.

4, 5 GND Analog and power ground.

6, 7 LX Power switch pin. Connected to the drain of the internal power MOSFET.

8 IN A nalog power supply input pin.

9 FREQ Frequency select pin. When FREQ is set low, switching frequency is set to 620kHz. When connected to

high or IN, switching frequency is set to 1.25MHz.

10 SS Soft-start control pin. Connect a capacitor to control the converter start-up.

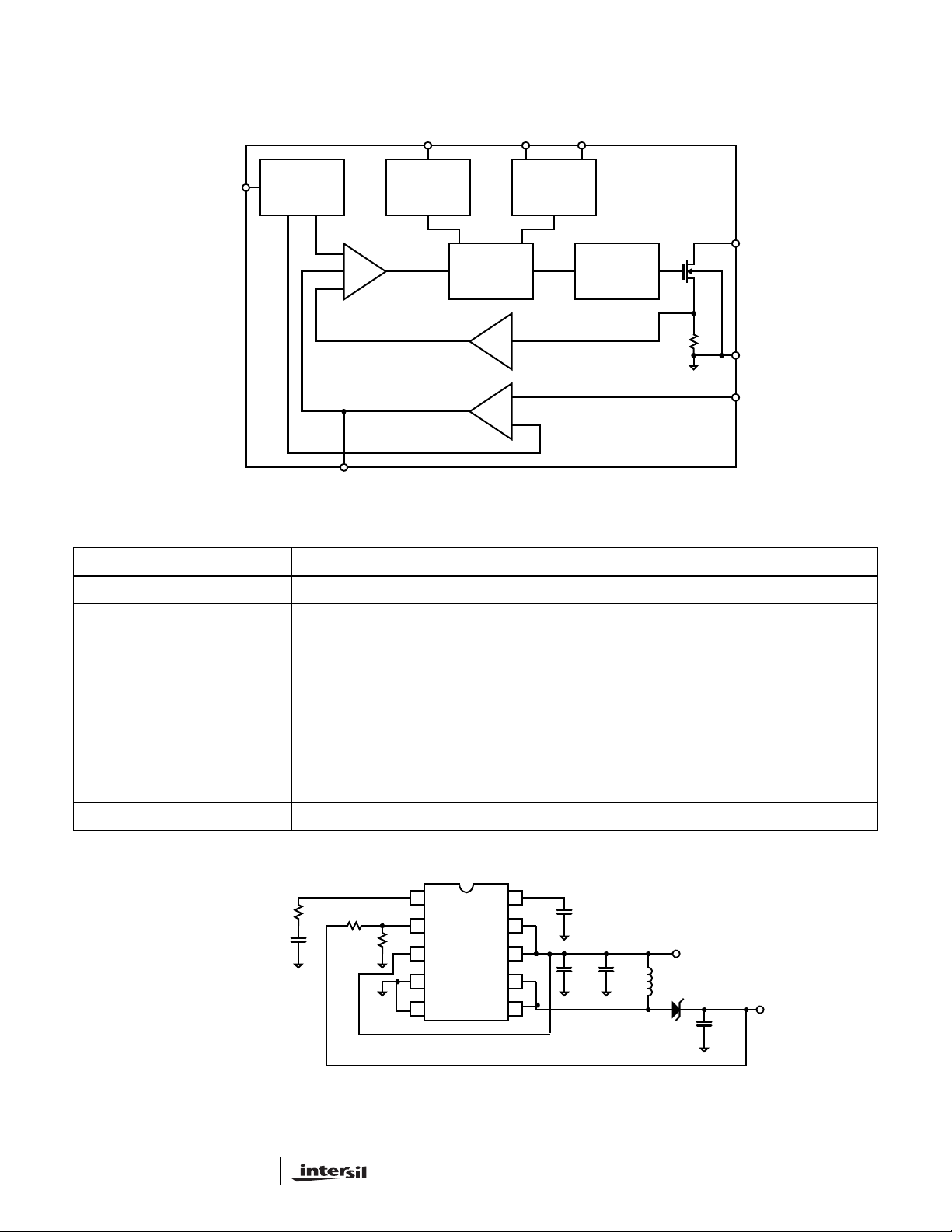

Typical Application Circuit

3.9kΩ

C

4.7nF

1

2

3

4

5

COMP

FB

EN

GND

GND

R

3

5

1

86.6kΩR

R

10kΩ

2

SS

FREQ

LX

LX

10

9

IN

8

7

6

C

3

27nF

C

4

0.1µF

+

C

1

22µF

10µH

D

1

2.3V TO 6.0V

C

+

2

22µF

12V

OUT

.

3

FN6439.3

April 23, 2009

Typical Performance Curves

ISL97656

92

90

88

86

EFFICIENCY (%)

84

82

80

0.4 0.6 0.8 1.0 1.2 1.4 1.6

VIN = 3.0V, VO = 5V

I

OUT (A)

FIGURE 1. 5V BOOST EFFICIENCY vs I

0.9

VIN = 5V, VO = 12V,

0.8

fs = 1.25MHz

0.7

0.6

0.5

0.4

0.3

0.2

LOAD REGULATION (%)

0.1

0

0 200 400 600 800 1000

VIN = 5V, VO = 12V,

= 620kHz

f

s

I

(mA)

OUT

FIGURE 3. LOAD REGULATION vs I

VIN = 4.5V, VO = 5V

V

= 4.0V, VO = 5V

IN

VIN = 3.6V, VO = 5V

VIN = 3.3V, VO = 5V

OUT

VIN = 5V, VO = 9V,

= 1.25MHz

f

s

VIN = 5V, VO = 9V,

= 620kHz

f

s

OUT

96

94

92

90

88

86

EFFICIENCY (%)

84

82

80

0 250 500 750 1000 1250 1500

V

= 3.3V, VO = 9V

IN

I

OUT (mA)

V

= 5.0V, VO = 9V

IN

FIGURE 2. 9V BOOST EFFICIENCY vs I

0.7

VIN = 3.3V, VO = 9V, fs = 1.25MHz

0.6

VIN = 3.3V, VO = 12V, fs = 1.25MHz

0.5

VIN = 3.3, VO = 9V ,

0.4

0.3

0.2

LOAD REGULATION (%)

0.1

0

0 100 200 300 400 500

VIN = 3.3, VO = 12V,

f

s

I

OUT

FIGURE 4. LOAD REGULATION vs I

fs = 1.25kHz

= 620kHz

(mA)

OUT

OUT

0.6

VO = 9V, IO = 80mA

0.5

0.4

0.3

0.2

0.1

LINE REGULATION (%)

0

-0.1

2

= 1.25MHz

f

s

VO = 12V, IO = 80mA

f

= 1.25MHz

s

VO = 9V, IO = 100mA

= 620kHz

f

s

VO = 12V, IO = 80mA

= 620kHz

f

s

3 4 5 6

V

(V)

IN

FIGURE 5. LINE REGULATION vs V

4

I

= 50mA to 300mA

VO = 12V

VIN = 3.3V

IN

FIGURE 6. TRANSIENT RESPONSE

f

= 600kHz

s

O

FN6439.3

April 23, 2009

Typical Performance Curves (Continued)

ISL97656

VO = 12V

= 50mA to 300mA

I

O

VIN = 3.3V

FIGURE 7. TRANSIENT RESPONSE

Applications Information

The ISL97656 is a high frequency, high efficiency boost

regulator operated at constant frequency PWM mode. The

boost converter stores energy from an input voltage source

and deliver it to a higher output voltage. The input voltage

range is 2.3V to 6.0V and output voltage range is 5V to 25V.

The switching frequency is selectable between 640kHz and

1.2MHz allowing smaller inductors and faster transient

response. An external compensation pin gives the user

greater flexibility in setting output transient response and

tighter load regulation. The converter soft-start characteristic

can also be controlled by external C

allows the user to completely shutdown the device.

Boost Converter Operations

Figure 8 shows a boost converter with all the key

components. In steady state operating and continuous

conduction mode where the inductor current is continuous,

the boost converter operates in two cycles. During the first

cycle, as shown in Figure 9, the internal power FET turns on

and the Schottky diode is reverse biased and cuts off the

current flow to the output. The output current is supplied

from the output capacitor. The voltage across the inductor is

V

and the inductor current ramps up in a rate of VIN/L, L is

IN

the inductance. The inductance is magnetized and energy is

stored in the inductor. The change in inductor current is

shown in Equation 1:

V

IN

ΔT1

D

----------

f

SW

---------

×=

L

ΔI

ΔT1

D Duty Cycle=

L1

=

capacitor. The EN pin

SS

= 1.2MHz

f

s

During the second cycle, the power FET turns off and the

Schottky diode is forward biased, (see Figure 10). The

energy stored in the inductor is pumped to the output

supplying output current and charging the output capacitor.

The Schottky diode side of the inductor is clamp to a

Schottky diode above the output voltage. So the voltage

drop across the inductor is V

IN

- V

. The change in

OUT

inductor current during the second cycle is shown in

Equation 2:

ΔT2

=

1D–

-------------

f

SW

×=

------------------------------- -

L

ΔI

L

ΔT2

–

V

INVOUT

For stable operation, the same amount of energy stored in

the inductor must be taken out. The change in inductor

current during the two cycles must be the same as shown in

Equation 3.

ΔI1 ΔI2+ 0=

D

----------

f

SW

V

OUT

--------------- -

V

IN

V

IN

---------

L

1

-------------

=

1D–

V

IN

C

IN

V

1D–

-------------

------------------------------- -

×+× 0=

f

SW

ISL97656

–

INVOUT

L

LD

C

OUT

(EQ. 2)

(EQ. 3)

V

OUT

ΔV

I

OUT

----------------

×=

C

OUT

ΔT

1

O

5

(EQ. 1)

FIGURE 8. BOOST CONVERTER

FN6439.3

April 23, 2009

)

ISL97656

L

V

IN

C

IN

ISL97656

I

L

ΔT

ΔT

1

I

L

2

ΔV

O

FIGURE 9. BOOST CONVERTER - CYCLE 1, POWER

SWITCH CLOSED

LD

V

IN

C

IN

ISL97656

ΔI

L2

FIGURE 10. BOOST CONVERTER - CYCLE 2, POWER

SWITCH OPEN

C

OUT

ΔI

L1

C

OUT

ΔV

O

V

V

OUT

OUT

Output Voltage

An external feedback resistor divider is required to divide the

output voltage down to the nominal 1.24V reference voltage.

The current drawn by the resistor network should be limited

to maintain the overall converter efficiency. The maximum

value of the resistor network is limited by the feedback input

bias current and the potential for noise being coupled into

the feedback pin. A resistor network less than 100k is

recommended. The boost converter output voltage is

determined by the relationship:

R

⎛⎞

V

OUTVFB

1

-------

1

+

×=

⎜⎟

R

⎝⎠

2

(EQ. 4)

:

I

L PEAK()

I

×

OUTVOUT

------------------------------------

V

IN

V

INVOUTVIN

-----------------------------------------------------

12⁄

×+=

LV

OUT

–()×

FREQ××

(EQ. 5)

Output Capacitor

Low ESR capacitors should be used to minimized the output

voltage ripple. Multilayer ceramic capacitors (X5R and X7R)

are preferred for the output capacitors because of their lower

ESR and small packages. Tantalum capacitors with higher

ESR can also be used. The output ripple can be calculated

using Equation 6:

I

D×

ΔV

O

OUT

-------------------------

×

f

SWCO

I

OUT

ESR×+=

(EQ. 6

For noise sensitive application, a 0.1µF placed in parallel

with the larger output capacitor is recommended to reduce

the switching noise coupled from the LX switching node.

Schottky Diode

In selecting the Schottky diode, the reverse break down

voltage, forward current and forward voltage drop must be

considered for optimum converter performance. The diode

must be rated to handle 4.0A, the current limit of the

ISL97656. The breakdown voltage must exceed the

maximum output voltage. Low forward voltage drop, low

leakage current, and fast reverse recovery will help the

converter to achieve the maximum efficiency.

Input Capacitor

The value of the input capacitor depends the input and

output voltages, the maximum output current, the inductor

value and the noise allowed to put back on the input line. For

most applications, a minimum 10µF is required. For

applications that run close to the maximum output current

limit, input capacitor in the range of 22µF to 47µF is

recommended.

The ISL97656 is powered from the VIN. A High frequency

0.1µF bypass capacitor is recommended to be close to the

VIN pin to reduce supply line noise and ensure stable

operation.

The nominal VFB voltage is 1.24V.

Inductor Selection

The inductor selection determines the output ripple voltage,

transient response, output current capability, and ef ficiency.

Its selection depends on the input voltage, output voltage,

switching frequency, and maximum output current. For most

applications, the inductance should be in the range of 2µH to

33µH. The inductor maximum DC current specification must

be greater than the peak inductor current required by the

regulator. The peak inductor current can be calculated using

Equation 5:

6

Loop Compensation

The ISL97656 incorporates a transconductance amplifier in

its feedback path to allow the user some adjustment on the

transient response and better regulation. The ISL97656

uses current mode control architecture which has a fast

current sense loop and a slow voltage feedback loop. The

fast current feedback loop does not require any

compensation. The slow voltage loop must be compensated

for stable operation. The compensation network is a series

RC network from COMP pin to ground. The resistor sets the

high frequency integrator gain for fast transient response

and the capacitor sets the integrator zero to ensure loop

stability. For most applications, the compensation resistor in

the range of 0k to 2.0k and the compensation capacitor in

the range of 3nF to 10nF.

FN6439.3

April 23, 2009

ISL97656

Soft-Start

The soft-start is provided by an internal 4.5µA current source

charges the external C

, the peak MOSFET current is

SS

limited by the voltage on the capacitor. This in turn controls

the rising rate of the output voltage. The regulator goes

through the start-up sequence as well after the EN pin is

pulled to HI.

Frequency Selection

The ISL97656 switching frequency can be user selected to

operate at either constant 640kH z or 1.25MHz. Connecting

FREQ pin to ground sets the PWM switching frequency to

640kHz. When connecting FREQ high or IN, the switching

frequency is set to 1.2MHz.

Shutdown Control

When the EN pin is pulled down, the ISL97656 is shutdown

reducing the supply current to <1µA.

Maximum Output Current

The MOSFET current limit is nominally 4.0A and guaranteed

3.0A. This restricts the maximum output current, I

based on Equation 7:

LILAVG()

12⁄ΔIL×()+=

OMAX

,

(EQ. 7)

TABLE 1. TYPICAL MAXIMUM I

(V) V

V

IN

2.5 5 1790

2.5 9 990

2.5 12 750

3.3 5 2370

3.3 9 1300

3.3 12 970

5 9 1970

5 12 1470

(V) I

OUT

OUT

VALUES

OMAX

(mA)

Cascaded MOSFET Application

A 24V N-Channel MOSFET is integrated in the boost

regulator. For the applications where the output voltage is

greater than 24V, an external cascaded MOSFET is needed

as shown in Figure 11. The voltage rating of the external

MOSFET should be greater than A

V

IN

IN

.

A

IN

where:

I

= MOSFET current limit

L

I

= average inductor current

L(AVG)

ΔIL = inductor ripple current

V

VOV

( V

I

OUT

------------1D–

+()VIN–[]×

DIODE

DIODE

) fS×+×

O

IN

------------------------------------------------------------------------------

=

ΔI

L

LV

V

f

I

= Schottky diode forward voltage, typically, 0.6V

DIODE

= switching frequency, 600kHz or 1.2MHz

S

=

L-AVG

D = MOSFET turn-on ratio:

D1

Table 1 gives typical maximum I

V

+

OUTVDIODE

values for 1.2MHz

OUT

V

IN

--------------------------------------------

–=

switching frequency and 10µH inductor.

(EQ. 8)

(EQ. 9)

(EQ. 10)

LX

INTERSIL

ISL97656

FIGURE 11. CASCADED MOSFET TOPOLOGY FOR HIGH

OUTPUT VOLTAGE APPLICATIONS

FB

DC PATH BLOCK APPLICATION

Note that there is a DC path in the boost converter from the

input to the output through the inductor and diode, hence the

input voltage will be seen at output with a forward voltage

drop of diode before the part is enabled. If this voltage is not

desired, the following circuit (see Figure 12) can be inserted

between input and inductor to disconnect the DC path when

the part is disabled.

TO INDUCTOR

INPUT

EN

FIGURE 12. CIRCUIT TO DISCONNECT THE DC PA TH OF

BOOST CONVERTER

7

FN6439.3

April 23, 2009

ISL97656

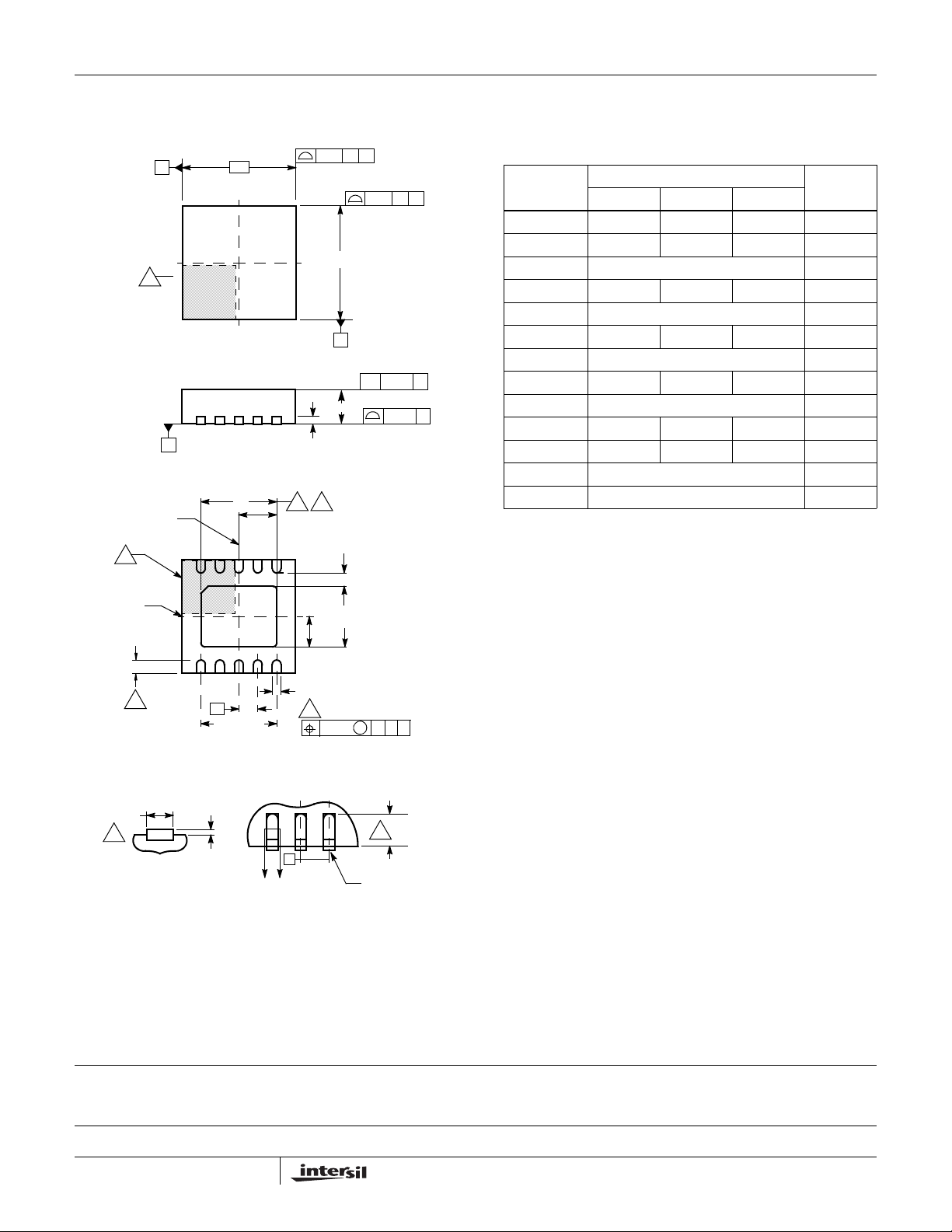

Thin Dual Flat No-Lead Plastic Package (TDFN)

(DATUM B)

6

INDEX

AREA

(DATUM A)

NX (b)

5

SECTION "C-C"

6

INDEX

AREA

SEATING

PLANE

NX L

8

A

C

D

TOP VIEW

SIDE VIEW

D2

D2/2

12

N

N-1

e

(Nd-1)Xe

REF.

BOTTOM VIEW

(A1)

2X

A3

E2/2

NX b

5

C

L

e

CC

FOR ODD TERMINAL/SIDE

E

A

87

NX k

E2

0.10

ABC0.15

2X

0.15

//

M

9

TERMINAL TIP

0.10

0.08

L

CB

C

BAC

L10.3x3B

10 LEAD THIN DUAL FLAT NO-LEAD PLASTIC PACKAGE

MILLIMETERS

SYMBOL

A

A1

A3

b

D

D2

E

E2

C

e

k

L

0.70 0.75 0.80

- - 0.05

0.20 REF

0.18 0.25 0.30

3.00 BSC

2.23 2.38 2.48

3.00 BSC

1.49 1.64 1.74

0.50 BSC

0.20 - -

0.30 0.40 0.50

N102

Nd 5 3

NOTES:

1. Dimensioning and tolerancing conform to ASME Y14.5-1994.

2. N is the number of terminals.

3. Nd refers to the number of terminals on D.

4. All dimensions are in millimeters. Angles are in degrees.

5. Dimension b applies to the metallized terminal and is measured

between 0.15mm and 0.30mm from the terminal tip.

6. The configuration of the pin #1 identifier is optional, but must be

located within the zone indicated. The pin #1 identi fier may be

either a mold or mark feature.

7. Dimensions D2 and E2 are for the exposed pads which provide

improved electrical and thermal performance.

8. Nominal dimensions are provided to assist with PCB Land

Pattern Design efforts, see Intersil Technical Brief TB389.

9. COMPLIANT TO JEDEC MO-229-WEED-3 except for

dimensions E2 & D2.

NOTESMIN NOMINAL MAX

-

-

-

5, 8

-

7, 8

-

7, 8

-

-

8

Rev. 0 2/06

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems.

Intersil Corporation’s quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without

notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and

reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result

from its use. No license is granted by implicat ion or oth erwise u nde r any p a tent or p at ent r ights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com

8

FN6439.3

April 23, 2009

Loading...

Loading...