Intersil ISL95836HRTZ, ISL95836IRTZ Schematic [ru]

PRELIMINARY

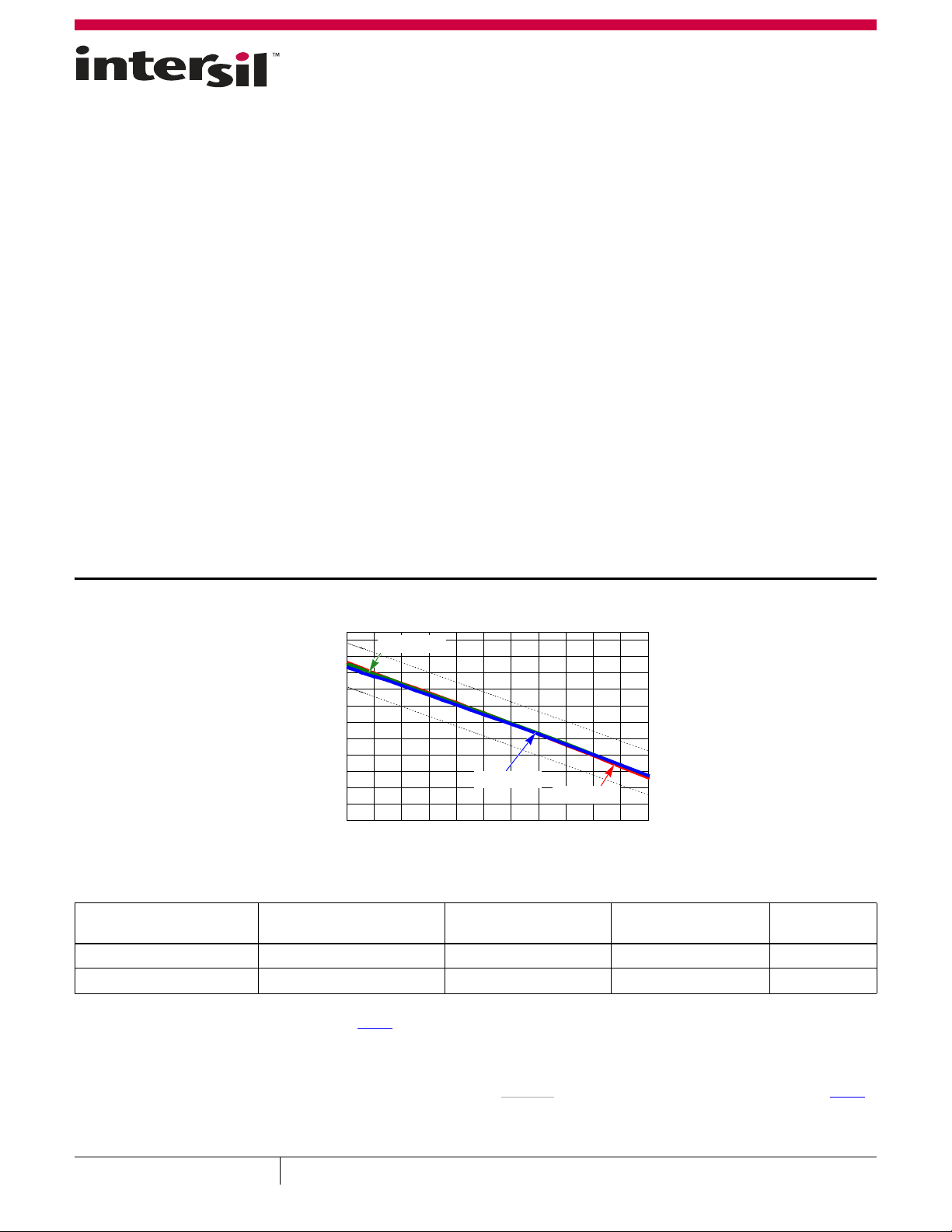

0.80

0.81

0.82

0.83

0.84

0.85

0.86

0.87

0.88

0.89

0.90

0.91

30 36 42 48 54 60 66

I

OUT

(A)

V

OUT

(V)

0 6 12 18 24

VIN = 19V

VIN = 12V

VIN = 8V

3+2 Voltage Regulator for IMVP-7/VR12™ CPUs

ISL95836

Compliant with IMVP-7/VR12™, the ISL95836 provides a

complete solution for microprocessor and graphic processor

core power supply. It provides two Voltage Regulators (VRs)

with three integrated gate drivers. The first VR can be

configured as 3-, 2- or 1-phase VR while the second VR could

be configured as 2- or 1-phase VR, providing maximum

flexibility. The two VRs share the serial control bus to

communicate with the CPU and achieve lower cost and smaller

board area compared with the two-chip approach.

Based on Intersil’s Robust Ripple Regulator (R3) technology™,

the PWM modulator compared to traditional modulators, has

faster transient settling time, variable switching frequency

during load transients and has improved light load efficiency

with it’s ability to automatically change switching frequency.

The ISL95836 has several other key features. Both outputs

support DCR current sensing with single NTC thermistor for

DCR temperature compensation or accurate resistor current

sensing. Both outputs come with remote voltage sense,

programmable V

adjustable OC protection and separate Power-Good.

PRELIMINARY

CONFIDENTIAL

BOOT

voltage, I

and switching frequency,

MAX

IN REVIEW

Load Line Regulation

Features

•Serial Data Bus

•Dual Outputs:

- Configurable 3-, 2- or 1-phase for the 1st Output using 2

integrated Gate Drivers

- Configurable 2- or 1-phase for the 2nd Output using an

Integrated Gate Driver

• 0.5% System Accuracy Over-Temperature

• Supports Multiple Current Sensing Methods

- Lossless Inductor DCR Current Sensing

- Precision Resistor Current Sensing

• Differential Remote Voltage Sensing

•Programmable V

• Resistor Programmable I

Outputs

• Adaptive Body Diode Conduction Time Reduction

Voltage at Start-up

BOOT

MAX

, Switching Frequency for Both

Applications

• IMVP-7/VR12 Compliant Computers

Ordering Information

PART NUMBER

(Notes 1, 2, 3) PART MARKING

ISL95836HRTZ 95836 HRTZ -10 to +100 40 Ld 5x5 TQFN L40.5x5

ISL95836IRTZ 95836 IRTZ -40 to +100 40 Ld 5x5 TQFN L40.5x5

NOTES:

1. Add “-T*” suffix for tape and reel. Please refer to TB347

2. These Intersil Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte

tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Intersil Pbfree products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

3. For Moisture Sensitivity Level (MSL), please see device information page for ISL95836

THIS IS A PRE-DEVELOPMENT PRELIMINARY DATASHEET. DEVICE FUNCTIONALITY AND SPECIFICATIONS ARE SUBJECT TO CHANGE

March 12, 2011

FN7835.0

1

for details on reel specifications.

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 1-888-468-3774

TEMP. RANGE

(°C)

. For more information on MSL please see techbrief TB363.

Intersil (and design) is a trademark owned by Intersil Corporation or one of its subsidiaries.

All other trademarks mentioned are the property of their respective owners.

|Copyright Intersil Americas Inc. 2011. All Rights Reserved

PACKAGE

(Pb-Free)

PKG.

DWG. #

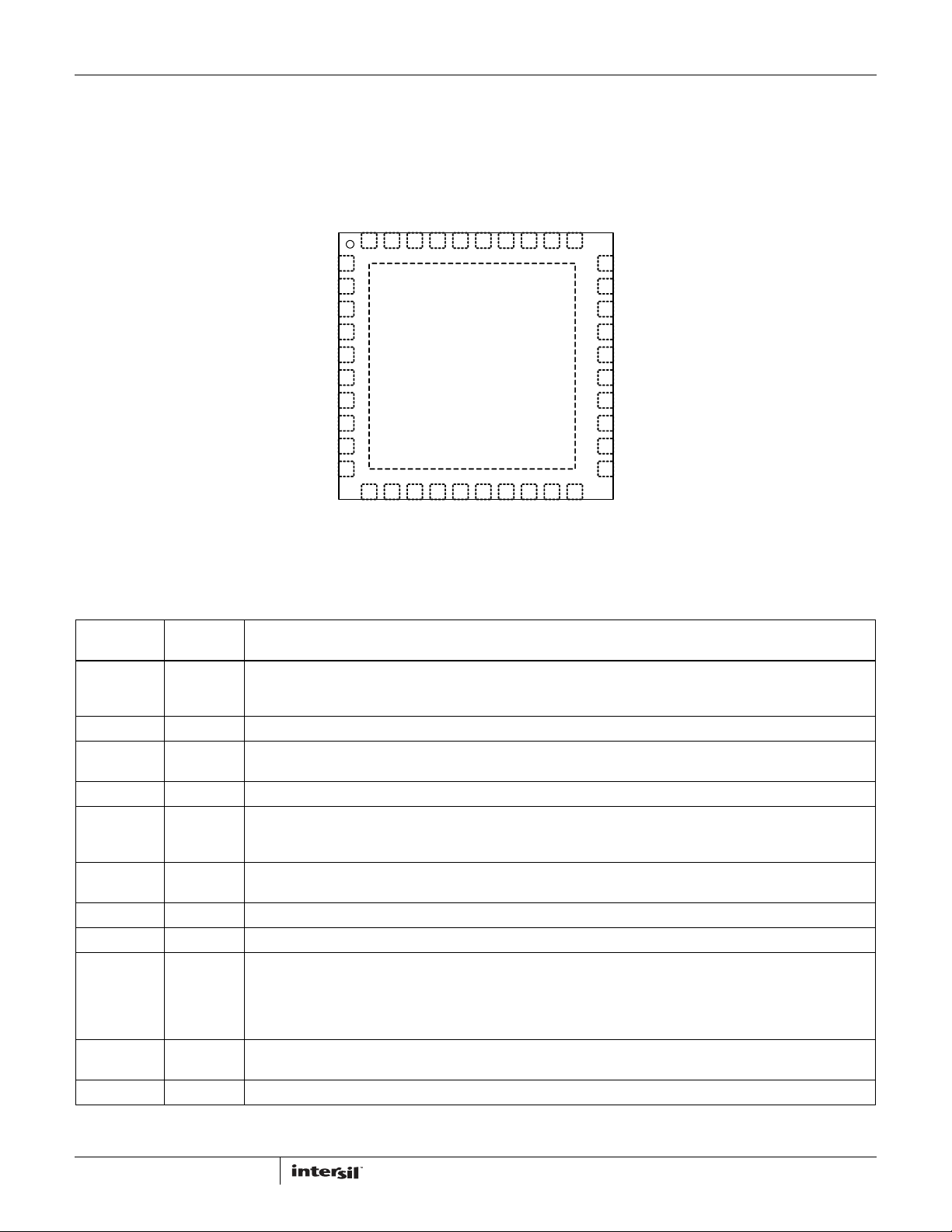

Pin Configuration

GND PAD

(BOTTOM)

40 39 38 37 36 35 34 33 32 31

29

30

27

28

25

26

23

24

21

22

11 12 13 14 15 16 17 18 19 20

2

1

4

3

6

5

8

7

10

9

NTCG

SCLK

ALERT#

SDA

VR_HOT#

VR_ON

NTC

ISEN2

ISEN1

ISUMP

ISUMN

RTN

FB

COMP

UGATE2

LGATE2

PWM3

LGATE1

FBG

COMPG

PGOODG

PWM2G

LGATE1G

PGOOD

PHASE2

VDD

BOOT2

ISEN2G

PHASE1

UGATE1

PHASE1G

RTNG

ISUMNGISEN3/FB2

UGATE1G

ISEN1G

ISUMPG

BOOT1 BOOT1G

VCCP

CONFIDENTIAL

ISL95836

ISL95836

(40 LD TQFN)

TOP VIEW

IN REVIEW

Pin Descriptions

ISL95836

PIN NUMBER SYMBOL DESCRIPTION

BOTTOM

PAD

2 ISEN1G Individual current sensing for VR2 Phase 1.

3 ISEN2G Individual current sensing for VR2 Phase 2. When ISEN2 is pulled to 5V VDD, the controller will

4 NTCG The second thermistor input to VR_HOT# circuit. Use it to monitor VR2 temperature.

5, 6, 7 SCLK,

8 VR_HOT# Open drain thermal overload output indicator. Can be considered part of communication bus with

9 VR_ON Controller enable input. A high level logic signal on this pin enables the controller.

10 NTC One of the thermistor inputs to VR_HOT# circuit. Use it to monitor VR1 temperature.

11 INSE3/FB2 When the VR1 is configured in 3-phase mode, this pin is ISEN3. ISEN3 is the individual current

12 ISEN2 Individual current sensing for VR1 Phase 2. When ISEN2 and PWM3 are both pulled to 5V VDD, the

13 ISEN1 Individual current sensing for VR1 Phase 1.

GND Signal common of the IC. Unless otherwise stated, signals are referenced to the GND pin. In

addition, it is the return path for all the low-side MOSFET gate drivers. It should also be used as the

thermal pad for heat removal.

disable VR2 Phases 2.

ALERT#,

SDA

Communication bus between the CPU and the VRs.

CPU.

sensing for VR1 phase 3. When VR1 is configured in 2-phase mode, this pin is FB2. There is a switch

between the FB2 pin and the FB pin. The switch is on when VR1 is in 2-phase mode and is off in 1phase mode. The components connecting to FB2 are used to adjust the compensation in 1-phase

mode to achieve optimum performance for VR1.

controller will disable VR1 Phases 3 and 2.

2

FN7835.0

March 12, 2011

ISL95836

Pin Descriptions (Continued)

ISL95836

PIN NUMBER SYMBOL DESCRIPTION

14, 15 ISUMP and

ISUMN

16 RTN VR1 remote voltage sensing return.

17 FB This pin is the inverting input of the error amplifier for VR1.

18 COMP This pin is the output of the error amplifier for VR1. Also, aresistor from this pin to GND programs

19 PGOOD Power-Good open-drain output indicating when VR1 is able to supply regulated voltage. Pull up

20 BOOT1 Connect an MLCC capacitor across the BOOT1 and the PHASE1 pins. The boot capacitor is charged

21 UGATE1 Output of VR1 Phase-1 high-side MOSFET gate driver. Connect the UGATE1 pin to the gate of the

22 PHASE1 Current return path for the VR1 Phase-1 high-side MOSFET gate driver. Connect the PHASE1 pin to

CONFIDENTIAL

23 LGATE1 Output of VR1 Phase-1 low-side MOSFET gate driver. Connect the LGATE1 pin to the gate of VR1

24 PWM3 PWM output for VR1 Phase 3. When PWM3 is pulled to 5V VDD, the controller will disable VR1 Phase

25 VDD 5V bias power.

26 VCCP Input voltage bias for the internal gate drivers. Connect +5V to the VCCP pin. Decouple with at least

27 LGATE2 Output of VR1 Phase-2 low-side MOSFET gate driver. Connect the LGATE2 pin to the gate of VR1

28 PHASE2 Current return path for VR1 Phase-2 high-side MOSFET gate driver. Connect the PHASE2 pin to the

29 UGATE2 Output of VR1 Phase-2 high-side MOSFET gate driver. Connect the UGATE2 pin to the gate of VR1

30 BOOT2 Connect an MLCC capacitor across the BOOT2 and the PHASE2 pins. The boot capacitor is charged

31 BOOT1G Connect an MLCC capacitor across the BOOTG and the PHASE1G pins. The boot capacitor is charged

32 UGATE1G Output of VR2 Phase-1 high-side MOSFET gate driver. Connect the UGATE1G pin to the gate of VR2

33 PHASE1G Current return path for VR2 Phase-1 high-side MOSFET gate driver. Connect the PHASEG pin to the

34 LGATE1G Output of VR2 Phase-1 low-side MOSFET gate driver. Connect the LGATE1G pin to the gate of VR2

35 PWM2G PWM output for VR2 Phase 2.

36 PGOODG Power-Good open-drain output indicating when VR2 is able to supply regulated voltage. Pull up

37 COMPG This pin is the output of the error amplifier for VR2. Also, aresistor from this pin to GND programs

VR1 droop current sense input.

Imax for VR1, and Vboot for both VR1 and VR2.

externally with a 680 resistor to VCCP or 1.9k to 3.3V.

through an internal boot diode connected from the VCCP pin to the BOOT1 pin, each time the PHASE1

pin drops below VCCP minus the voltage dropped across the internal boot diode.

Phase-1 high-side MOSFET.

the node consisting of the high-side MOSFET source, the low-side MOSFET drain, and the output

inductor of VR1 Phase 1.

Phase-1 low-side MOSFET.

3.

IN REVIEW

1µF of an MLCC capacitor.

Phase-2 low-side MOSFET.

node consisting of the high-side MOSFET source, the low-side MOSFET drain, and the output inductor

of VR1 Phase 2.

Phase-2 high-side MOSFET.

through an internal boot diode connected from the VCCP pin to the BOOT2 pin, each time the PHASE2

pin drops below VCCP minus the voltage dropped across the internal boot diode.

through an internal boot diode connected from the VCCP pin to the BOOT1G pin, each time the

PHASEG pin drops below VCCP minus the voltage dropped across the internal boot diode.

Phase-1 high-side MOSFET.

node consisting of the high-side MOSFET source, the low-side MOSFET drain, and the output inductor

of VR2 Phase 1.

Phase-1 low-side MOSFET.

externally with a 680 resistor to VCCP or 1.9k to 3.3V.

Imax for VR2 and Tmax for both VR1 and VR2.

3

FN7835.0

March 12, 2011

ISL95836

Pin Descriptions (Continued)

ISL95836

PIN NUMBER SYMBOL DESCRIPTION

38 FBG This pin is the inverting input of the error amplifier for VR2.

39 RTNG VR2 remote voltage sensing return.

40, 1 ISUMNG

and

ISUMPG

VR2 droop current sense input. When ISUMNG is pulled to 5V VDD, all the communication to VR2 is

disabled.

CONFIDENTIAL

IN REVIEW

4

FN7835.0

March 12, 2011

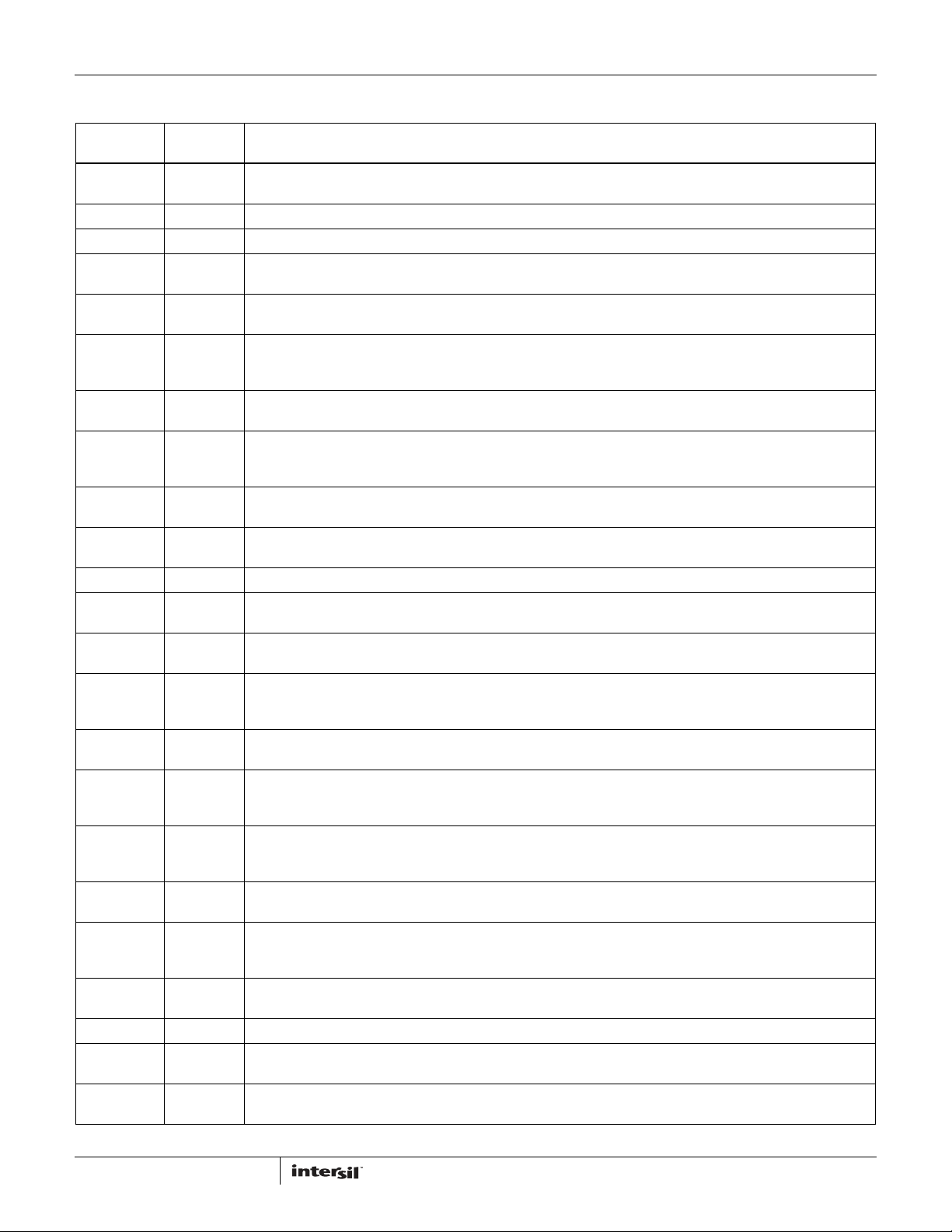

Block Diagram

RTN

E/A

FB

IDROOP

CURRENT

SENSE

ISUMP

ISUMN

COMP

DRIVER

DRIVER

LGATE1

PHASE1

UGATE1

BOOT1

VCCP

OV FAULT

PGOOD

_

+

_

+

+

+

DRIVER

DRIVER

LGATE2

PHASE2

UGATE2

BOOT2

IBAL FAULT

OC FAULT

PWM3

ISEN3/FB2

ISEN2

ISEN1

CURRENT

BALANCING

DIGITAL

INTERFACE

SDA

ALERT#

SCLK

DRIVER

DRIVER

LGATE1G

PHASE1G

UGATE1G

BOOT1G

OV FAULT

PGOODG

OC FAULT

MODE1

DAC1

MODE2

DAC2

TEMP

MONITOR

NTCG

NTC

VR_HOT#

T_MONITOR

IMAX

VBOOT

TMAX

SET (A/D)

PROG

VR_ON

MODE

D/A

A/D IDROOP

IDROOPG

VREADY

RTNG

E/A

FBG

IDROOPG

CURRENT

SENSE

ISUMPG

ISUMNG

COMPG

VR2

MODULATOR

_

+

_

+

+

+

VR1

MODULATOR

FB2

CIRCUIT

VDD

GND

ISEN1G

ISEN2G

CURRENT

BALANCING

IBAL FAULT

PWM2G

ISL95836

CONFIDENTIAL

IN REVIEW

5

FN7835.0

March 12, 2011

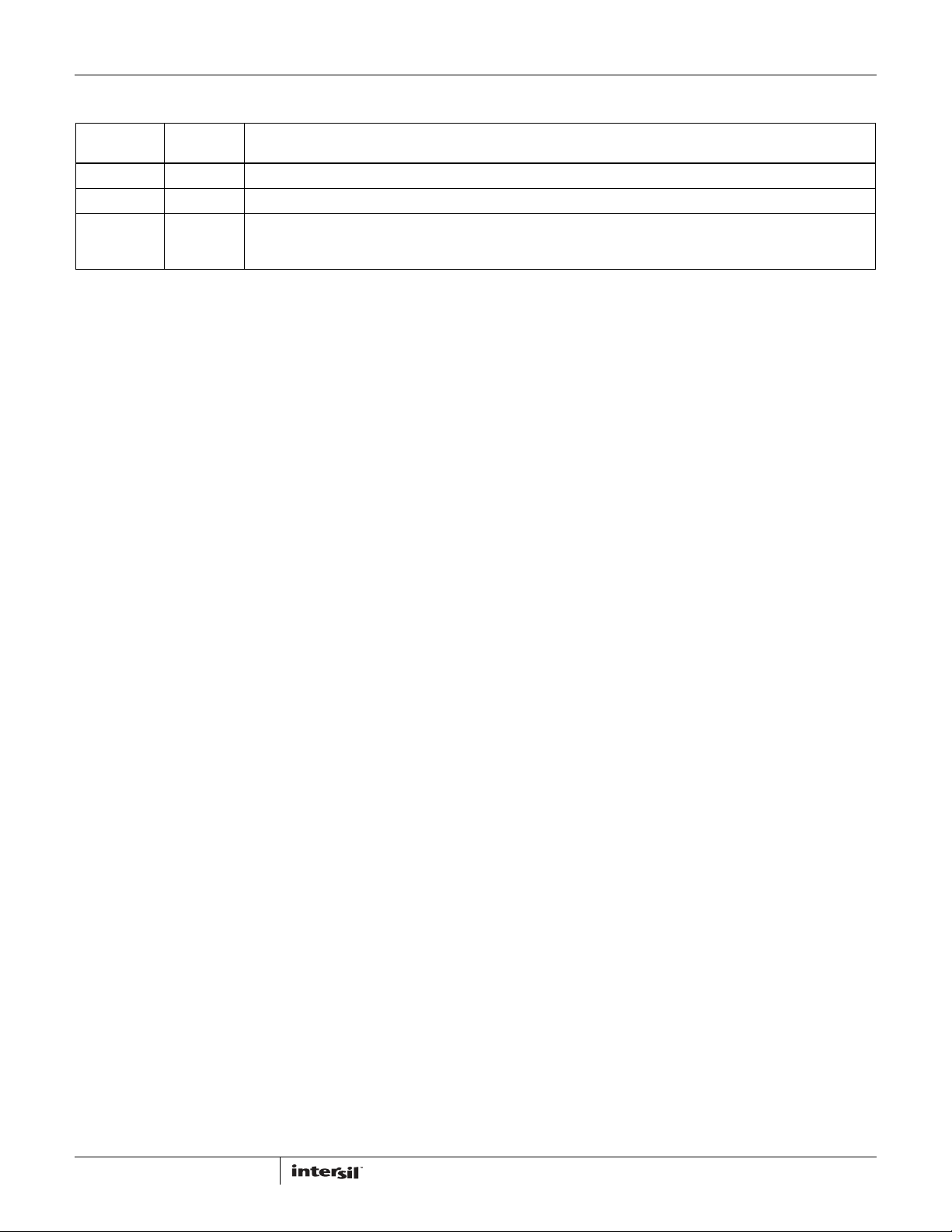

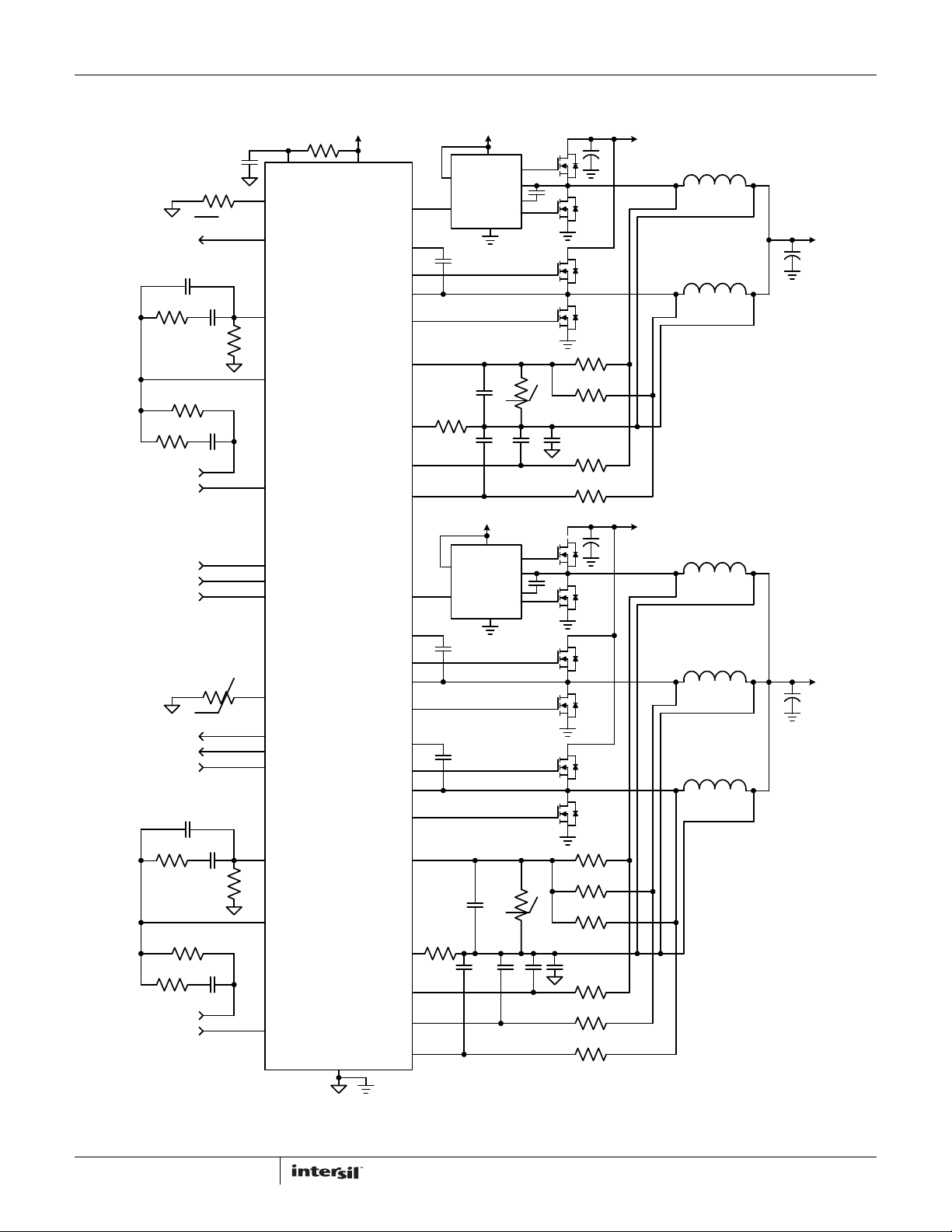

Simplified Application Circuit

FIGURE 1. TYPICAL ISL95836 APPLICATION CIRCUIT USING INDUCTOR DCR SENSING

NTCG

GND

VCCP

V+5

ISL95836

L2

L1

ISEN3/FB2

PHASE2

UGATE2

Rsum2

Rsum1

Rn

Cn

Ri

L3

Rsum3

BOOT2

V+5

Vin

LGATE2

ISEN2

PHASE1

UGATE1

BOOT1

LGATE1

PWM3

ISUMP

ISUMN

o

C

Risen2

Risen1

Risen3

ISEN1

Vsumn

Cisen3Cisen2Cisen1

Cvsumn

L4

GT Vcore

ISEN2G

UGATE1G

Rsum4

Rng

Cng

Rig

L5

Rsum5

BOOT1G

V+5

Vin

LGATE1G

ISEN1G

PWM2G

ISUMPG

ISUMNG

o

C

Risen4

Risen5

Vsumng

Cisen4

Cisen5

Cvsumng

CPU Vcore

PHASE1G

VDD

Rdroop

VR_ON

PGOOD

VSSSENSE

VCCSENSE

Rntc

o

C

FB

VR_ON

COMP

RTN

PGOOD

NTC

Rdroopg

VSSSENSEG

VCCSENSEG

Rntcg

o

C

FBG

COMPG

RTNG

SDA SDA

ALERT# ALERT#

SCLK SCLK

PGOODG PGOODG

VR_HOT# VR_HOT#

Rprog2

Rprog1

VCC

UGATE

LGATE

PHASE

BOOT

PWM

FCCM

GND

ISL6208

VCC

UGATE

LGATE

PHASE

BOOT

PWM

FCCM

GND

ISL6208

ISL95836

CONFIDENTIAL

IN REVIEW

6

FN7835.0

March 12, 2011

ISL95836

Table of Contents

Load Line Regulation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

Pin Descriptions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

Simplified Application Circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

Absolute Maximum Ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Thermal Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Recommended Operating Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Electrical Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Gate Driver Timing Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Theory of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Multiphase R3™ Modulator. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Diode Emulation and Period Stretching . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Start-up Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Voltage Regulation and Load Line Implementation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Differential Voltage Sensing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Phase Current Balancing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

CCM Switching Frequency . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .19

Dynamic Operation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

VR_HOT#/ALERT# Behavior . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

FB2 Function . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Adaptive Body Diode Conduction Time Reduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21

Protections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21

Supported Data And Configuration Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Key Component Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Inductor DCR Current-Sensing Network . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Resistor Current-Sensing Network . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Overcurrent Protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25

Compensator. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

Programming Resistors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .27

Current Balancing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .27

Slew Rate Compensation Circuit For VID Transition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .28

Layout Guidelines . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Package Outline Drawing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

Products . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

CONFIDENTIAL

IN REVIEW

7

FN7835.0

March 12, 2011

ISL95836

Absolute Maximum Ratings Thermal Information

Supply Voltage, VDD. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -0.3V to +7V

Battery Voltage, VIN . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . +28V

Boot Voltage (BOOT). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -0.3V to +33V

Boot-to-Phase Voltage

(BOOT-PHASE) -0.3V to +7V(DC) . . . . . . . . . . . . . . -0.3V to +9V(<10ns)

Phase Voltage (PHASE) . . . . . . . . . . . . . . . . -7V (<20ns Pulse Width, 10µJ)

UGATE Voltage (UGATE) . . . . . . . . . . . . . . . . . . . PHASE - 0.3V (DC) to BOOT

. . . . . . . . . . . . . . . . . . . . PHASE - 5V (<20ns Pulse Width, 10µJ) to BOOT

LGATE Voltage

. . . . . . . . . . . . . . . . . . . . . . . . -2.5V (<20ns Pulse Width, 5µJ) to VDD+0.3V

All Other Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -0.3V to (VDD +0.3V)

Open Drain Outputs, PGOOD, VR_HOT#, ALERT#. . . . . . . . . . -0.3V to +7V

ESD Rating

Human Body Model (Tested per JESD22-A114E). . . . . . . . . . . . . . . . 2kV

Machine Model (Tested per JESD22-A115-A) . . . . . . . . . . . . . . . . . 200V

Charged Device Model (Tested per JESD22-C101A) . . . . . . . . . . . . . . 1k

Latch Up (Tested per JESD-78B; Class 2, Level A) . . . . . . . . . . . . . . 100mA

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product

reliability and result in failures not covered by warranty.

NOTES:

4.

Brief TB379.

5. For

CONFIDENTIAL

is measured in free air with the component mounted on a high effective thermal conductivity test board with “direct attach” features. See Tech

JA

, the “case temp” location is the center of the exposed metal pad on the package underside.

JC

Thermal Resistance (Typical)

40 Ld TQFN Package (Notes 4, 5) . . . . . . . 29 1

Maximum Junction Temperature . . . . . . . . . . . . . . . . . . . . . . . . . . . .+150°C

Maximum Storage Temperature Range . . . . . . . . . . . . . .-65°C to +150°C

Maximum Junction Temperature (Plastic Package) . . . . . . . . . . . .+150°C

Storage Temperature Range. . . . . . . . . . . . . . . . . . . . . . . .-65°C to +150°C

Pb-Free Reflow Profile . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . see link below

http://www.intersil.com/pbfree/Pb-FreeReflow.asp

(°C/W) JC (°C/W)

JA

Recommended Operating Conditions

Supply Voltage, VDD. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . +5V ±5%

Battery Voltage, VIN . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . +4.5V to 25V

Ambient Temperature

HRTZ. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -10°C to +100°C

IRTZ . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .-40°C to +100°C

Junction Temperature

HRTZ. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .-10°C to +125°C

IRTZ . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .-40°C to +125°C

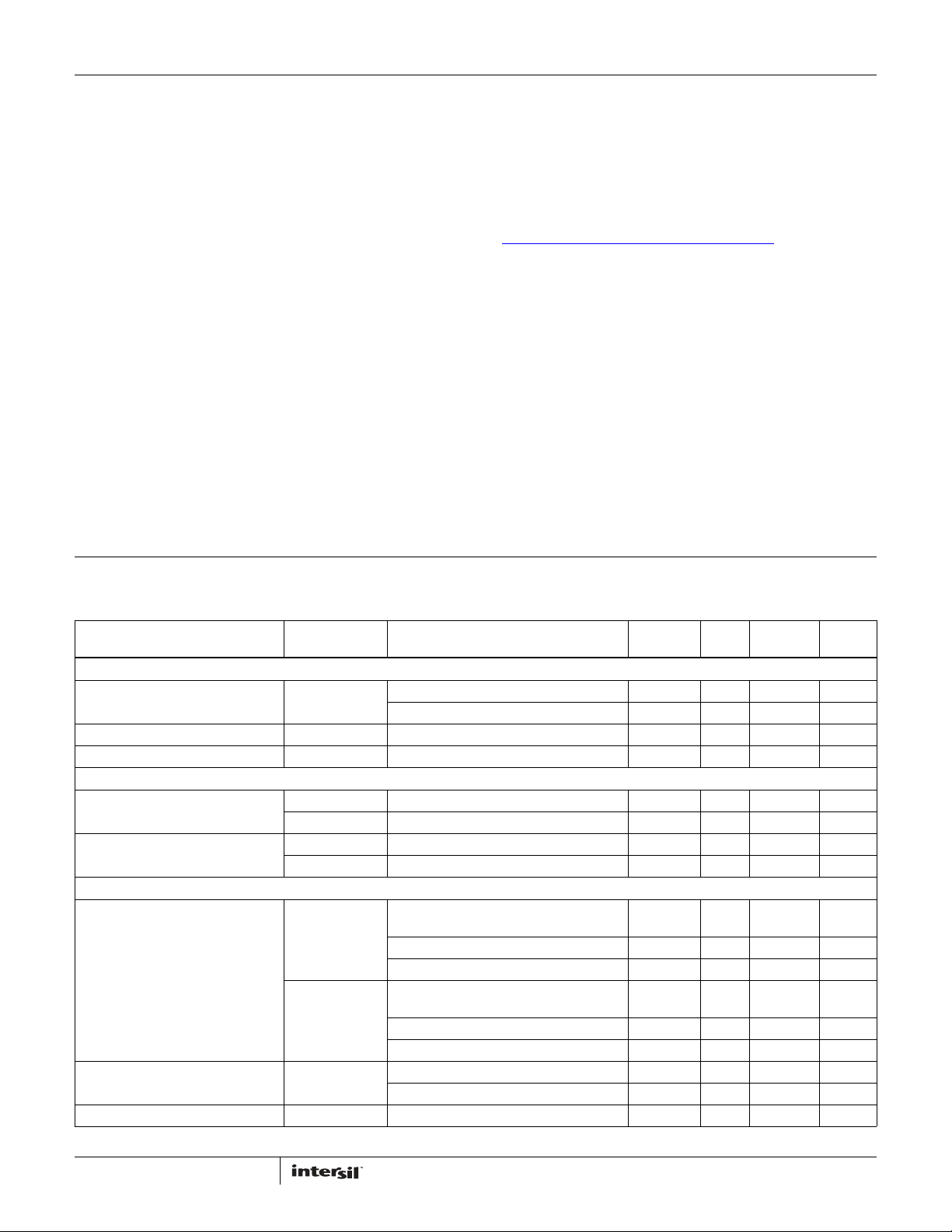

Electrical Specifications "Operating Conditions: VDD = 5V, T

(ISL95836HRTZ), fSW = 300kHz, unless otherwise noted." Boldface limits apply over the operating temperature ranges, -10°C to +100°C or

-40°C to +100°C.

PARAMETER SYMBOL TEST CONDITIONS

INPUT POWER SUPPLY

+5V Supply Current I

Battery Supply Current I

Input Resistance R

V

IN

POWER-ON-RESET THRESHOLDS

VDD Power-On-Reset Threshold VDDPOR

VIN Power-On-Reset Threshold VINPOR

SYSTEM AND REFERENCES

System Accuracy HRTZ

Internal V

Maximum Output Voltage V

BOOT

IN REVIEW

VDD

VIN

VIN

VDDPOR

VINPOR

%Error (V

IRTZ

%Error (V

OUT(max)

VR_ON = 1V 5 mA

VR_ON = 0V 1 µA

VR_ON = 0V 1 µA

VR_ON = 1V 550 k

VDD rising 4.35 4.5 V

r

VDD falling 4.00 4.15 V

f

VIN rising 4.00 4.35 V

r

VIN falling 2.8 3.3 V

f

No load; closed loop, acti ve mode ra ng e, VID

= 0.75V to 1.52V, -0.5 +0.5 %

OUT)

VID = 0.5V to 0.745V -8 +8 mV

VID = 0.25V to 0.495V -15 +15 mV

No load; closed loop, acti ve mode ra ng e, VID

)

= 0.75V to 1.52V -0.8 +0.8 %

OUT

VID = 0.5V to 0.745V -10 +10 mV

VID = 0.25V to 0.495V -18 +18 mV

HRTZ 1.0945 1.100 1.1055 V

IRTZ 1.0912 1.100 1.1088 V

VID = [11111111] 1.52 V

= -40°C to +100°C (ISL95836IRTZ), TA = -10°C to +100°C

A

MIN

(Note 6) TYP

MAX

(Note 6) UNITS

8

FN7835.0

March 12, 2011

ISL95836

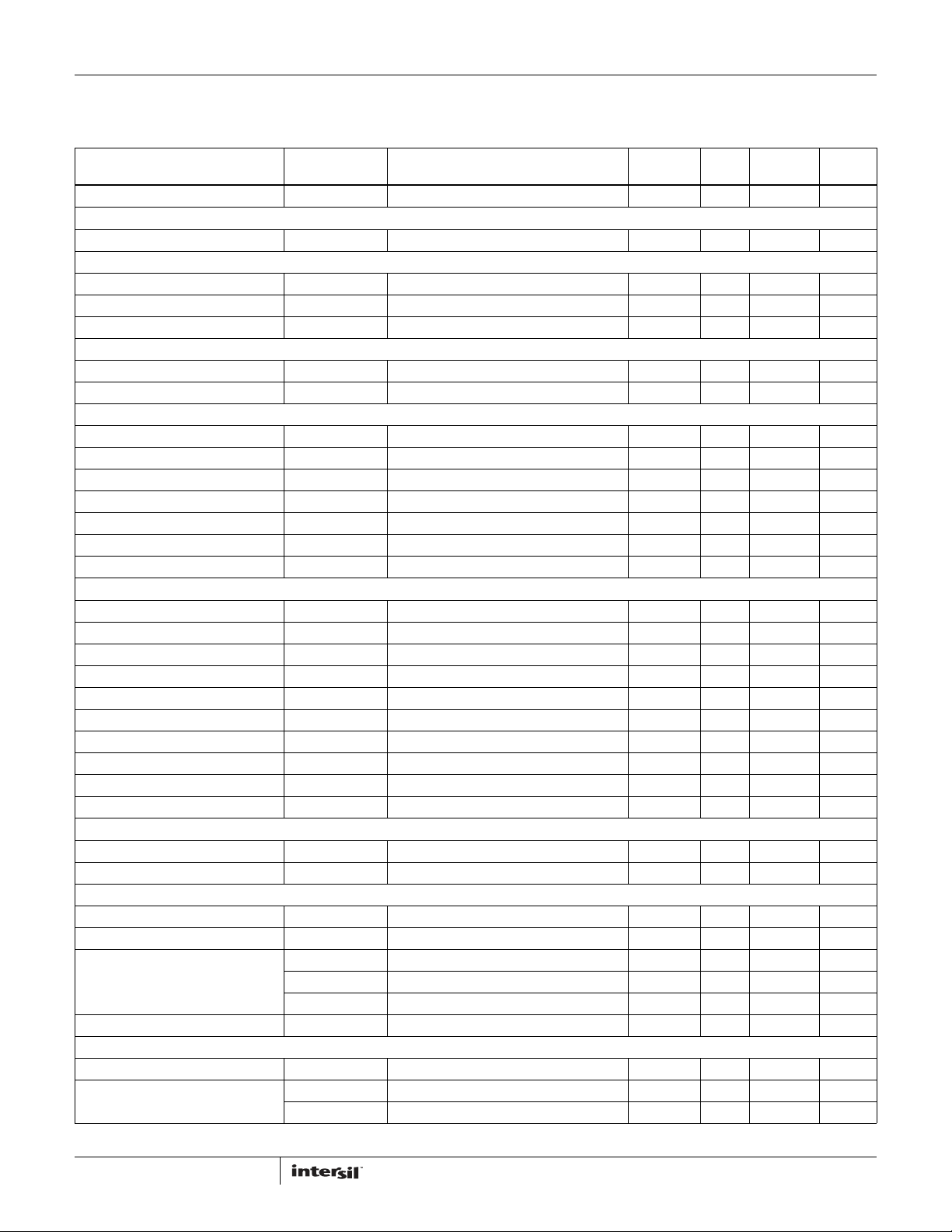

Electrical Specifications "Operating Conditions: VDD = 5V, T

(ISL95836HRTZ), fSW = 300kHz, unless otherwise noted." Boldface limits apply over the operating temperature ranges, -10°C to +100°C or

-40°C to +100°C. (Continued)

PARAMETER SYMBOL TEST CONDITIONS

Minimum Output Voltage V

CHANNEL FREQUENCY

Adjustment Range 300 450 kHz

AMPLIFIERS

Current-Sense Amplifier Input Offset I

Error Amp DC Gain A

Error Amp Gain-Bandwidth Product GBW C

ISEN

Imbalance Voltage Maximum of ISENs - Minimum of ISENs 1 mV

Input Bias Current 20 nA

POWER-GOOD AND PROTECTION MONITORS

PGOOD Low Voltage V

PGOOD Leakage Current I

PGOOD Delay tpgd 1.2 ms

ALERT# Low Voltage 7 12

VR_HOT# Low Voltage 7 12

ALERT# Leakage Current 1 µA

VR_HOT# Leakage Current 1 µA

GATE DRIVER

UGATE Pull-Up Resistance R

UGATE Source Current I

UGATE Sink Resistance R

UGATE Sink Current I

LGATE Pull-Up Resistance R

LGATE Source Current I

LGATE Sink Resistance R

LGATE Sink Current I

UGATE to LGAT E De adtime t

LGATE to UGAT E De adtime t

BOOTSTRAP DIODE

Forward Voltage V

Reverse Leakage I

PROTECTION

Overvoltage Threshold OV

Current Imbalance Threshold One ISEN above another ISEN for >1.2ms 9 mV

VR1 Overcurrent Threshold 3-Phase - PS0 and 1-Phase - all states 25.5 30.6 35.5 µA

VR2 Overcurrent Threshold All states 28.5 30.6 33.5 µA

LOGIC THRESHOLDS

VR_ON Input Low V

VR_ON Input High V

CONFIDENTIAL

IN REVIEW

OUT(min)

v0

OL

OH

UGPU

UGSRC

UGPD

UGSNK

LGPU

LGSRC

LGPD

LGSNK

UGFLGR

LGFUGR

F

R

H

IL

IH

V

IH

VID = [00000001] 0.25 V

= 0A -0.15 +0.15 mV

FB

= 20pF 18 MHz

L

I

= 4mA 0.15 0.4 V

PGOOD

PGOOD = 3.3V 1 µA

200mA Source Current 1.0 1.5

UGATE - PHASE = 2.5V 2.0 A

250mA Sink Current 1.0 1.5

UGATE - PHASE = 2.5V 2.0 A

250mA Source Current 1.0 1.5

LGATE - VSSP = 2.5V 2.0 A

250mA Sink Current 0.5 0.9

LGATE - VSSP = 2.5V 4.0 A

UGATE falling to LGATE rising, no load 23 ns

LGATE falling to UGATE rising, no load 28 ns

PVCC = 5V, IF = 2mA 0.58 V

VR = 25V 0.2 µA

VSEN rising above setpoint for >1µs 120 155 200 mV

3-Phase - PS1, 2-Phase - PS0 16.75 20.6 24.25 µA

3-Phase - PS2, 2-Phase - PS1 and PS2 8.5 10.6 12.75 µA

HRTZ 0.7 V

IRTZ 0.75 V

= -40°C to +100°C (ISL95836IRTZ), TA = -10°C to +100°C

A

MIN

(Note 6) TYP

90 dB

MAX

(Note 6) UNITS

0.3 V

9

FN7835.0

March 12, 2011

ISL95836

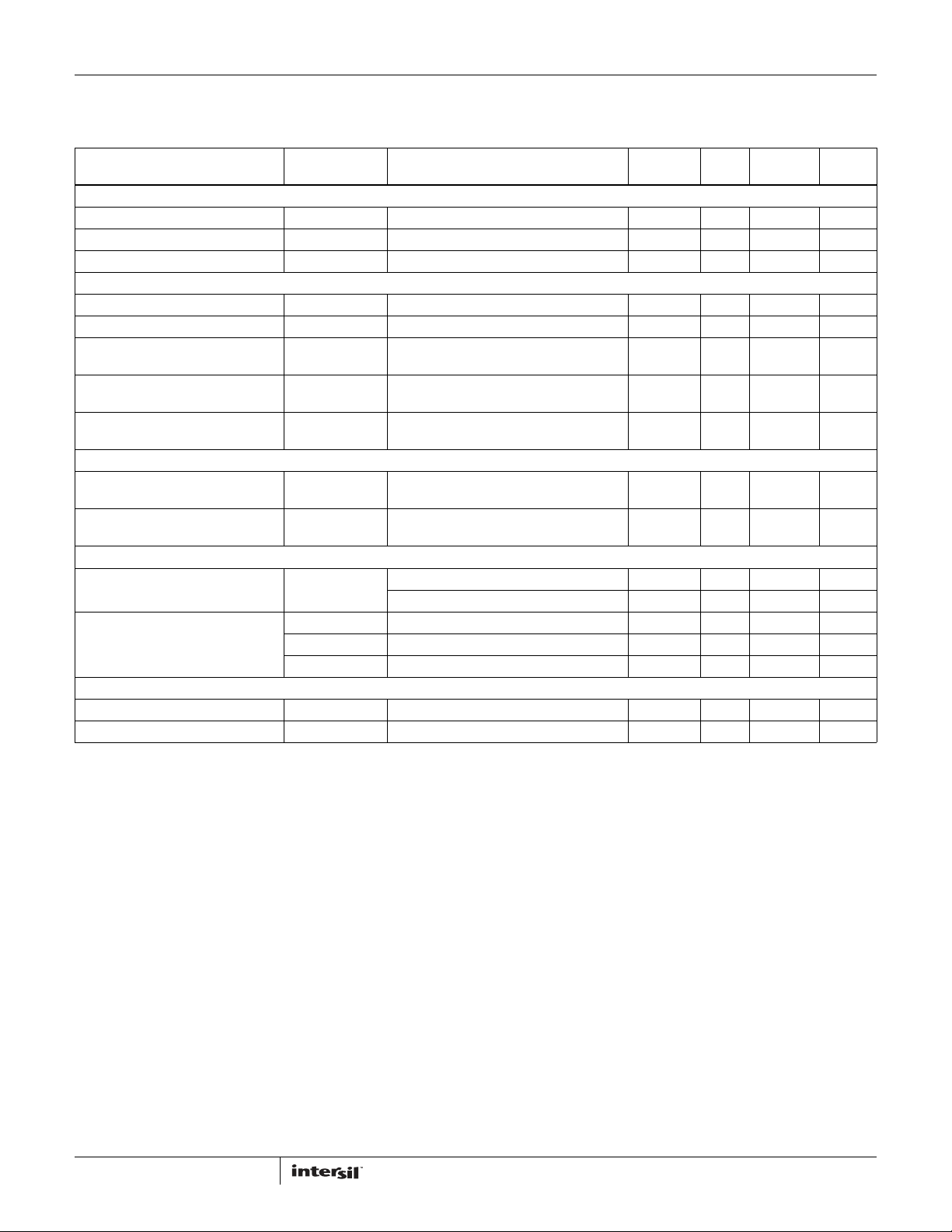

Electrical Specifications "Operating Conditions: VDD = 5V, T

(ISL95836HRTZ), fSW = 300kHz, unless otherwise noted." Boldface limits apply over the operating temperature ranges, -10°C to +100°C or

-40°C to +100°C. (Continued)

PARAMETER SYMBOL TEST CONDITIONS

PWM

PWM Output Low V

PWM Output High V

PWM Tri-State Leakage PWM = 2.5V 2 µA

THERMAL MONITOR

NTC Source Current NTC = 1.3V 59 60 61 µA

VR_HOT# Trip Voltage (VR1 and VR2) Falling 0.86 0.873 0.89 V

VR_HOT# Reset Voltage (VR1

and VR2)

Therm_Alert Trip Voltage (VR1

and VR2)

Therm_Alert Reset Voltage (VR1

and VR2)

CURRENT MONITOR

IccMax_Alert Trip Voltage (VR1

and VR2)

IccMax_Alert reset Voltage (VR1

and VR2)

INPUTS

VR_ON Leakage Current I

SCLK, SDA Leakage VR_ON = 0V, SCLK & SDA = 0V & 1V -1 1 µA

SLEW RATE (For VID Change)

Fast Slew Rate 10 mV/µs

Slow Slew Rate 2.5 mV/µs

NOTES:

6. Compliance to datasheet limits is assured by one or more methods: production test, characterization and/or design.

CONFIDENTIAL

IN REVIEW

0L

0H

VR_ON

Sinking 5mA 1.0 V

Sourcing 5mA 3.5 4.2 V

Rising 0.905 0.929 0.935 V

Falling 0.9 0.913 0.93 V

Rising 0.945 0.961 0.975 V

Rising 2.63 2.66 2.69 V

Falling 2.585 2.62 2.655 V

VR_ON = 0V -1 0µA

VR_ON = 1V 18 35 µA

VR_ON = 1V, SCLK & SDA = 1V -5 1 µA

VR_ON = 1V, SCLK & SDA = 0V -85 -60 -30 µA

= -40°C to +100°C (ISL95836IRTZ), TA = -10°C to +100°C

A

MIN

(Note 6) TYP

MAX

(Note 6) UNITS

10

FN7835.0

March 12, 2011

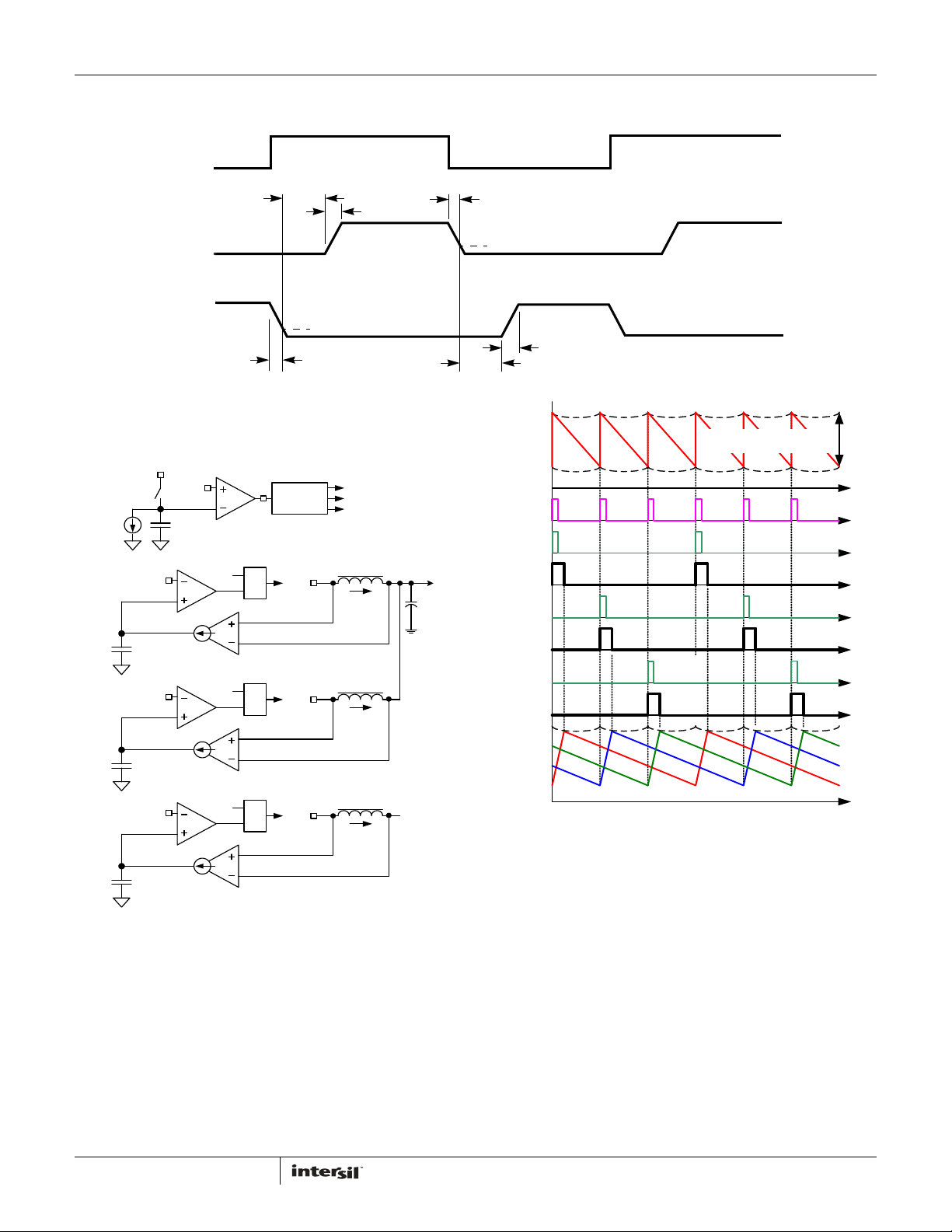

Gate Driver Timing Diagram

PWM

UGATE

LGATE

1V

1V

t

UGFLGR

t

RL

t

FU

t

RU

t

FL

t

LGFUGR

FIGURE 2. R

3

™ MODULATOR CIRCUIT

Crm

gmVo

MASTER

CLOCK

VW

COMP

MASTER

CLOCK

Phase

Sequencer

Clock1

Clock2

R

I

L1

gm

Clock1

Phase1

Crs1

VW

S

Q

PWM1

L1

R

I

L2

gm

Clock2

Phase2

Crs2

VW

S

Q

PWM2

L2

Co

Vo

Vcrm

Vcrs1

Vcrs2

MASTER CLOCK CIRCUIT

SLAVE CIRCUIT 1

SLAVE CIRCUIT 2

R

I

L3

gm

Clock3

Phase3

Crs3

VW

S

Q

PWM3

L3

Vcrs3

SLAVE CIRCUIT 3

Clock3

FIGURE 3. R

3

™ MODULATOR OPERATION PRINCIPLES IN

STEADY STATE

COMP

Vcrm

Master

Clock

PWM1

VW

Clock1

PWM2

Clock2

Hysteretic

Window

PWM3

Vcrs3

Clock3

Vcrs2 Vcrs1

VW

Theory of Operation

Multiphase R3™ Modulator

CONFIDENTIAL

ISL95836

IN REVIEW

11

FN7835.0

March 12, 2011

Loading...

Loading...