Intersil ISL88731AHRZ Schematics

SMBus Level 2 Battery Charger

ISL88731A

The ISL88731A is a highly integrated Lithium-ion battery

charger controller, programmable over the SMBus system

management bus (SMBus). The ISL88731A is intended to be

used in a smart battery charger (SBC) within a smart battery

system (SBS) that throttles the charge power such that the

current from the AC-adapter is automatically limited. High

efficiency is achieved with a DC/DC synchronous-rectifier buck

converter, equipped with diode emulation for enhanced light

load efficiency and system bus boosting prevention. The

ISL88731A charges one to four Lithium-ion series cells, and

delivers up to 8A charge current. Integrated MOSFET drivers

and bootstrap diode result in fewer components and smaller

implementation area. Low offset current-sense amplifiers

provide high accuracy with 10mΩ sense resistors. The

ISL88731A provides 0.5% end-of-charge battery voltage

accuracy.

The ISL88731A provides a digital output that indicates the

presence of the AC-adapter as well as an analog output which

indicates the adapter current within 4% accuracy.

The ISL88731A is available in a small 5mmx5mm 28 Ld thin

(0.8mm) QFN package. An evaluation kit is available to reduce

design time. The ISL88731A is available in Pb-Free packages.

Pin Configuration

ISL88731A

(28 LD TQFN)

TOP VIEW

Features

• 0.5% Battery Voltage Accuracy

• 3% Adapter Current Limit Accuracy

• 3% Charge Current Accuracy

• SMBus 2 Wire Serial Interface

• Battery Short Circuit Protection

• Fast Response for Pulse-Charging

• Fast System-Load Transient Response

• Monitor Outputs

- Adapter Current (3% Accuracy)

- AC-Adapter Detection

• 11-Bit Battery Voltage Setting

• 6 Bit Charge Current/Adapter Current Setting

• 8A Maximum Battery Charger Current

• 11A Maximum Adapter Current

• +8V to +28V Adapter Voltage Range

• Pb-Free (RoHS compliant)

Applications

• Notebook Computers

•Tablet PCs

• Portable Equipment with Rechargeable Batteries

NC

ACIN

VREF

ICOMP

NC

VCOMP

NC

CSSP

CSSN

VCC

BOOT

28 27 26 25 24 23 22

1

2

3

4

5

6

7

8 9 10 11 12 13 14

ICM

SDA

SCL

VDDSMB

UGATE

GND

PHASE

ACOK

DCIN

NC

21

20

19

18

17

16

15

VDDP

LGATE

PGND

CSOP

CSON

NC

VFB

Ordering Information

PART

NUMBER

(Notes 1, 2, 3)

ISL88731AHRZ ISL887 31AHRZ -10 to +100 28 Ld 5x5 TQFN L28.5x5B

NOTES:

1. Add “-T*” suffix for tape and reel. Please refer to TB347

reel specifications.

2. These Intersil Pb-free plastic packaged products employ special

Pb-free material sets, molding compounds/die attach materials, and

100% matte tin plate plus anneal (e3 termination finish, which is

RoHS compliant and compatible with both SnPb and Pb-free soldering

operations). Intersil Pb-free products are MSL classified at Pb-free

peak reflow temperatures that meet or exceed the Pb-free

requirements of IPC/JEDEC J STD-020.

3. For Moisture Sensitivity Level (MSL), please see device information

page for ISL88731A

techbrief TB363

PART

MARKING

. For more information on MSL please see

.

TEMP

RANGE

(°C)

PACKAGE

(Pb-Free)

PKG.

DWG. #

for details on

June 8, 2011

FN6738.3

1

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 1-888-468-3774 |Copyright Intersil Americas Inc. 2008, 2009, 2011. All Rights Reserved

Intersil (and design) is a trademark owned by Intersil Corporation or one of its subsidiaries.

All other trademarks mentioned are the property of their respective owners.

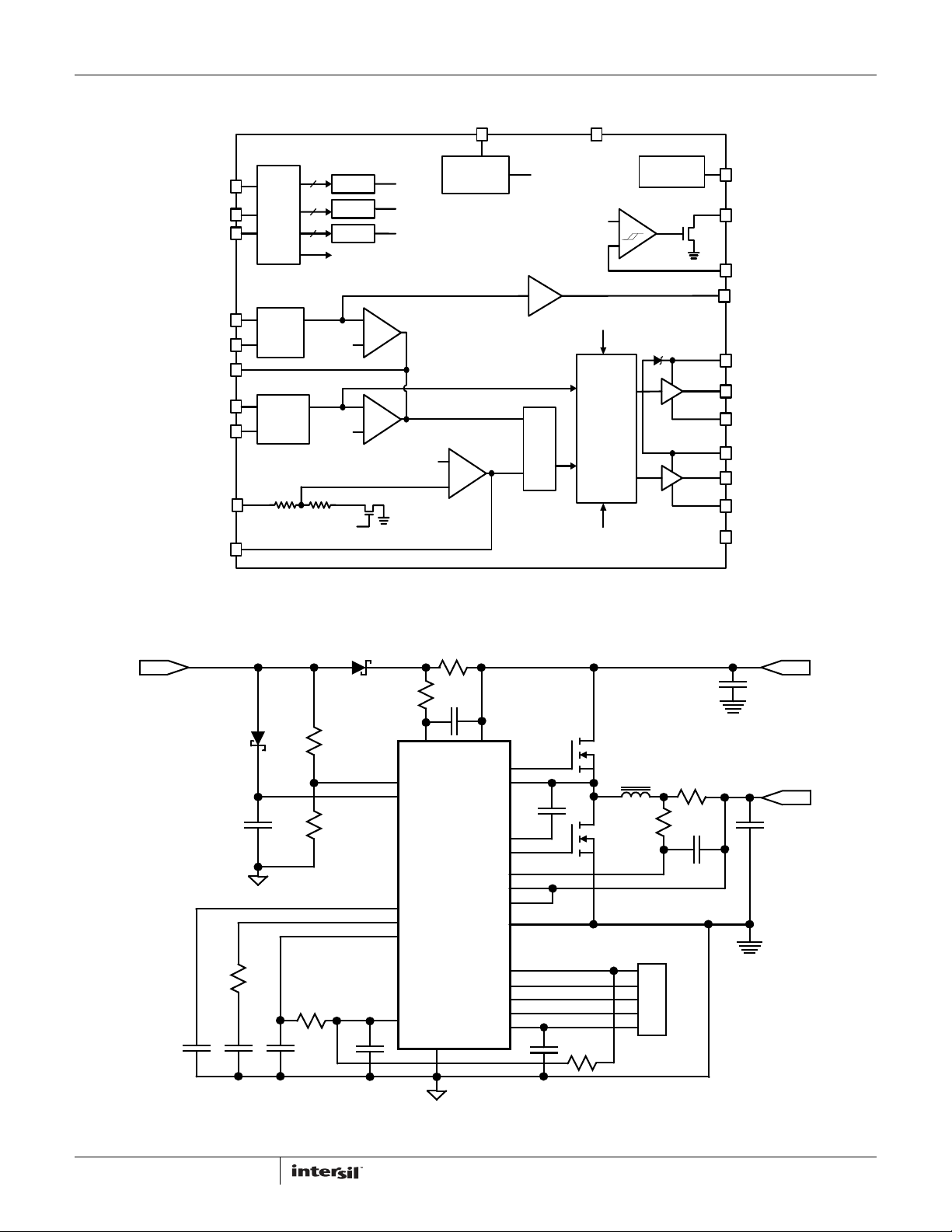

ISL88731A

VDDSMB

SDA

SCL

CSSP

CSSN

ICOM P

CSOP

CSON

VFB

VCOMP

SMBUS

LEVEL

SHIFTER

20x

LEVEL

SHIFTER

20x

500k

11

6

6

100k

DACV

DACS

EN

DACS

DACI

EN

DACI

-

GMS

+

-

+

GMI

DACV

DACS

DACI

DACV

DCIN

LINEAR

REGULATO R

+

GMV

-

BUFF

LVB

VDDP

CSO

LVB

VCC

REF

+

-

EN

DC/DC

CONVERTER

CSSP

REFERENCE

VREF

ACOK

ACIN

ICM

BOOT

UGATE

PHASE

VDDP

LGATE

PGND

GND

AC ADAPTER

AGND

FIGURE 1. FUNCTIONAL BLOCK DIAGRAM

RS1

CSSNCSSP

UGATE

ACIN

DCIN

PHASE

ISL88731A

BOOT

LGATE

CSOP

CSON

ICOMP

VCOMP

VDDP

VREF

VCC

GND

VFB

PGND

ACOK

ICM

SDA

SCL

VDDSMB

TO SYSTEM

RS2

HOST

TO BATTERY

PGND

AGND

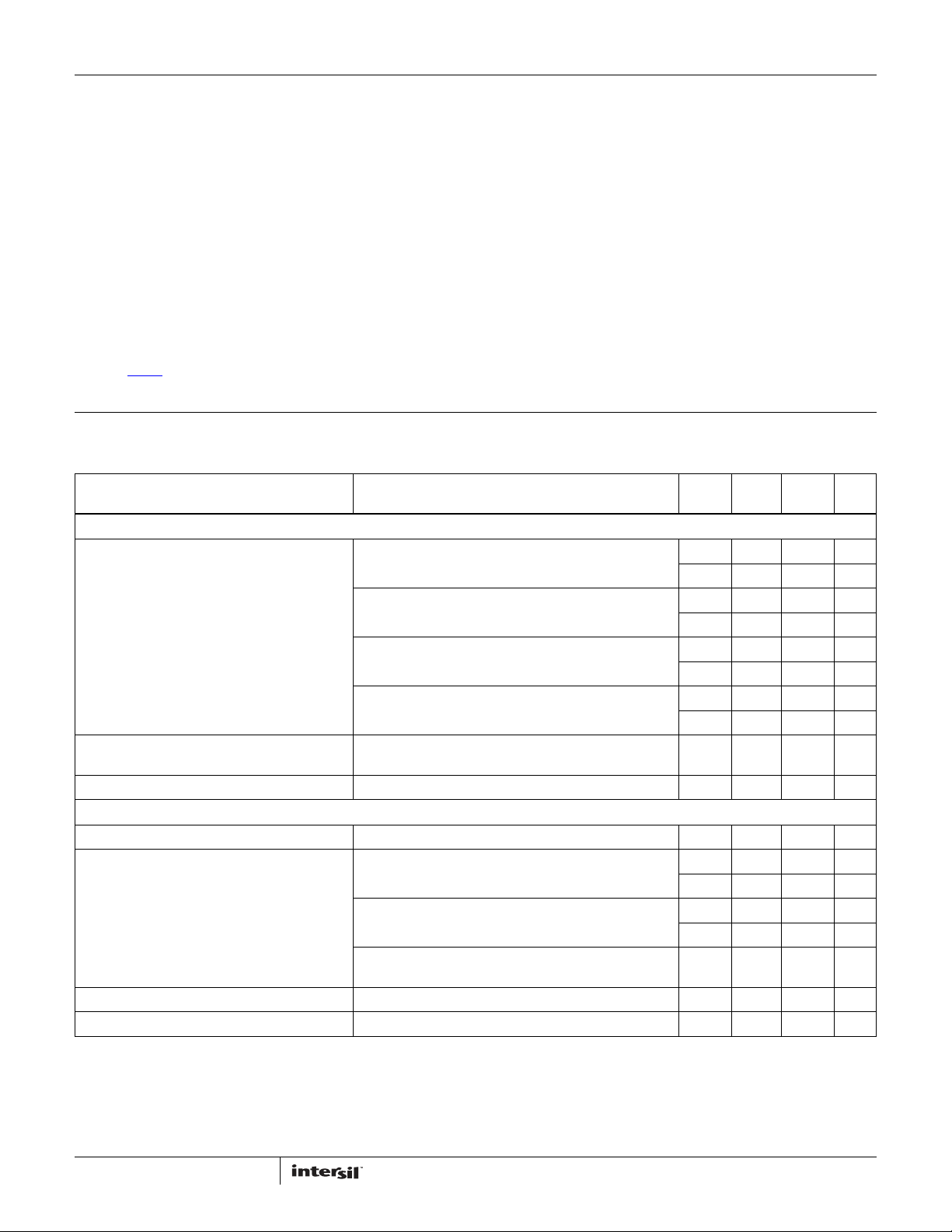

FIGURE 2. TYPICAL APPLICATION CIRCUIT

2

FN6738.3

June 8, 2011

ISL88731A

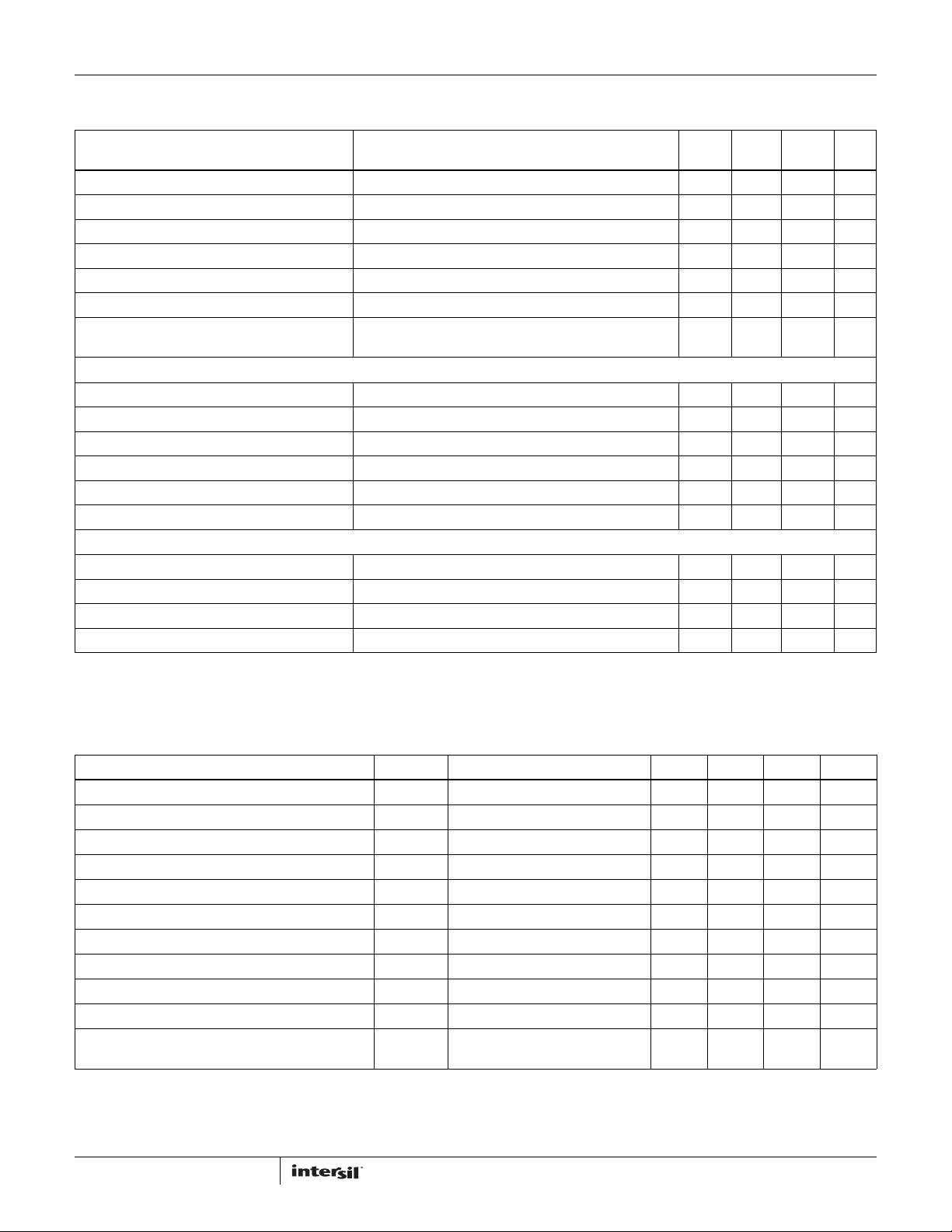

Absolute Maximum Ratings Thermal Information

DCIN, CSSP, CSSN, CSOP, CSON, VFB . . . . . . . . . . . . . . . . . . . -0.3V to +28V

CSSP-CSSN, CSOP-CSON, PGND-GND . . . . . . . . . . . . . . . . . . -0.3V to +0.3V

PHASE to GND . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -6V to +30V

BOOT to GND . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -0.3V to +33V

BOOT to PHASE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -0.3V to +6V

UGATE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . PHASE - 0.3V to BOOT +0.3V

LGATE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . PGND - 0.3V to VDDP +0.3V

ICOMP, VCOMP, VREF, to GND. . . . . . . . . . . . . . . . . . . . . -0.3V to VCC +0.3V

VDDSMB, SCL, SDA, ACIN, ACOK . . . . . . . . . . . . . . . . . . . . . . . . -0.3V to +6V

VDDP, ICM, VCC to GND, VDDP to PGND . . . . . . . . . . . . . . . . . . -0.3V to +6V

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product

reliability and result in failures not covered by warranty.

NOTES:

4. θ

is measured in free air with the component mounted on a high effective thermal conductivity test board with “direct attach” features. See Tech

JA

Brief TB379

5. For θJC, the “case temp” location is the center of the exposed metal pad on the package underside.

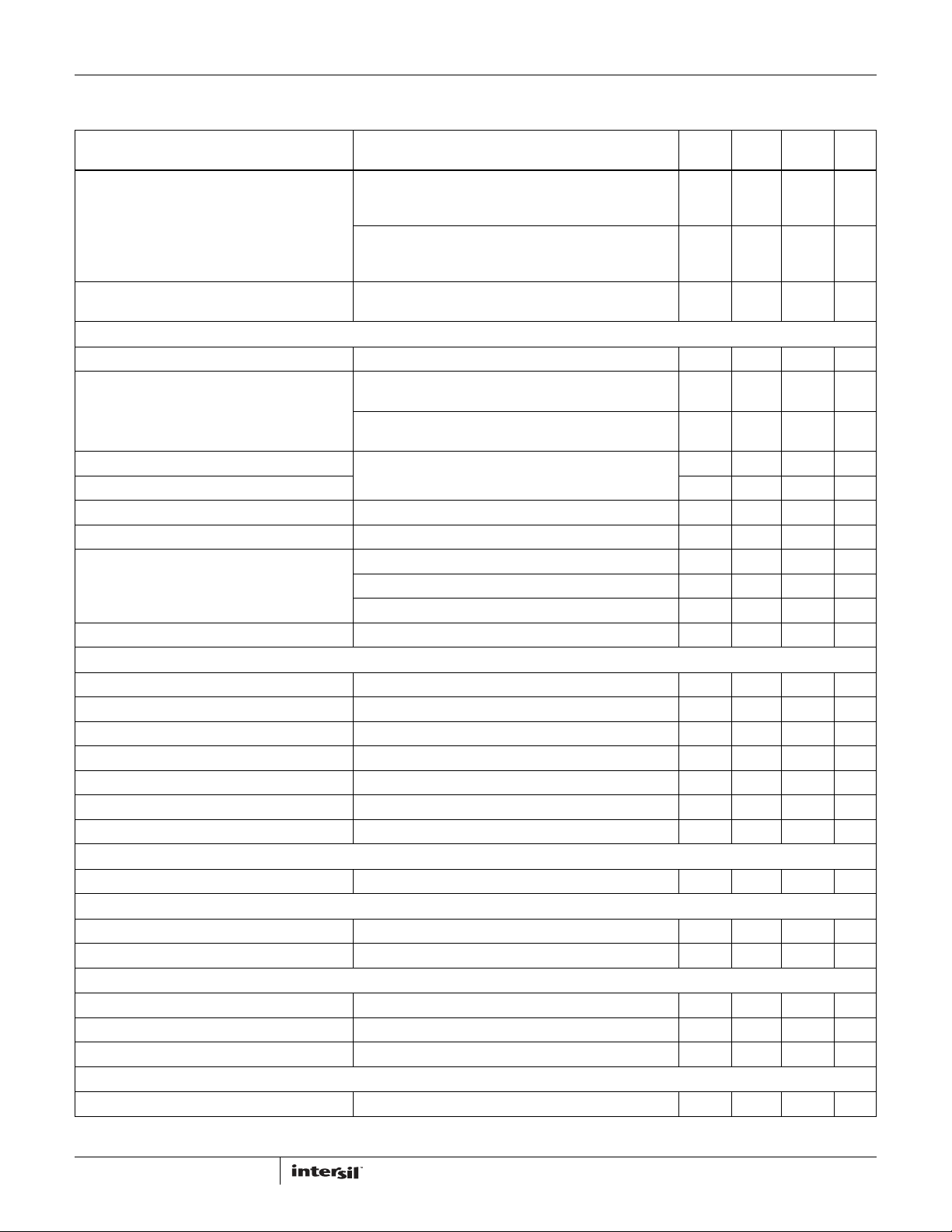

Electrical Specifications DCIN = CSSP = CSSN = 18V, CSOP = CSON = 12V, VDDP = 5V, BOOT-PHASE = 5.0V, GND = PGND = 0V,

CVDDP = 1µF, IVDDP = 0mA, T

PARAMETER CONDITIONS

CHARGE VOLTAGE REGULATION

Battery Full Charge Voltage and Accuracy ChargeVoltage = 0x41A0 16.716 16.8 16.884 V

Battery Undervoltage Lockout Trip Point for Trickle

Charge

Battery Undervoltage Lockout Trip Point Hysteresis 100 250 400 mV

CHARGE CURRENT REGULATION

CSOP to CSON Full-Scale Current-Sense Voltage 78.22 80.64 83.06 mV

Charge Current and Accuracy RS2 = 10mΩ (see Figure 2)

Charge Current Gain Error Based on charge current = 128mA and 8.064A -1.6 1.4 %

CSOP/CSON Input Voltage Range 019V

= -10°C to +100°C. Boldface limits apply over the operating temperature range, -10°C to +100°C.

A

ChargeVoltage = 0x3130 12.529 12.592 12.655 V

ChargeVoltage = 0x20D0 8.350 8.4 8.450 V

ChargeVoltage = 0x1060 4.163 4.192 4.221 V

VFB rising 2.55 2.7 2.85 V

ChargingCurrent = 0x1f80

RS2 = 10mΩ (see Figure 2)

ChargingCurrent = 0x0f80

RS2 = 10mΩ (see Figure 2)

ChargingCurrent = 0x0080

Thermal Resistance (Typical, Notes 4, 5) θ

QFN Package . . . . . . . . . . . . . . . . . . . . . . . . 36 6

Junction Temperature Range . . . . . . . . . . . . . . . . . . . . . . . -55°C to +150°C

Operating Temperature Range . . . . . . . . . . . . . . . . . . . . . . -10°C to +100°C

Storage Temperature. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -65°C to +150°C

Pb-Free Reflow Profile . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . see link below

http://www.intersil.com/pbfree/Pb-FreeReflow.asp

MIN

(Note 6) TYP

-0.5 0.5 %

-0.5 0.5 %

-0.6 0.6 %

-0.7 0.7 %

7.822 8.064 8.306 A

-3 3 %

3.809 3.968 4.126 A

-4 4 %

64 128 220 mA

(°C/W) θJC (°C/W)

JA

MAX

(Note 6) UNITS

3

FN6738.3

June 8, 2011

ISL88731A

Electrical Specifications DCIN = CSSP = CSSN = 18V, CSOP = CSON = 12V, VDDP = 5V, BOOT-PHASE = 5.0V, GND = PGND = 0V,

CVDDP = 1µF, IVDDP = 0mA, T

PARAMETER CONDITIONS

Battery Quiescent Current Adapter present, not charging,

Adapter Quiescent Current I

INPUT CURRENT REGULATION

CSSP to CSSN Full-Scale Current-Sense Voltage CSSP = 19V 106.7 110 113.3 mV

Input Current Accuracy RS1 = 10mΩ (see Figure 2)

Input Current Limit Gain Error Based on InputCurrent = 1024mA and 11004mA -1.5 1.5 %

Input Current Limit Offset -1 1 mV

CSSP/CSSN Input Voltage Range 826V

ICM Gain V

ICM Accuracy V

ICM Max Output Current V

SUPPLY AND LINEAR REGULATOR

DCIN, Input Voltage Range 826V

VDDP Output Voltage 8.0V < V

VDDP Load Regulation 0 < I

VDDSMB Range 2.7 5.5 V

VDDSMB UVLO Rising 2.4 2.5 2.6 V

VDDSMB UVLO Hysteresis 40 100 150 mV

VDDSMB Quiescent Current VDDP = SCL = SDA = 5.5V 20 27 µA

V REFERENCE

VREF Output Voltage 0 < I

ACOK

ACOK Sink Current V

ACOK Leakage Current V

ACIN

ACIN Rising Threshold 3.1 3.2 3.3 V

ACIN Threshold Hysteresis 40 60 90 mV

ACIN Input Bias Current -1 1 µA

SWITCHING REGULATOR

Frequency 330 400 440 kHz

= -10°C to +100°C. Boldface limits apply over the operating temperature range, -10°C to +100°C. (Continued)

A

MIN

(Note 6) TYP

MAX

(Note 6) UNITS

135 400 µA

I

+ I

CSON

= V

+ I

CSON

CSOP

V

PHASE

Adapter Absent

I

+ I

CSOP

V

PHASE

DCIN+ICSSP+ICSSN

V

ADAPTER

+ I

CSON

= V

CSON

= 8V to 26V, V

PHASE

= V

CSOP

PHASE

= V

CSOP

+ I

CSSP

= V

+ I

CSSP

= 19V, V

BATTERY

+ I

CSSN

= 19V, V

DCIN

+ I

CSSN

DCIN

4V to 16.8V

+ I

+ I

= 0V

FB

ACIN

FB

= 5V

-1 0.2 4 µA

3 10 mA

-3 3 %

Adapter Current = 11004mA or 3584mA

RS1 = 10mΩ (see Figure 2)

-5 5 %

Adapter Current = 2048mA

CSSP-CSSN

CSSP-CSSN

V

CSSP-CSSN

V

CSSP-CSSN

CSSP-CSSN

ACOK

ACOK

= 110mV 20 V/V

= 110mV -2.5 2.5 %

= 55mV or 35mV -4 4 %

= 20mV -8 8 %

= 0.1V 500 µA

< 28V, no load 4.9 5.1 5.3 V

DCIN

< 30mA 35 100 mV

VDDP

< 300µA 3.1 3.2 3.3 V

VREF

= 0.4V, ACIN = 1.5V 2 8mA

= 5.5V, ACIN = 3.7V 1 µA

4

FN6738.3

June 8, 2011

ISL88731A

Electrical Specifications DCIN = CSSP = CSSN = 18V, CSOP = CSON = 12V, VDDP = 5V, BOOT-PHASE = 5.0V, GND = PGND = 0V,

CVDDP = 1µF, IVDDP = 0mA, T

PARAMETER CONDITIONS

BOOT Supply Current UGATE High 170 290 400 µA

PHASE Input Bias Current V

UGATE ON-Resistance Low I

UGATE ON-Resistance High I

LGATE ON-Resistance High I

LGATE ON-Resistance Low I

Dead Time Falling UGATE to rising LGATE or

ERROR AMPLIFIERS

GMV Amplifier Transconductance 200 250 300 µA/V

GMI Amplifier Transconductance 40 50 60 µA/V

GMS Amplifier Transconductance 40 50 60 µA/V

GMI/GMS Saturation Current 15 21 25 µA

GMV Saturation Current 10 17 30 µA

ICOMP, VCOMP Clamp Voltage 0.25V < V

LOGIC LEVELS

SDA/SCL Input Low Voltage VDDSMB = 2.7V to 5.5V 0.8 V

SDA/SCL Input High Voltage VDDSMB = 2.7V to 5.5V 2 V

SDA/SCL Input Bias Current VDDSMB = 2.7V to 5.5V -1 1 µA

SDA, Output Sink Current V

NOTE:

6. Parameters with MIN and/or MAX limits are 100% tested at +25°C, unless otherwise specified. Temperature limits established by characterization

and are not production tested.

= -10°C to +100°C. Boldface limits apply over the operating temperature range, -10°C to +100°C. (Continued)

A

MIN

(Note 6) TYP

= 28V, V

DCON

= -100mA 0.9 1.6 Ω

UGATE

= 10mA 1.4 2.5 Ω

UGATE

= +10mA 1.4 2.5 Ω

LGATE

= -100mA 0.9 1.6 Ω

LGATE

falling LGATE to rising UGATE

ICOMP, VCOMP

= 0.4V 7 15 mA

SDA

CSON

= V

= 20V 0 2 µA

PHASE

35 50 80 ns

< 3.5V 200 300 400 mV

MAX

(Note 6) UNITS

SMBus Timing Specification VDDSMB = 2.7V TO 5.5V

PARAMETERS SYMBOL CONDITIONS MIN T YP MAX UNITS

SMBus Frequency FSMB 10 100 kHz

Bus Free Time TBUF 4.7 µs

Start Condition Hold Time from SCL THD:STA 4 µs

Start Condition Setup Time from SCL TSU:STA 4.7 µs

Stop Condition Setup Time from SCL TSU:STO 4 µs

SDA Hold Time from SCL THD:DAT 300 ns

SDA Setup Time from SCL TSU:DAT 250 ns

SCL Low Timeout (Note 7) TTIMEOUT 22 25 30 ms

SCL Low Period TLOW 4.7 µs

SCL High Period THIGH 4 µs

Maximum Charging Period Without a SMBus Write to

ChargeVoltage or ChargeCurrent Register

NOTES:

7. If SCL is low for longer than the specified time, the charger is disabled.

5

140 180 220 s

FN6738.3

June 8, 2011

ISL88731A

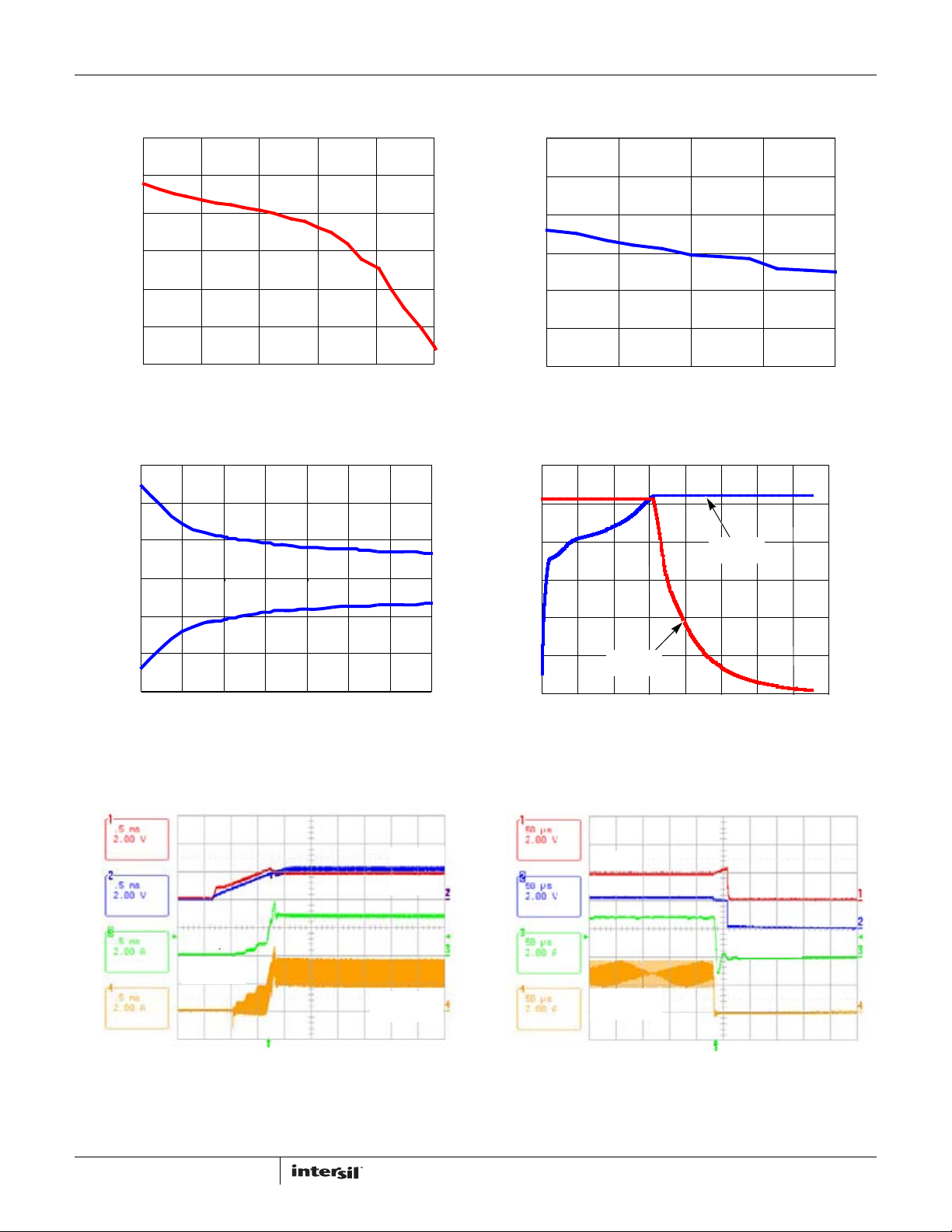

Typical Operating Performance DCIN = 20V, 3S2P Li-Battery, T

5.15

5.10

5.05

5.00

VDDP (V)

4.95

4.90

4.85

020406080100

VDDP LOAD CURRENT (mA)

FIGURE 3. VDD LOAD REGULATION

15

10

5

0

-5

ICM ACCURACY (%)

-10

3.23

3.22

3.21

3.20

VREF (V)

3.19

3.18

3.17

0 50 100 150 200

FIGURE 4. VREF LOAD REGULATION

13.0

12.5

12.0

11.5

11.0

BATTERY VOLTAGE

10.5

ICHG (A)

= +25°C, unless otherwise noted.

A

I VREF (µA)

VCHG (V)

1.0%

0.5%

0.0%

-0.5%

-1.0%

3.5

3.0

2.5

2.0

1.5

1.0

0.5

BATTERY CURRENT

-15

123 567

48

ADAPTER CURRENT (A)

FIGURE 5. ICM ACCURACY vs AC-ADAPTER CURRENT

VCOMP

ICOMP

CHARGE

CURRENT

INDUCTOR

CURRENT

FIGURE 7. CHARGE ENABLE

10.0

0 20406080100120140160

TIME (MINUTES)

FIGURE 6. TYPICAL CHARGING VOLTAGE AND CURRENT

ICOMP

VCOMP

CHARGE

CURRENT

INDUCTOR

CURRENT

FIGURE 8. CHARGE DISABLE

0.0

6

FN6738.3

June 8, 2011

ISL88731A

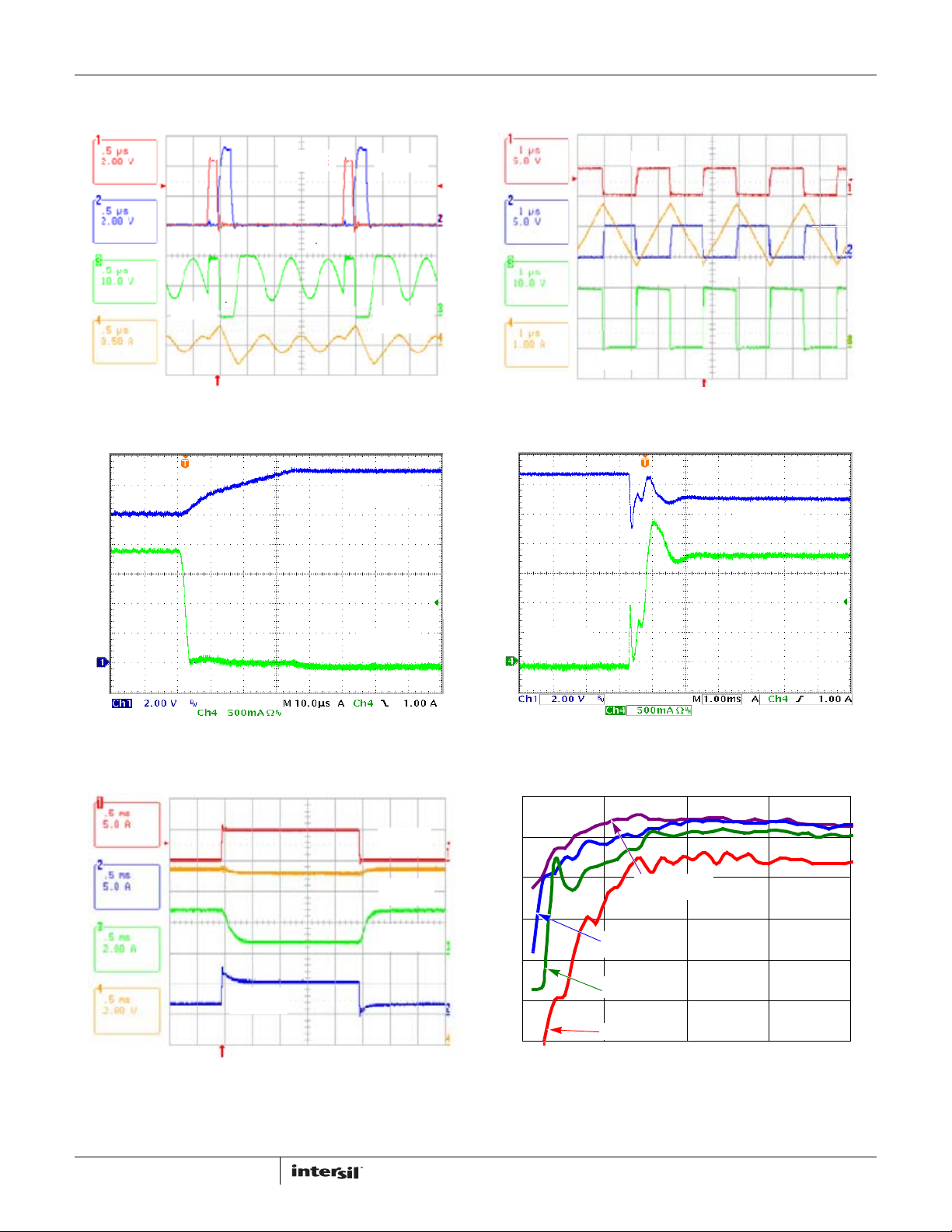

Typical Operating Performance DCIN = 20V, 3S2P Li-Battery, T

UGATE

PHASE

FIGURE 9. SWITCHING WAVEFORMS AT DIODE EMULATION

CSON/

V

BATTERY

LGATE

INDUCTOR

CURRENT

PHASE

FIGURE 10. SWITCHING WAVEFORMS IN CC MODE

= +25°C, unless otherwise noted.

A

UGATE

INDUCTOR

CURRENT

LGATE

CSON/

V

BATTERY

BATTERY

CURRENT

FIGURE 11. BATTERY REMOVAL

ADAPTER

CURRENT

FIGURE 13. LOAD TRANSIENT RESPONSE

SYSTEM

LOAD

BATTERY

VOLTAGE

CHARGE

CURRENT

BATTERY

CURRENT

FIGURE 12. BATTERY INSERTION

100

95

90

85

80

75

70

04 8

16.8V

BATTERY

12.6V

BATTERY

8.4V

BATTERY

4.2V

BATTERY

26

CHARGE CURRENT (A)

FIGURE 14. EFFICIENCY vs CHARGE CURRENT AND BATTERY

VOLTAGE (EFFICIENCY DCIN = 20V)

7

FN6738.3

June 8, 2011

ISL88731A

Functional Pin Descriptions

BOOT

High-Side Power MOSFET Driver Power-Supply Connection.

Connect a 0.1µF capacitor from BOOT to PHASE.

UGATE

High-Side Power MOSFET Driver Output. Connect to the high-side

N-Channel MOSFET gate.

LGATE

Low-Side Power MOSFET Driver Output. Connect to low-side

N-Channel MOSFET. LGATE drives between VDDP and PGND.

PHASE

High-Side Power MOSFET Driver Source Connection. Connect to

the source of the high-side N-Channel MOSFET.

CSOP

Charge Current-Sense Positive Input.

CSON

Charge Current-Sense Negative Input.

CSSP

Input Current-Sense Positive Input.

CSSN

Input Current-Sense Negative Input.

DCIN

Charger Bias Supply Input. Bypass DCIN with a 0.1µF capacitor to

GND.

ACIN

AC-adapter Detection Input. Connect to a resistor divider from the

AC-adapter output.

ACOK

AC Detect Output. This open drain output is high impedance

when ACIN is greater than 3.2V. The ACOK output remains low

when the ISL88731A is powered down. Connect a 10k pull-up

resistor from ACOK to VDDSMB.

PGND

Power Ground. Connect PGND to the source of the low side

MOSFET.

VCC

Power input for internal analog circuits. Connect a 4.7Ω resistor

from VCC to VDDP and a 1µF ceramic capacitor from VCC to

ground.

VDDP

Linear Regulator Output. VDDP is the output of the 5.2V linear

regulator supplied from DCIN. VDDP also directly supplies the

LGATE driver and the BOOT strap diode. Bypass with a 1µF

ceramic capacitor from VDDP to PGND.

ICOMP

Compensation Point for the charging current and adapter current

regulation Loop. Connect 0.01µF to GND. See “Voltage Control

Loop” on page 20 for details of selecting the ICOMP capacitor.

VCOMP

Compensation Point for the voltage regulation loop. Connect

4.7kΩ in series with 0.01µF to GND. See “Voltage Control Loop”

on page 20 for details on selecting VCOMP components.

VFB

Feedback for the Battery Voltage.

VDDSMB

SMBus interface Supply Voltage Input. Bypass with a 0.1µF

capacitor to GND.

SDA

SMBus Data I/O. Open-drain Output. Connect an external pull-up

resistor according to SMBus specifications.

SCL

SMBus Clock Input. Connect an external pull-up resistor

according to SMBus specifications.

GND

Analog Ground. Connect directly to the backside paddle. Connect

to PGND close to the output capacitor.

ICM

Input Current Monitor Output. ICM voltage equals 20 x (V

).

V

CSSN

CSSP

-

VREF

VREF is a reference output pin. It is internally compensated. Do

not connect a decoupling capacitor.

8

Back Side Paddle

Connect the backside paddle to GND.

NC

No Connect. Pins 1, 5, 7 and 14 are not connected.

FN6738.3

June 8, 2011

Loading...

Loading...