Page 1

查询ISL84541IB供应商

®

ISL84541, ISL84542, ISL84543, ISL84544

Data Sheet April 2003

Low-Voltage, Single Supply, Dual SPST,

SPDT Analog Switches

The Intersil ISL84541–ISL84544 devices are precision, dual

analog switches designed to operate from a single +2.7V to

+12V supply. Targeted applications include battery powered

equipment that benefit from the devices’ low power

consumption (5µW), low leakage currents (100pA max), and

fast switching speeds (t

= 35ns, t

ON

= 25ns). Cell phones,

OFF

for example, often face ASIC functionality limitations. The

number of analog input or GPIO pins may be limited and

digital geometries are not well suited to analog switch

performance. This family of parts may be used to “mux-in”

additional functionality while reducing ASIC design risk. Some

of the smallest packages are available alleviating board space

limitations, and making Intersil’s newest line of low-voltage

switches an ideal solution.

The ISL84541/ISL84542/ISL84543 are dual singlepole/single-throw (SPST) devices. The ISL84541 has two

normally open (NO) switches; the ISL84542 has two normal ly

closed (NC) switches; the ISL84543 has one NO and one NC

switch and can be used as an SPDT. The ISL84544 is a

committed SPDT, which is perfect for use in 2-to-1 multiplexer

applications.

Table 1 summarizes the performance of this family. For higher

performance, pin compatible versions, see the ISL43120 - 22

and ISL43210 datasheet.

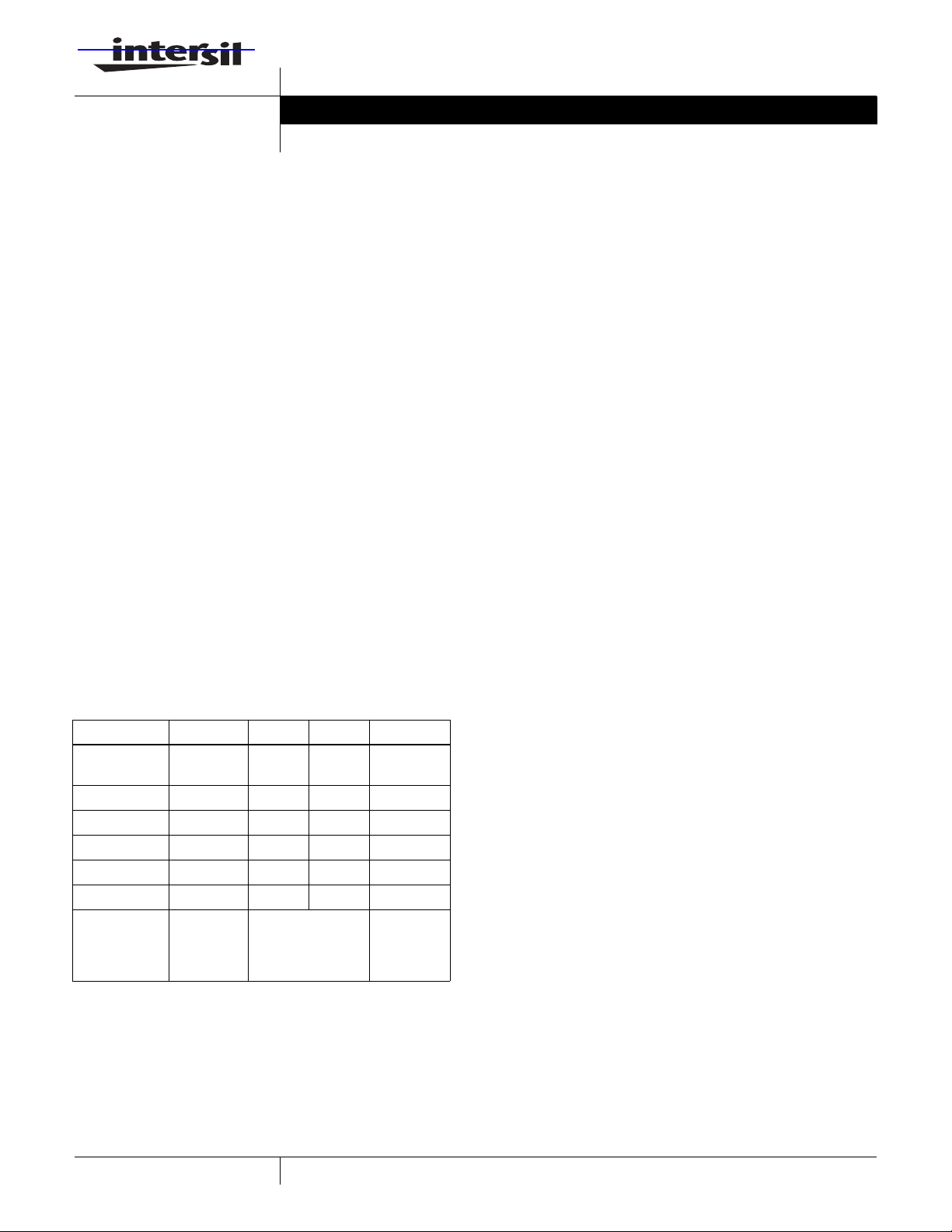

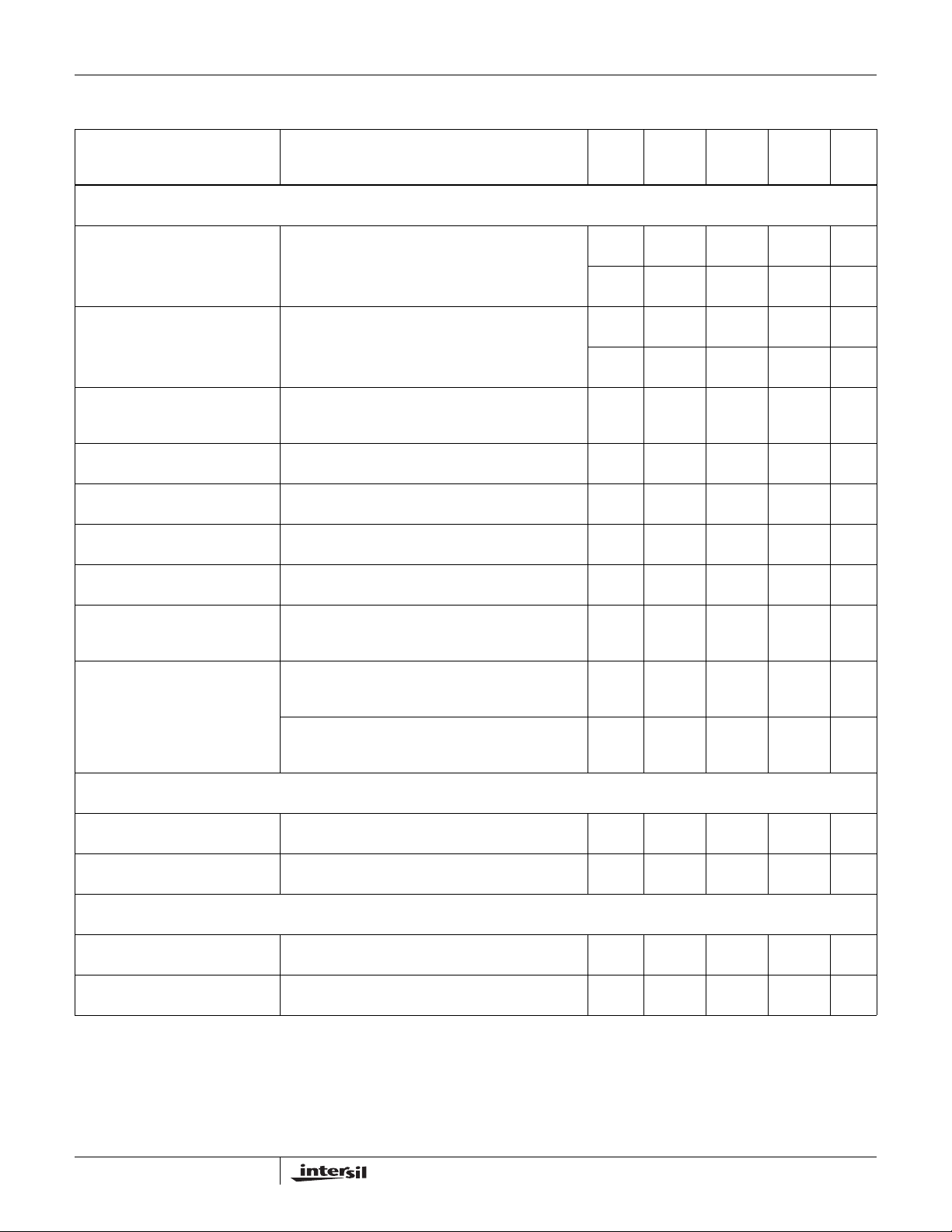

TABLE 1. FEATURES AT A GLANCE

ISL84541 ISL84542 ISL84543 ISL84544

NUMBER OF

SWITCHES

SW 1 / SW 2 NO / NO NC / NC NO / NC SPDT

3.3V R

ON

3.3V tON / t

5V t

PACKAGES

5V R

ON

/ t

OFF

ON

OFF

2221

50Ω 50Ω 50Ω 50Ω

50 / 20ns 50 / 20ns 50 / 20ns 50 / 20ns

30Ω 30Ω 30Ω 30Ω

35 / 25ns 35 / 25ns 35 / 25ns 35 / 25ns

8 Ld PDIP,

8 Ld SOIC,

8 Ld SOT-23,

8 Ld MSOP

8 Ld PDIP,

8 Ld SOIC,

8 Ld SOT-23

8 Ld PDIP,

8 Ld SOIC,

6 Ld SOT-23

Related Literature

Technical Brief TB363 “Guidelines for Handling and

Processing Moisture Sensitive Surface Mount Devices

(SMDs)”

FN6016.5

Features

• Drop-in Replacements for MAX4541 - MAX4544,

DG9461, DG9262 - DG9263

• Fully Specified at 3.3V and 5V Supplies

• Pin Compatible with MAX323 - MAX325

• ON Resistance (R

Matching Between Channels. . . . . . . . . . . . . . . . . . <1Ω

•R

ON

) . . . . . . . . . . . . . . . . . . . . . . . . 30Ω

ON

• Low Charge Injection . . . . . . . . . . . . . . . . . . . . . . 5pC (Max)

• Single Supply Operation. . . . . . . . . . . . . . . . . +2.7V to +12V

• Low Power Consumption (P

• Low Leakage Current (Max at 85

). . . . . . . . . . . . . . . . . . . .<5µW

D

o

C) . . . . . . . . . . . . 10nA

• Fast Switching Action

-t

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35ns

ON

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25ns

-t

OFF

• Guaranteed Break-Before-Make (ISL84543/ISL84544

only)

• Minimum 2000V ESD Protection per Method 3015.7

• TTL, CMOS Compatible

• Available in SOT-23 Packaging

Applications

• Battery Powered, Handheld, and Portable Equipment

- Cellular/Mobile Phones

- Pagers

- Laptops, Notebooks, Palmtops

• Communications Systems

- Military Radios

- PBX, PABX

• Test Equipment

- Ultrasound

- Electrocardiograph

• Heads-Up Displays

• Audio and Video Switching

• Various Circuits

- +3V/+5V DACs and ADCs

- Sample and Hold Circuits

- Digital Filters

- Operational Amplifier Gain Switching Networks

- High Frequency Analog Switching

- High Speed Multiplexing

- Integrator Reset Circuits

1

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 321-724-7143

| Intersil (and design) is a registered trademark of Intersil Americas Inc.

All other trademarks mentioned are the property of their respective owners.

Copyright © Intersil Americas Inc. 2003. All Rights Reserved

Page 2

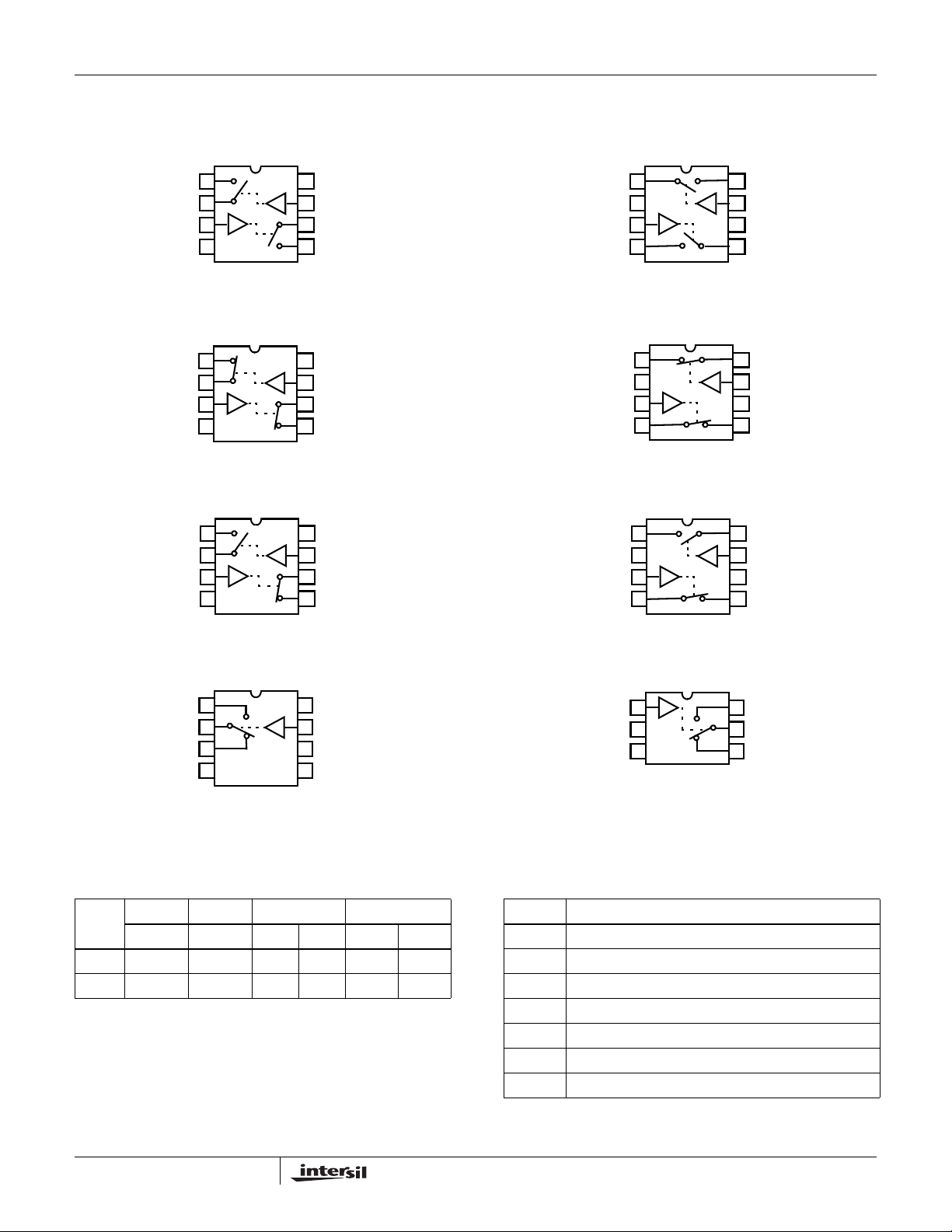

Pinouts (Note 1)

ISL84541 (PDIP, SOIC, MSOP)

TOP VIEW

ISL84541, ISL84542, ISL84543, ISL84544

ISL84541 (SOT-23)

TOP VIEW

NO

1

1

COM

2

1

3

IN

2

4

GND

ISL84542 (PDIP, SOIC)

TOP VIEW

NC

1

1

COM

2

1

3

IN

2

4

GND

ISL84543 (PDIP, SOIC)

TOP VIEW

NO

1

1

COM

2

1

3

IN

2

4

GND

V+

8

7

IN

1

6

COM

2

5

NO

2

NO

COM

1

1

V+

2

IN

3

2

4

2

COM

8

1

7

IN

1

6

GND

5

NO

2

ISL84542 (SOT-23)

TOP VIEW

COM

NC

COM

1

1

V+

2

IN

3

2

4

2

V+

8

7

IN

1

6

COM

2

5

NC

2

8

1

7

IN

1

6

GND

5

NC

2

ISL84543 (SOT-23)

TOP VIEW

V+

8

7

IN

1

6

COM

2

5

NC

2

NO

COM

1

1

V+

2

IN

3

2

4

2

COM

8

1

7

IN

1

6

GND

5

NC

2

ISL84544 (PDIP, SOIC)

TOP VIEW

V+

NO

COM

NC

GND

1

2

3

4

8

7

IN

6

NC

5

NC

NOTE:

1. Switches Shown for Logic “0” Input.

Truth Table

ISL84541 ISL84542 ISL84543 ISL84544

LOGIC

NOTE: Logic “0” ≤ 0.8V. Logic “1” ≥ 2.4V.

SW 1, 2 SW 1, 2 SW 1 SW 2 PIN NC PIN NO

0 OFF ONOFFONONOFF

1 ON OFF ON OFF OFF ON

ISL84544 (SOT-23)

TOP VIEW

6

NO

5

COM

4

NC

V+

GND

1

IN

2

3

Pin Descriptions

PIN FUNCTION

V+ System Power Supply Input (+2.7V to +12V)

GND Ground Connection

IN Digital Control Input

COM Analog Switch Common Pin

NO Analog Switch Normally Open Pin

NC Analog Switch Normally Closed Pin

N.C. No Internal Connection

2

Page 3

ISL84541, ISL84542, ISL84543, ISL84544

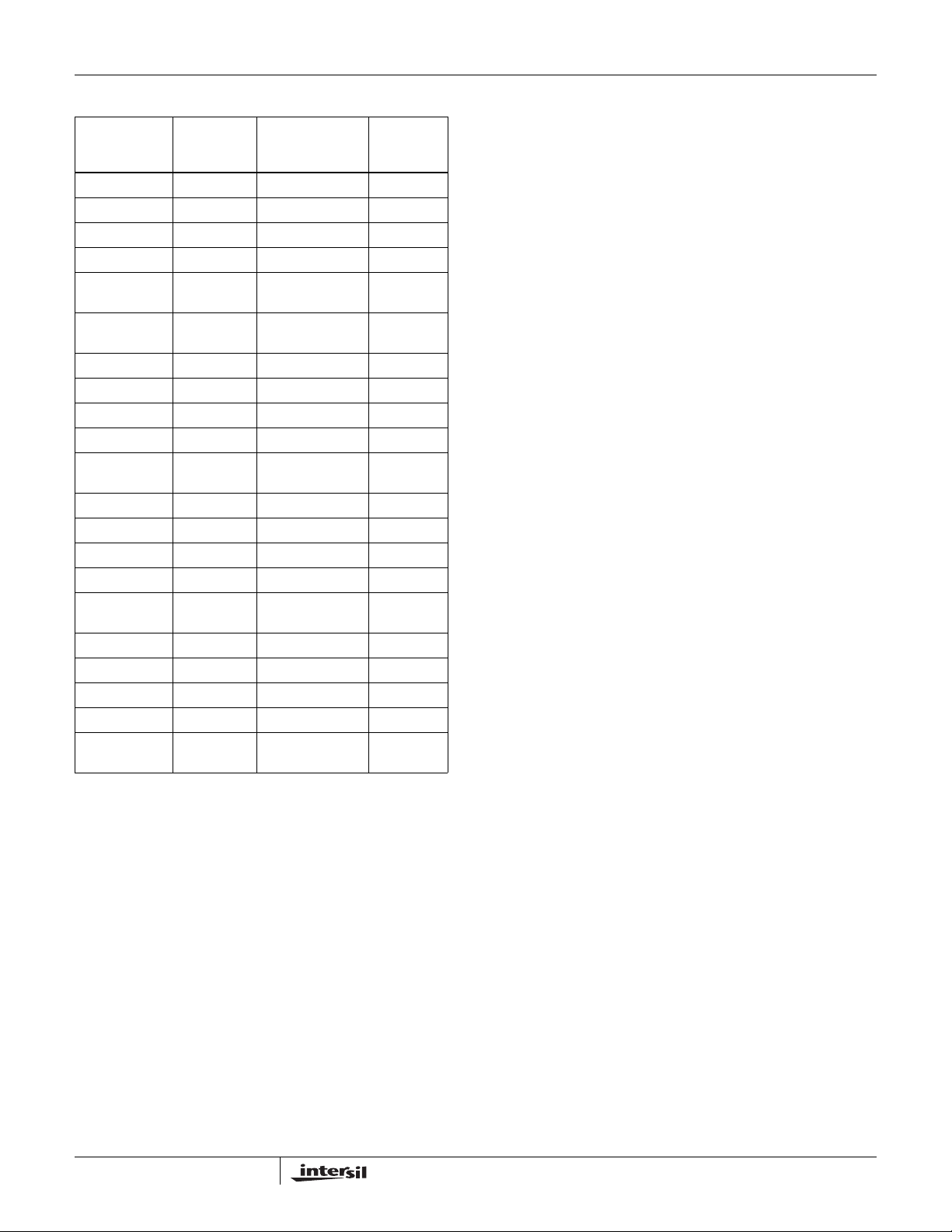

Ordering Information

PART NO.

(BRAND)

(NOTE 2)

ISL84541CP 0 to 70 8 Ld PDIP E8.3

ISL84541CB 0 to 70 8 Ld SOIC M8.15

ISL84541IP -40 to 85 8 Ld PDIP E8.3

ISL84541IB -40 to 85 8 Ld SOIC M8.15

ISL84541IH-T

(541I)

ISL84541IU

(541I)

ISL84542CP 0 to 70 8 Ld PDIP E8.3

ISL84542CB 0 to 70 8 Ld SOIC M8.15

ISL84542IP -40 to 85 8 Ld PDIP E8.3

ISL84542IB -40 to 85 8 Ld SOIC M8.15

ISL84542IH-T

(542I)

ISL84543CP 0 to 70 8 Ld PDIP E8.3

ISL84543CB 0 to 70 8 Ld SOIC M8.15

ISL84543IP -40 to 85 8 Ld PDIP E8.3

ISL84543IB -40 to 85 8 Ld SOIC M8.15

ISL84543IH-T

(543I)

ISL84544CP 0 to 70 8 Ld PDIP E8.3

ISL84544CB 0 to 70 8 Ld SOIC M8.15

ISL84544IP -40 to 85 8 Ld PDIP E8.3

ISL84544IB -40 to 85 8 Ld SOIC M8.15

ISL84544IH-T

(544I)

NOTES:

2. Most surface mount devices are available on tape and reel; add

“-T” to suffix.

TEMP.

RANGE (

o

C) PACKAGE PKG. NO.

-40 to 85 8 Ld SOT-23

Tape and Reel

-40 to 85 8 Ld MSOP M8.118

-40 to 85 8 Ld SOT-23

Tape and Reel

-40 to 85 8 Ld SOT-23

Tape and Reel

-40 to 85 6 Ld SOT-23

Tape and Reel

P8.064

P8.064

P8.064

P6.064

3

Page 4

ISL84541, ISL84542, ISL84543, ISL84544

Absolute Maximum Ratings Thermal Information

V+ to GND . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -0.3 to15V

Input Voltages

IN (Note 3). . . . . . . . . . . . . . . . . . . . . . . . . . . -0.3 to ((V+) + 0.3V)

NO, NC (Note 3) . . . . . . . . . . . . . . . . . . . . . . -0.3 t o ((V+) + 0.3V)

Output Voltages

COM (Note 3) . . . . . . . . . . . . . . . . . . . . . . . . -0.3 to ((V+) + 0.3V)

Continuous Current (Any Terminal). . . . . . . . . . . . . . . . . . . . . 10mA

Peak Current, IN, NO, NC, or COM

(Pulsed 1ms, 10% Duty Cycle, Max) . . . . . . . . . . . . . . . . . . 20mA

ESD Rating (Per MIL-STD-883 Method 3015). . . . . . . . . . . . . .>2kV

Thermal Resistance (Typical, Note 4) θ

6 Ld SOT-23 Package . . . . . . . . . . . . . . . . . . . . . . . 230

8 Ld SOT-23 Package . . . . . . . . . . . . . . . . . . . . . . . 215

8 Ld MSOP Package . . . . . . . . . . . . . . . . . . . . . . . . 210

8 LD SOIC Package. . . . . . . . . . . . . . . . . . . . . . . . . 170

8 LD PDIP Package . . . . . . . . . . . . . . . . . . . . . . . . . 140

Maximum Junction Temperature (Plastic Package) . . . . . . . 150

Moisture Sensitivity (See Technical Brief TB363)

All Other Packages . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Level 1

8 Ld SOT-23 Package . . . . . . . . . . . . . . . . . . . . . . . . . . . . Level 2

Maximum Storage Temperature Range. . . . . . . . . . . . -65

Operating Conditions

Temperature Range

ISL8454XCX . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0

ISL8454XIX . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -40

CAUTION: Stresses above those listed in “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress only rating and operation of the

device at these or any other conditions above those indicated in the operational sections of this specification is not implied .

o

C to 70oC

o

C to 85oC

Maximum Lead Temperature (Soldering 10s). . . . . . . . . . . . 300

(SOIC, MSOP and SOT-23 - Lead Tips Only)

NOTES:

3. Signals on NC, NO, COM, or IN exceeding V+ or GND are clamped by internal diodes. Limit forward diode current to maximum current ratings.

is measured with the component mounted on a low effective thermal conductivity test board in free air. See Tech Brief TB379 for details.

4. θ

JA

(oC/W)

JA

o

C to 150oC

o

o

C

C

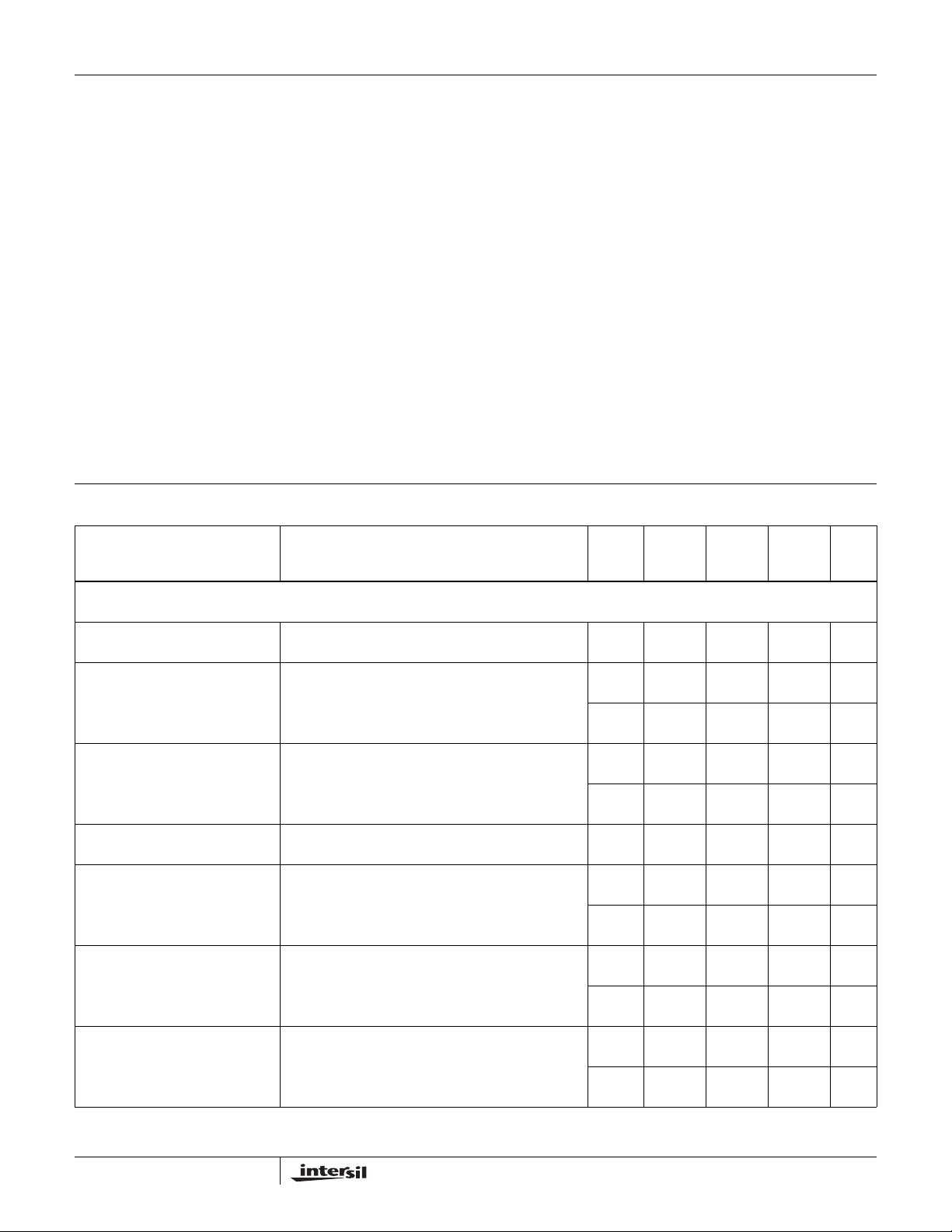

Electrical Specifications - 5V Supply Test Conditions: V+ = +4.5V to +5.5V, GND = 0V, V

Unless Otherwise Specified

TEMP

PARAMETER TEST CONDITIONS

ANALOG SWITCH CHARACTERISTICS

Analog Signal Range, V

ON Resistance, R

ON

ANALOG

V+ = 4.5V, I

See Figure 5

Matching Between Channels,

R

ON

∆R

ON

R

Flatness, R

ON

FLAT(ON)

NO or NC OFF Leakage Current,

NO(OFF)

or I

NC(OFF)

I

V+ = 5V, I

V+ = 5V, I

V+ = 5.5V, V

Note 7

= 1.0mA, VNO or VNC = 3.5V,

COM

= 1.0mA, VNO or VNC= 3.5V 25 - 0.8 2 Ω

COM

= 1.0mA, VNO or VNC = 1V, 2V, 3V Full - 7 8 Ω

COM

= 1V, 4.5V, VNO or VNC = 4.5V, 1V,

COM

o

(

C)

Full 0 - V+ V

25 - 30 60 Ω

Full - - 75 Ω

Full - - 4 Ω

25 -0.1 0.01 0.1 nA

Full -5 - 5 nA

= 2.4V, V

INH

INL

MIN

(NOTE 6) TYP

= 0.8V (Note 5),

MAX

(NOTE 6) UNITS

COM OFF Leakage Current,

I

COM(OFF)

COM ON Leakage Current,

I

COM(ON)

V+ = 5.5V, V

Note 7

V+ = 5.5V, V

COM

COM

4.5V, or Floating, Note 7

4

= 4.5V, 1V, VNO or VNC = 1V, 4.5V,

= 1V, 4.5V, or VNO or VNC = 1V,

25 -0.1 - 0.1 nA

Full -5 - 5 nA

25 -0.2 - 0.2 nA

Full -10 - 10 nA

Page 5

ISL84541, ISL84542, ISL84543, ISL84544

Electrical Specifications - 5V Supply Test Conditions: V+ = +4.5V to +5.5V, GND = 0V, V

Unless Otherwise Specified (Continued)

TEMP

PARAMETER TEST CONDITIONS

DYNAMIC CHARACTERISTICS

Turn-ON Time, t

Turn-OFF Time, t

ON

OFF

Break-Before-Make Time Delay

(ISL84543, ISL84544), t

D

Charge Injection, Q C

OFF Isolation R

Crosstalk (Channel-to-Channel) R

VNO or VNC = 3V, RL =1kΩ, CL = 35pF, VIN = 0 to 3V,

See Figure 1

VNO or VNC = 3V, RL =1kΩ, CL = 35pF, VIN = 0 to 3V,

See Figure 1

RL = 300Ω, CL = 35pF, VNO = VNC = 3V, VIN = 0 to 3V,

See Figure 3

= 1.0nF, VG = 0V, RG = 0Ω, See Figure 2 25 - 1 5 pC

L

= 50Ω, CL = 5pF, f = 1MHz, See Figure 4 25 - 76 - dB

L

= 50Ω, CL = 5pF, f = 1MHz, See Figure 6 25 - -90 - dB

L

o

(

C)

25 - 35 100 ns

Full - - 240 ns

25 - 25 75 ns

Full - - 150 ns

Full 2 10 - ns

= 2.4V, V

INH

INL

MIN

(NOTE 6) TYP

= 0.8V (Note 5),

MAX

(NOTE 6) UNITS

NO or NC OFF Capacitance, C

COM OFF Capacitance,

C

COM(OFF)

COM ON Capacitance, C

COM(ON)

f = 1MHz, VNO or VNC = V

OFF

f = 1MHz, VNO or VNC = V

f = 1MHz, VNO or VNC = V

ISL84541/2/3

f = 1MHz, V

ISL84544

NO

or VNC = V

= 0V, See Figure 7 25 - 8 - pF

COM

= 0V, See Figure 7 25 - 8 - pF

COM

= 0V, See Figure 7,

COM

= 0V, See Figure 7,

COM

25 - 13 - pF

25 - 20 - pF

POWER SUPPLY CHARACTERISTICS

Power Supply Range Full 2.7 12 V

Positive Supply Current, I+ V+ = 5.5V, V

= 0V or V+, all channels on or off Full -1 0.0001 1 µA

IN

DIGITAL INPUT CHARACTERISTICS

Input Voltage Low, V

Input Voltage High, V

INL

INH

Full - - 0.8 V

Full 2.4 - - V

NOTES:

5. V

= input voltage to perform proper function.

IN

6. The algebraic convention, whereby the most negative value is a minimum and the most positive a maximum, is used in this data sheet.

o

7. Leakage parameter is 100% tested at high temp, and guaranteed by correlation at 25

C.

5

Page 6

ISL84541, ISL84542, ISL84543, ISL84544

Electrical Specifications - 3.3V Supply Test Conditions: V+ = +3.0V to +3.6V, GND = 0V, V

Unless Otherwise Specified

TEMP

PARAMETER TEST CONDITIONS

ANALOG SWITCH CHARACTERISTICS

Analog Signal Range, V

ON Resistance, R

R

Matching Between Channels,

ON

∆R

ON

R

Flatness, R

ON

NO or NC OFF Leakage Current,

I

NO(OFF)

or I

NC(OFF)

COM OFF Leakage Current,

I

COM(OFF)

COM ON Leakage Current,

I

COM(ON)

ON

FLAT(ON)

ANALOG

V+ = 3V, I

V+ = 3.3V, I

V+ = 3.3V, I

1V, 1.5V

V+ = 3.6V, V

Note 7

V+ = 3.6V, V

Note 7

V+ = 3.6V, V

or floating, Note 7

= 1.0mA, VNO or VNC = 1.5V 25 - 50 80 Ω

COM

= 1.0mA, VNO or VNC = 1.5V 25 - 0.8 2 Ω

COM

= 1.0mA, VNO or VNC = 0.5V,

COM

= 1V, 3V, VNO or VNC = 3V, 1V,

COM

= 3V, 1V, VNO or VNC = 1V, 3V,

COM

= 1V, 3V, or VNO or VNC = 1V, 3V,

COM

o

(

C)

(NOTE 6) TYP

Full 0 - V+ V

Full - - 140 Ω

Full - - 4 Ω

25 - 6 10 Ω

Full - 7 12 Ω

25 -0.1 0.01 0.1 nA

Full -5 - 5 nA

25 -0.1 0.01 0.1 nA

Full -5 - 5 nA

25 -0.2 - 0.2 nA

Full -10 - 10 nA

INH

MIN

= 2.4V, V

= 0.8V (Note 5),

INL

MAX

(NOTE 6)UNITS

DYNAMIC CHARACTERISTICS

Turn-ON Time, t

ON

VNO or VNC = 1.5V, RL =1kΩ, CL = 35pF, VIN = 0 to 3V 25 - 50 120 ns

Full 200 ns

Turn-OFF Time, t

OFF

VNO or VNC = 1.5V, RL =1kΩ, CL = 35pF, VIN = 0 to 3V 25 - 20 50 ns

Full - - 120 ns

Break-Before-Make Time Delay

(ISL84543, ISL84544), t

D

Charge Injection, Q C

OFF Isolation R

RL = 300Ω, CL = 35pF, VNO or VNC = 1.5V,

V

= 0 to 3V

IN

= 1.0nF, VG = 0V, RG = 0Ω 25 - 1 5 pC

L

= 50Ω, CL = 5pF, f = 1MHz 25 - 76 - dB

L

Full 3 30 - ns

Crosstalk (Channel-to-Channel) 25 - -90 - dB

NO or NC OFF Capacitance, C

COM OFF Capacitance,

C

COM(OFF)

COM ON Capacitance, C

COM(ON)

f = 1MHz, VNO or VNC = V

OFF

f = 1MHz, VNO or VNC = V

f = 1MHz, VNO or VNC = V

f = 1MHz, V

NO

or VNC = V

= 0V 25 - 8 - pF

COM

= 0V 25 - 8 - pF

COM

= 0V, ISL84541/2/3 25 - 13 - pF

COM

= 0V, ISL84544 25 - 20 - pF

COM

POWER SUPPLY CHARACTERISTICS

Positive Supply Current, I+ V+ = 3.6V, V

= 0V or V+, all channels on or off Full -1 - 1 µA

IN

DIGITAL INPUT CHARACTERISTICS

Input Voltage Low, V

Input Voltage High, V

Input Current, I

INH

, I

INL

INH

INL

Full - - 0.8 V

Full 2.4 - - V

V+ = 3.6V, VIN = 0V or V+ Full -1 - 1 µA

6

Page 7

ISL84541, ISL84542, ISL84543, ISL84544

Test Circuits and Waveforms

3V

LOGIC

INPUT

SWITCH

INPUT

SWITCH

OUTPUT

0V

V

NO

0V

t

ON

50%

90%

t

OFF

V

OUT

tr < 20ns

< 20ns

t

f

90%

SWITCH

LOGIC

INPUT

INPUT

NO or NC

IN

V+

GND

C

COM

RL

1kΩ

V

OUT

C

L

35pF

Logic input waveform is inverted for switches that have the opposite

logic sense.

FIGURE 1A. MEASUREMENT POINTS

FIGURE 1. SWITCHING TIMES

SWITCH

OUTPUT

V

OUT

LOGIC

INPUT

ON

Q = ∆V

OUT

∆V

x C

OUT

L

OFF

ON

V+

0V

FIGURE 2A. MEASUREMENT POINTS FIGURE 2B. TEST CIRCUIT

FIGURE 2. CHARGE INJECTION

OUT1

OUT2

3V

0V

0V

0V

90%

90%

t

D

t

D

LOGIC

INPUT

SWITCH

OUTPUT

V

SWITCH

OUTPUT

V

Repeat test for all switches. C

capacitance.

V

OUT

V

=

(NO or NC)

FIGURE 1B. TEST CIRCUIT

V+

R

G

NO or NC

V

G

V

NX

LOGIC

INPUT

NO1

NC2

IN

IN

GND

V+

1

2

GND

includes fixture and stray

L

R

L

------------------------------

RLR

+

ON()

C

COM

IN

LOGIC

INPUT

C

COM

1

V

OUT2

COM

2

R

L2

300Ω

300Ω

35pF

V

OUT

C

L

V

OUT1

R

L1

C

L2

C

L1

35pF

FIGURE 3A. MEASUREMENT POINTS (ISL84543 ONLY)

7

C

includes fixture and stray capacitance.

L

FIGURE 3B. TEST CIRCUIT (ISL84543 ONLY)

Page 8

ISL84541, ISL84542, ISL84543, ISL84544

Test Circuits and Waveforms (Continued)

V

OUT

3V

0V

0V

t

D

FIGURE 3. BREAK-BEFORE-MAKE TIME

LOGIC

INPUT

SWITCH

OUTPUT

FIGURE 3C. MEASUREMENT POINTS (ISL84544 ONLY)

90%

V+

V

NX

LOGIC

INPUT

includes fixture and stray capacitance.

C

L

NO

NC

IN

GND

FIGURE 3D. TEST CIRCUIT (ISL84544 ONLY)

C

V

R

300Ω

OUT

C

L

L

35pF

COM

SIGNAL

GENERATOR

ANALYZER

FIGURE 4. OFF ISOLATION TEST CIRCUIT FIGURE 5. R

SIGNAL

GENERATOR

R

L

0V or 2.4V

NO or NC

COM

NO1 or NC1

IN

1

GND

V+

IN

V+

COM1

IN

C

X

C

0V or 2.4V

2

0V or 2.4V

50Ω

RON = V1/1mA

V

NX

IMPEDANCE

ANALYZER

1mA

V

1

NO or NC

COM

GND

TEST CIRCUIT

ON

NO or NC

V+

IN

V+

IN

C

0.8V or 2.4V

C

0V or 2.4V

X

ANALYZER

COM2

R

L

NO2 or NC2

GND

NC

COM

GND

FIGURE 6. CROSSTALK TEST CIRCUIT FIGURE 7. CAPACITANCE TEST CIRCUIT

8

Page 9

ISL84541, ISL84542, ISL84543, ISL84544

Detailed Description

The ISL84541–ISL84544 dual analog switches offer precise

switching capability from a single 2.7V to 12V supply with

low on-resistance (30Ω) and high speed operation

(t

=35ns, t

ON

suited to portable battery powered equipment thanks to the

low operating supply voltage (2.7V), low power consumption

(5µW), low leakage currents (100pA max), and the tiny

SOT-23 packaging. High frequency applications also benefit

from the wide bandwidth, and the very high off isolation and

crosstalk rejection.

Supply Sequencing And Overvoltage Protection

With any CMOS device, proper power supply sequencing is

required to protect the device from excessive input currents

which might permanently damage the IC. All I/O pins contain

ESD protection diodes from the pin to V+ and to GND (see

Figure 8). To prevent forward biasing these diodes, V+ must

be applied before any input signals, and input signal voltages

must remain between V+ and GND. If these conditions cannot

be guaranteed, then one of the following two protection

methods should be employed.

Logic inputs can easily be protected by adding a 1kΩ resistor

in series with the input (see Figure 8). The resistor limits the

input current below the threshold that produces permanent

damage, and the sub-microamp input current produces an

insignificant voltage drop during normal operation.

Adding a series resistor to the switch input defeats the

purpose of using a low R

can be added in series with the supply pins to provide

overvoltage protection for all pins (see Figure 8). These

additional diodes limit the analog signal from 1V below V+ to

1V above GND. The low leakage current performance is

unaffected by this approach, but the switch resistance may

increase, especially at low supply voltages.

OPTIONAL

PROTECTION

RESISTOR

Power-Supply Considerations

The ISL8454X construction is typical of most CMOS analog

switches, except that they have only two supply pins: V+ and

GND. V+ and GND drive the internal CMOS switches and set

= 25ns). The devices are especially well

OFF

switch, so two small signal diodes

ON

OPTIONAL PROTECTION

DIODE

V+

IN

X

V

NO or NC

GND

OPTIONAL PROTECTION

DIODE

FIGURE 8. OVERVOLTAGE PROTECTION

V

COM

their analog voltage limits. Unlike switches with a 13V

maximum supply voltage, the ISL8454X 15V maximum supply

voltage provides plenty of room for the 10% tolerance of 12V

supplies, as well as room for overshoot and noise spikes.

The minimum recommended supply voltage is 2.7V. It is

important to note that the input signal range, switching times,

and on-resistance degrade at lower supply voltages. Refer to

the electrical specification tables and Typical Performance

curves for details.

V+ and GND also power the internal logic and level shifters.

The level shifters convert the logic levels to switched V+ and

GND signals to drive the analog switch gate terminals.

This family of switches cannot be operated with bipolar

supplies, because the input switching point becomes negative

in this configuration.

Logic-Level Thresholds

This switch family is TTL compatible (0.8V and 2.4V) over a

supply range of 3V to 11V (see Figure 15). At 12V the V

IH

level is about 2.5V. This is still below the TTL guaranteed

high output minimum level of 2.8V, but noise margin is

reduced. For best results with a 12V supply, use a logic

family the provides a V

greater than 3V.

OH

The digital input stages draw supply current whenever the

digital input voltage is not at one of the supply rails. Driving

the digital input signals from GND to V+ with a fast transition

time minimizes power dissipation.

High-Frequency Performance

In 50Ω systems, signal response is reasonably flat even past

300MHz (see Figure 16). Figure 16 also illustrate s that the

frequency response is very consistent over a wide V+ range,

and for varying analog signal levels.

An off switch acts like a capacitor and passes higher

frequencies with less attenuation, resulting in signal

feedthrough from a switch’s input to its output. Off Isolation

is the resistance to this feedthrough, while Crosstalk

indicates the amount of feedthrough from one switch to

another. Figure 17 details the high Off Isolation and

Crosstalk rejection provided by this family. At 10MHz, off

isolation is about 50dB in 50Ω systems, decreasing

approximately 20dB per decade as frequency increases.

Higher load impedances decrease Off Isolation and

Crosstalk rejection due to the voltage divider action of the

switch OFF impedance and the load impedance.

Leakage Considerations

Reverse ESD protection diodes are internally connected

between each analog-signal pin and both V+ and GND.

One of these diodes conducts if any analog signal exceeds

V+ or GND.

Virtually all the analog leakage current comes from the ESD

diodes to V+ or GND. Although the ESD diodes on a given

signal pin are identical and therefore fairly well balanced,

9

Page 10

ISL84541, ISL84542, ISL84543, ISL84544

they are reverse biased differently. Each is biased by either

V+ or GND and the analog signal. This means their leakages

will vary as the signal varies. The difference in the two diode

leakages to the V+ and GND pins constitutes the analogsignal-path leakage current. All analog leakage current flows

Typical Performance Curves T

40

35

30

25

(Ω)

ON

20

R

15

10

85oC

25oC

-40oC

5

3 4 5 6 7 8 9 10 11 12 13

V+ (V)

FIGURE 9. ON RESISTANCE vs SUPPLY VOLTAGE

= 25oC, Unless Otherwise Specified

A

between each pin and one of the supply terminals, not to the

other switch terminal. This is why both sides of a given

switch can show leakage currents of the same or opposite

polarity. There is no connection between the analog-signal

paths and V+ or GND.

45

40

35

30

25

20

15

30

(Ω)

25

ON

20

R

15

10

20

85oC

15

10

-40oC

5

0 4 6 8 10 12

2

25oC

85oC

25oC

-40oC

85oC

25oC

-40oC

V

COM

(V)

FIGURE 10. ON RESISTANCE vs SWITCH VOLTAGE

V+ = 3.3V

V+ = 5V

V+ = 12V

0.5

0.4

0.3

0.2

0.1

0.25

0.2

0.15

(Ω)

0.1

ON

∆R

0.05

0.15

0.1

0.05

25oC

85oC

0

25oC

85oC

0

-40oC

0

0 4 6 8 10 12

FIGURE 11. R

-40oC

85oC

-40oC

25oC

85oC

2

ON

V

(V)

COM

MATCH vs SWITCH VOLTAGE

-40oC

V+ = 3.3V

V+ = 5V

V+ = 12V

25oC

60

50

40

30

20

Q (pC)

10

V+ = 3.3V

0

-10

-20

0 4 6 8 10 12

2

V+ = 5V

V

COM

V+ = 12V

(V)

FIGURE 12. CHARGE INJECTION vs SWITCH VOLTAGE

10

Page 11

ISL84541, ISL84542, ISL84543, ISL84544

Typical Performance Curves T

100

90

80

70

60

(ns)

ON

t

50

40

30

20

23456789101112

85oC

-40oC

25oC

V+ (V)

= 25oC, Unless Otherwise Specified (Continued)

A

35

30

(ns)

25

OFF

t

-40oC

20

15

23456789101112

85oC

V+ (V)

FIGURE 13. TURN - ON TIME vs SUPPLY VOLTAGE FIGURE 14. TURN - OFF TIME vs SUPPLY VOLTAGE

3.0

2.5

V

INH

V+ = 3.3V to 12V

0

GAIN

-3

-6

-40oC

25oC

(V)

2.0

INL

AND V

1.5

INH

V

1.0

85oC

0.5

34 678910111213

25

-40oC

25oC

-40oC

V+ (V)

85oC

85oC

25oC

V

INL

FIGURE 15. DIGITAL SWITCHING POINT vs SUPPLY VOLTAGE

-10

V+ = 3V to 13V

-20

-30

-40

-50

-60

-70

CROSSTALK (dB)

-80

-90

-100

-110

1k 100k 1M 100M 500M10k 10M

ISOLATION

FREQUENCY (Hz)

CROSSTALK

10

20

30

40

50

60

70

80

90

100

110

FIGURE 17. CROSSTALK AND OFF ISOLATION

PHASE

NORMALIZED GAIN (dB)

RL = 50Ω

VIN = 0.2V

= 0.2V

V

IN

= 0.2V

V

IN

1 10 100 600

P-P

P-P

P-P

to 2.5V

to 4V

to 5V

(V+ = 3.3V)

P-P

(V+ = 5V)

P-P

(V+ = 12V)

P-P

FREQUENCY (MHz)

0

20

40

60

80

100

PHASE (DEGREES)

FIGURE 16. FREQUENCY RESPONSE

Die Characteristics

SUBSTRATE POTENTIAL (POWERED UP):

GND

TRANSISTOR COUNT:

ISL84541: 66

ISL84542: 66

ISL84543: 66

OFF ISOLATION (dB)

ISL84544: 58

PROCESS:

Si Gate CMOS

11

Page 12

ISL84541, ISL84542, ISL84543, ISL84544

Dual-In-Line Plastic Packages (PDIP)

N

D1

-C-

E1

-B-

A2

A

L

A

1

e

C

e

e

INDEX

AREA

BASE

PLANE

SEATING

PLANE

D1

B1

12 3 N/2

-AD

e

B

0.010 (0.25) C AM BS

NOTES:

1. Controlling Dimensions: INCH. In case of conflict between

English and Metric dimensions, the inch dimensions control.

2. Dimensioning and tolerancing per ANSI Y14.5M-1982.

3. Symbols are defined in the “MO Series Symbol List” in Section

2.2 of Publication No. 95.

4. Dimensions A, A1 and L are measured with the package seated

in JEDEC seating plane gauge GS-3.

5. D, D1, and E1 dimensions do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.010 inch

(0.25mm).

6. E and are measured with the leads constrained to be per-

7. e

e

pendicular to datum .

A

and eC are measured at the lead tips with the leads uncon-

B

strained. e

must be zero or greater.

C

-C-

8. B1 maximum dimensions do not include dambar protrusions.

Dambar protrusions shall not exceed 0.010 inch (0.25mm).

9. N is the maximum number of terminal positions.

10. Corner leads (1, N, N/2 and N/2 + 1) for E8.3, E16.3, E18.3,

E28.3, E42.6 will have a B1 dimension of 0.030 - 0.045 inch

(0.76 - 1.14mm).

E8.3 (JEDEC MS-001-BA ISSUE D)

8 LEAD DUAL-IN-LINE PLASTIC PACKAGE

INCHES MILLIMETERS

SYMBOL

A - 0.210 - 5.33 4

E

A1 0.015 - 0.39 - 4

A2 0.115 0.195 2.93 4.95 -

B 0.014 0.022 0.356 0.558 -

C

L

A

C

B

B1 0.045 0.070 1.15 1.77 8, 10

C 0.008 0.014 0.204 0.355 D 0.355 0.400 9.01 10.16 5

D1 0.005 - 0.13 - 5

E 0.300 0.325 7.62 8.25 6

E1 0.240 0.280 6.10 7.11 5

e 0.100 BSC 2.54 BSC -

e

A

e

B

0.300 BSC 7.62 BSC 6

- 0.430 - 10.92 7

L 0.115 0.150 2.93 3.81 4

N8 89

NOTESMIN MAX MIN MAX

Rev. 0 12/93

12

Page 13

ISL84541, ISL84542, ISL84543, ISL84544

Mini Small Outline Plastic Packages (MSOP)

N

EE1

INDEX

AREA

AA1A2

-H-

SIDE VIEW

12

TOP VIEW

b

e

D

NOTES:

1. These package dimensions are within allowable dimensions of

JEDEC MO-187BA.

2. Dimensioning and tolerancing per ANSI Y14.5M-1994.

3. Dimension “D” does not include mold flash, protrusions or gate

burrs and are measured at Datum Plane. Mold flash, protrusion

and gate burrs shall not exceed 0.15mm (0.006 inch) per side.

4. Dimension “E1” does not include interlead flash or protrusions

and are measured at Datum Plane. Interlead flash and

protrusions shall not exceed 0.15mm (0.006 inch) per side.

5. Formed leads shall be planar with respect to one another within

0.10mm (0.004) at seating Plane.

6. “L” is the length of terminal for soldering to a substrate.

7. “N” is the number of terminal positions.

8. Terminal numbers are shown for reference only.

9. Dimension “b” does not include dambar protrusion. Allowable

dambar protrusion shall be 0.08mm (0.003 inch) total in excess

of “b” dimension at maximum material condition. Minimum space

between protrusion and adjacent lead is 0.07mm (0.0027 inch).

- H -

-A -

.

10. Datums and to be determined at Datum plane

11. Controlling dimension: MILLIMETER. Converted inch dimensions are for reference only.

-B-

0.20 (0.008) A

GAUGE

PLANE

SEATING

PLANE

0.10 (0.004) C

-A-

0.20 (0.008) C

- B -

0.25

(0.010)

-C-

SEATING

PLANE

a

0.20 (0.008) C

- H -

B

4X θ

C

D

4X θ

L1

C

C

L

E

1

END VIEW

R1

R

L

-B-

M8.118 (JEDEC MO-187AA)

8 LEAD MINI SMALL OUTLINE PLASTIC PACKAGE

INCHES MILLIMETERS

SYMBOL

A 0.037 0.043 0.94 1.10 A1 0.002 0.006 0.05 0.15 A2 0.030 0.037 0.75 0.95 -

b 0.010 0.014 0.25 0.36 9

c 0.004 0.008 0.09 0.20 -

D 0.116 0.120 2.95 3.05 3

E1 0.116 0.120 2.95 3.05 4

e 0.026 BSC 0.65 BSC -

E 0.187 0.199 4.75 5.05 -

L 0.016 0.028 0.40 0.70 6

L1 0.037 REF 0.95 REF -

N8 87

R 0.003 - 0.07 - -

R1 0.003 - 0.07 - -

05

α

o

o

0

15

o

o

6

o

5

o

0

15

o

o

6

Rev. 2 01/03

NOTESMIN MAX MIN MAX

-

-

13

Page 14

ISL84541, ISL84542, ISL84543, ISL84544

Small Outline Plastic Packages (SOIC)

N

INDEX

AREA

123

SEATING PLANE

-AD

e

B

0.25(0.010) C AM BS

E

-B-

A

-C-

M

0.25(0.010) BM M

H

α

µ

A1

0.10(0.004)

L

h x 45

o

C

NOTES:

1. Symbols are defined in the “MO Series Symbol List” in Section 2.2 of

Publication Number 95.

2. Dimensioning and tolerancing per ANSI Y14.5M-1982.

3. Dimension “D” does not include mold flash, protrusions or gate burrs.

Mold flash, protrusion and gate burrs shall not exceed 0.15mm (0.006

inch) per side.

4. Dimension “E” does not include interlead flash or protrusions. Interlead flash and protrusions shall not exceed 0.25mm (0.010 inch) per

side.

5. The chamfer on the body is optional. If it is not present, a visual index

feature must be located within the crosshatched area.

6. “L” is the length of terminal for soldering to a substrate.

7. “N” is the number of terminal positions.

8. Terminal numbers are shown for reference only.

9. The lead width “B”, as measured 0.36mm (0.014 inch) or greater

above the seating plane, shall not exceed a maximum value of

0.61mm (0.024 inch).

10. Controlling dimension: MILLIMETER. Converted inch dimensions

are not necessarily exact.

M8.15 (JEDEC MS-012-AA ISSUE C)

8 LEAD NARROW BODY SMALL OUTLINE PLASTIC

PACKAGE

INCHES MILLIMETERS

SYMBOL

A 0.0532 0.0688 1.35 1.75 -

A1 0.0040 0.0098 0.10 0.25 -

B 0.013 0.020 0.33 0.51 9

C 0.0075 0.0098 0.19 0.25 D 0.1890 0.1968 4.80 5.00 3

E 0.1497 0.1574 3.80 4.00 4

e 0.050 BSC 1.27 BSC -

H 0.2284 0.2440 5.80 6.20 -

h 0.0099 0.0196 0.25 0.50 5

L 0.016 0.050 0.40 1.27 6

N8 87

o

α

0

o

8

o

0

o

8

Rev. 0 12/93

NOTESMIN MAX MIN MAX

-

14

Page 15

ISL84541, ISL84542, ISL84543, ISL84544

Small Outline Transistor Plastic Packages (SOT23-6)

0.20 (0.008)

C

L

b

C

L

123

A2

A

e

e1

D

C

L

C

M

456

0.10 (0.004) C

C

E E1

L

α

SEATING

A1

PLANE

-C-

L

NOTES:

1. Dimensioning and tolerances per ANSI 14.5M-1982.

2. Package conforms to EIAJ SC-74 (1992).

3. Dimensions D and E1 are exclusive of mold flash, protrusions, or

gate burrs.

4. Footlength L measured at reference to seating plane.

5. “L” is the length of flat foot surface for soldering to substrate.

6. “N” is the number of terminal positions.

7. Controlling dimension: MILLIMETER. Converted inch dimensions are for reference only

P6.064

6 LEAD SMALL OUTLINE TRANSISTOR PLASTIC PACKAGE

INCHES MILLIMETERS

SYMBOL

A 0.036 0.057 0.90 1.45 A1 0.000 0.0059 0.00 0.15 A2 0.036 0.051 0.90 1.30 -

b 0.012 0.020 0.30 0.50 -

C 0.0036 0.0078 0.09 0.20 D 0.111 0.118 2.80 3.00 3

E 0.103 0.118 2.60 3.00 -

C

E1 0.060 0.068 1.50 1.75 3

e 0.0374 Ref 0.95 Ref -

e1 0.0748 Ref 1.90 Ref -

L 0.014 0.022 0.35 0.55 4, 5

N6 66

o

α

0

10

o

o

0

10

o

NOTESMIN MAX MIN MAX

-

Rev. 2 5/01

15

Page 16

ISL84541, ISL84542, ISL84543, ISL84544

Small Outline Transistor Plastic Packages (SOT23-8)

0.20 (0.008) M

C

L

b

87

C

L

1234

e1

D

C

L

A2

A

C

e

56

0.10 (0.004) C

C

E E1

L

α

SEATING

A1

PLANE

-C-

NOTES:

1. Dimensioning and tolerances per ANSI 14.5M-1982.

2. Package patterned after EIAJ SC-74 (1992).

3. Dimensions D and E1 are exclusive of mold flash, protrusions, or

gate burrs.

4. Footlength L measured at reference to seating plane.

5. “L” is the length of flat foot surface for soldering to substrate.

6. “N” is the number of terminal positions.

7. Controlling dimension: MILLIMETER. Converted inch dimensions are for reference only.

P8.064

8 LEAD SMALL OUTLINE TRANSISTOR PLASTIC PACKAGE

INCHES MILLIMETERS

L

SYMBOL

A 0.036 0.057 0.90 1.45 A1 0.000 0.0059 0.00 0.15 A2 0.036 0.051 0.90 1.30 -

b 0.011 0.018 0.28 0.45 -

C 0.0036 0.0078 0.09 0.20 D 0.111 0.118 2.80 3.00 3

E 0.103 0.118 2.60 3.00 -

C

E1 0.060 0.068 1.50 1.75 3

e 0.0256 Ref 0.65 Ref e1 0.0768 Ref 1.95 Ref -

L 0.012 0.020 0.30 0.50 4, 5

N8 86

o

α

0

10

o

o

0

10

NOTESMIN MAX MIN MAX

o

Rev. 1 10/01

-

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems.

Intersil Corporation’s quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without

notice. Accordingly, the reader is cautioned to verify that data she ets are current before placin g orders. Information furn ished by Intersil is believed to be accurate and

reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result

from its use. No license is granted by implication or othe rwise under any patent or patent righ ts of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com

16

Loading...

Loading...