intersil ISL6615A DATA SHEET

®

ISL6615A

Data Sheet April 30, 2008

High-Frequency 6A Sink Synchronous

MOSFET Drivers with Protection Features

The ISL6615A is a high-speed MOSFET driver optimized to

drive upper and lower power N-Channel MOSFETs in a

synchronous rectified buck converter topology. This driver,

combined with an Intersil Digital or Analog multiphase PWM

controller, forms a complete high frequency and high

efficiency voltage regulator.

The ISL6615A drives both upper and lower gates over a

range of 4.5V to 13.2V. This drive-voltage provides the

flexibility necessary to optimize applications involving

trade-offs between gate charge and conduction losses.

The ISL6615A features 6A typical sink current for the

low-side gate driver, enhancing the lower MOSFET gate

hold-down capability during PHASE node rising edge,

preventing power loss caused by the self turn-on of the lower

MOSFET due to the high dV/dt of the switching node.

An advanced adaptive zero shoot-through protection is

integrated to prevent both the upper and lower MOSFETs

from conducting simultaneously and to minimize the

dead-time. The ISL6615A includes an overvoltage protection

feature operational before VCC exceeds its turn-on

threshold, at which the PHASE node is connected to the

gate of the low side MOSFET (LGATE). The output voltage

of the converter is then limited by the threshold of the low

side MOSFET, which provides some protection to the load if

the upper MOSFET(s) is shorted.

The ISL6615A also features an input that recognizes a

high-impedance state, working together with Intersil

multiphase PWM controllers to prevent negative transients

on the controlled output voltage when operation is

suspended. This feature eliminates the need for the Schottky

diode that may be utilized in a power system to protect the

load from negative output voltage damage.

FN6608.0

Features

• Dual MOSFET Drives for Synchronous Rectified Bridge

• Advanced Adaptive Zero Shoot-Through Protection

- Body Diode Detection

- LGATE Detection

- Auto-zero of r

• Adjustable Gate Voltage for Optimal Efficiency

• 36V Internal Bootstrap Schottky Diode

• Bootstrap Capacitor Overcharging Prevention

• Supports High Switching Frequency (up to 1MHz)

- 6A LGATE Sinking Current Capability

- Fast Rise/Fall Times and Low Propagation Delays

• Support 5V PWM Input Logic

• Tri-State PWM Input for Safe Output Stage Shutdown

• Tri-State PWM Input Hysteresis for Applications with

Power Sequencing Requirement

• Pre-POR Overvoltage Protection

• VCC Undervoltage Protection

• Expandable Bottom Copper PAD for Better Heat

Spreading

• Dual Flat No-Lead (DFN) Package

- Near Chip-Scale Package Footprint; Improves PCB

Efficiency and Thinner in Profile

• Pb-free (RoHS compliant)

Conduction Offset Effect

DS(ON)

Applications

• Optimized for POL DC/DC Converters for IBA Systems

• Core Regulators for Intel® and AMD® Microprocessors

• High Current Low-Profile DC/DC Converters

• High Frequency and High Efficiency VRM and VRD

• Synchronous Rectification for Isolated Power Supplies

Related Literature

Technical Brief TB363 “Guidelines for Handling and

Processing Moisture Sensitive Surface Mount Devices

(SMDs)”

Technical Brief TB389 “PCB Land Pattern Design and

Surface Mount Guidelines for QFN Packages”

1

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 1-888-468-3774

| Intersil (and design) is a registered trademark of Intersil Americas Inc.

All other trademarks mentioned are the property of their respective owners.

Copyright Intersil Americas Inc. 2008. All Rights Reserved

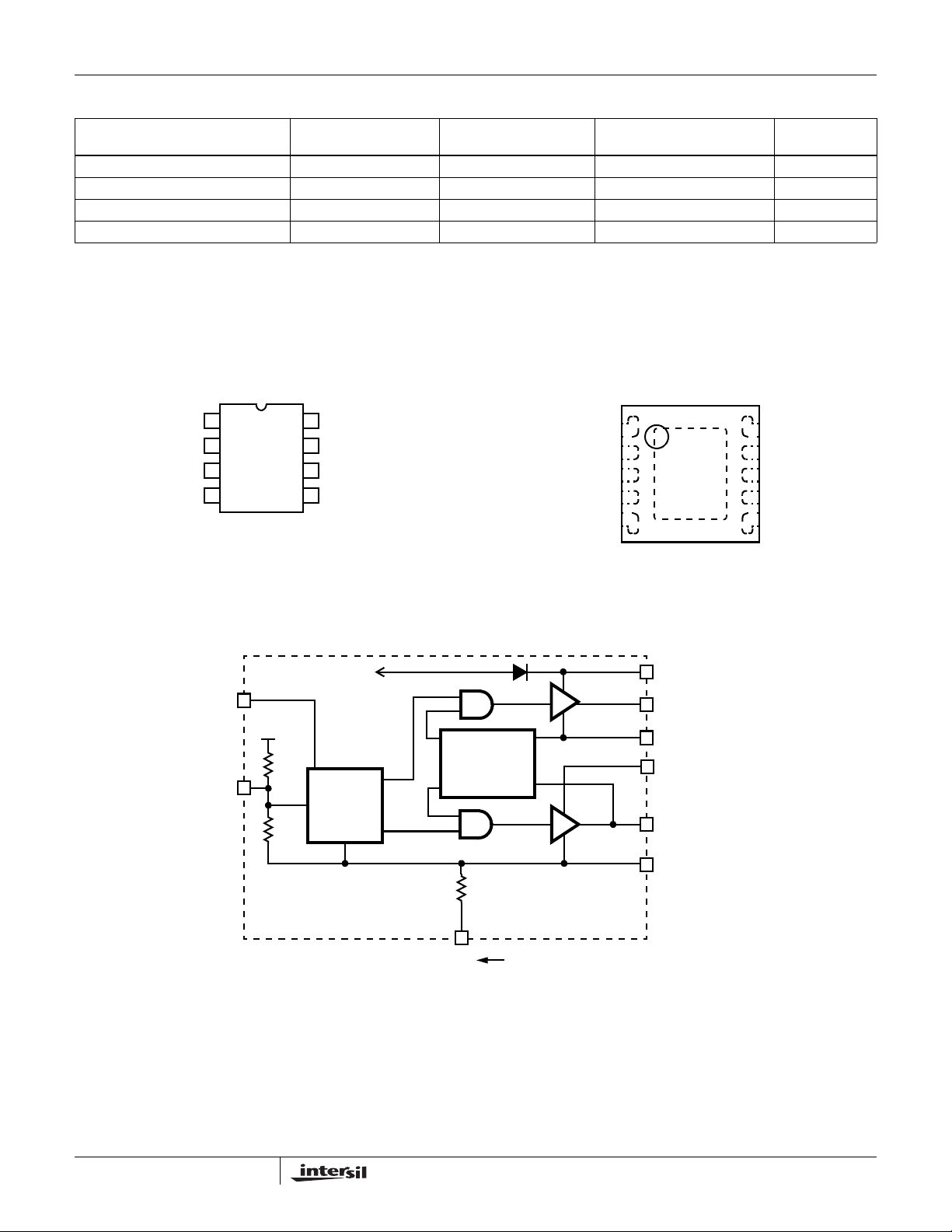

ISL6615A

Ordering Information

PART NUMBER

(Note) PART MARKING

ISL6615ACBZ* 6615A CBZ 0 to +70 8 Ld SOIC M8.15

ISL6615ACRZ* 615A 0 to +70 10 Ld 3x3 DFN L10.3x3

ISL6615AIBZ* 6615A IBZ -40 to +70 8 Ld SOIC M8.15

ISL6615AIRZ* 15AI -40 to +70 10 Ld 3x3 DFN L10.3x3

*Add “-T” suffix for tape and reel. Please refer to TB347 for details on reel specifications.

NOTE: These Intersil Pb-free plastic packaged products employ special Pb-free material sets; molding compounds/die attach materials and 100%

matte tin plate PLUS ANNEAL - e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations.

Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J

STD-020.

TEMP.

RANGE (°C)

PACK AGE

(Pb-free)

PKG.

DWG. #

Pinouts

ISL6615ACB

(8 LD SOIC)

TOP VIEW

ISL6615ACR

(10 LD 3x3 DFN)

TOP VIEW

UGATE

BOOT

PWM

GND

Block Diagram

1

2

3

4

VCC

PWM

+5V

10k

8k

8

PHASE

7

PVCC

6

VCC

5

LGATE

(UVCC)

PRE-POR OVP

FEATURES

POR/

CONTROL

LOGIC

ISL6615A

SHOOT-

THROUGH

PROTECTION

10

9

8

7

6

PHASE

PVCC

N/C

VCC

LGATE

BOOT

N/C

PWM

GND

1

2

3

4

5

GND

BOOT

UGATE

PHASE

PVCC

LGATE

GND

UVCC = PVCC

UGATE

RECOMMEND TO CONNECT PIN 3 TO GND AND PIN 8 TO PVCC

(LVCC)

SUBSTRATE RESIST ANCE

PAD

2

FOR DFN DEVICES, THE PAD ON THE BOTTOM SIDE OF

THE PACKAGE MUST BE SOLDERED TO THE CIRCUIT’S GROUND.

FN6608.0

April 30, 2008

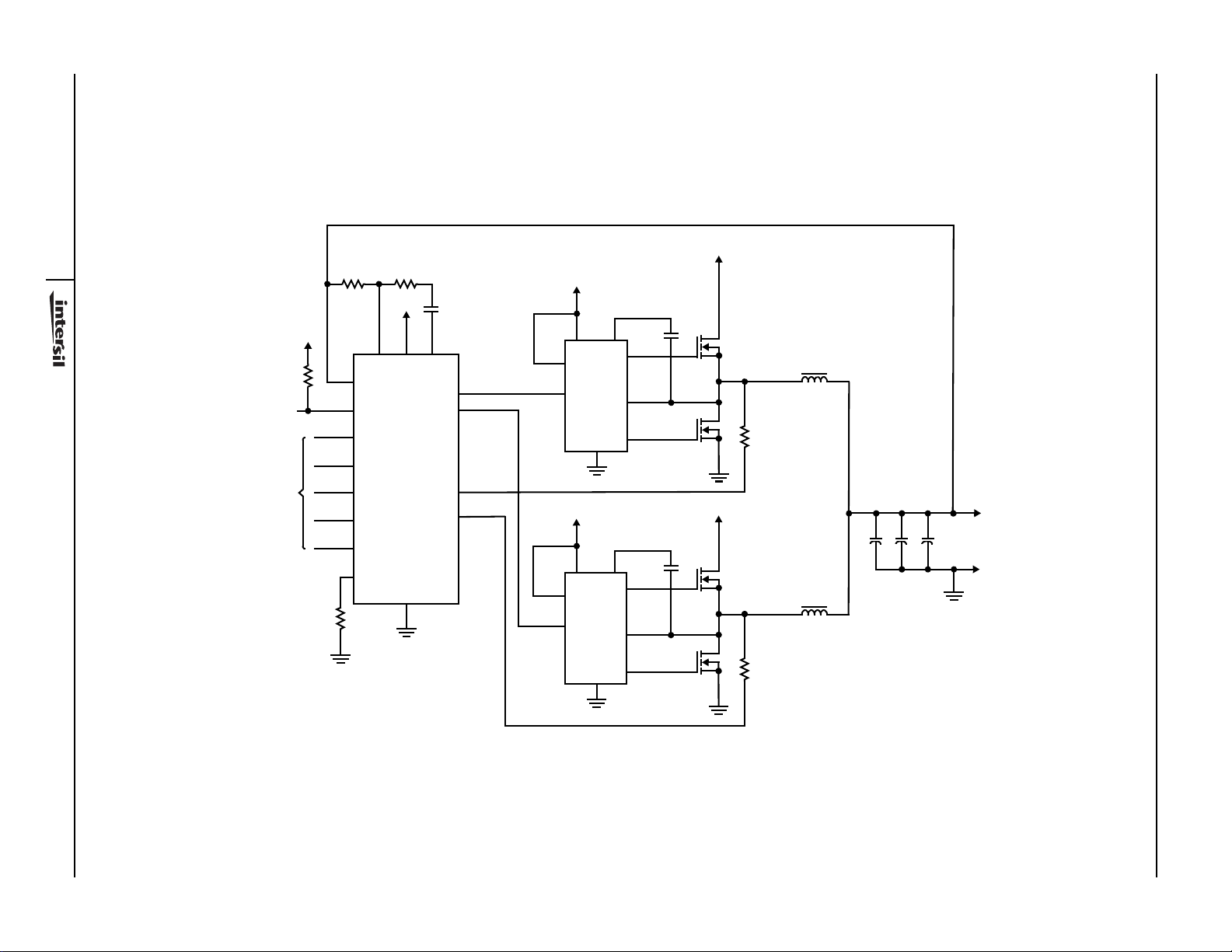

Typical Application - 2 Channel Converter

3

+7V TO +13.2V

+5V

GND

GND

BOOT

UGATE

PHASE

LGATE

BOOT

UGATE

PHASE

LGATE

PGOOD

VID

(OPTIONAL)

+5V

FB

VCC

VSEN

PWM

CONTROL

(ISL63xx

OR ISL65xx)

FS/EN

GND

COMP

PWM1

PWM2

ISEN1

ISEN2

PVCC

VCC

PWM

ISL6615A

+7V TO +13.2V

PVCC

VCC

PWM

ISL6615A

V

IN

ISL6615A

+V

V

IN

CORE

THE ISL6615A CAN SUPPORT 5V PWM INPUT

April 30, 2008

FN6608.0

ISL6615A

Absolute Maximum Ratings Thermal Information

Supply Voltage (VCC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15V

Supply Voltage (PVCC) . . . . . . . . . . . . . . . . . . . . . . . . . VCC + 0.3V

BOOT Voltage (V

Input Voltage (V

UGATE. . . . . . . . . . . . . . . . . . . V

V

BOOT-GND

PWM

- 3.5V (<100ns Pulse Width, 2µJ) to V

PHASE

LGATE. . . . . . . . . . . . . . . . . . . . . . GND - 0.3V

GND - 5V (<100ns Pulse Width, 2µJ) to V

PHASE. . . . . . . . . . . . . . . . . . . . . . . . . . . . GND - 0.3V

GND - 8V (<400ns, 20µJ) to 30V (<200ns, V

ESD Rating

). . . . . . . . . . . . . . . . . . . . . . . . . . . .36V

) . . . . . . . . . . . . . . . . . . . . . .GND - 0.3V to 7V

PHASE

- 0.3VDC to V

to V

DC

BOOT-GND

BOOT

BOOT

PVCC

PVCC

to 15V

DC

+ 0.3V

+ 0.3V

+ 0.3V

+ 0.3V

DC

< 36V))

Human Body Model . . . . . . . . . . . . . . . . . . . .Class I JEDEC STD

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and

result in failures not covered by warranty.

NOTES:

is measured with the component mounted on a high effective thermal conductivity test board in free air.

1. θ

JA

is measured in free air with the component mounted on a high effective thermal conductivity test board with “direct attach” features. See

2. θ

JA

Tech Brief TB379.

3. For θ

, the “case temp” location is the center of the exposed metal pad on the package underside.

JC

Thermal Resistance θ

(°C/W) θJC (°C/W)

JA

SOIC Package (Note 1) . . . . . . . . . . . . 100 N/A

DFN Package (Notes 2, 3). . . . . . . . . . 48 7

Maximum Junction Temperature (Plastic Package) . . . . . . .+150°C

Maximum Storage Temperature Range. . . . . . . . . .-65°C to +150°C

Pb-free reflow profile . . . . . . . . . . . . . . . . . . . . . . . . . .see link below

http://www.intersil.com/pbfree/Pb-FreeReflow.asp

Recommended Operating Conditions

Ambient Temperature Range

ISL6615ACRZ, ISL6615ACBZ. . . . . . . . . . . . . . . . . 0°C to +70°C

ISL6615AIRZ, ISL6615AIBZ . . . . . . . . . . . . . . . . .-40°C to +85°C

Maximum Operating Junction Temperature. . . . . . . . . . . . . . +125°C

VCC Supply Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . 6.8V to 13.2V

PVCC Supply Voltage . . . . . . . . . . . . . . . . . . . . . . . 5V to 12V ±10%

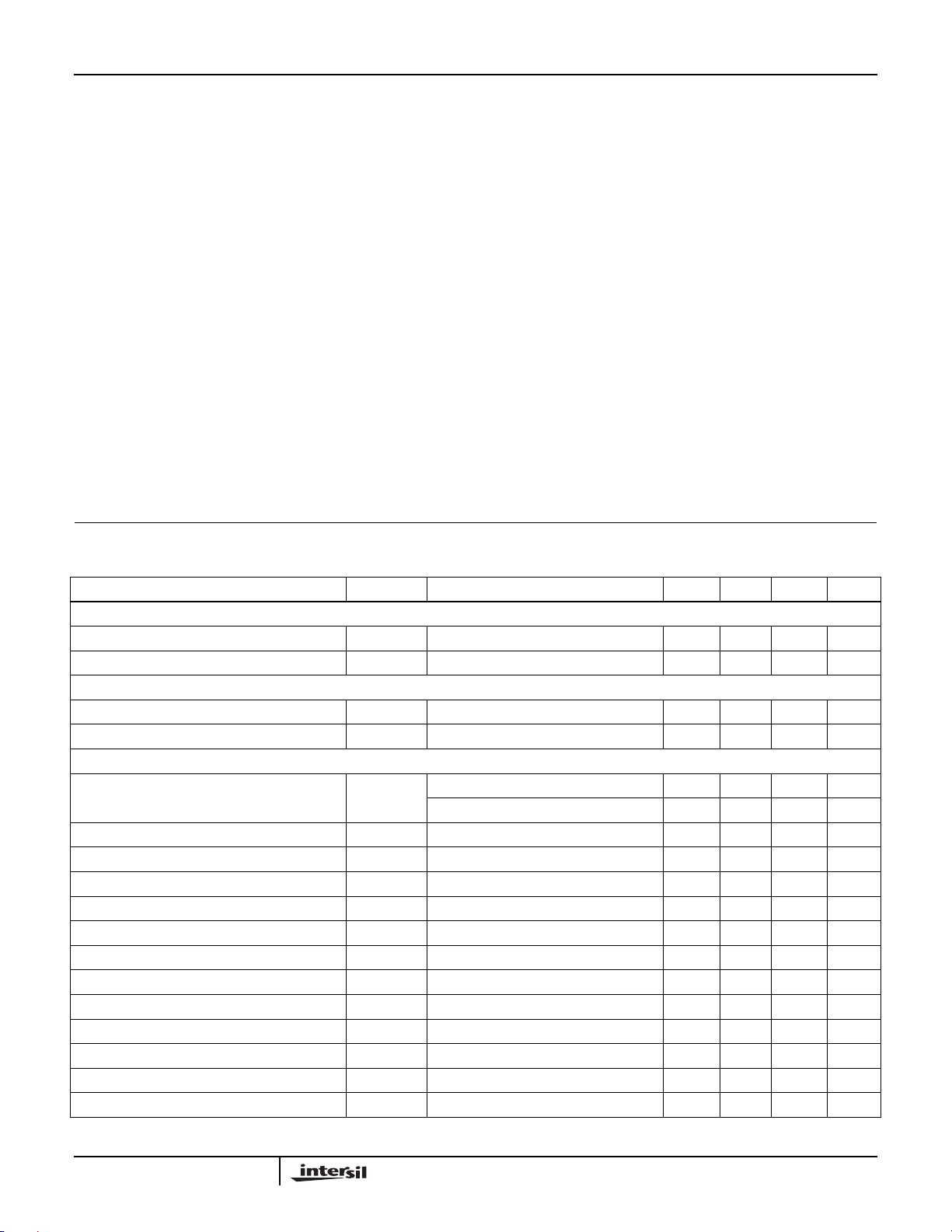

Electrical Specifications Recommended Operating Conditions; Parameters with MIN and/or MAX limits are 100% tested at +25°C,

unless otherwise specified. Temperature limits established by characterization and are not production

tested.

PARAMETER SYMBOL TEST CONDITIONS MIN TYP MAX UNITS

VCC SUPPLY CURRENT

Bias Supply Current I

Gate Drive Bias Current I

VCC

PVCC

POWER-ON RESET AND ENABLE

VCC Rising Threshold 6.1 6.4 6.7 V

VCC Falling Threshold 4.7 5.0 5.3 V

PWM INPUT (See “TIMING DIAGRAM” on page 6)

Input Current I

PWM

PWM Rising Threshold (Note 4) VCC = 12V - 3.00 - V

PWM Falling Threshold (Note 4) VCC = 12V - 2.00 - V

Typical Tri-State Shutdown Window VCC = 12V 1.80 - 2.40 V

Tri-State Lower Gate Falling Threshold VCC = 12V - 1.50 - V

Tri-State Lower Gate Rising Threshold VCC = 12V - 1.00 - V

Tri-State Upper Gate Rising Threshold VCC = 12V - 3.20 - V

Tri-State Upper Gate Falling Threshold VCC = 12V - 2.70 - V

Shutdown Holdoff Time t

UGATE Rise Time (Note 4) t

LGATE Rise Time (Note 4) t

UGATE Fall Time (Note 4) t

LGATE Fall Time (Note 4) t

TSSHD

RU

RL

FU

FL

f

= 300kHz, V

PWM

f

= 300kHz, V

PWM

V

= 5V - 510 - µA

PWM

V

= 0V - -475 - µA

PWM

= 12V - 4.5 - mA

VCC

= 12V - 8 - mA

PVCC

-65-ns

V

= 12V, 3nF Load, 10% to 90% - 13 - ns

PVCC

V

= 12V, 3nF Load, 10% to 90% - 10 - ns

PVCC

V

= 12V, 3nF Load, 90% to 10% - 10 - ns

PVCC

V

= 12V, 3nF Load, 90% to 10% - 10 - ns

PVCC

4

FN6608.0

April 30, 2008

Loading...

Loading...