intersil ISL6524 DATA SHEET

查询ISL6524ACB供应商

®

ISL6524

Data Sheet April 18, 2005

VRM8.5 PWM and Triple Linear Power

System Controller

The ISL6524 provides the power control and protection for

four output voltages in high-performance microprocessor

and computer applications. The IC integrates one PWM

controller and three linear controllers, as well as the

monitoring and protection functions into a 28-pin SOIC

package. The PWM controller regulates the microprocessor

core voltage with a synchronous-rectified buck converter.

One linear controller supplies the computer system’s AGTL+

1.2V bus power. The other two linear controllers regulate

power for the 1.5V AGP bus and the 1.8V power for the chip

set core voltage and/or cache memory circuits.

The ISL6524 includes an Intel VRM8.5 compatible, TTL

5-input digital-to-analog converter (DAC) that adjusts the

microprocessor core-targeted PWM output voltage from

1.050V to 1.825V in 25mV steps. The precision reference and

voltage-mode control provide ±1% static regulation. The linear

regulators use external N-channel MOSFETs or bipolar NPN

pass transistors to provide fixed output voltages of 1.2V ±3%

(V

The ISL6524 monitors all the output voltages. A delayedrising VTT (V

before the core PWM starts to ramp up. Another system

Power Good signal is issued when the core is within ±10% of

the DAC setting and all other outputs are above their undervoltage levels. Additional built-in overvoltage protection for

the core output uses the lower MOSFET to prevent output

voltages above 115% of the DAC setting. The PWM

controllers’ overcurrent function monitors the output current

by using the voltage drop across the upper MOSFET’s

r

), 1.5V ±3% (V

OUT2

output) Power Good signal is issued

OUT2

, eliminating the need for a current sensing resistor.

DS(ON)

) and 1.8V ±3% (V

OUT3

OUT4

).

FN9015.3

Features

• Provides 4 Regulated Voltages

- Microprocessor Core, AGTL+ Bus, AGP Bus Power,

and North/South Bridge Core

• Drives N-Channel MOSFETs

• Linear Regulator Drives Compatible with both MOSFET

and Bipolar Series Pass Transistors

• Simple Single-Loop Control Design

- Voltage-Mode PWM Control

• Fast PWM Converter Transient Response

- High-Bandwidth Error Amplifier

- Full 0% to 100% Duty Ratio

• Excellent Output Voltage Regulation

- Core PWM Output: ±1% Over Temperature

- All Other Outputs: ±3% Over Temperature

• VRM8.5 TTL-Compatible 5-Bit DAC Microprocessor Core

Output Voltage Selection

- Wide Range - 1.050V to 1.825V

• Power-Good Output Voltage Monitors

- Separate delayed VTT Power Good

• Overcurrent Fault Monitor

- Switching Regulator Doesn’t Require Extra Current

Sensing Element, Uses MOSFET’s r

DS(ON)

• Small Converter Size

- Constant Frequency Operation

- 200kHz Internal Oscillator

• Pb-Free Available (RoHS Compliant)

Applications

•

Motherboard Power Regulation for Computers

Ordering Information

TEMP.

PAR T N UMBER

ISL6524CB* 0 to 70 28 Ld SOIC M28.3

ISL6524CBZ*

(See Note)

ISL6524CBZA*

(See Note)

ISL6524EVAL1 Evaluation Board

*Add “-T” suffix for tape and reel.

NOTE: Intersil Pb-free products employ special Pb-free material

sets; molding compounds/die attach materials and 100% matte tin

plate termination finish, which are RoHS compliant and compatible

with both SnPb and Pb-free soldering operations. Intersil Pb-free

products are MSL classified at Pb-free peak reflow temperatures that

meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

RANGE (°C) PACKAGE

0 to 70 28 Ld SOIC

(Pb-free)

0 to 70 28 Ld SOIC

(Pb-free)

1

PKG.

DWG. #

M28.3

M28.3

1-888-INTERSIL or 1-888-352-6832

Pinout

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

Copyright Intersil Americas Inc. 2001-2002, 2004-2005. All Rights Reserved

All other trademarks mentioned are the property of their respective owners.

ISL6524 (SOIC) TOP VIEW

VCC

DRIVE2

PGOOD

FAULT/RT

| Intersil (and design) is a registered trademark of Intersil Americas Inc.

FIX

VID3

VID2

VID1

VID0

VID25

VTTPG

VSEN2

SS24

SS13

VSEN4

1

2

3

4

5

6

7

8

9

10

11

12

13

14

28

27

26

25

24

23

22

21

20

19

18

17

16

15

UGATE

PHASE

LGATE

PGND

OCSET

VSEN1

FB

COMP

VSEN3

DRIVE3

GND

VAU X

DRIVE4

VAUX

PGOOD

UGATE

PHASE

LGATE

PGND

GND

VCC

OCSET

VSEN1

POWER-ON

RESET (POR)

VCC

DRIVE1

200µA

-

+

1.10

x

-

+

0.90

x

-

+

1.15

x

OV

-

+

OC

SOFT-

LOGIC

START

AND FAULT

GATE

CONTROL

+

-

+

VCC

VCC

-

EA1

PWM

PWM

COMP

DRIVE

SYNCH

(DAC)

TTL D/A

CONVERTER

DACOUT

28µA

28µA

4.5V

4.5V

VID25

VID0

VID1

VID2

VID3

COMP

FB

SS24

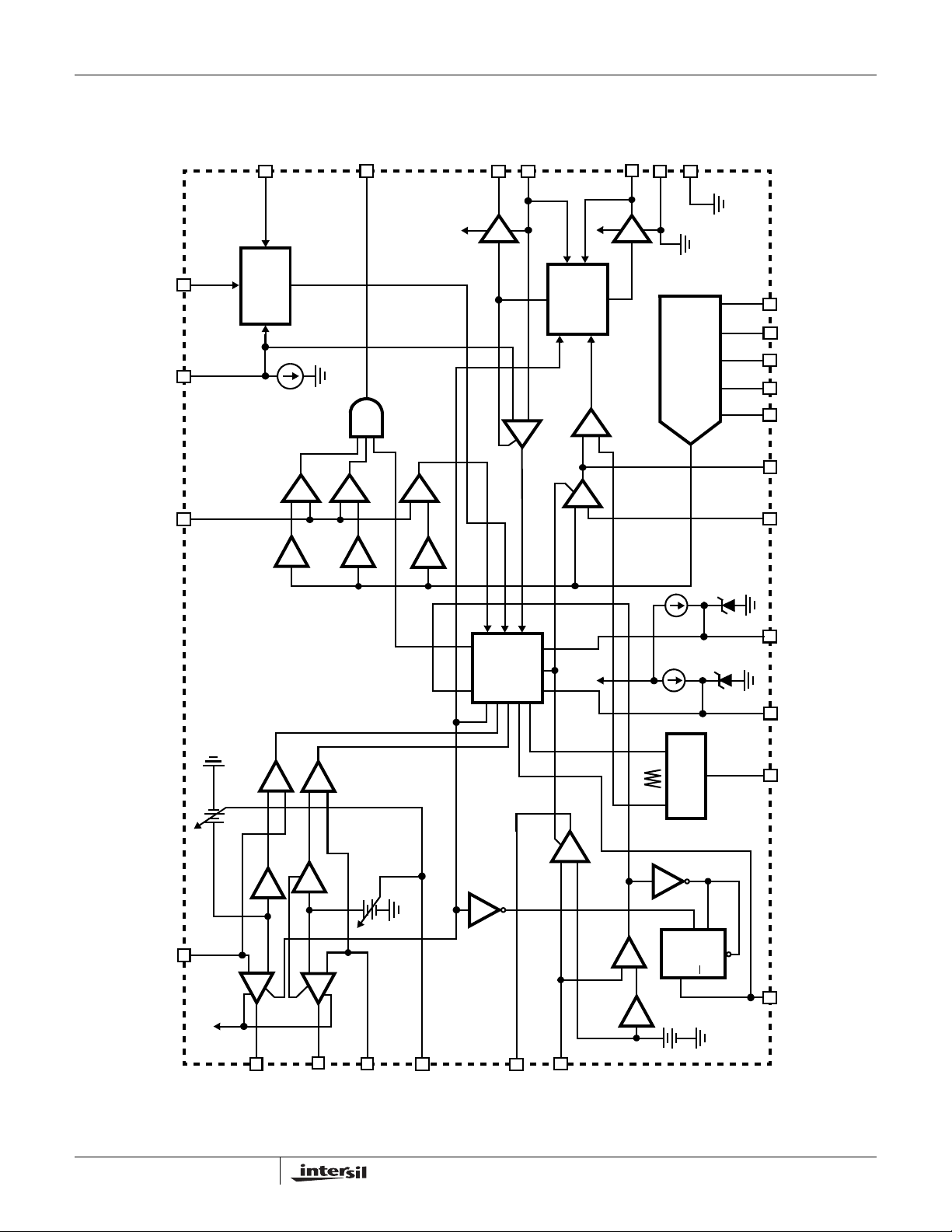

FIGURE 1.

VSEN3

Block Diagram

-

+

1.5V or 1.26V

VAUX

EA3

UV3

-

x0.75

-

+

DRIVE3

2

SS13

FAULT

UV4

-

+

+

x0.75

-

+

DRIVE4

EA4

1.8V or 1.26V

+

-

VSEN4

OSCILLATOR

INHIBIT

FIX

DRIVE2

-

+

VSEN2

EA2

UV2

-

>

D

+

x0.90

CLK

SET

+

1.2V

CLR

Q

Q

-

FAULT/RT

VTTPG

FN9015.3

April 18, 2005

+5V

IN

+3.3V

+12V

V

OUT2

1.2V

+5V

Q1

V

OUT1

V

OUT2

Q3

LINEAR

CONTROLLER

PWM1

CONTROLLER

Q2

ISL6524

IN

V

OUT3

Q4

LINEAR

CONTROLLER

LINEAR

CONTROLLER

Q5

V

OUT4

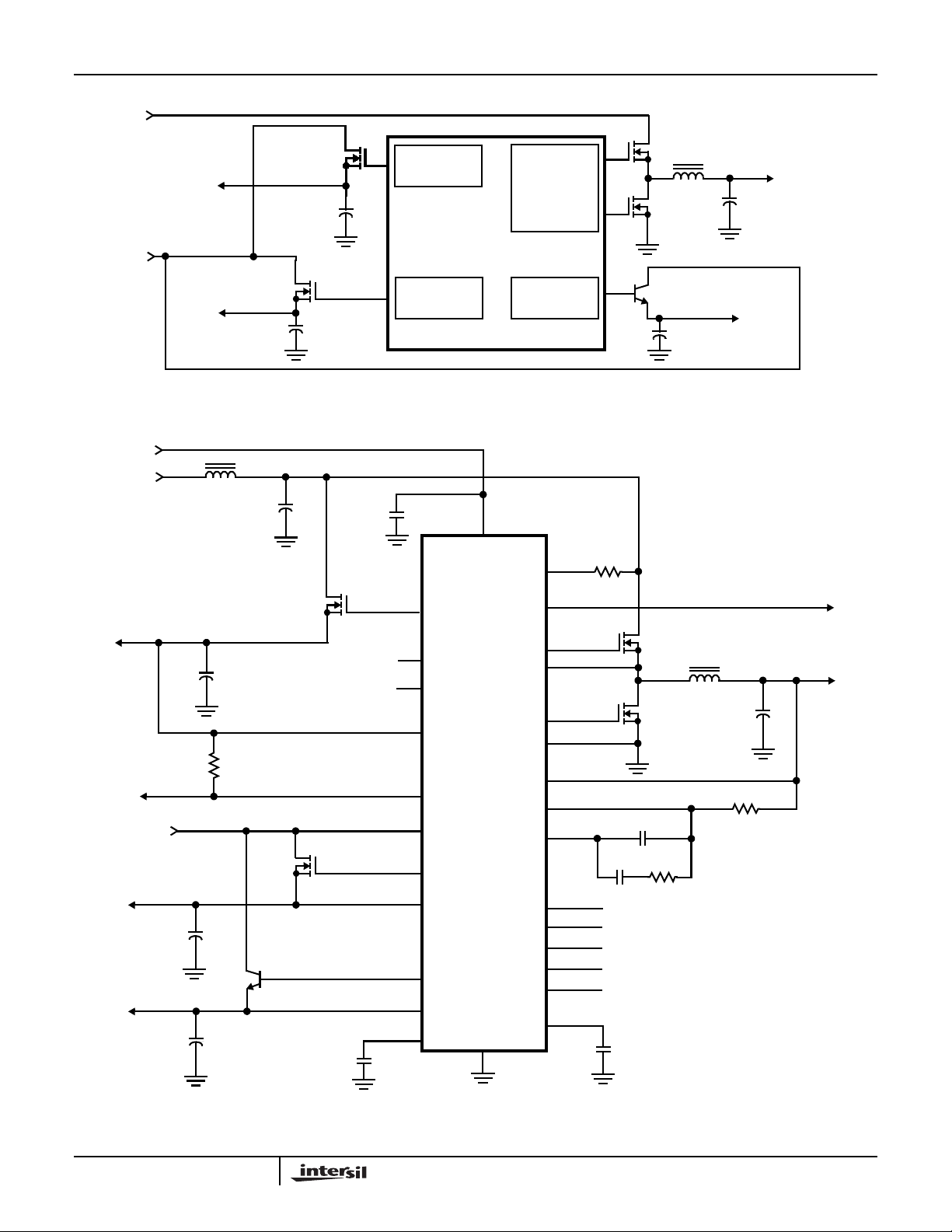

FIGURE 2. SIMPLIFIED POWER SYSTEM DIAGRAM

IN

IN

L

IN

C

OUT2

C

IN

VCC

OCSET

Q3

DRIVE2

FAULT/RT

PGOOD

UGATE

PHASE

Q1

L

OUT1

POWERGOOD

V

OUT1

1.3V to 3.5V

FIX

VTT POWERGOOD

+3.3V

IN

V

OUT3

1.5V

C

OUT3

V

OUT4

1.8V

C

OUT4

Q5

Q4

C

VSEN2

VTTPG

ISL6524

VAUX

DRIVE3

VSEN3

DRIVE4

VSEN4

SS24

SS24

FIGURE 3. TYPICAL APPLICATION

GND

LGATE

PGND

VSEN1

FB

COMP

VID3

VID2

VID1

VID0

VID25

SS13

C

SS13

Q2

C

OUT1

3

FN9015.3

April 18, 2005

Absolute Maximum Ratings Thermal Information

Supply Voltage, VCC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .+15V

PGOOD, RT/FAULT, DRIVE, PHASE, and

GATE Voltage. . . . . . . . . . . . . . . . . . . GND - 0.3V to V

CC

+ 0.3V

Input, Output or I/O Voltage. . . . . . . . . . . . . . . . . . GND -0.3V to 7V

ESD Classification . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Class 1

Thermal Resistance (Typical, Note 1)

θ

JA

(oC/W)

SOIC Package . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

Maximum Junction Temperature (Plastic Package) . . . . . . . .150

Maximum Storage Temperature Range. . . . . . . . . . -65

o

C to 150oC

Maximum Lead Temperature (Soldering 10s) . . . . . . . . . . . . . 300

(SOIC - Lead Tips Only)

o

C

o

C

Recommended Operating Conditions

Supply Voltage, VCC . . . . . . . . . . . . . . . . . . . . . . . . . . . +12V ±10%

Ambient Temperature Range. . . . . . . . . . . . . . . . . . . . 0

Junction Temperature Range. . . . . . . . . . . . . . . . . . . 0

CAUTION: Stresses above those listed in “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress only rating and operation of the

device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

NOTE:

is measured with the component mounted on a low effective thermal conductivity test board in free air. See Tech Brief TB379 for details.

1. θ

JA

o

C to 70oC

o

C to 125oC

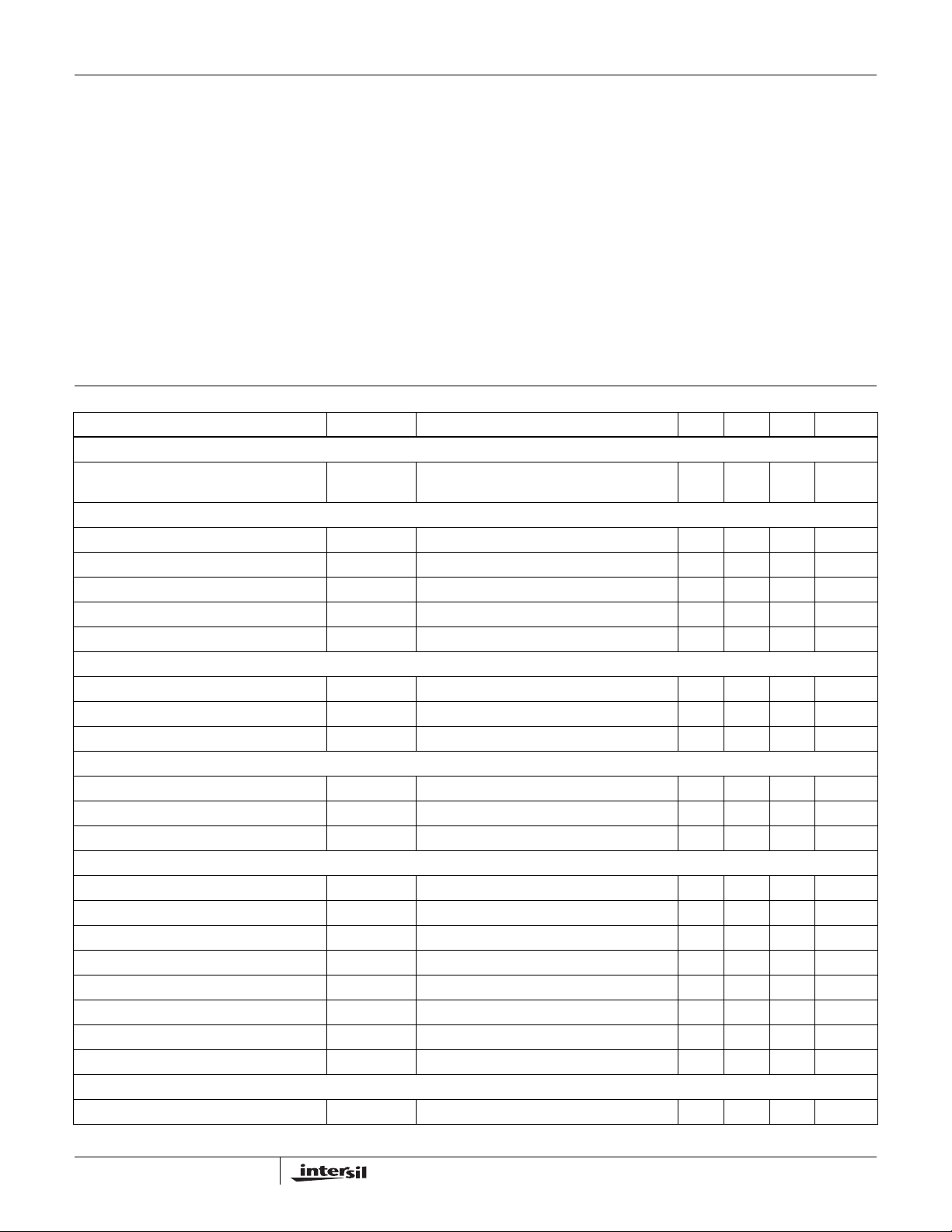

Electrical Specifications Recommended Operating Conditions, Unless Otherwise Noted. Refer to Figures 1, 2 and 3

PARAMETER SYMBOL TEST CONDITIONS MIN TYP MAX UNITS

VCC SUPPLY CURRENT

Nominal Supply Current I

CC

POWER-ON RESET

Rising VCC Threshold - - 10.4 V

Falling VCC Threshold 8.2 - - V

Rising VAUX Threshold -2.5- V

VAUX Threshold Hysteresis -0.5- V

Rising V

Threshold -1.26- V

OCSET

OSCILLATOR

Free Running Frequency F

OSC

Total Variation 6kΩ < RT to GND < 200kΩ; Note 2 -15 - +15 %

Ramp Amplitude ∆V

OSC

DAC REFERENCE

DAC (VID25-VID3) Input Low Voltage 0.8 V

DAC (VID25-VID3) Input High Voltage 2.0 V

DACOUT Voltage Accuracy -1.0 - +1.0 %

LINEAR REGULATORS (V

OUT2

, V

OUT3

, AND V

OUT4

Regulation Tolerance -3- %

VSEN3 Regulation Voltage VREG

VSEN2 Regulation Voltage VREG

VSEN3 Regulation Voltage VREG

VSEN4 Regulation Voltage VREG

VSEN3, 4 Undervoltage Level VSEN3, 4

VSEN3, 4 Undervoltage Hysteresis VSEN3, 4 Falling 7 %

Output Drive Current VAUX-V

SYNCHRONOUS PWM CONTROLLER ERROR AMPLIFIER

DC Gain Note 2 - 88 - dB

UGATE, LGATE, DRIVE2, DRIVE3, and

-9- mA

DRIVE4 Open

185 200 215 kHz

-1.9- V

)

FIX = 0V - 1.26 - V

3

2

FIX = Open - 1.5 - V

3

FIX = Open - 1.8 - V

4

VSEN3, 4 Rising - 75 - %

UV

DRIVE2,3,4

> 0.6V 20 40 - mA

-1.2- V

P-P

4

FN9015.3

April 18, 2005

Electrical Specifications Recommended Operating Conditions, Unless Otherwise Noted. Refer to Figures 1, 2 and 3 (Continued)

PARAMETER SYMBOL TEST CONDITIONS MIN TYP MAX UNITS

Gain-Bandwidth Product GBWP Note 2 - 15 - MHz

Slew Rate SR COMP = 10pF, Note 2 - 6 - V/µs

PWM CONTROLLERS GATE DRIVERS

UGATE Source I

UGATE Sink R

LGATE Source I

LGATE Sink R

UGATE

UGATE

LGATE

LGATE

PROTECTION

FAULT Sourcing Current I

OCSET Current Source I

Soft-Start Current I

OVP

OCSET

SS13,24

POWER GOOD

VSEN1 Upper Threshold

(VSEN1/DACOUT)

VSEN1 Undervoltage

(VSEN1/DACOUT)

VSEN1 Hysteresis (VSEN1/DACOUT) VSEN1 Falling - 2 - %

PGOOD Voltage Low V

PGOODIPGOOD

VSEN2 Undervoltage VSEN2 Rising 1.08 V

VSEN2 Hysteresis VSEN2 Falling - 48 - mV

VTTPG Voltage Low V

VTTPGIVTTPG

NOTE:

2. Guaranteed by design

VCC = 12V, V

V

GATE-PHASE

VCC = 12V, V

V

= 1V - 1.4 3.0 Ω

LGATE

V

FAULT/R T

V

OCSET

V

SS13,24

= 2.0V - 8.5 - mA

= 4.5V

= 2.0V

= 6V - 1 - A

UGATE

= 1V - 1.7 3.5 Ω

= 1V - 1 - A

LGATE

DC

DC

170 200 230 µA

-28- µA

VSEN1 Rising 108 - 110 %

VSEN1 Rising 92 - 94 %

= -4mA - - 0.8 V

= -4mA - - 0.8 V

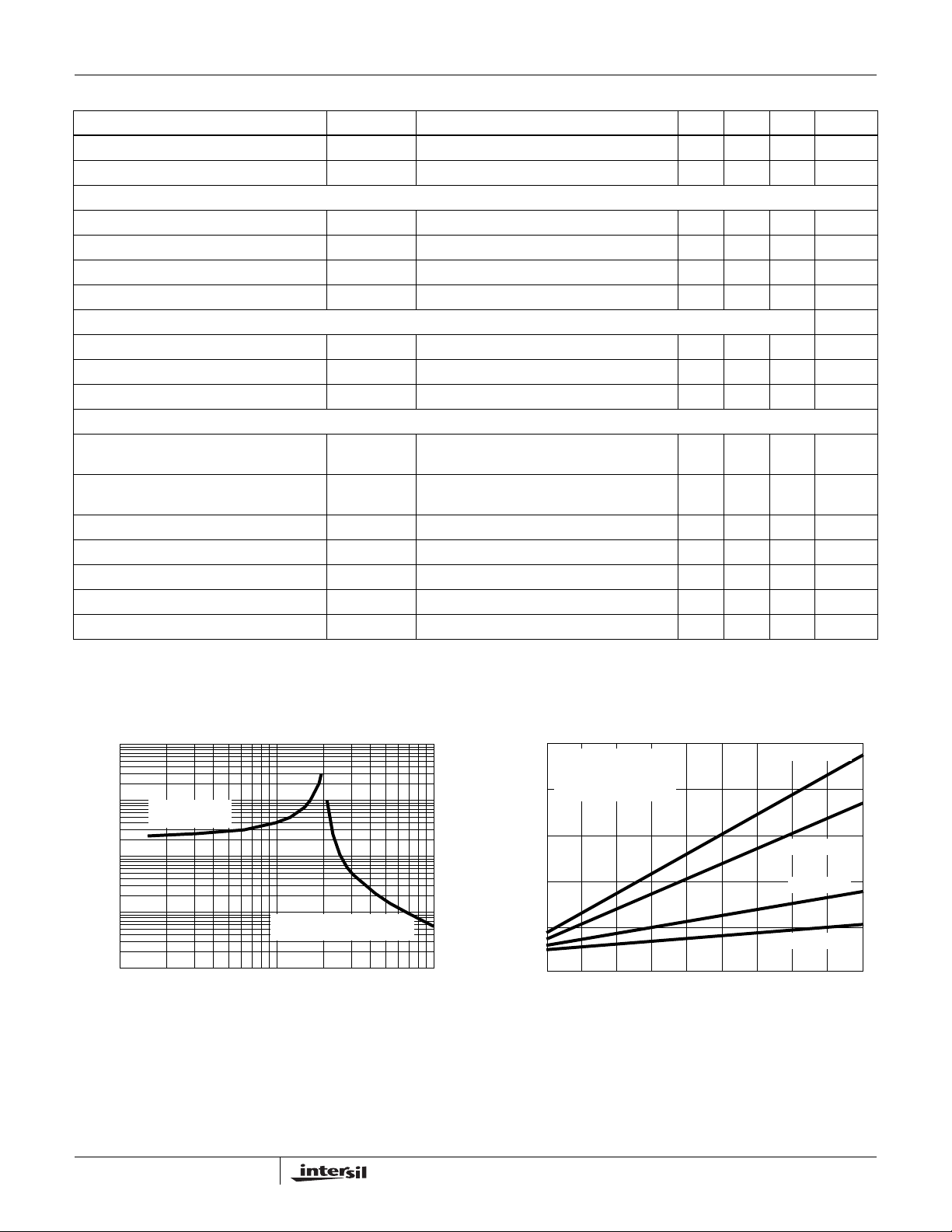

Typical Performance Curves

1000

100

RESISTANCE (kΩ)

10

RT PULLUP

TO +12V

RT PULLDOWN TO V

10 100 1000

SWITCHING FREQUENCY (kHz)

FIGURE 4. RT RESISTANCE vs FREQUENCY FIGURE 5. BIAS SUPPLY CURRENT vs FREQUENCY

SS

100

C

= C

UGATE

VIN = 5V

80

VCC = 12V

60

(mA)

CC

I

40

20

0

100 200 300 400 500 600 700 800 900 1000

= C

LGATE

SWITCHING FREQUENCY (kHz)

C = 4800pF

C = 3600pF

C = 1500pF

C = 660pF

5

FN9015.3

April 18, 2005

Loading...

Loading...