Intersil ISL6377HRZ, ISL6377IRZ Schematics

Multiphase PWM Regulator for AMD Fusion™ Desktop

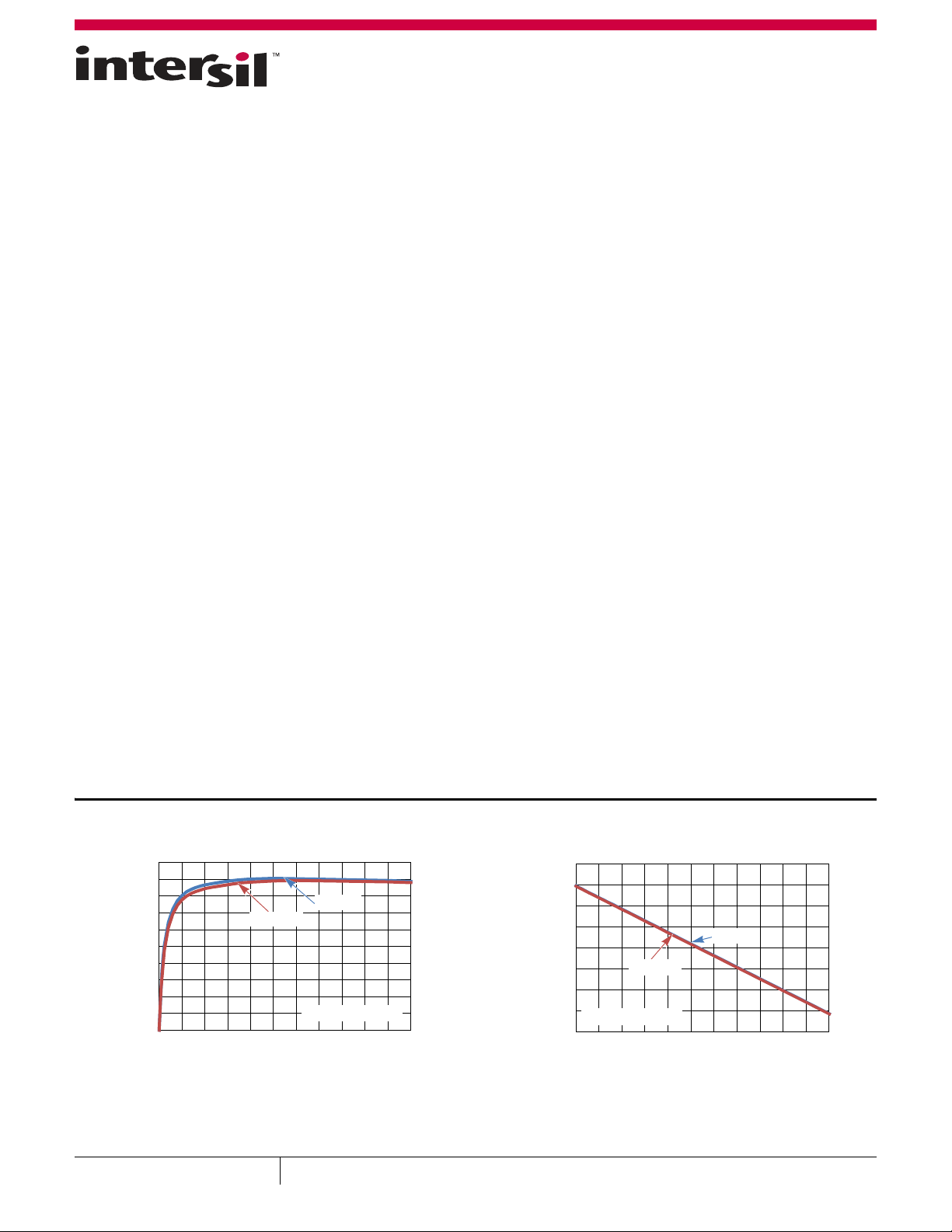

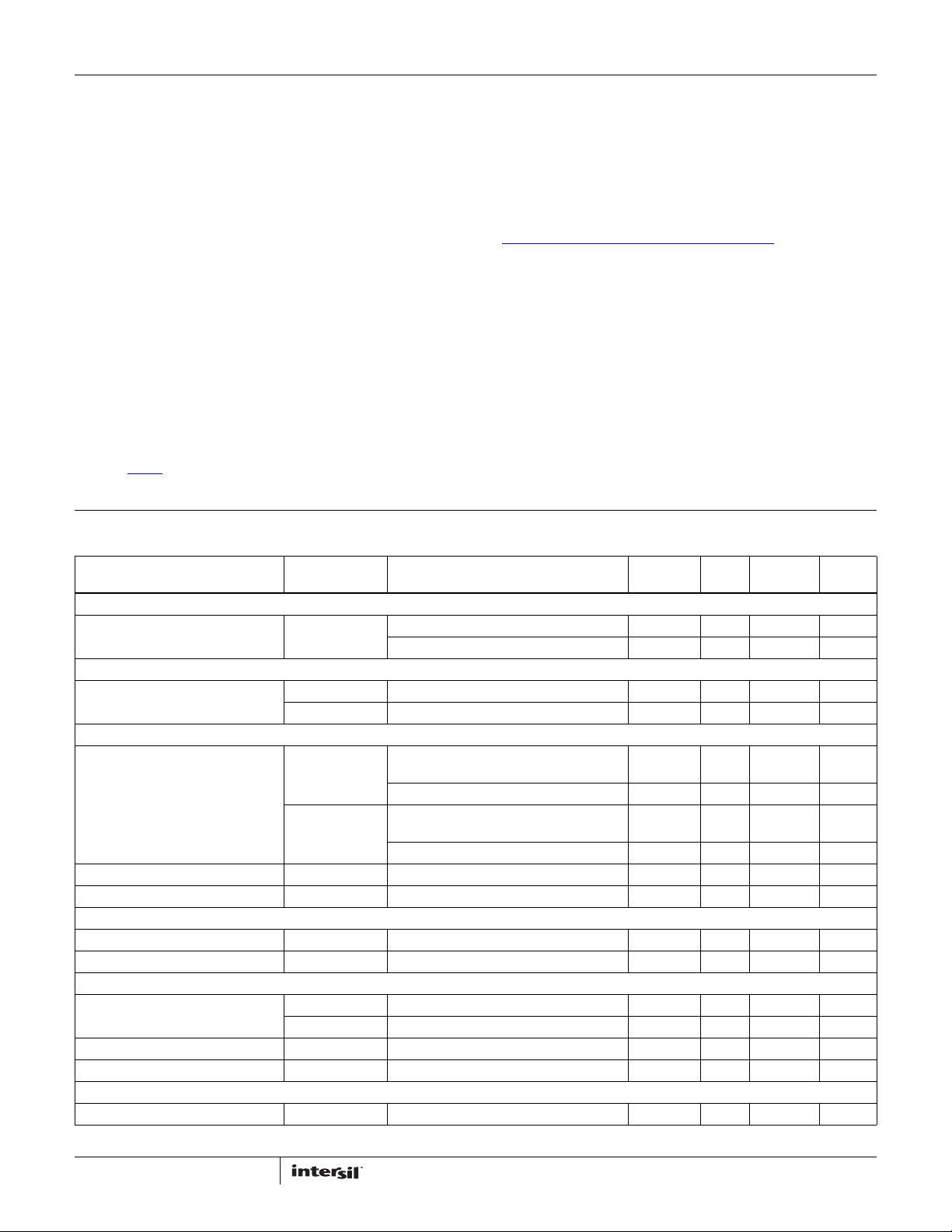

0

10

20

30

40

50

60

70

80

90

100

0 5 10 15 20 25 30 35 40 45 50 55

I

OUT

(A)

EFFICIENCY (%)

V

OUT

CORE = 1.1V

V

IN

= 8V

V

IN

= 12V

0.96

0.98

1.00

1.02

1.04

1.06

1.08

1.10

1.12

0 5 10 15 20 25 30 35 40 45 50 55

I

OUT

(A)

V

OUT

(A)

V

IN

= 8V

V

IN

= 12V

V

OUT

CORE = 1.1V

CPUs Using SVI 2.0

ISL6377

The ISL6377 is fully compliant with AMD Fusion™ SVI 2.0 and

provides a complete solution for microprocessor and graphics

processor core power. The ISL6377 controller supports two

Voltage Regulators (VRs) with three integrated gate drivers and

three optional external drivers for maximum flexibility. The Core

VR can be configured for 4-, 3-, 2-, or 1-phase operation while the

Northbridge VR supports 2- or 1-phase configurations. The two

VRs share a serial control bus to communicate with the AMD CPU

and achieve lower cost and smaller board area compared with

two-chip solutions.

The PWM modulator is based on Intersil’s Robust Ripple

Regulator R3 Technology™. Compared to traditional modulators,

the R3 modulator can automatically change switching frequency

for faster transient settling time during load transients and

improved light load efficiency.

The ISL6377 has several other key features. Both outputs

support DCR current sensing with single NTC thermistor for

DCR temperature compensation or accurate resistor current

sensing. Both outputs utilize remote voltage sense, adjustable

switching frequency, OC protection and power good.

Applications

• AMD Fusion CPU/GPU Core Power

•Desktop Computers

Features

• Supports AMD SVI 2.0 Serial Data Bus Interface

• Dual Output Controller with Integrated Drivers

- Two Dedicated Core Drivers

- One Programmable Driver for Either Core or Northbridge

• Precision Voltage Regulation

- 0.5% System Accuracy Over-Temperature

- 0.5V to 1.55V in 6.25mV Steps

- Enhanced Load Line Accuracy

• Supports Multiple Current Sensing Methods

- Lossless Inductor DCR Current Sensing

- Precision Resistor Current Sensing

• Programmable 1-, 2-, 3- or 4-Phase for the Core Output and

1- or 2-Phase for the Northbridge Output

• Adaptive Body Diode Conduction Time Reduction

• Superior Noise Immunity and Transient Response

• Output Current and Voltage Telemetry

• Differential Remote Voltage Sensing

• High Efficiency Across Entire Load Range

•Programmable Slew Rate

• Programmable VID Offset and Droop on Both Outputs

• Programmable Switching Frequency for Both Outputs

• Excellent Dynamic Current Balance Between Phases

• Protection: OCP/WOC, OVP, PGOOD, and Thermal Monitor

• Small Footprint 48 Ld 6x6 QFN Package

- Pb-Free (RoHS Compliant)

Core Performance

August 6, 2012

FN8336.0

FIGURE 1. EFFICIENCY vs LOAD

1

FIGURE 2. V

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

Intersil (and design) and R3 Technology are trademarks owned by Intersil Corporation or one of its subsidiaries.

1-888-INTERSIL or 1-888-468-3774

All other trademarks mentioned are the property of their respective owners.

| Copyright Intersil Americas Inc. 2012. All Rights Reserved

OUT

vs LOAD

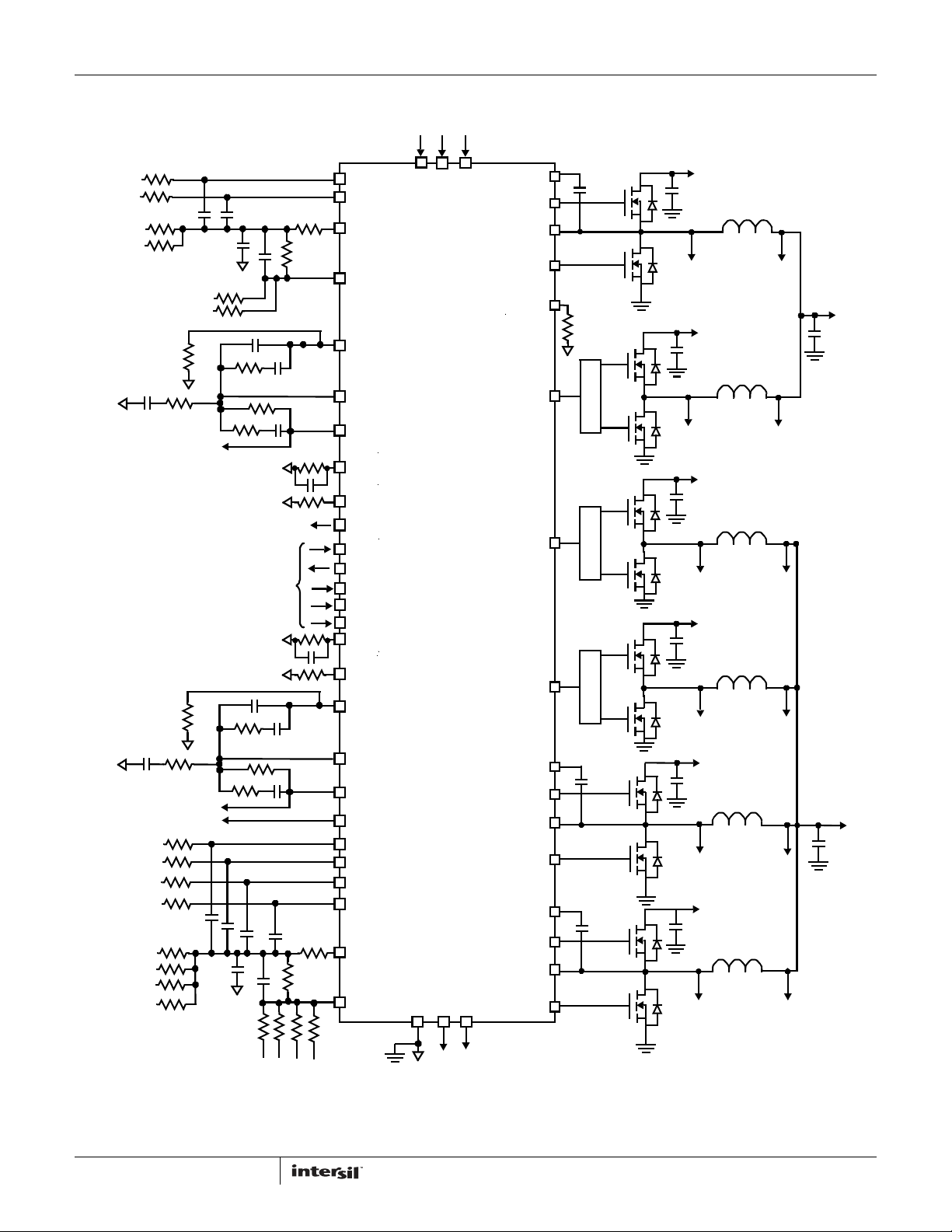

ISL6377

NB_PH1

NB_PH2

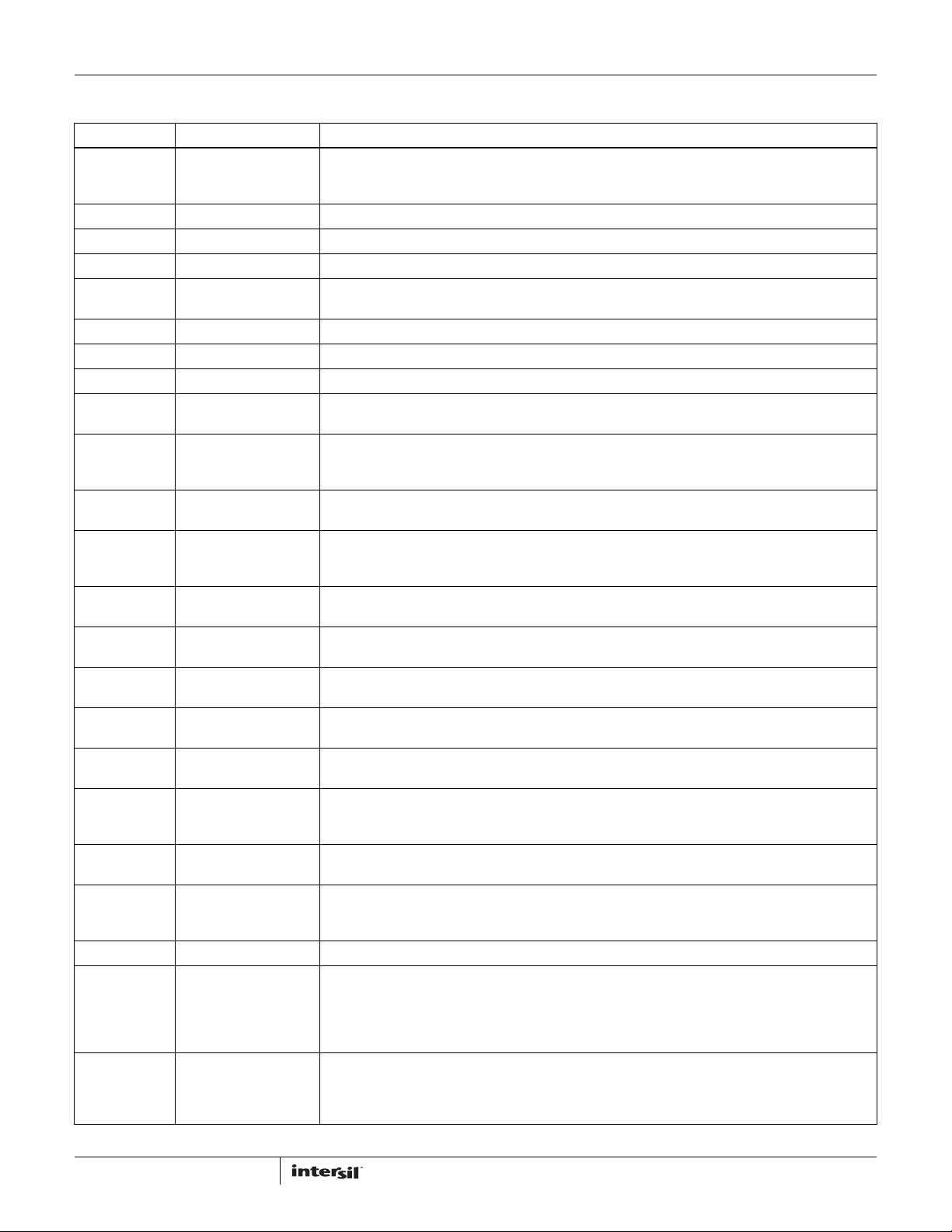

FIGURE 3. TYPICAL APPLICATION CIRCUIT USING INDUCTOR DCR SENSING

BOOTX

UGATEX

PHASEX

LGATEX

BOOT2

UGATE2

PHASE2

LGATE2

BOOT1

UGATE1

PHASE1

LGATE1

PWM_Y

ISL6377

ISUMP

ISUMN

PH1

PH2

PH3

VO1

VO2

VO3

GND PAD

FB_NB

COMP_NB

VSEN_NB

VNB_SENSE

VDDP

PGOOD

ISEN1

ISEN2

ISEN3

ENABLE

PH1

PH2

PH3

VCORE

PH2

ISL6208

VO2

VO1

+12V

VO3

PH1

+12V

+12V

VO1

PH3

PH1

+12V

VNB

VDD

PWM2_NB

ISL6208

VNB1

NB_PH1

VNB2

NB_PH2

ISEN1_NB

ISEN2_NB

ISUMP_NB

ISUMN_NB

NB_PH1

NB_PH2

VNB1

VNB2

NTC_NB

IMON

IMON_NB

PWROK

SVT

SVD

µP

SVC

VDDIO

NTC

VR_HOT_L

THERMAL INDICATOR

FCCM_NB

VCORE_SENSE

FB

COMP

VSEN

RTN

+12V

NTC

NTC

Cn

Cn

Ri

Ri

*OPTIONAL

*

*

*OPTIONAL

*

*

ISEN4

PH4

VO4

PH4

PWM4

ISL6208

+12V

VO4

PH4

PGOOD_NB

Simplified Application Circuit for High Power CPU Core

2

FN8336.0

August 6, 2012

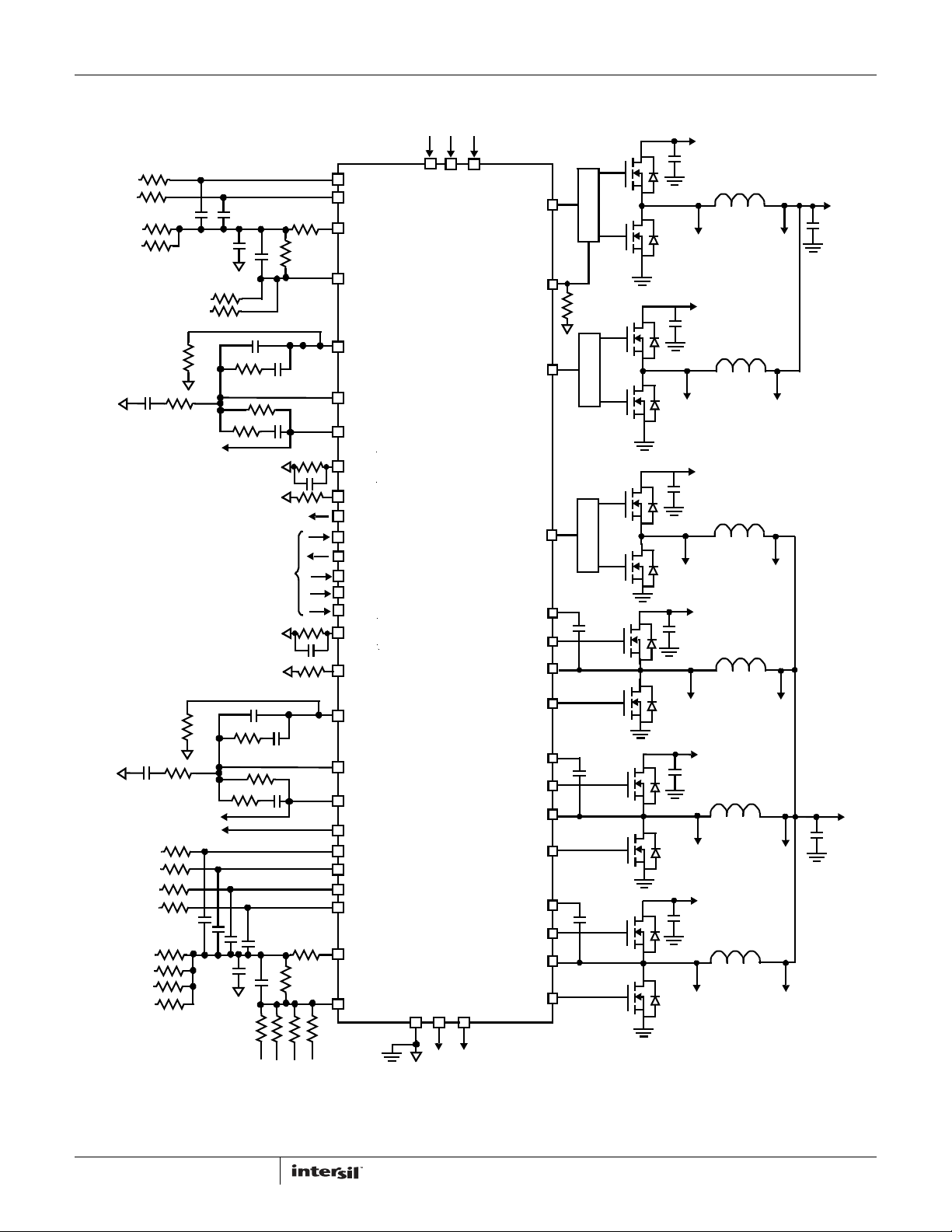

ISL6377

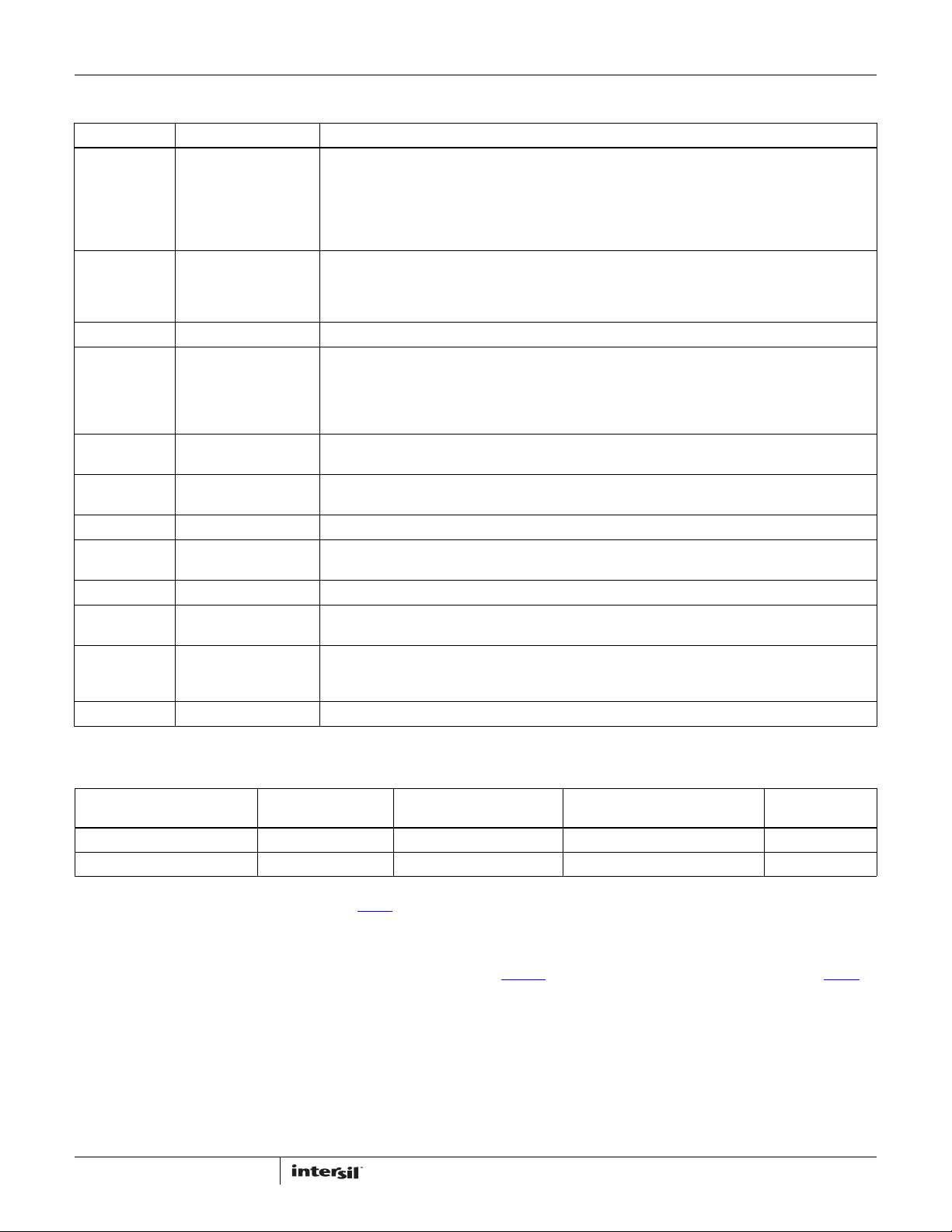

FIGURE 4. TYPICAL APPLICATION CIRCUIT USING INDUCTOR DCR SENSING

BOOTX

UGATEX

PHASEX

LGATEX

BOOT2

UGATE2

PHASE2

LGATE2

BOOT1

UGATE1

PHASE1

LGATE1

ISL6377

GND PAD

VCORE_SENSE

FB_NB

COMP_NB

VSEN_NB

VNB_SENSE

VDDP

PGOOD

ENABLE

VCORE

PH2

ISL6208

VO2

VO1

+12V

VNB1

PH1

+12V

+12V

VO1

NB_PH1

PH1

+12V

VNB

VDD

PWM2_NB

ISL6208

V03

PH3

VNB2

NB_PH2

NTC_NB

IMON

IMON_NB

PWROK

SVT

SVD

µP

SVC

VDDIO

NTC

VR_HOT_L

THERMAL INDICATOR

FB

COMP

VSEN

RTN

FCCM_NB

PWM_Y

+12V

NB_PH1

NB_PH2

ISEN1_NB

ISEN2_NB

ISUMP_NB

ISUMN_NB

NB_PH1

NB_PH2

VNB1

VNB2

ISUMP

ISUMN

PH1

PH2

PH3

VO1

VO2

VO3

ISEN1

ISEN2

ISEN3

PH1

PH2

PH3

NTC

NTC

Cn

Cn

Ri

Ri

*OPTIONAL

*

*

*OPTIONAL

*

*

PWM4

ISL6208

V04

PH4

+12V

ISEN4PH4

VO4

PH4

PGOOD_NB

Simplified Application Circuit with 3 Internal Drivers Used for Core

FN8336.0

August 6, 2012

3

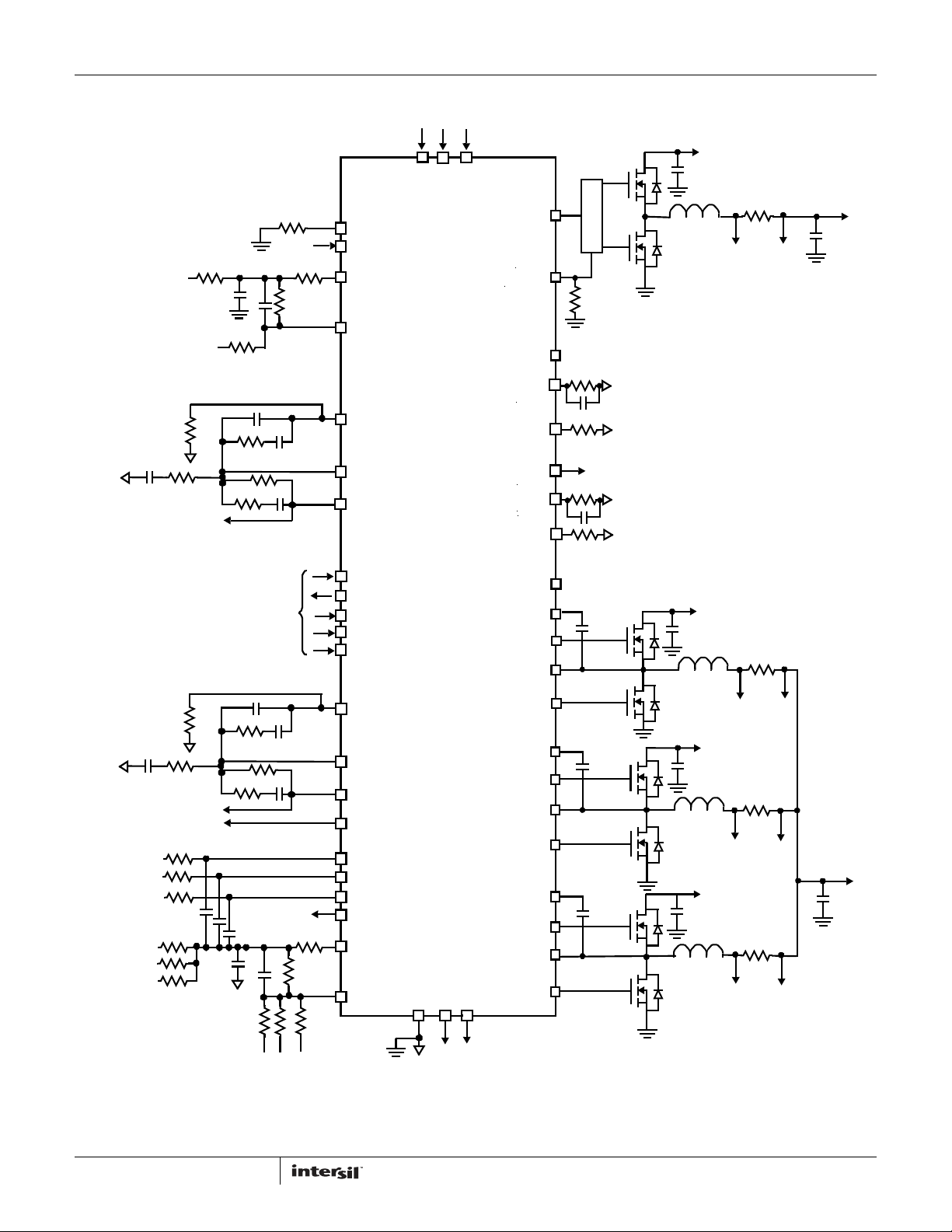

Simplified Application Circuit for Mid-Power CPUs [3+1 Configuration]

FIGURE 5. TYPICAL APPLICATION CIRCUIT USING RESISTOR SENSING

BOOT2

UGATE2

PHASE2

LGATE2

BOOT1

UGATE1

PHASE1

LGATE1

PWM2_NB

ISL6377

ISUMP

ISUMN

VP1

VP2

VN1

VN2

GND PAD

FB_NB

COMP_NB

VSEN_NB

VNB_SENSE

VDDP

PGOOD

ISEN1

ISEN2

ISEN3

ENABLE

VP1

VP2

VCORE

VP2

VN2

+12V

+12V

VNB

VDD

PWM_Y

ISL6208

NBN

NBP

NTC_NB

IMON

IMON_NB

PWROK

SVT

SVD

µP

SVC

VDDIO

NTC

VR_HOT_L

Thermal Indicator

FCCM_NB

VCORE_SENSE

FB

COMP

VSEN

RTN

+12V

+5V

ISEN1_NB

ISEN2_NB

ISUMP_NB

ISUMN_NB

NBP

NBN

10kΩ*

OPEN

NTC

NTC

* Resistor required or ISEN1_NB

will pull HIGH if left open and

disable Channel 1.

VP1

VN1

Cn

Cn

Ri

Ri

*OPTIONAL

*

*

*OPTIONAL

*

*

PWM4

OPEN

ISEN4

+5V

BOOTX

UGATEX

PHASEX

LGATEX

+12V

VP3

VN3

VP3

VN3

VP3

PGOOD_NB

ISL6377

4

FN8336.0

August 6, 2012

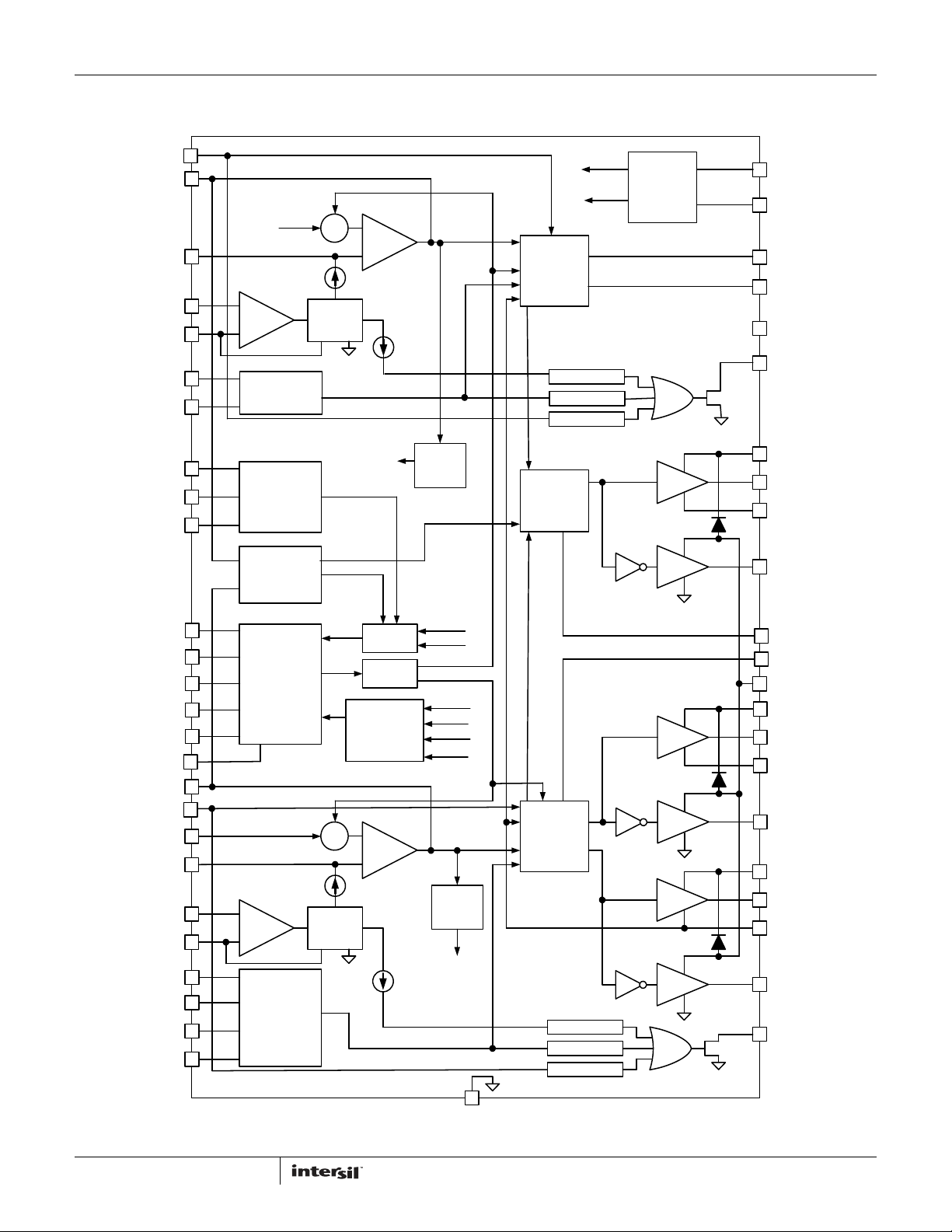

Block Diagram

RTN

E/A

FB

IDROOP

CURRENT

SENSE

ISUMP

ISUMN

COMP

DRIVER

DRIVER

LGATE1

PHASE1

UGATE1

BOOT1

VCCP

OV FAULT

PGOOD

_

+

_

+

+

+

DRIVER

DRIVER

LGATE2

PHASE2

UGATE2

BOOT2

IBAL FAULT

OC FAULT

PWM_Y

ISEN3

ISEN2

ISEN1

CURRENT

BALANCING

DIGITAL

INTERFACE

PWROK

SVC

SVD

DRIVER

DRIVER

LGATEX

PHASEX

UGATEX

BOOTX

OV FAULT

PGOOD_NB

CORE_I

DAC1

NB_I

DAC2

TEMP

MONITOR

NTC_NB

NTC

VR_HOT_L

T_MONITOR

OFFSET

FREQ

SLEWRATE

CONFIG

PROG

ENABLE

TELEMETRY

D/A

A/D IDROOP

IDROOP_NB

RTN

E/A

FB_NB

IDROOP_NB

CURRENT

SENSE

ISUMP_NB

ISUMN_NB

COMP_NB

VR2

MODULATOR

_

+

_

+

+

+

VR1

MODULATOR

VDD

GND

ISEN1_NB

ISEN2_NB

CURRENT

BALANCING

IBAL FAULT

PWM2_NB

SVT

FLOATING

DRIVER &

PWM

CONFIG

LOGIC

OC FAULT

CURRENT

A/D

IMON

IMON_NB

VSEN

VSEN_NB

VDDIO

CORE_I

NB_I

CORE_V

NB_V

NB_V

VOLTAGE

A/D

CORE_V

VOLTAGE

A/D

ISEN4

PWM4

FCCM_NB

ISL6377

Σ

5

Σ

FN8336.0

August 6, 2012

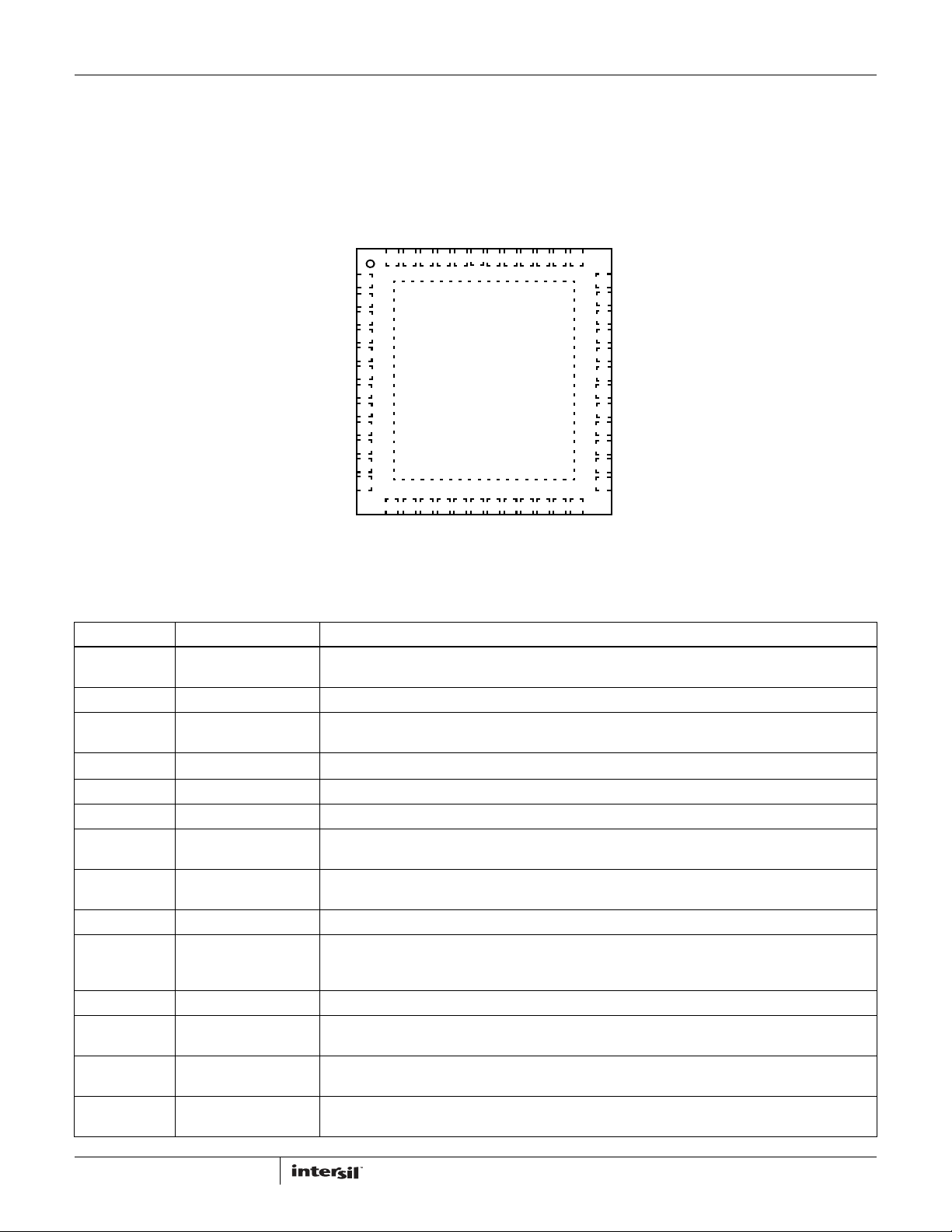

ISL6377

1

48

GND PAD

(BOTTOM)

C

O

M

P

_

N

B

I

S

U

M

P

_

N

B

2

I

S

E

N

1

_

N

B

3

ISEN2_NB

4

IMON_NB

5

6

SVC

7

PWROK

8

SVD

9

VDDIO

10

SVT

11

VR_HOT_L

12

NTC

47

P

G

O

O

D

_

N

B

46

F

C

C

M

_

N

B

45

V

S

E

N

_

N

B

44

P

W

M

2

_

N

B

43

L

G

A

T

E

X

42 41 40

N

T

C

_

N

B

39

P

H

A

S

E

X

38

U

G

A

T

E

X

37

B

O

O

T

X

36

PWM4

35

34

BOOT2

33

UGATE2

32

PHASE2

31

LGATE2

30

VDDP

29

VDD

28

PWM_Y

27

LGATE1

26

PHASE1

25

UGATE1

1

3

I

S

E

N

1

1

4

I

S

U

M

P

1

5

I

S

U

M

N

1

6

V

S

E

N

1

7

I

M

O

N

1

8

F

B

192

0

C

O

M

P

2

1

I

S

E

N

4

2

2

P

G

O

O

D

2

3

R

T

N

37

2

4

I

S

E

N

2

ENABLE

I

S

E

N

3

F

B

_

N

B

I

S

U

M

N

_

N

B

B

O

O

T

1

Pin Configuration

ISL6377

(48 LD QFN)

TOP VIEW

Pin Descriptions

PIN NUMBER SYMBOL DESCRIPTION

1 ISEN2_NB Individual current sensing for Channel 2 of the Northbridge VR. When ISEN2_NB is pulled to +5V, the

controller will disable Channel 2 and the Northbridge VR will run single-phase.

2 NTC_NB Thermistor input to VR_HOT_L circuit to monitor Northbridge VR temperature.

3 IMON_NB Northbridge output current monitor. A current proportional to the Northbridge VR output current is

sourced from this pin.

4SVC

5 VR_HOT_L Thermal indicator signal to AMD CPU. Thermal overload open drain output indicator active LOW.

6 SVD Serial VID data bidirectional signal from the CPU processor master device to the VR.

7 VDDIO VDDIO is the processor memory interface power rail and this pin serves as the reference to the controller

8 SVT Serial VID Telemetry (SVT) data line input to the CPU from the controller IC. Telemetry and VID-on-the-fly

9 ENABLE Enable input. A high level logic on this pin enables both VRs.

10 PWROK System power-good input. When this pin is high, the SVI 2 interface is active and the I

11 NTC Thermistor input to VR_HOT_L circuit to monitor Core VR temperature.

12 ISEN4 ISEN4 is the individual current sensing for Channel 4. When ISEN4 is pulled to +5V, the controller disables

13 ISEN3 ISEN3 is the individual current sensing for Channel 3. When ISEN3 is pulled to +5V, the controller disables

14 ISEN2 Individual current sensing for Channel 2 of the Core VR. When ISEN2 is pulled to +5V, the controller

6

Serial VID clock input from the CPU processor master device.

IC for this processor I/O signal level.

complete signal provided from this pin.

running. While this pin is low, the SVC and SVD input states determine the pre-PWROK metal VID. This

pin must be low prior to the ISL6377 PGOOD output going high per the AMD SVI 2.0 Controller Guidelines.

Channel 4, and the Core VR runs in three-phase mode.

Channel 3, and the Core VR runs in two-phase mode.

disables Channel 2, and the Core VR runs in single-phase mode.

2

C protocol is

August 6, 2012

FN8336.0

ISL6377

Pin Descriptions (Continued)

PIN NUMBER SYMBOL DESCRIPTION

15 ISEN1 Individual current sensing for Channel 1 of the Core VR. If ISEN2 is tied to +5V, this pin cannot be left

open and must be tied to GND with a 10kΩ resistor. If ISEN1 is tied to +5V, the Core portion of the IC is

shut down.

16 ISUMP Non-inverting input of the transconductance amplifier for current monitor and load line of Core output.

17 ISUMN Inverting input of the transconductance amplifier for current monitor and load line of Core output.

18 VSEN Output voltage sense pin for the Core controller. Connect to the +sense pin of the microprocessor die.

19 RTN Output voltage sense return pin for both Core VR and Northbridge VR. Connect to the -sense pin of the

microprocessor die.

20 IMON Core output current monitor. A current proportional to the Core VR output current is sourced from this pin.

21 FB Output voltage feedback to the inverting input of the Core controller error amplifier.

22 COMP Core controller error amplifier output. A resistor from COMP to GND sets the Core VR offset voltage.

23 PGOOD Open-drain output to indicate the Core portion of the IC is ready to supply regulated voltage. Pull up

24 BOOT1 Connect an MLCC capacitor across the BOOT1 and the PHASE1 pins. The boot capacitor is charged,

25 UGATE1 Output of the Phase 1 high-side MOSFET gate driver of the Core VR. Connect the UGATE1 pin to the gate

26 PHASE1 Current return path for the Phase 1 high-side MOSFET gate driver of VR1. Conne ct the PHASE1 pin to the

27 LGATE1 Output of the Phase 1 low-side MOSFET gate driver of the Core VR. Connect the LGATE1 pin to the gate

28 PWM_Y Floating PWM output used for either Channel 3 of the Core VR or Channel 1 of the Northbridge VR

29 VDD 5V bias power. A resistor [2Ω] and a decoupling capacitor should be used from the +5V supply. A high

30 VDDP Input voltage bias for the internal gate drivers. Connect +5V to the VDDP pin. Decouple with at least 1µF

31 LGATE2 Output of the Phase 2 low-side MOSFET gate driver of the Core VR. Connect the LGATE2 pin to the gate

32 PHASE2 Current return path for the Phase 2 high-side MOSFET gate driver of the Core VR. Connect the PHASE2

33 UGATE2 Output of the Phase 2 high-side MOSFET gate driver of the Core VR. Connect the UGATE2 pin to the gate

34 BOOT2 Connect an MLCC capacitor across the BOOT2 and PHASE2 pins. The boot capacitor is charged, through

35 PWM4 PWM output of Channel 4 of the Core VR. Disabled if ISEN4 is tied to +5V.

36 BOOTX Boot connection of the programmable internal driver used for either Channel 3 of the Core VR or

37 UGATEX High-side MOSFET gate driver portion of the programmable internal driver used for either Channel 3 of

externally to VDD or 3.3V through a resistor.

through an internal boot diode connected from the VDDP pin to the BOOT1 pin, each time the PHASE1

pin drops below VDDP minus the voltage dropped across the internal boot diode.

of the Phase 1 high-side MOSFET(s).

node consisting of the high-side MOSFET source, the low-side MOSFET drain, and the output inductor of

Phase 1.

of the Phase 1 low-side MOSFET(s).

depending on the FCCM_NB resistor connected between FCCM_NB and GND.

quality, X7R dielectric MLCC capacitor is recommended.

of capacitance to GND. A high quality, X7R dielectric MLCC capacitor is recommended.

of the Phase 2 low-side MOSFET(s).

pin to the node consisting of the high-side MOSFET source, the low-side MOSFET drain, and the output

inductor of Phase 2.

of the Phase 2 high-side MOSFET(s).

an internal boot diode connected from the VDDP pin to the BOOT2 pin, each time the PHASE2 pin drops

below VDDP minus the voltage dropped across the internal boot diode.

Channel 1 of the Northbridge VR based on the configuration state selected by the FCCM_NB resistor.

Connect an MLCC capacitor across the BOOT1X and the PHASEX pins. The boot capacitor is charged,

through an internal boot diode connected from the VDDP pin to the BOOTX pin, each time the PHASEX

pin drops below VDDP minus the voltage dropped across the internal boot diode.

the Core VR or Channel 1 of the Northbridge VR based on the configuration state selected by the

FCCM_NB resistor. Connect the UGATEX pin to the gate of the high-side MOSFET(s) for either Phase 3 of

the Core VR or Phase 1 of the Northbridge VR based on the configuration state selected.

7

FN8336.0

August 6, 2012

ISL6377

Pin Descriptions (Continued)

PIN NUMBER SYMBOL DESCRIPTION

38 PHASEX Phase connection of the programmable internal driver used for either Channel 3 of the Core VR or

Channel 1 of the Northbridge VR based on the configuration state selected by the FCCM_NB resistor.

Current return path for the high-side MOSFET gate driver of the floating internal driver. Connect the

PHASEX pin to the node consisting of the high-side MOSFET source, the low-side MOSFET drain, and the

output inductor of either Phase 3 of the Core VR or Phase 1 of the Northbridge VR based on the

configuration state selected.

39 LGATEX Low-side MOSFET gate driver portion of floating internal driver used for either Channel 3 of the Core VR

or Channel 1 of the Northbridge VR based on the configuration state selected by the FCCM_NB resistor.

Connect the LGATEX pin to the gate of the low-side MOSFET(s) for either Phase 3 of the Core VR or Phase

1 of the Northbridge VR based on the configuration state selected.

40 PWM2_NB PWM output for Channel 2 of the Northbridge VR. Disabled when ISEN2_NB is tied to +5V.

41 FCCM_NB Diode emulation control signal for Intersil MOSFET Drivers. When FCCM_NB is LOW, diode emulation at

42 PGOOD_NB Open-drain output to indicate the Northbridge portion of the IC is ready to supply regulated voltage.

43 COMP_NB Northbridge VR error amplifier output. A resistor from COMP_NB to GND sets the Northbridge VR offset

44 FB_NB Output voltage feedback to the inverting input of the Northbridge controller error amplifier.

45 VSEN_NB Output voltage sense pin for the Northbridge controller. Connect to the +sense pin of the microprocessor

46 ISUMN_NB Inverting input of the transconductance amplifier for current monitor and load line of the Northbridge VR.

47 ISUMP_NB Non-inverting input of the transconductance amplifier for current monitor and load line of the

48 ISEN1_NB Individual current sensing for Channel 1 of the Northb ridge VR . If ISEN2_NB is tied to +5V, this pin cann ot

GND (Bottom Pad) Signal common of the IC. Unless otherwise stated, signals are referenced to the GND pin.

the driver this pin connects to is allowed. A resistor from FCCM_NB pin to GND configures the PWM_Y

and floating internal gate driver [BOOTX, UGATEX, PHASEX, LGATEX pins] to support Phase 3 of the Core

VR and Phase 1 of the Northbridge VR. The FCCM_NB resistor value also is used to set the slew rate for

the Core VR and Northbridge VR.

Pull-up externally to VDDP or 3.3V through a resistor.

voltage and is used to set the switching frequency for the Core VR and Northbridge VR.

die.

Northbridge VR.

be left open and must be tied to GND with a 10kΩ resistor. If ISEN1_NB is tied to +5V, the Northbridge

portion of the IC is shutdown.

Ordering Information

PART NUMBER

(Notes 1, 2, 3)

ISL6377HRZ ISL6377 HRZ -10 to +100 48 Ld 6x6 QFN L48.6x6B

ISL6377IRZ ISL6377 IRZ -40 to +85 48 Ld 6x6 QFN L48.6x6B

NOTES:

1. Add “-T*” suffix for tape and reel. Please refer to TB347

2. Intersil Pb-free plus anneal products employ special Pb-free material sets; molding compounds/die attach materials and 100% matte tin plate

termination finish, which are RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free products are MSL

classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

3. For Moisture Sensitivity Level (MSL), please see device information page for ISL6377

8

PART

MARKING

TEMP.

RANGE (°C)

for details on reel specifications.

. For more information on MSL please see tech brief TB363.

PACKAGE

(Pb-free)

PKG.

DWG. #

August 6, 2012

FN8336.0

ISL6377

Table of Contents

Absolute Maximum Ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Thermal Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Recommended Operating Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Electrical Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

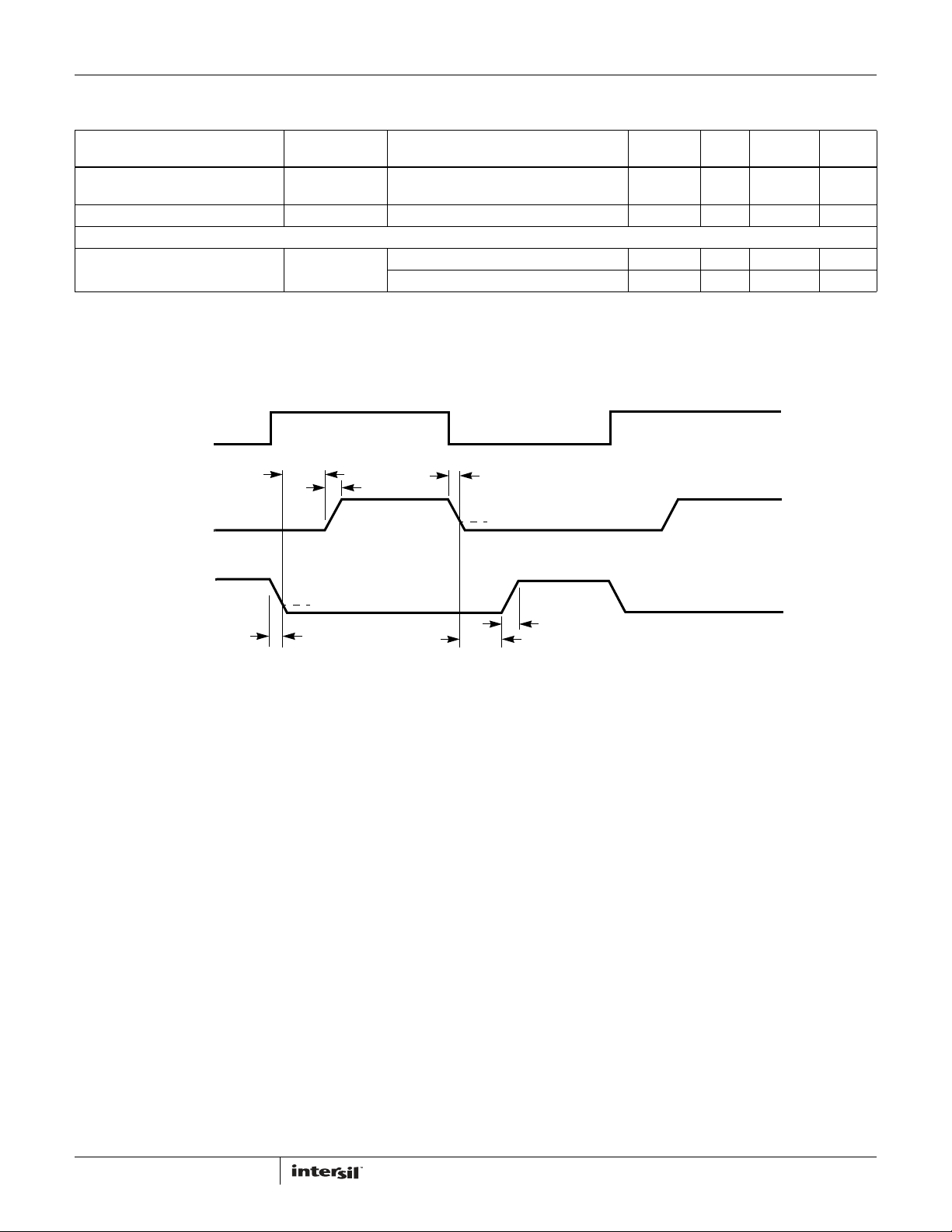

Gate Driver Timing Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Theory of Operation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Multiphase R3™ Modulator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Diode Emulation and Period Stretching . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Channel Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Power-On Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Start-up Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Voltage Regulation and Load Line Implementation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Differential Sensing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Phase Current Balancing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Dynamic Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Adaptive Body Diode Conduction Time Reduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Resistor Configuration Options . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

VR Offset Programming . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Floating DriverX and PWM_Y Configuration. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

VID-on-the-Fly Slew Rate Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

CCM Switching Frequency . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

AMD Serial VID Interface 2.0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Pre-PWROK Metal VID. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

SVI Interface Active . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

VID-on-the-Fly Transition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

SVI Data Communication Protocol . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

SVI Bus Protocol. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Power States . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Dynamic Load Line Slope Trim . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Dynamic Offset Trim . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Telemetry . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Protection Features. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Overcurrent. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Current-Balance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

Undervoltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

Overvoltage. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

Thermal Monitor [NTC, NTC_NB] . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

Fault Recovery . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Interface Pin Protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Key Component Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Inductor DCR Current-Sensing Network . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Resistor Current-Sensing Network . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Overcurrent Protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Load Line Slope . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

Compensator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

Current Balancing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

Thermal Monitor Component Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

Layout Guidelines . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

PCB Layout Considerations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

Products . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

Package Outline Drawing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

9

FN8336.0

August 6, 2012

ISL6377

Absolute Maximum Ratings Thermal Information

Supply Voltage, V

Boot Voltage (BOOT). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -0.3V to +33V

Boot to Phase Voltage (BOOT-PHASE) . . . . . . . . . . . . . . . . -0.3V to +7V(DC)

Phase Voltage (PHASE) . . . . . . . . . . . . . . . . -7V (<20ns Pulse Width, 10µJ)

UGATE Voltage (UGATE) . . . . . . . . . .PHASE - 0.3V (DC) to BOOTPHASE - 5V

All Other Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -0.3V to (VDD + 0.3V)

Open Drain Outputs, PGOOD, PGOOD_NB, VR_HOT_L. . . . . . . -0.3V to +7V

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product

reliability and result in failures not covered by warranty.

NOTES:

4. θ

is measured in free air with the component mounted on a high effective thermal conductivity test board with “direct attach” features. See Tech

JA

Brief TB379

5. For θ

DD, VDDP

.

, the “case temp” location is the center of the exposed metal pad on the package underside.

JC

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . -0.3V to +7V

-0.3V to +9V (<10ns)

(<20ns Pulse Width, 10µJ) to BOOT LGATE Voltage

-2.5V (<20ns Pulse Width, 5µJ) to VDD + 0.3V

Thermal Resistance (Typical) θ

48 Ld QFN Package (Notes 4, 5) . . . . . . . . 29 3.5

Maximum Junction Temperature . . . . . . . . . . . . . . . . . . . . . . . . . . . .+150°C

Maximum Storage Temperature Range . . . . . . . . . . . . . .-65°C to +150°C

Maximum Junction Temperature (Plastic Package) . . . . . . . . . . . .+150°C

Storage Temperature Range. . . . . . . . . . . . . . . . . . . . . . . .-65°C to +150°C

Pb-Free Reflow Profile . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . see link below

http://www.intersil.com/pbfree/Pb-FreeReflow.asp

(°C/W) θJC (°C/W)

JA

Recommended Operating Conditions

Supply Voltage, VDD. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . +5V ±5%

Input Supply Voltage, V

Ambient Temperature HRZ . . . . . . . . . . . . . . . . . . . .-10°C to +100°C

Junction Temperature . . . . . . . . . . . . . . . . . . . . . . . . . . . . .-10°C to +125°C

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10V to 12.6V

IN

IRZ . . . . . . . . . . . . . . . . . . . . . . -40°C to +85°C

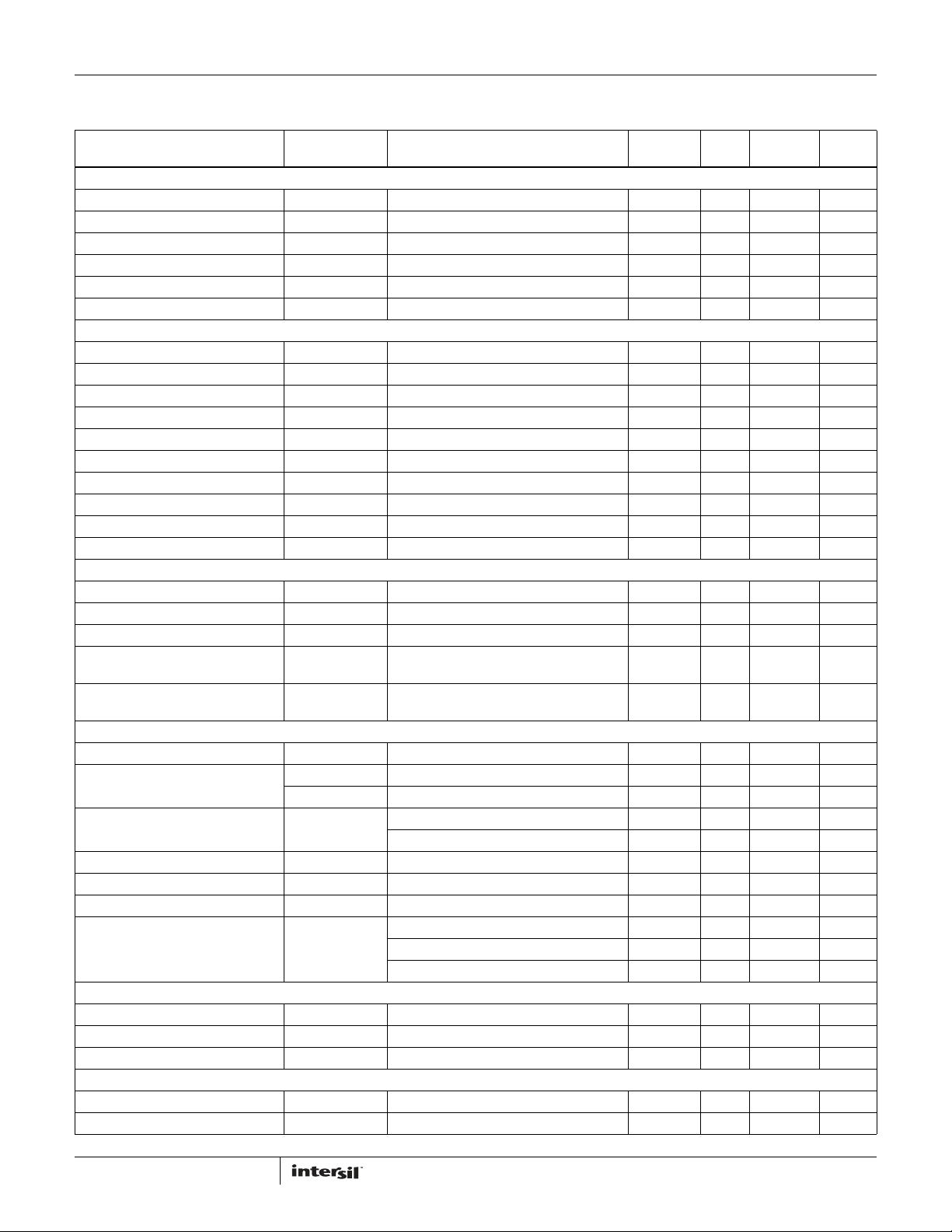

Electrical Specifications Operating Conditions: V

otherwise noted. Boldface limits apply over the operating temperature range, -40°C to +100°C.

PARAMETER SYMBOL TEST CONDITIONS

INPUT POWER SUPPLY

+5V Supply Current I

POWER-ON-RESET THRESHOLDS

VDD POR Threshold VDD_POR

SYSTEM AND REFERENCES

System Accuracy HRZ

Maximum Output Voltage V

Minimum Output Voltage V

CHANNEL FREQUENCY

Nominal Channel Frequency f

Adjustment Range 300 450 kHz

AMPLIFIERS

Current-Sense Amplifier Input Offset HRZ I

Error Amp DC Gain A

Error Amp Gain-Bandwidth Product GBW C

ISEN

Input Bias Current 20 nA

VDD

VDD_POR

%Error (V

IRZ

%Error (V

OUT(max)

OUT(min)

SW(nom)

IRZ I

v0

ENABLE = 1V 8 11 mA

ENABLE = 0V 1 µA

VDD rising 4.35 4.5 V

r

VDD falling 4.00 4.15 V

f

No load; closed loop, active mode range,

VID = 0.75V to 1.55V -0.5 +0.5 %

OUT)

VID = 0.25V to 0.74375V -10 +10 mV

No load; closed loop, active mode range,

)

VID = 0.75V to 1.55V -0.8 +0.8 %

OUT

VID = 0.25V to 0.74375V -12 +12 mV

VID = [00000000] 1.55 V

VID = [11111111] 0.0 V

= 5V, TA = -10°C to +100°C (HRZ), TA = -40°C to +85°C (IRZ), fSW = 300kHz, unless

DD

MIN

(Note 6) TYP

280 300 320 kHz

= 0A -0.15 +0.15 mV

FB

= 0A -0.20 +0.20 mV

FB

119 dB

= 20pF 17 MHz

L

MAX

(Note 6) UNITS

10

FN8336.0

August 6, 2012

ISL6377

Electrical Specifications Operating Conditions: V

= 5V, TA = -10°C to +100°C (HRZ), TA = -40°C to +85°C (IRZ), fSW = 300kHz, unless

DD

otherwise noted. Boldface limits apply over the operating temperature range, -40°C to +100°C. (Continued)

PARAMETER SYMBOL TEST CONDITIONS

MIN

(Note 6) TYP

MAX

(Note 6) UNITS

POWER-GOOD (PGOOD & PGOOD_NB) AND PROTECTION MONITORS

I

PGOOD Low Voltage V

PGOOD Leakage Current I

OL

OH

= 4mA 0.4 V

PGOOD

PGOOD = 3.3V -1 1 µA

PWROK High Threshold 750 mV

VR_HOT_L Pull-down 11 Ω

PWROK Leakage Current 1 µA

VR_HOT_L Leakage Current 1 µA

GATE DRIVER

UGATE Pull-Up Resistance R

UGATE Source Current I

UGATE Sink Resistance R

UGATE Sink Current I

LGATE Pull-Up Resistance R

LGATE Source Current I

LGATE Sink Resistance R

LGATE Sink Current I

UGATE to LGATE De ad ti me t

LGATE to UGATE De ad ti me t

UGPU

UGSRC

UGPD

UGSNK

LGPU

LGSRC

LGPD

LGSNK

UGFLGR

LGFUGR

200mA Source Current 1.0 1.5 Ω

UGATE - PHASE = 2.5V 2.0 A

250mA Sink Current 1.0 1.5 Ω

UGATE - PHASE = 2.5V 2.0 A

250mA Source Current 1.0 1.5 Ω

LGATE - VSSP = 2.5V 2.0 A

250mA Sink Current 0.5 0.9 Ω

LGATE - VSSP = 2.5V 4.0 A

UGATE falling to LGATE rising, no load 23 ns

LGATE falling to UGATE rising, no load 28 ns

PROTECTION

Overvoltage Threshold OV

Undervoltage Threshold OV

H

H

VSEN rising above setpoint for >1µs 275 325 375 mV

VSEN falls below setpoint for >1µs 275 325 375 mV

Current Imbalance Threshold One ISEN above another ISEN for >1.2ms 9 mV

Way Overcurrent Trip Threshold

[IMONx Current Based Detection]

Overcurrent Trip Threshold

[IMONx Voltage Based Detection]

IMONx

V

IMONx_OCP

WOC

All states, I

All states, I

I

= 11.25µA, R

IMONx

DROOP

DROOP

= 60µA, R

= 45µA,

= 135kΩ

IMON

= 135kΩ 15 µA

IMON

1.485 1.51 1.535 V

LOGIC THRESHOLDS

ENABLE Input Low V

ENABLE Input High V

ENABLE Leakage Current I

ENABLE

IL

IH

V

IH

HRZ 1.6 V

IRZ 1.65 V

ENABLE = 0V -1 01µA

1 V

ENABLE = 1V 18 35 µA

SVT Impedance 50 Ω

SVC, SVD Input Low V

SVC, SVD Input High V

IL

IH

% of VDDIO 30 %

% of VDDIO 70 %

SVC, SVD Leakage ENABLE = 0V, SVC, SVD = 0V and 1V -1 1 µA

ENABLE = 1V, SVC, SVD = 1V -5 1 µA

ENABLE = 1V, SVC, SVD = 0V -35 -20 -5 µA

PWM

PWM Output Low V

PWM Output High V

0L

0H

Sinking 5mA 1.0 V

Sourcing 5mA 3.5 V

PWM Tri-State Leakage PWM = 2.5V 0.5 µA

THERMAL MONITOR

NTC Source Current NTC = 0.6V 27 30 33 µA

NTC Thermal Warning Voltage 600 640 680 mV

11

FN8336.0

August 6, 2012

ISL6377

PWM

UGATE

LGATE

1V

1V

t

UGFLGR

t

RL

t

FU

t

RU

t

FL

t

LGFUGR

Electrical Specifications Operating Conditions: V

= 5V, TA = -10°C to +100°C (HRZ), TA = -40°C to +85°C (IRZ), fSW = 300kHz, unless

DD

otherwise noted. Boldface limits apply over the operating temperature range, -40°C to +100°C. (Continued)

PARAMETER SYMBOL TEST CONDITIONS

NTC Thermal Warning Voltage

MIN

(Note 6) TYP

20 mV

MAX

(Note 6) UNITS

Hysteresis

NTC Thermal Shutdown Voltage 530 580 630 mV

SLEW RATE

VID-on-the-Fly Slew Rate Maximum Programmed 16 20 24 mV/µs

Minimum Programmed 8 10 12 mV/µs

NOTE:

6. Compliance to datasheet limits is assured by one or more methods: production test, characterization and/or design.

Gate Driver Timing Diagram

12

FN8336.0

August 6, 2012

Loading...

Loading...