®

ISL54003, ISL54005, ISL54006

Data Sheet June 27, 2007

Integrated Audio Amplifier Systems

The Intersil ISL54003, ISL54005, ISL54006 family of devices

are integrated audio power amplifier systems that combine a

mono BTL amplifier and stereo headphone a mp lifiers i n a

single device. The devices are designed to operate from a

single +2.7V to +5V power supply. Targeted applications

include handheld equipment such as cell-phones, MP3

players, and games/toys.

These parts contain one class AB BTL type p ower amplifier

for driving an 8Ω mono speaker and two class AB headphone

amplifiers for driving 16Ω or 32Ω headphone speakers.

The BTL when using a 5V supply is capable of delivering

800mW (typ) with 0.4% THD+N and 941mW (typ) with 1%

THD+N of continuous average power into an 8Ω BTL speaker

load.

Each headphone amplifier when using a 5V supply is capable

of delivering 50mW (typ) with 0.3% THD+N and 94mW (typ)

with 1% THD+N of continuous average power into a 32Ω

headphone speaker .

When in Mono Mode these devices automatically mix the

active left and right audio inputs and send the combi ned signal

to the BTL driver. In Head phone Mode the active right channel

input is sent to the right headphone speaker and the active left

channel is sent to the left headphone speaker.

The ISL54005 and ISL54006 feature a 2:1 stereo input

multiplexer front-end. This allows selection between two

stereo sources. In addition the ISL54006 can mix the four

inputs to the BTL driver or the two pairs of inputs to the

headphone drivers.

These parts feature headphone sense circuitry that detects

when a headphone jack has been inserted and automatically

switches the active audio inputs from the mono BTL output

driver to the headphone drivers. These parts also feature a

logic control pin that can override the headphone sense

input circuitry.

All devices in this family feature low power shutdown,

thermal overload protection and click/pop suppression. The

click and pop circuitry eliminates audible transients during

audio source changes and transitioning in and out of

shutdown.

FN6514.1

Features

• Pb-Free Plus Anneal (RoHS Compliant)

• Class AB 94mW Headphone Amplifiers and 941mW Mono

BTL Speaker Ampli fie r

• THD+N at 1kHz, 800mW into 8Ω BTL. . . . . . . . . . . . . . 0.4%

• THD+N at 1kHz, 50mW into 32Ω Headphone . . . . . . . 0.3%

• Single Supply Operation. . . . . . . . . . . . . . . . . +2.7V to +5.5V

• Headphone Sense Input

• Low Power Shutdown

• Thermal Shutdown Protection

• “Click and Pop” Suppression Circuitry

• 2:1 Stereo Input Mux (ISL54005, ISL54006)

• Mixing of Two Stereo Inputs (ISL54006)

• TTL Logic-Compatible

• Available in 20 Ld 4x4 Thin QFN

Applications

• Battery powered, Handheld, and Portable Equipment

- Cellular/mobile Phones

- PDA’s, MP3 Players, DVD Players, Cameras

- Laptops, Notebooks, Palmtops

- Handheld Games and Toys

• Desktop Computers

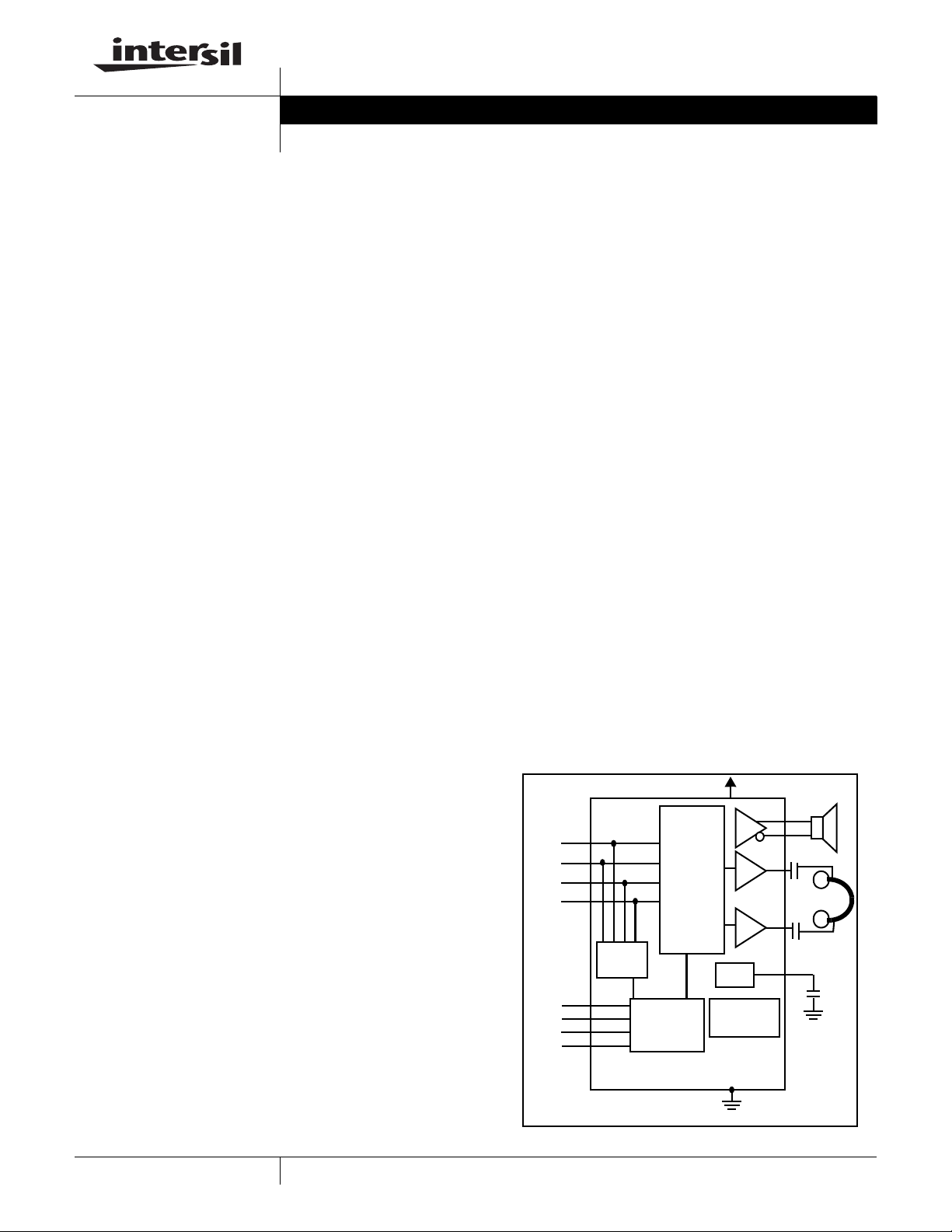

Simplified Block Diagram

V

DD

R1

L1

R2

L2

CLICK

SD

INS

MIX

HO

AND

POP

ROUTER/

MIXER

LOGIC

CONTROL

BIAS

THERMAL

SHUTDOWN

ISL54006

1

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 1-888-468-3774

| Intersil (and design) is a registered trademark of Intersil Americas Inc.

All other trademarks mentioned are the property of their respective owners.

Copyright Intersil Americas Inc. 2007. All Rights Reserved

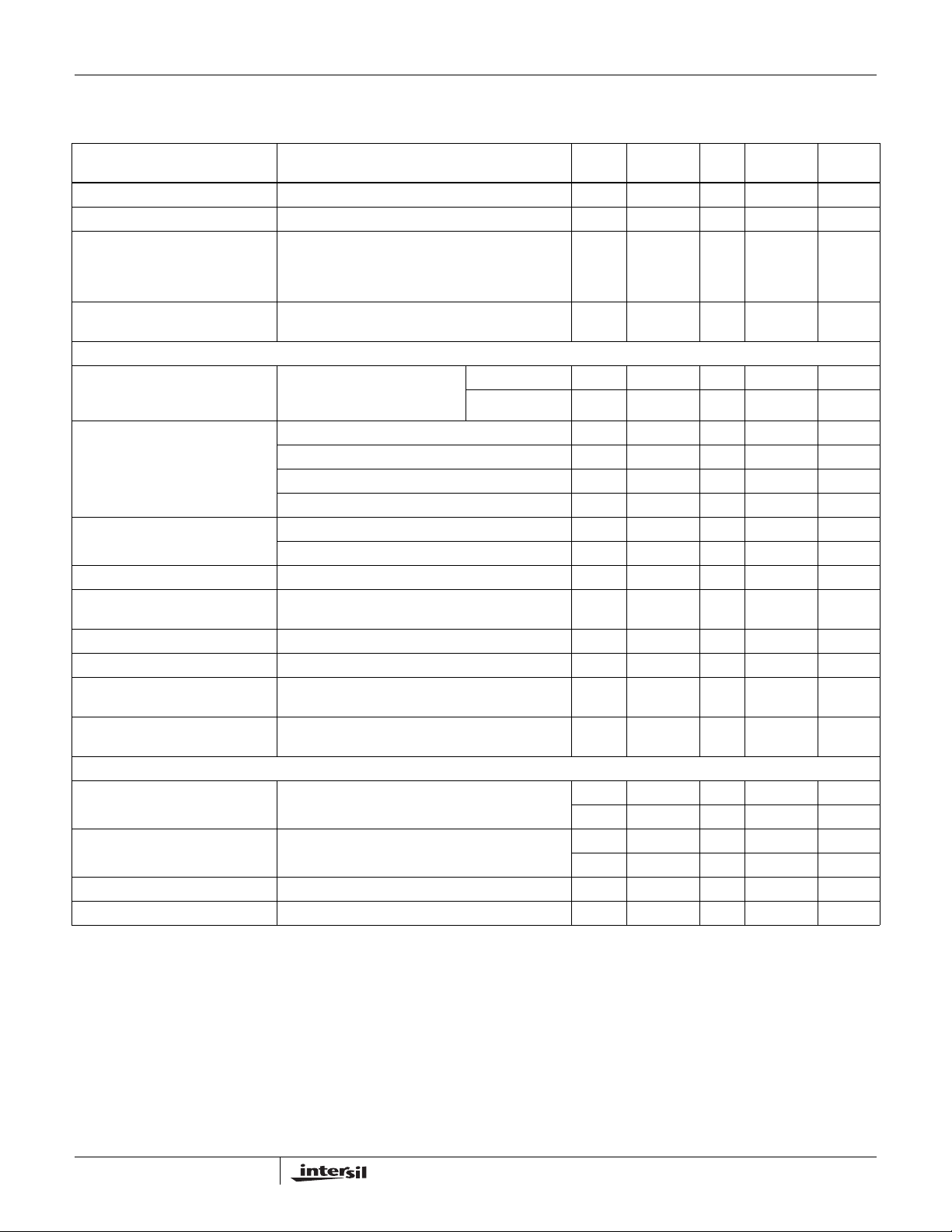

ISL54003, ISL54005, ISL54006

Pinouts

SPK-

SPK+

V

DD

GND

HpR

SPK-

SPK+

V

DD

GND

HpR

SPK-

SPK+

V

DD

ISL54003

(20 LD 4X4 TQFN)

TOP VIEW

GND

20 19 18 17 16

1

2

3

4

5

678910

DD

V

NC

HpL

NC

HD

ISL54005

(20 LD 4X4 TQFN)

TOP VIEW

2R

GND

20 19 18 17 16

1

2

3

4

5

678910

DD

V

INS

IN

HD

HpL

ISL54006

(20 LD 4X4 TQFN)

TOP VIEW

2R

GND

20 19 18 17 16

1

2

3

INS

IN

R

IN

GND

1R

IN

GND

1R

IN

NC

REF

NC

REF

MIX

Pin Descriptions

PIN

NAME FUNCTIONISL54003 ISL54005 ISL54006

3, 6, 12 3, 6, 12 3, 6, 12 V

4, 9, 20 4, 9, 20 4, 9, 20 GND Ground Connection

HO

15

SD

14

NC

13

11 11 11 IN

-1313IN

17 17 17 IN

V

12

DD

IN

11

L

-1919IN

5 5 5 HpR Headphone Right

7 7 7 HpL Headphone Left

2 2 2 SPK+ Positive Speaker

1 1 1 SPK- Negative Speaker

14 14 14 SD Shutdown, High to

HO

15

SD

14

IN

13

2L

V

12

DD

IN

11

1L

-8 8 8 HD Headphone

15 15 15 HO Headphone Override,

- 18 18 INS Input Select

- - 16 MIX Mixer, High to mix

HO

15

SD

14

IN

13

2L

10 10 10 REF Common-mode Bias

System Power Supply

DD

Left Channel Audio

1L

Input 1

Left Channel Audio

2L

Input 2

Right Channel Audio

1R

Input 1

Right Channel Audio

2R

Input 2

Ouput

Ouput

Output

Output

disable amplifiers,

Low for normal

operation.

Detection, Internally

pulled up to V

in Mono Mode, High in

Headphone Mode if

HO = Low

High in Mono Mode,

Low in Headphone

Mode if HD = High

Right and Left Audio

Inputs, Low to pass

Audio Inputs without

mixing

Voltage, Bypass with

a 1µF capacitor to

GND.

DD,

Low

GND

HpR

4

5

678910

DD

V

HD

HpL

2

V

12

DD

IN

11

1L

REF

GND

FN6514.1

June 27, 2007

ISL54003, ISL54005, ISL54006

Ordering Information

TEMP.

PART

NUMBER

PART

MARKING

RANGE

(°C) PACKAGE

ISL54003IR* 54 03IR -40 to +85 20 Ld 4x4 TQFN L20.4x4A

ISL54003IRTZ*

(Note)

54 03IRTZ -40 to +85 20 Ld 4x4 TQFN

Tape and Reel

(Pb-free)

ISL54005IR* 540 05IR -40 to +85 20 Ld 4x4 TQFN L20.4x4A

ISL54005IRTZ*

(Note)

540 05IRTZ -40 to +85 20 Ld 4x4 TQFN

Tape and Reel

(Pb-free)

ISL54006IR* 540 06IR -40 to +85 20 Ld 4x4 TQFN L20.4x4A

ISL54006IRTZ*

(Note)

540 06IRTZ -40 to +85 20 Ld 4x4 TQFN

Tape and Reel

(Pb-free)

*Add “-T” suffix for tape and reel.

NOTE: Intersil Pb-free plus anneal products employ special Pb-free

material sets; molding compounds/die attach materials and 100% matte

tin plate termination finish, which are RoHS compliant and com patible

with both SnPb and Pb-free soldering operations. Intersil Pb-free

products are MSL classified at Pb-free peak reflow temperatures that

meet or exceed the Pb-free requirements of IPC/JEDEC J STD-0 20.

PKG.

DWG. #

L20.4x4A

L20.4x4A

L20.4x4A

ISL54003 Truth Table

SD HD HO SPK+/SPK- HpR HpL

1 X X Disabled Disabled Disabled

00X IN

010 - IN

011 INR + IN

R

+ IN

L

L

--

R

IN

--

ISL54005 Truth Table

SD INS HD HO SPK+/SPK- HpR HpL

1 X X X Disabled Disabled Disabled

000XIN

0010 - IN

0011IN1R + IN

010XIN

0110 - IN

0111IN2R + IN

1R

2R

+ IN

+ IN

1L

1L

2L

2L

--

1R

IN

--

--

2R

IN

--

ISL54006 Truth Table

SD MIX INS HD HO SPK+/SPK- HpR HpL

1 X X X X Disabled Disabled Disabled

0000XIN

00010 - IN1RIN

00011IN1R + IN

0010XIN

00110 - IN2RIN

00111IN2R + IN

01X0XIN

01X10 - IN

01X11IN1R + IN2R +

1R

2R

+ IN2R +

1R

IN

1L

IN

1L

+ IN

+ IN

+ IN

+ IN

1L

1L

2L

2L

--

--

--

--

--

2L

+

1R

IN

IN1L +

2R

--

2L

L

1L

2L

1L

2L

IN

2L

3

FN6514.1

June 27, 2007

ISL54003, ISL54005, ISL54006

Absolute Maximum Ratings Thermal Information

VDD to GND . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -0.3 to +6.0V

Input Voltages

In_R, In_L, SD, INS, MIX, H_. . . . . . . . . . . . -0.3 to (VDD + 0.3V)

Output Voltages

SPK+, SPK-, Hp_. . . . . . . . . . . . . . . . . . . . . -0.3 to (VDD + 0.3V)

Continuous Current (VDD, SPK_, Hp_, GND). . . . . . . . . . . . 750mA

ESD Rating:

HBM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .>2kV

MM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .>200V

CDM. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .>1kV

Operating Conditions

Temperature Range. . . . . . . . . . . . . . . . . . . . . . . . . .-40°C to +85°C

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and

result in failures not covered by warranty.

NOTE:

is measured in free air with the component mounted on a high effective thermal conductivity test board with “direct attach” features. θ

1. θ

JA

“case temp” is measured at the center of the exposed metal pad on the package underside. See Tech Brief TB379.

2. For θ

, the “case temp” location is the center of the exposed metal pad on the package underside.

JC

Thermal Resistance (Typical, Notes 1, 2) θ

(°C/W) θJC (°C/W)

JA

20 Ld 4x4 TQFN Package . . . . . . . . . . 45 6.5

Maximum Junction Temperature. . . . . . . . . . . . . . . . . . . . . . . . . +150°C

Maximum Stor age Temperature Range. . . . . . . . . . . -65°C to +150°C

Pb-free reflow profile . . . . . . . . . . . . . . . . . . . . . . . . . .see link below

http://www.intersil.com/pbfree/Pb-FreeReflow.asp

the

JC,

Electrical Specifications - 5V Supply T est Conditions: V

C

= 1µF, RL is terminated between SPK+ and SPK- for BTL driver and between Hp_ and

REF

= +5V , GND = 0V, V

DD

= 2.4V , V

INH

= 0.8V , SD = MIX = INS = HD = V

INL

GND for SE drivers, Unless Otherwise Specified (Note 3).

PARAMETER TEST CONDITIONS

TEMP

(°C)

MIN

(Notes 4, 5) TYP

MAX

(Notes 4, 5) UNITS

GENERAL

Power Supply Range, V

DD

Quiescent Supply Current, I

Shutdown Supply Current, I

Input Resistance, R

Thermal Shutdown, T

IN

SD

DD

SD

HO = V

MIX = V

(SE), Inputs AC coupled to ground (0.1µF)

HO = V

MIX = V

INL

INL

INL

INL

or V

or V

or V

or V

, HD = V

INH

, RL = 8Ω (BTL) and RL = 32Ω

INH

, HD = V

INH

, RL = None, Inputs AC coupled

INH

, INS = V

INL

, INS = V

INL

INL

INL

to ground (0.13µF)

SD = V

INS = V

(BTL) and R

ground (0.1µF)

INS = 0V or V

INS = MIX = 0V or V

, HO = V

INH

or V

INL

= 32Ω (SE), Inputs AC coupled to

L

DD

INL

, MIX = V

INH

DD

or V

INH

INL

, HD = V

or V

INL

INH

or V

INH

or V

INH

,

, RL = 8Ω

Full 2.7 - 5.5 V

25 - 4.7 50 mA

,

Full - 10 - mA

25 - 4.6 12 mA

,

Full - 5.5 - mA

25 - 28 50 µA

Full - 31 - µA

25 - 100 - kΩ

25 - 150 - °C

Thermal Shutdown Hysteresis 25 - 10 - °C

SD to Full Operation, t

SD(ON)

BTL AMPLIFIER DRIVER, HD = V

Output Offset Voltage, V

OS

Power Supply Rejection Ratio,

PSRR

Output Power, P

OUT

Total Harmonic Distortion + Noise,

THD + N

Max Output Volt a ge S wing, V

OUT

INS = 0V or 5V, MIX = 0V or 5V Full - 1 - ms

HO = V

INH,

Measured between SPK+ and SPK-, Inputs AC

coupled to ground (0.1µF)

V

RIPPLE

V

, RL = 8Ω, Ιnputs AC

INL

coupled to ground (0.1µF)

UNLESS OTHERWISE SPECIFIED

INH,

= 200mV

P-P

, HD =

F

RIPPLE

F

RIPPLE

25 -150 45 150 mV

Full - 49 - mV

= 217Hz 25 - 49 - dB

= 1kHz 25 - 47 - dB

RL = 8Ω, THD+N = 1%, f = 1kHz 25 - 941 - mW

= 8Ω, THD+N = 10%, f = 1kHz 25 - 1.23 - W

R

L

= 8Ω, P

R

L

R

= 8Ω, P

L

RL = 8Ω, V

= 800mW, f = 1kHz 25 - 0.4 - %

OUT

= 800mW, f = 20Hz to 20kHz 25 - 0.7 - %

OUT

= 5V

SIGNAL

, f = 1kHz 25 7.2 7.7 - V

P-P

P-P

INL

,

4

FN6514.1

June 27, 2007

ISL54003, ISL54005, ISL54006

Electrical Specifications - 5V Supply T est Conditions: V

C

= 1µF, RL is terminated between SPK+ and SPK- for BTL driver and between Hp_ and

REF

GND for SE drivers, Unless Otherwise Specified (Note 3). (Continued)

PARAMETER TEST CONDITIONS

Signal to Noise Ratio, SNR RL = 8Ω, P

Output Noise, N

Crosstalk

R

to LCH, LCH to R

CH

OUT

CH

A - Weight filter, BW = 22Hz to 22kHz 25 - 140 - µV

RL = 8Ω, P

from the input of active amplifier to the output of an

adjacent amplifier with its input AC coupled to

ground.

Off-Isolation SD = V

coupled from input to output of a disabled amplifier.

SINGLE ENDED AMPLIFIER DRIVERS, HD = V

Power Supply Rejection Ratio, PSRR V

Output Power, P

OUT

Total Harmonic Distortion + Noise,

THD + N

Max Output Volt a ge S wing, V

OUT

Cross - Talk

R

to LCH, LCH to R

CH

CH

RIPPLE

R

= 32Ω, Input AC coupled to

L

ground (0.1µF)

RL = 16Ω, THD+N = 1%, f = 1kHz 25 - 170 - mW

= 32Ω, THD+N = 1%, f = 1kHz 25 - 94 - mW

R

L

R

= 16Ω, THD+N = 10%, f = 1kHz 25 - 215 - mW

L

R

= 32Ω, THD+N = 10%, f= 1kHz 25 - 116 - mW

L

= 32Ω, P

R

L

R

= 32Ω, P

L

RL = 32Ω, V

RL = 32Ω, P

Off-Isolation SD = V

Signal to Noise Ratio, SNR R

Channel Gain Matching

to L

R

CH

CH

Channel Phase Matching

R

to L

CH

CH

= 32Ω, POUT = 50mW, f = 1kHz 25 - 85 - dB

L

RL = 32Ω, VINxR = VINxL = 1.3V

same source)

RL = 32Ω, VINxR = VINxL = 1.3V

same source)

LOGIC INPUT

Input Leakage Current, I

I

, IHD, I

MIX

HO

Input Leakage Current, I

I

, IHD, I

MIX

V

V

INH

INL

HO

SD

SD

, I

,

VDD = 5V, SD = 0V, INS = 0V, MIX = 0V, HD = 0V,

INS

HO = 0V

, I

,

VDD = 5V, SD = VDD, INS = VDD, MIX = VDD,

INS

HD = V

= 900mW, f = 1kHz 25 - 85 - dB

OUT

= 800mW, f = 1kHz, Signal coupled

OUT

DD, POUT

DD, RL

DD

= 800mW, f = 10kHz, Signal

HO = V

INH,

= 200mV

P-P

= 50mW, f = 1kHz 25 - 0.3 - %

OUT

= 50mW, f = 20Hz to 20kHz 25 - 0.4 - %

OUT

= 5V

SIGNAL

= 15mW, f = 1kHz 25 - 75 - dB

OUT

= 32Ω, P

UNLESS OTHERWISE SPECIFIED

INL,

, HD = 0V,

, f = 1kHz 25 3.6 4.7 - V

P-P

= 15mW, f = 10kHz 25 - 95 - dB

OUT

, HO = VDD,

= +5V , GND = 0V, V

DD

F

F

RMS

RMS

= 217Hz 25 - 48 - dB

RIPPLE

= 1kHz 25 - 47 - dB

RIPPLE

(Connect to the

(Connect to the

= 2.4V , V

INH

TEMP

(°C)

= 0.8V , SD = MIX = INS = HD = V

INL

MIN

(Notes 4, 5) TYP

(Notes 4, 5) UNITS

MAX

25 - 80 - dB

25 - 110 - dB

25 - ±0.2 - dB

25 - 1.3 - °

25 -3 1.9 3 µA

Full - 1.9 - µA

25 -1 0.02 1 µA

Full - 0.02 - µA

Full 2.4 - - V

Full - - 0.8 V

INL

RMS

P-P

,

5

FN6514.1

June 27, 2007

ISL54003, ISL54005, ISL54006

Electrical Specifications - 3.6V Supply Test Conditions: V

GSO = GS1 = V

and between Hp_ and GND for SE drivers, Unless Otherwise Specified (Note 3).

PARAMETER TEST CONDITIONS

= +3.6V, GND = 0V, V

DD

, C

INL

= 1µF, RL is terminated between SPK+ and SPK- for BTL driver

REF

TEMP

(°C)

= 1.4V. V

INH

MIN

(Notes 4, 5) TYP

= 0.4V, SD = MIX = INS =

INL

MAX

(Notes 4, 5) UNITS

GENERAL

Quiescent Supply Current, I

Shutdown Supply Current, I

DD

SD

HO = V

INL

MIX = V

INL

(SE), Input AC coupled to ground (0.1µF)

HO = V

INL

MIX = V

INL

ground (0.1µF)

SD = VDD, HO = V

INS = V

INL

(BTL) and R

ground (0.1µF)

BTL AMPLIFIER DRIVER, HD = V

Output Offset Voltage, V

OS

Power Supply Rejection Ratio,

PSRR

HO = V

INH,

Measured between SPK+ and SPK-, Input AC

coupled to ground (0.1µF)

V

R

= 200mV

RIPPLE

= 8Ω, input AC coupled to

L

ground (0.1µF)

Output Power, P

OUT

Total Harmonic Distortion + Noise,

THD + N

Max Output Volt age Swing, V

RL = 8Ω, THD+N = 1%, f = 1kHz 25 - 310 - mW

= 8Ω, THD+N = 10%, f = 1kHz 25 - 528 - mW

R

L

= 8Ω, P

R

L

= 8Ω, P

R

L

OUTRL

= 8Ω, VSIGNAL = 3.6V

SINGLE ENDED AMPLIFIER DRIVERS, HD = V

Power Supply Rejection Ratio,

PSRR

Output Power, P

OUT

Total Harmonic Distortion + Noise,

THD + N

Max Output Volt age Swing, V

OUTRL

V

R

ground (0.1µF)

RL = 16Ω, THD+N = 1%, f = 1kHz 25 - 80 - mW

R

R

R

R

R

= 200mV

RIPPLE

= 32Ω, Ιnput AC coupled to

L

= 32Ω, THD+N = 1%, f = 1kHz 25 - 47 - mW

L

= 16Ω, THD+N = 10%, f = 1kHz 25 - 107 - mW

L

= 32Ω, THD+N = 10%, f = 1kHz 25 - 58 - mW

L

= 32Ω, P

L

= 32Ω, P

L

= 32Ω, V

or V

, HD = V

INH

or V

, RL = 8Ω (BTL) and RL = 32Ω

INH

or V

, HD = V

INH

or V

, RL = None, Input AC coupled to

INH

INL

or V

, MIX = V

INH

= 32Ω (SE), Input AC coupled to

L

UNLESS OTHERWISE SPECIFIED

INH,

, HD = 0V ,

P-P

= 200mW, f = 1kHz 25 - 0.4 - %

OUT

= 200mW, f = 20Hz to 20kHz 25 - 0.4 - %

OUT

HO = V

INH,

, HD = 0V ,

P-P

= 30mW, f = 1kHz 25 - 0.2 - %

OUT

= 30mW, f = 20Hz to 20kHz 25 - 0.3 - %

OUT

= 3.6V

SIGNAL

, INS = V

INL

, INS = V

INL

or V

, HD = Float,

INH

or V

INL

F

F

, f = 1kHz 25 - 5.8 - V

P-P

UNLESS OTHERWISE SPECIFIED

INL,

F

F

, f = 1kHz 25 - 3.2 - V

P-P

or V

INL

INH

or V

INL

INH

, RL = 8Ω

INH

= 217Hz 25 - 49 - dB

RIPPLE

= 1kHz 25 - 47 - dB

RIPPLE

= 217Hz 25 - 48 - dB

RIPPLE

= 1kHz 25 - 47 - dB

RIPPLE

25 - 4 50 mA

,

Full - 10 - mA

25 - 2.7 12 mA

,

Full - 3 - mA

25 - 13 50 µA

Full - 15 - µΑ

25 -150 38 150 mV

Full - 58 - mV

LOGIC INPUT

Input Leakage Current, I

I

, IHD, I

MIX

HO

Input Leakage Current, I

I

, IHD, I

MIX

V

V

INH

INL

HO

SD

SD

VDD = 3.6V , SD = 0V, INS = 0V, MIX = 0V, HD = 0V ,

INS

HO = 0V

, I

,

VDD = 3.6V, SD = VDD, INS = VDD, MIX = VDD,

INS

HD = V

, HO = VDD,

DD

25 - 1.9 - µA

Full - 1.9 - µA

25 - 0.02 - µA

Full - 0.02 - µA

Full 1.4 - - V

Full - - 0.4 V

, I

,

NOTES:

= input voltage to perform proper function.

3. V

IN

4. The algebraic convention, whereby the most negative value is a minimum and the most positive a maximum, is used in this data sheet.

5. Parts are 100% tested at +25°C. Over temperature limits established by characterization and are not production tested.

P-P

P-P

6

FN6514.1

June 27, 2007

ISL54003, ISL54005, ISL54006

ISL54003 Typical Application Circuit and Block Diagram

RIGHT AUDIO

LEFT AUDIO

0.22µF

0.22µF

IN

R

ROUTER/

IN

L

MIXER

V

BTL

SE

0.1µF

DD

SPK+

SPK-

100kΩ

HpR

HD

THERMAL

PROTECTION

MICRO

CONTROLLER

CLICK AND POP

SD

HO

LOGIC CONTROL

ISL54005 Typical Application Circuit and Block Diagram

RIGHT 1 AUDIO

RIGHT 2 AUDIO

LEFT 1 AUDIO

0.22µF

0.22µF

0.22µF

IN

1R

IN

2R

MUX/

IN

1L

ROUTER/

MIXER

SE

BIAS

GND

V

BTL

SE

DD

HpL

V

DD

REF

0.1µF

SPK+

SPK-

HpR

HD

C

1µF

REF

10k

100kΩ

HEADPHONE JACK

Ω

LEFT 2 AUDIO

CONTROLLER

MICRO

0.22µF

7

IN

2L

CLICK AND POP

SD

INS

HO

PROTECTION

LOGIC CONTROL

THERMAL

SE

BIAS

GND

V

HpL

DD

REF

C

1µF

REF

10k

Ω

HEADPHONE JACK

FN6514.1

June 27, 2007

ISL54003, ISL54005, ISL54006

ISL54006 Typical Application Circuit and Block Diagram

0.1µF

RIGHT 1 AUDIO

RIGHT 2 AUDIO

LEFT 1 AUDIO

LEFT 2 AUDIO

CONTROLLER

MICRO

0.22µF

0.22µF

0.22µF

0.22µF

IN

1R

IN

2R

IN

1L

IN

2L

CLICK AND POP

SD

INS

MIX

HO

MUX/

ROUTER/

MIXER

PROTECTION

LOGIC CONTROL

THERMAL

V

BTL

SE

SE

BIAS

GND

DD

SPK+

SPK-

HpR

HD

HpL

V

DD

REF

C

1µF

REF

100kΩ

10k

Ω

HEADPHONE JACK

Detailed Description

The Intersil ISL54003, ISL54005, and ISL54006 family of

devices are integrated audio power amplifier systems

designed to provide quality audio, while requiring minimal

external components. The low 0.4% THD+N ensures clean,

low distortion amplification of the audio signals. The devices

are designed to operate from a single +2.7V to +5V power

supply . All devices are of fered in a 20 Ld 4x4 TQFN package.

Targeted applications include battery powered equipment

such as cell-phones, MP3 players, and games/toys.

These parts contain one class AB BTL type p ower amplifier

for driving an 8Ω mono speaker and two class AB singleended (SE) type amplifiers for driving 16Ω or 32Ω

headphones.

The BTL when using a 5V supply is capable of delivering

800mW (typ) with 0.4% THD+N and 941mW (typ) with 1%

THD+N of continuous average power into an 8Ω BTL speaker

load. When the speaker load is connected across the

positive and negative terminals of the BTL driver the voltage

is doubled across the load and the power is quadrupled.

Each SE amplifier when using a 5V supply is capable of

delivering 50mW (typ) with 0.3% THD+N and 94mW (typ) with

1% THD+N of continuous average power into a 32Ω

headphone speaker .

When in Mono Mode (BTL driver active) these devices

automatically mix the active left and right audio inputs and

send the combined signal to the BTL driver. In Head phone

Mode the active right channel input is sent to the right

headphone speaker and the active left channel is sent to the

left headphone speaker.

The ISL54005 and ISL54006 feature a 2:1 stereo input

multiplexer front-end. This allows selection between two

stereo sources. The INS control pin determines which stereo

input is active. Applying logic “0” to the INS control pin

selects stereo input 1 (R1 and L1). Applying logic “1” to the

INS control pin selects stereo input 2 (R2 and L2).

The ISL54006 has the capablity of mixing the two stereo

inputs. When in MIX Mode and HEADPHONE Mode, the

part mixes the R1 input with the R2 input and sends the

combined signal to the HpR headphone driver and it mixes

the L1 input with the L2 input and sends the combined signal

to the HpL headphone driver. When in MIX Mode and

MONO Mode, it mixes all four inputs (R1 + R2 + L1 + L2)

and sends the combined signal to the BTL mono driver.

These parts have headphone sense input circuitry that

detects when a headphone jack has been inserted and

automatically switches the active audio inputs from the mono

BTL output driver to the headphone drivers. These parts also

feature a logic control pin (HO) that can override the sense

input circuitry.

8

FN6514.1

June 27, 2007

ISL54003, ISL54005, ISL54006

All devices in this family feature low power shutdown,

thermal overload protection and click/pop suppression. The

click and pop circuitry prohibits switching between input

channels until the audio input signals are at there lowest

point which eliminates audible transients in the speakers

when changing the audio input sources. The click/pop

circuitry also keeps speaker transients to an inaudibile level

when entering and leaving shutdown.

Typical application circuits and block diagrams for each

device in the family are provided on page 7 and page 8.

Truth tables for each device are provided on page 3.

DC Bias Voltage

The ISL54003, ISL54005, and ISL54006 have internal DC

bias circuitry, which DC offsets the incoming audio signal at

V

2. When using a 5V supply, the DC offset will be 2.5V.

DD/

When using a 3.6V supply, the DC offset will be 1.8V.

Since the signal gets biased internally at V

signals need to be AC coupled to the inputs of the device.

The value of the AC coupling capacitor depends on the low

frequency range required for the application. A capacitor of

0.22µF will pass a signal as low as 7.2Hz. The formula

required to calculated the capacitor value is:

C 1 6.28 f 100kΩ••⁄≥

The 100k

Ω is the impedance looking into the input of the

ISL54003, ISL54004, ISL54006 devices.

/2 the audio

DD

(EQ. 1)

Headphone (Single-Ended) Amplifiers

The ISL54003, ISL54005, and ISL54006 contains two

single-ended (SE) headphone amplifiers for driving the left

and right channels of a 32Ω or 16Ω headphone speaker.

One SE amplifier drives the right speaker of the headphone

and other SE amplifier drives the left speaker of the

headphone. The speaker load gets connected between the

output of the amplifier and ground.

The audio signal at the output of each SE driver is biased at

V

/2 and unlike the BTL driver that cancels this offset due

DD

to its differential connection, a capacitor is required at the

output of each SE driver to remove this DC voltage from the

headphone load.

This coupling capacitor along with the resistance of the

speaker load creates a high pass filter that sets the

amplifier’s lower bandpass frequency limit. The value of this

AC coupling capacitor depends on the low frequency range

required by the application. The formula required to calculate

the capacitor value is:

C 1 6.28 f Rspeaker••⁄≥

For an application driving a 32

Ω headphone with a lower

frequency requirement of 150Hz, the required capacitor

value would be :

C 1 6.28 150 32 33μF=••⁄≥

(EQ. 2)

(EQ. 3)

BTL Speaker Amplifier

The ISL54003, ISL54005, and ISL54006 contain one bridgetied load (BTL) amplifier designed to drive an 8Ω speaker

load differentially. The output to the BTL amplifier are SPK+

and SPK-. The speaker load gets connected across these

terminals.

A single BTL driver consists of an inverting and non-inverting

power op amps. The AC signal out of each op amp are equal

in magnitude but 180° out of phase, so the AC signal at

SPK+ and SPK- have the same amplitude but are 180° out

of phase.

Driving the load differentially using a BTL configuration

doubles the output voltage across the speaker load and

quadruples the power to the load. In effect you get a gain of

two due to this configuration at the load as compared to

driving the load with a single-ended amplifier with its load

connected between a single amplifier’s output and ground.

The outputs of the BTL are biased at V

gets connected across the + and - terminal of the BTL the

mid supply DC bias voltage at each output gets cancelled

out eliminating the need for large bulky output coupling

capacitors.

/2. When the load

DD

Use the closest standard value.

Headphone Sense Function

With a logic “1” at the HP control pin while the HO control pin

is low will activate the headphone drivers and disable the

BTL driver.

The application block diagrams on page 7 and page 8 show

the implementation of the headphone control function using

a common headphone jack.

The HP pin gets connected to the mechanical wiper blade of

the headphone jack. Two external resistors are required for

proper operation. A 100kΩ pull-up resistor from the HP pin to

V

and a 10kΩ pull-down resistor from the jack’s audio

DD

signal pin to ground of the jack signal pin to which the wiper

is connected. See the block diagrams on page 7 and page 8.

When no headphone plug is inserted into the jack, the

voltage at the HP pin gets set at a low voltage level due to

the 10kΩ resistor and 100kΩ resistor divider network

connection to V

When a headphone is inserted into the jack, the 10kΩ

resistor gets disconnected from the HP control pin and the

HP pin gets pulled up to V

the headphone drivers are activated.

DD

.

. Since the HP pin is now high,

DD

9

FN6514.1

June 27, 2007

ISL54003, ISL54005, ISL54006

A microprocessor or a switch can be used to drive the HP

pin rather than using the headphone jack contact pin.

Note: With a logic “1” at the HO pin, the BTL driver remains

active regardless of the voltage level at the HD pin. This

allows a headphone to be plugged into the headphone jack

without activating the HP drivers. Music will continue to play

through the internal 8Ω speaker rather than headphones.

Low Power Shutdown

With a logic “1” at the SD control pin the device enters the

low power shutdown state. When in shutdown the BTL and

headphone amplifiers go into an high impedance state and

I

supply current is reduced to 26µA (typ).

DD

In shutdown mode before the amplifiers enter the high

impedance/low current drive state, the bias voltage of V

remains connected at the output of the amplifiers through a

100kΩ resistor.

This resistor is not present during active operation of the

drivers but gets switch in when the SD pin goes high. It gets

removed when the SD pin goes low.

Leaving the DC bias voltage connected through a 100kΩ

resistor while going into and out of shutdown reduces the

transient at the speakers to a small level preventing clicking

or popping in the speakers.

Note: When the SD pin is High it over-rides all other logic

pins.

DD

/2

QFN Thermal Pad Considerations

The QFN package features an exposed thermal pad on its

underside. This pad lowers the package’s thermal resistance

by providing a direct heat conduction path from the die to the

PCB. Connect the exposed thermal pad to GND by using a

large copper pad and multiple vias to the GND plane. The

vias should be plugged and tented with plating and solder

mask to ensure good thermal conductivity.

Best thermal performance is achieved with the largest

practical copper ground plane area.

PCB Layout Considersations and Power

Supply Bypassing

To maintain the highest load dissipation and widest output

voltage swing, the power supply PCB traces and the traces

that connect the output of the drivers to the speaker loads

should be made as wide as possible to minimize losses due

to parasitic trace resistance.

Proper supply bypassing is necessary for high power supply

rejection and low noise performance. A filter network

consisting of a 10µF capacitor in parallel with a 0.1µF

capacitor is recommended at the voltage regulator that is

providing the power to the ISL54003, ISL54004, ISL54006

IC.

Local bypass capacitors of 0.1µF should be put at each VDD

pin of the ISL54003, ISL54004, ISL54006 devices. They

should be located as close as possible to the pin, keeping

the length of leads and traces as short as possible.

Typical Performance Curves T

1

0.9

VDD = 5V

0.8

BTL

0.7

0.6

0.5

0.4

0.3

THD+N (%)

0.2

0.1

= 8Ω

R

L

PO = 800mW

20 20k50 100 200 500 1k 2k 5k 10k

FREQUENCY (Hz)

FIGURE 1. THD+N vs FREQUENCY FIGURE 2. THD+N vs FREQUENCY

A 1µF capacitor from the REF pin (pin 10) to ground is

needed for optimum PSRR and internal bias voltage stability.

= +25°C, Unless Otherwise Specified.

A

1

0.9

0.8

0.7

0.6

0.5

0.4

0.3

THD+N (%)

0.2

0.1

20 20k50 100 200 500 1k 2k 5k 10k

VDD = 3.6V

BTL

R

= 8Ω

L

= 200mW

P

O

FREQUENCY (Hz)

10

FN6514.1

June 27, 2007

ISL54003, ISL54005, ISL54006

Typical Performance Curves T

10

VDD = 5V

5

BTL

R

= 8Ω

L

2

f = 1kHz

1

0.50

0.20

THD+N (%)

0.10

0.05

0.02

0.01

10m 120m 50m 100m 200m 500m

OUTPUT POWER (W)

FIGURE 3. THD+N vs OUTPUT POWER FIGURE 4. THD+N vs OUTPUT POWER

1

0.9

VDD = 5V

0.8

SE

0.7

0.6

0.5

0.4

= 32Ω

R

L

P

= 50mW

O

= +25°C, Unless Otherwise Specified. (Continued)

A

10

VDD = 3.6V

5

BTL

R

= 8Ω

L

2

f = 1kHz

1

0.50

0.20

THD+N (%)

0.10

0.05

0.02

0.01

10m 600m20m 40m 70m 100m 200m

1

0.9

0.8

0.7

0.6

0.5

0.4

VDD = 5V

SE

= 16Ω

R

L

= 50mW

P

O

OUTPUT POWER (W)

0.3

THD+N (%)

0.2

0.1

20 20k50 100 200 500 1k 2k 5k 10k

FREQUENCY (Hz)

FIGURE 5. THD+N vs FREQUENCY FIGURE 6. THD+N vs FREQUENCY

1

VDD = 3.6V

0.50

0.20

0.10

THD+N (%)

0.05

0.02

SE

R

= 32Ω

L

P

= 30mW

O

0.3

THD+N (%)

0.2

0.1

20 20k50 100 200 500 1k 2k 5k 10k

FREQUENCY (Hz)

1

VDD = 3.6V

0.50

0.20

0.10

THD+N (%)

0.05

0.02

SE

= 16Ω

R

L

P

= 60mW

O

0.01

20 20k50 100 200 500 1k 2k 5k 10k

FREQUENCY (Hz)

FIGURE 7. THD+N vs FREQUENCY FIGURE 8. THD+N vs FREQUENCY

11

0.01

20 20k50 100 200 500 1k 2k 5k 10k

FREQUENCY (Hz)

FN6514.1

June 27, 2007

ISL54003, ISL54005, ISL54006

Typical Performance Curves T

10

5

2

1

0.50

0.20

THD+N (%)

0.10

0.05

0.02

0.01

10m 100m20m 30m 40m 50m 70m

0.50

VDD = 5V

SE

= 32Ω

R

L

f = 1kHz

OUTPUT POWER (W)

FIGURE 9. THD+N vs OUTPUT POWER FIGURE 10. THD+N vs OUTPUT POWER

10

5

2

1

VDD = 3.6V

SE

= 32Ω

R

L

f = 1kHz

= +25°C, Unless Otherwise Specified. (Continued)

A

10

5

2

1

0.50

0.20

THD+N (%)

0.10

0.05

0.02

0.01

10m 200m20m 30m 50m 70m 100m

10

5

2

1

0.50

VDD = 5V

SE

RL = 16Ω

f = 1kHz

VDD = 3.6V

SE

R

= 16Ω

L

f = 1kHz

OUTPUT POWER (W)

0.20

THD+N (%)

0.10

0.05

0.02

0.01

10m 55m12m 15m 20m 25m 35m 45m

OUTPUT POWER (W)

0.20

THD+N (%)

0.01

0.05

0.02

0.01

10m 100m20m 30m 40m 50m 70m

OUTPUT POWER (W)

FIGURE 11. THD+N vs OUTPUT POWER FIGURE 12. THD+N vs OUTPUT POWER

-50

VDD = 5V

= 15mW

P

O

INxR TO HPL

INxL TO HPR

20 20k50 100 200 500 1k 2k 5k 10k

FREQUENCY (Hz)

CROSSTALK (dB)

-55

-60

-65

-70

-75

-80

-85

-90

-95

-100

-105

-110

-60

VDD = 5V

-65

-70

-75

-80

-85

-90

-95

-100

OFF ISOLATION (dB)

-105

-110

-115

-120

20 20k50 100 200 500 1k 2k 5k 10k

FREQUENCY (Hz)

HPR AND HPL

BTL

FIGURE 13. CROSSTALK vs FREQUENCY FIGURE 14. OFF ISOLATION vs FREQUENCY

12

FN6514.1

June 27, 2007

ISL54003, ISL54005, ISL54006

Typical Performance Curves T

-22

-26

-30

-34

-38

-42

-46

-50

PSRR (dB)

-54

-58

-62

-66

-70

VDD = 5V

BTL

V

= 200mV

RIPPLE

10 20k20 50 100 200 500 1k 2k 5k 10k

P-P

FREQUENCY (Hz)

FIGURE 15. PSRR vs FREQUENCY FIGURE 16. PSRR vs FREQUENCY

700

600

= +25°C, Unless Otherwise Specified. (Continued)

A

-20

-25

VDD = 5V

SE

-30

V

= 200mV

RIPPLE

-35

-40

-45

-50

-55

-60

PSRR (dB)

-65

-70

-75

-80

-85

-90

10 20k20 50 100 200 500 1k 2k 5k 10k

400

350

P-P

HPR

HPL

FREQUENCY (Hz)

500

400

300

200

POWER DISSIPATION (mW)

100

0

0 250 500 750 1000

P

(mW)

OUT

VDD = 5V

BTL

R

= 8Ω

L

300

250

200

150

100

POWER DISSIPATION (mW)

50

0

0 100 200 300 400

(mW)

P

OUT

FIGURE 17. POWER DISSIPATION vs OUTPUT POWER FIGURE 18. POWER DISSIPATION vs OUTPUT POWER

Die Characteristics

SUBSTRATE POTENTIAL (POWERED UP):

GND

PROCESS:

Submicron CMOS

VDD = 3.6V

BTL

R

= 8Ω

L

500

13

FN6514.1

June 27, 2007

ISL54003, ISL54005, ISL54006

Thin Quad Flat No-Lead Plastic Package

(TQFN)

Thin Micro Lead FramePlastic Package

(TMLFP)

L20.4x4A

20 LEAD QUAD FLAT NO-LEAD PLASTIC PACKAGE

(COMPLIANT TO JEDEC MO-220WGGD-1 ISSUE I)

MILLIMETERS

SYMBOL

A 0.70 0.75 0.80 -

A1 - 0.02 0.05 -

A2 - 0.55 0.80 9

A3 0.20 REF 9

b 0.18 0.25 0.30 5, 8

D 4.00 BSC -

D1 3.75 BSC 9

D2 1.95 2.10 2.25 7, 8

E 4.00 BSC -

E1 3.75 BSC 9

E2 1.95 2.10 2.25 7, 8

e 0.50 BSC -

k0.20 - - -

L 0.35 0.60 0.75 8

N202

Nd 5 3

Ne 5 3

P- -0.609

θ --129

NOTES:

1. Dimensioning and tolerancing conform to ASME Y14.5-1994.

2. N is the number of terminals.

3. Nd and Ne refer to the number of terminals on each D and E.

4. All dimensions are in millimeters. Angles are in degrees.

5. Dimension b applies to the metallized terminal and is measured

between 0.15mm and 0.30mm from the terminal tip.

6. The configuration of the pin #1 identifier is optional, but must be

located within the zone indicated. The pin #1 identifier may be

either a mold or mark feature.

7. Dimensions D2 and E2 are for the exposed pads which provide

improved electrical and thermal performance.

8. Nominal dimensions are provided to assist with PCB Land Pattern

Design efforts, see Intersil Technical Brief TB389.

9. Features and dimensions A2, A3, D1, E1, P & θ are present when

Anvil singulation method is used and not present for saw

singulation.

NOTESMIN NOMINAL MAX

Rev. 0 11/04

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems.

Intersil Corporation’s quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without

notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and

reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result

from its use. No license is granted by implicat ion or oth erwise u nde r any p a tent or p at ent r ights of Intersil or its subsidiari es.

For information regarding Intersil Corporation and its products, see www.intersil.com

14

FN6514.1

June 27, 2007

Loading...

Loading...