Page 1

®

www.BDTIC.com/Intersil

ISL5217

Data Sheet July 8, 2005 FN6004.3

Quad Programmable Up Converter

The ISL5217 Quad Programmable UpConverter (QPUC) is a

QASK/FM modulator/FDM upconverter designed for high

dynamic range applications such as cellular basestations. The

QPUC combines shaping and interpolation filters, a complex

modulator, and timing and carrier NCOs into a single package.

Each QPUC can create four FDM channels. Multiple QPUCs can

be cascaded digitally to provide for up to 16 FDM channels in

multi-channel applications.

The ISL5217 supports both vector and FM modulation. In vector

modulation mode, the QPUC accepts 16-bit I and Q samples to

generate virtually any quadrature AM or PM modulation format.

The QPUC also has two FM modulation modes. In the FM with

pulse shaping mode, the 16-bit frequency samples are pulse

shaped/bandlimited prior to FM modulation. No band limiting filter

follows the FM modulator. This FM mode is useful for GMSK type

modulation formats. In the FM with band limiting filter mode, the

16-bit frequency samples directly drive the FM modulator. The

FM modulator output is filtered to limit the spectral occupancy.

This FM mode is useful for analog FM or FSK modulation

formats.

The QPUC includes an NCO driven interpolation filter, which

allows the input and output sample rate to have an integer

and/or variable relationship. This re-sampling feature

simplifies cascading modulators with sample rates that do not

have harmonic or integer frequency relationships.

The QPUC offers digital output spectral purity that exceeds

100dB at the maximum output sample rate of 104MSPS, for

input sample rates as high as 6.5MSPS.

A 16-bit microprocessor compatible interface is used to load

configuration and baseband data. A programmable FIFO depth

interrupt simplifies the interface to the I and Q input FIFOs.

Features

• Output Sample Rates Up to 104MSPS with Input Data

Rates Up to 6.5MSPS

• Processing Capable of >140dB SFDR Out of Band

• Vector modulation for supporting IS-136, EDGE, IS95, TDSCDMA, CDMA-2000-1X/3X, W-CDMA, and UMTS

• FM Modulation for Supporting AMPS, NMT, and GSM

• Four Completely Independent Channels on Chip, Each With

Programmable 256 Tap Shaping FIR, Half-Band, and High

Order Interpolation Filters

• 16-Bit parallel µProcessor Interface and Four Independent

Serial Data Inputs

• Two 20-bit I/O Buses and Two 20-bit Output Buses Allow

Cascading Multiple Devices

• 32-Bit Programmable Carrier NCO; 48-Bit Programmable

Symbol Timing NCOs

• Dynamic Gain Profiling and Output Routing Control

• Pb-Free Plus Anneal Available (RoHS Compliant)

Applications

• Single or Multiple Channel Digital Software Radio

Transmitters (Wide-Band or Narrow-Band)

• Base Station Transmitter and Smart Antennas

• Operates with HSP50216 in Software Radio Solutions

• Compatible with the HI5960/ISL5961 or HI5828/ISL5929

D/A Converters

Ordering Information

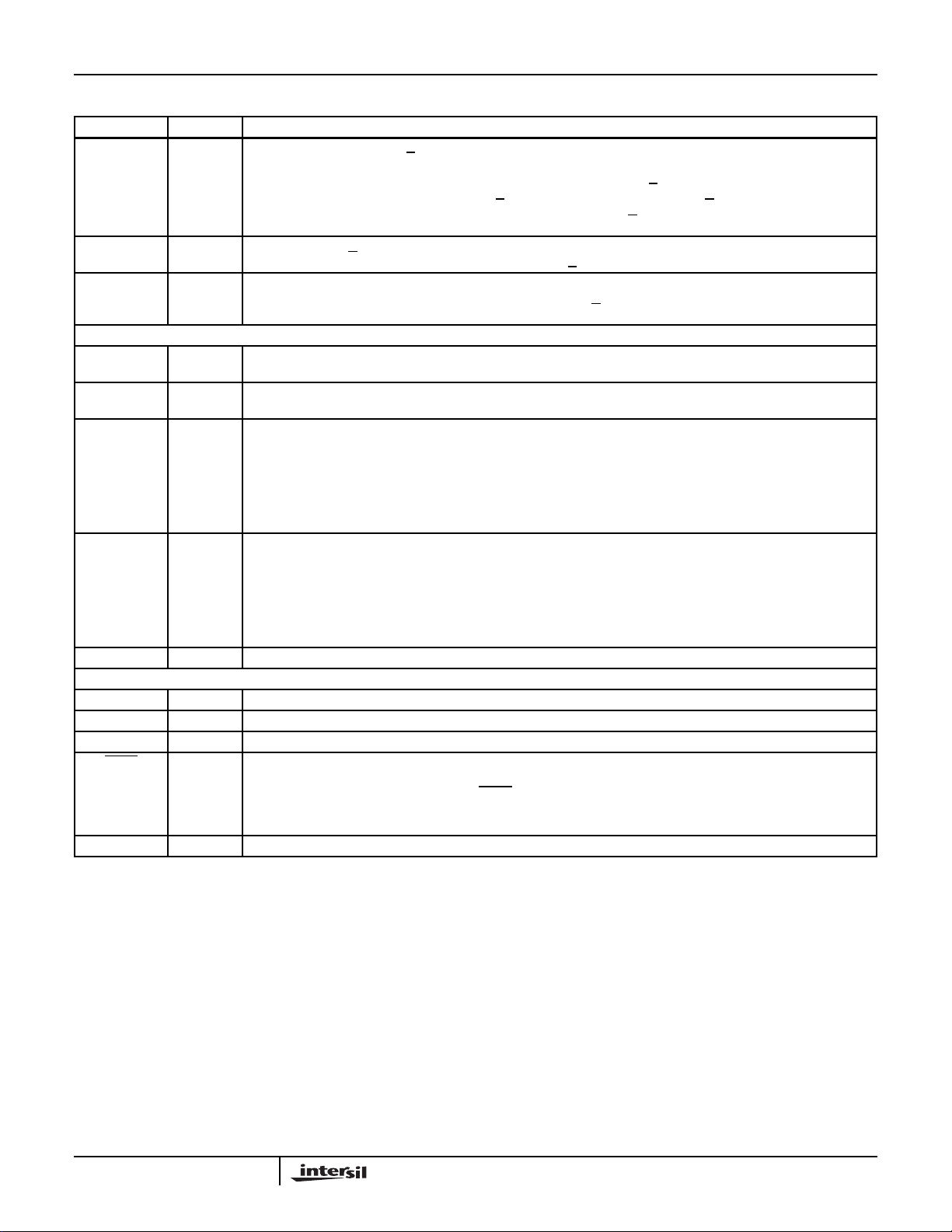

PART

NUMBER

ISL5217KI -40 to 85 196 Ld BGA V196.15x15

ISL5217KIZ (Note) -40 to 85 196 Ld BGA (Pb-free) V196.15x15

ISL5217EVAL1 25 Evaluation Kit

NOTE: Intersil Pb-free plus anneal products employ special Pb-free material sets;

molding compounds/die attach materials and 100% matte tin plate termination finish,

which are RoHS compliant and compatible with both SnPb and Pb-free soldering

operations. Intersil Pb-free products are MSL classified at Pb-free peak reflow

temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

TEMP

RANGE (

o

C) PACKAGE

PKG. DWG.

#

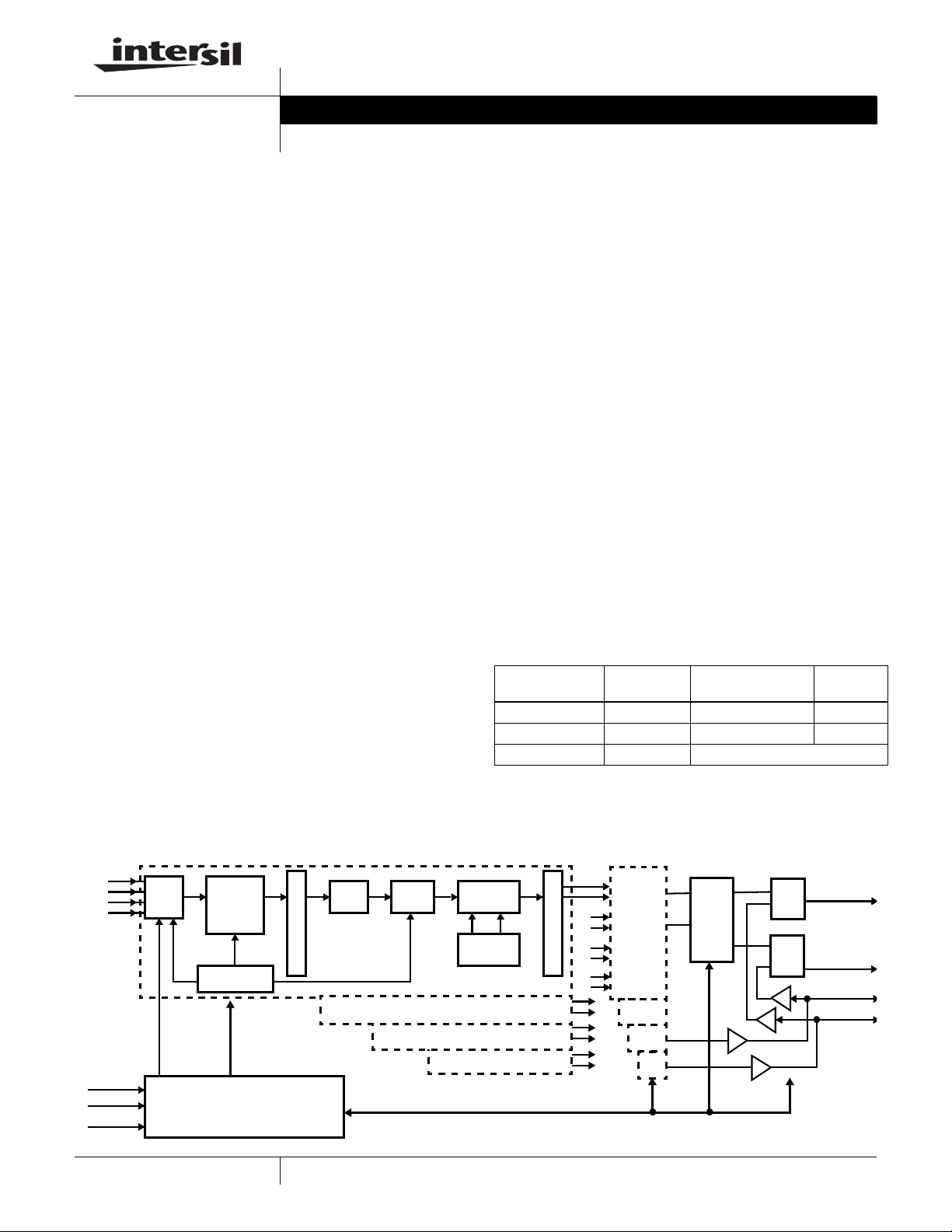

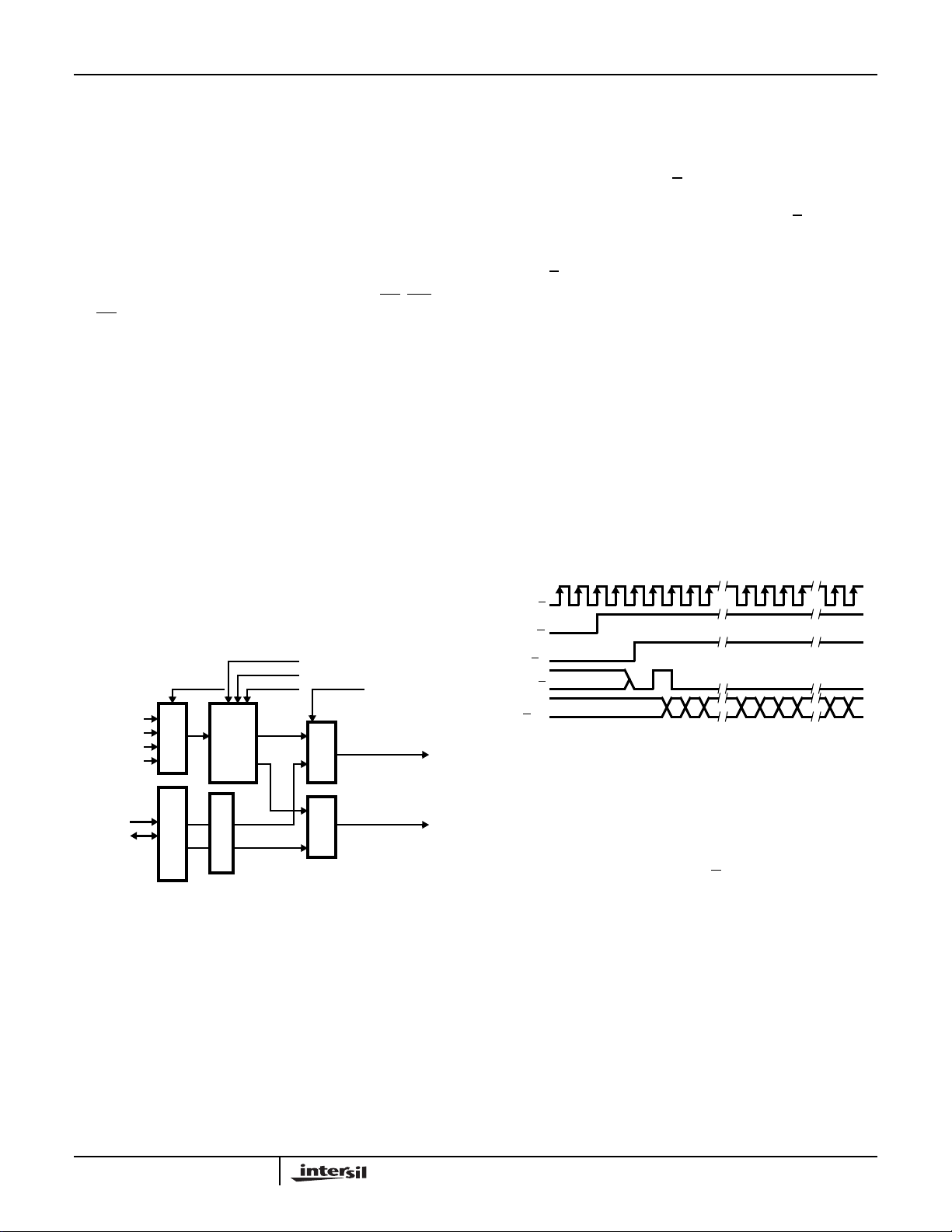

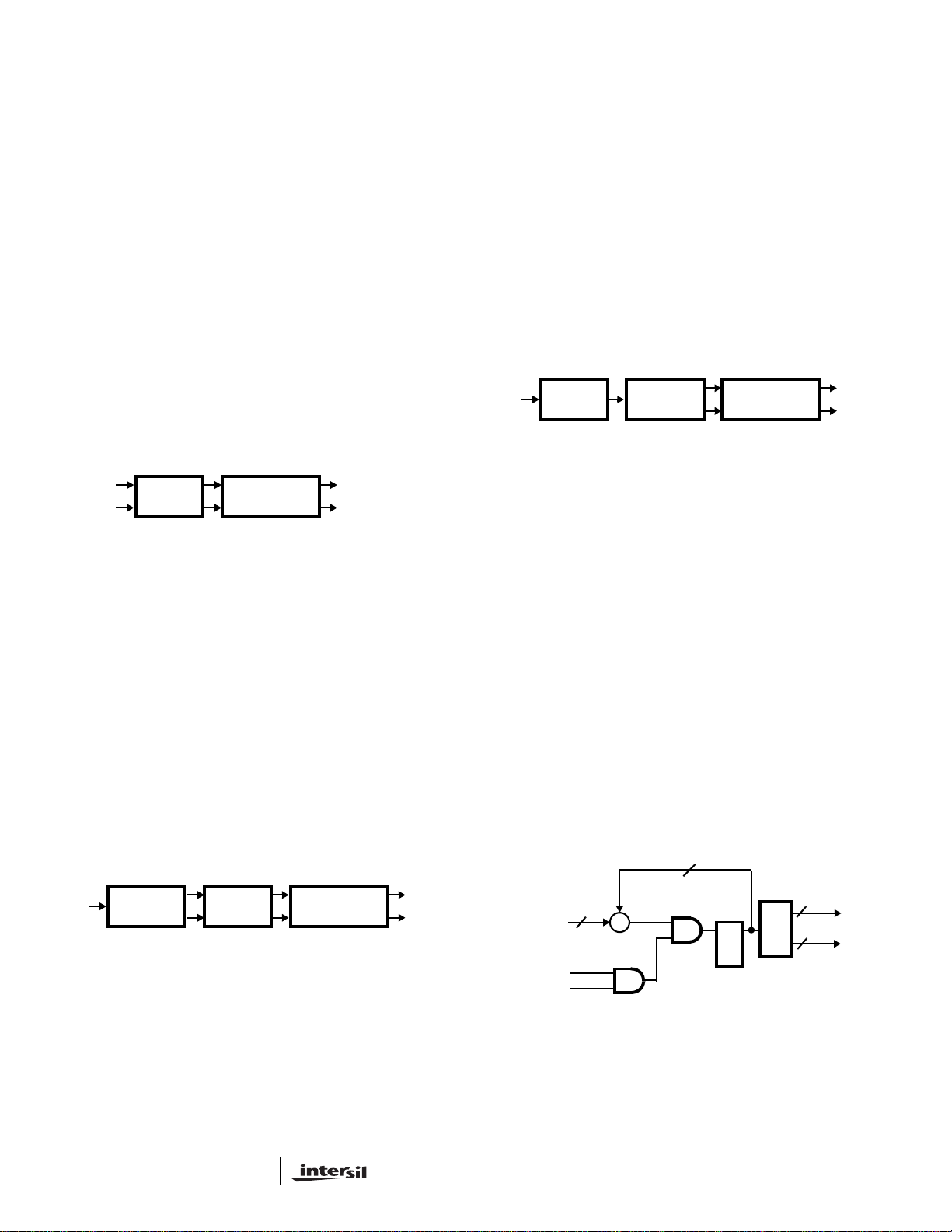

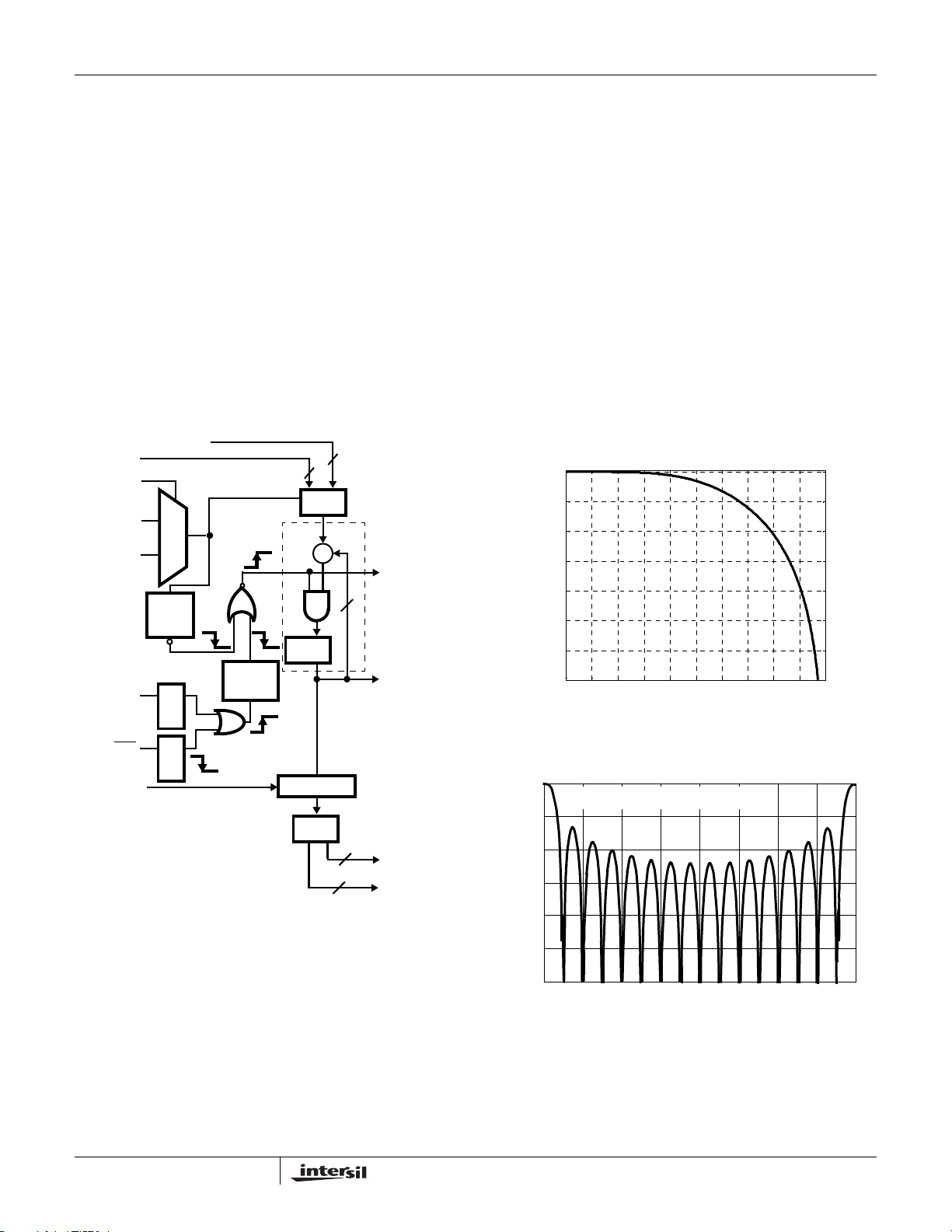

Block Diagram

SDA

SDB

SDC

SDD

P<15:0>

A<6:0>

{CNTRL}

I/Q

INPUT

DATA

SHAPING

FILTER/

FM MOD.

SAMPLE

PARALLEL HOST INTERFACE

I/Q

NCO

1

I/Q I/Q I/Q

HALF

BAND

GAIN PROFILE

INTPL

FILTER

CONFIGURATION AND CONTROL BUS

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 1-888-468-3774

COMPLEX

MIXER

SIN COS

CARRIER

NCO

CHANNEL 0

CHANNEL 1

CHANNEL 2

CHANNEL 3

I/Q

GAIN CONTROL

| Intersil (and design) is a registered trademark of Intersil Americas Inc.

All other trademarks mentioned are the property of their respective owners.

I0

Q0

4 CH

I1

SUM

Q1

I2

Q2

Σ

I3

Q3

Σ

Σ

Σ

Σ

Copyright Intersil Americas Inc. 2003, 2005. All Rights Reserved

DELAY

SUM

1

2

3

4

CAS

SUM

CAS

SUM

IOUT(19:0)

QOUT(19:0)

QIN(19:0)

IIN(19:0)

Page 2

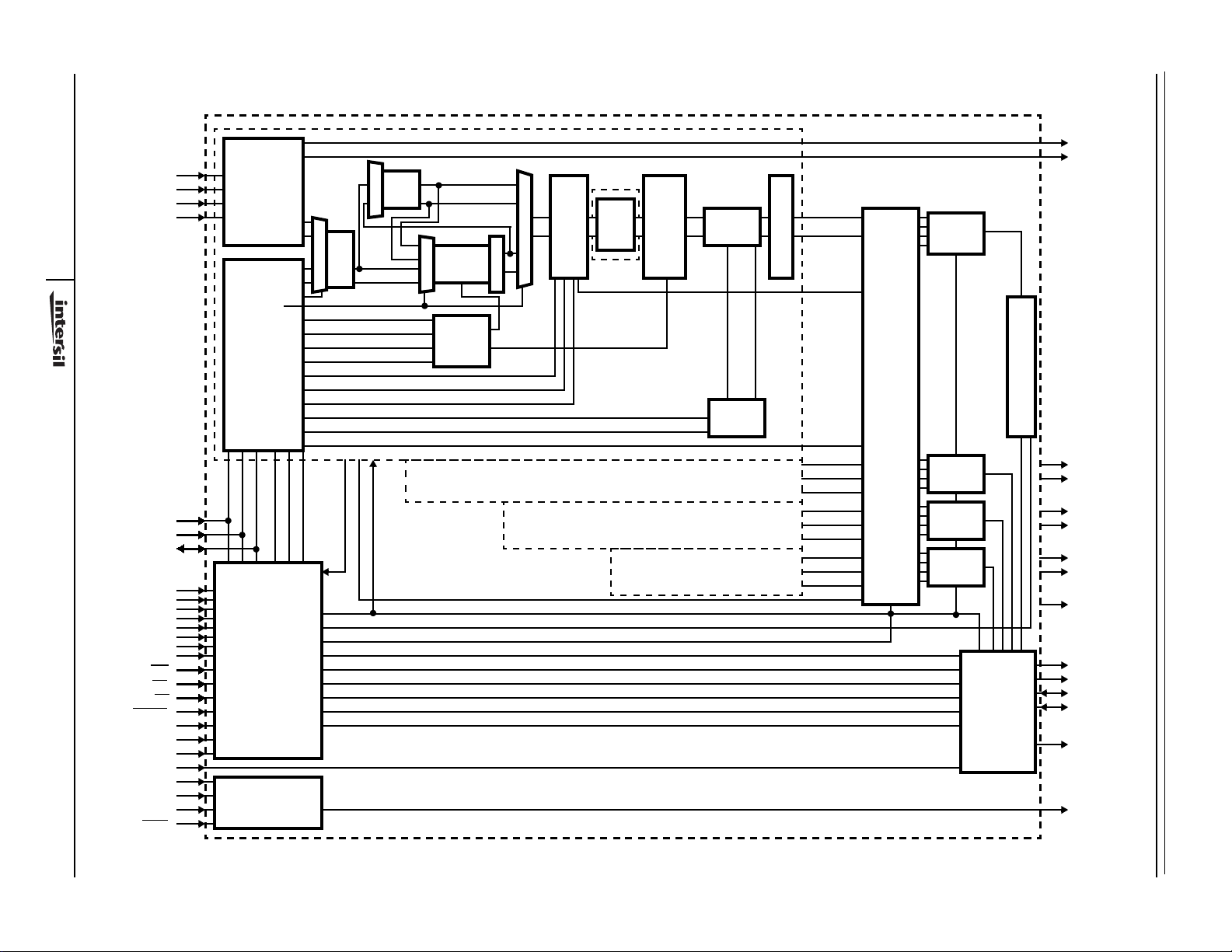

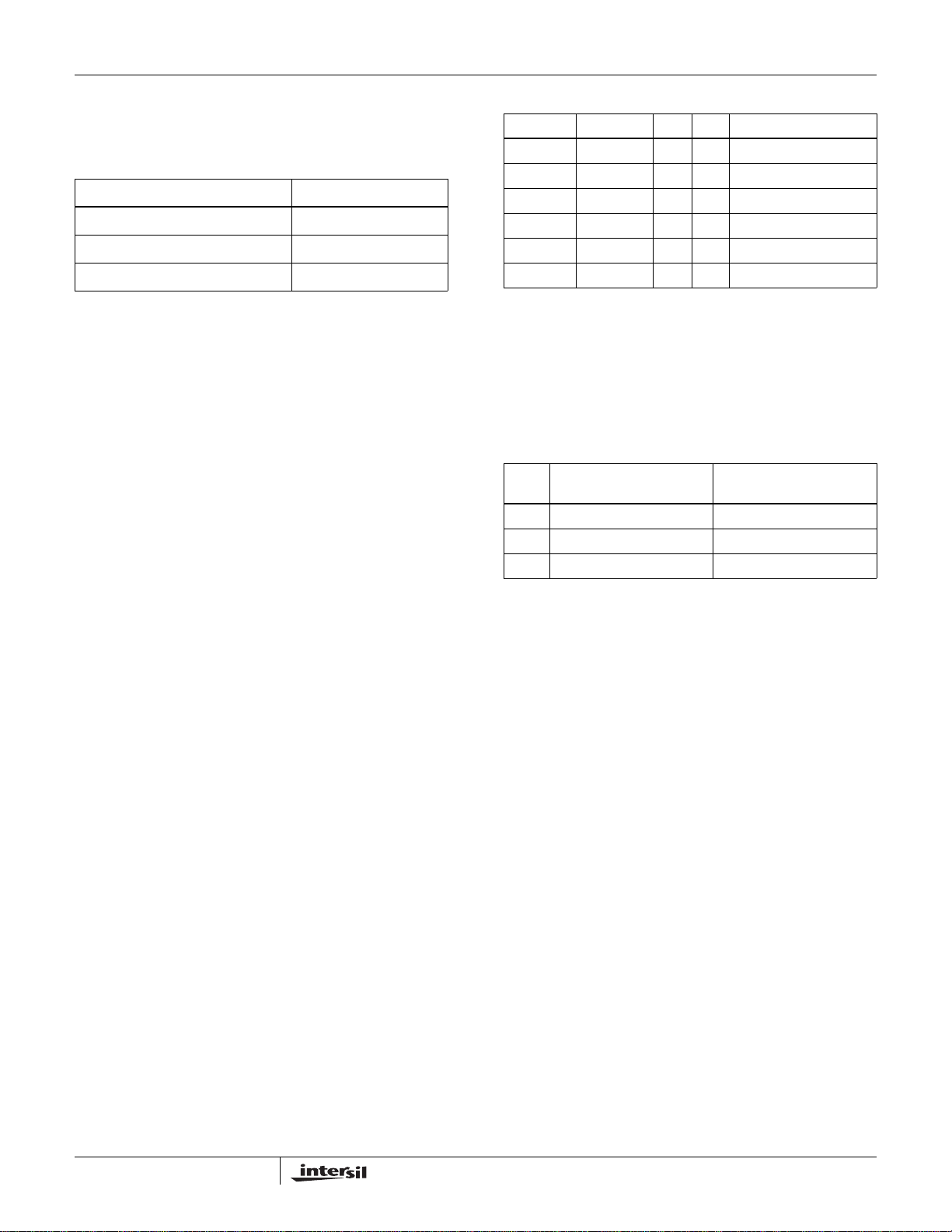

Functional Block Diagram

www.BDTIC.com/Intersil

ISL5217

SDA

SDB

SDC

SDD

2

CLK

A<6:0>

P<15:0>

TXENA

TXENB

TXENC

TXEND

UPDA

UPDB

UPDC

UPDD

WR

RD

CS

RESET

RDMODE

OUTEN<1:0>

TRITST

OFFBIN

TMS

TDI

July 8, 2005

FN6004.3

TCK

TRST

SERIAL

INTERFACE

I IN<15:0>

Q IN<15:0>

I IN<15:0>

Q IN<15:0>

SER._PAR.

CHANNEL

UP

INTERFACE

AND TIMING

<4:0>

UPDATE<3:0>

TX_ENABLE<3:0>

DEVICE

UPROCESSOR

INTERFACE

JTAG

16

I FM

Q FM

I SF

SHAPING

MUX

FILTER

SAMPLE

NCO

FM

MUX

MOD.

/

I FIFO

MUX

FIFO

1-7 DEEP

MOD. TYPE <1:0>

FID<31:0>

SR<47:0>

INTPL PHASES<1:0>

PHASE OFFSET<1:0>

GAIN<11:0>

GAIN PROFILE LENGTH<6:0>

OUTPUT_EN

CARRIER PHASE<15:0>

CARRIER FREQUENCY<31:0>

DUALQUADMODE (CH0 AND CH2 ONLY)

CH_SELECT<3:0>

ROUTEBUS_UPDATE

RESET

CASCADE_DELAY<1:0>

ROUTEBUS<15:0>

CASCADE_IN_ENABLE

OUTPUTMODE<1:0>

OUTPUTMODE2X

I_STROBE_EN

ISTROBEPOLARITY

TRITST_ENABLE_BUS<7:0>

/

16

Q FIFO

/

ISTROBEUPDATE

/

18

/

18

/

20

/

LIMITER

COARSE

PHASE<3:0>

20

20

MUX

/

/

HALF

BAND

GAIN PROFILE

BYPASS

CH_ENABLE<0>

FINE

PHASE<11:0>

INTERPOLATION

SCLKA

FSRA

21

/

COMPLEX

21

MIXER

/

FILTER

COS<18:0>

SIN<18:0>

CARRIER

NCO

CHANNEL 0

CHANNEL 1

CHANNEL 2

CHANNEL 3

GAIN CONTROL

I<21:0>

Q<21:0>

I<21:0>

Q<21:0>

CH_EN<1>

I<21:0>

Q<21:0>

CH_EN<2>

I<21:0>

Q<21:0>

CH_EN<3>

ROUTING

CONTROL

4 INPUT

SUMMER

1

4 INPUT

SUMMER

2

4 INPUT

SUMMER

3

4 INPUT

SUMMER

4

OUTPUT

CONTROL

PROGRAMMABLE DELAY

ISL5217

SCLKB

FSRB

SCLKC

FSRC

SCLKD

FSRD

ISTRB

IOUT<19:0>

QOUT<19:0>

IIN<19:0>

QIN<19:0>

SYNCO

TDO

Page 3

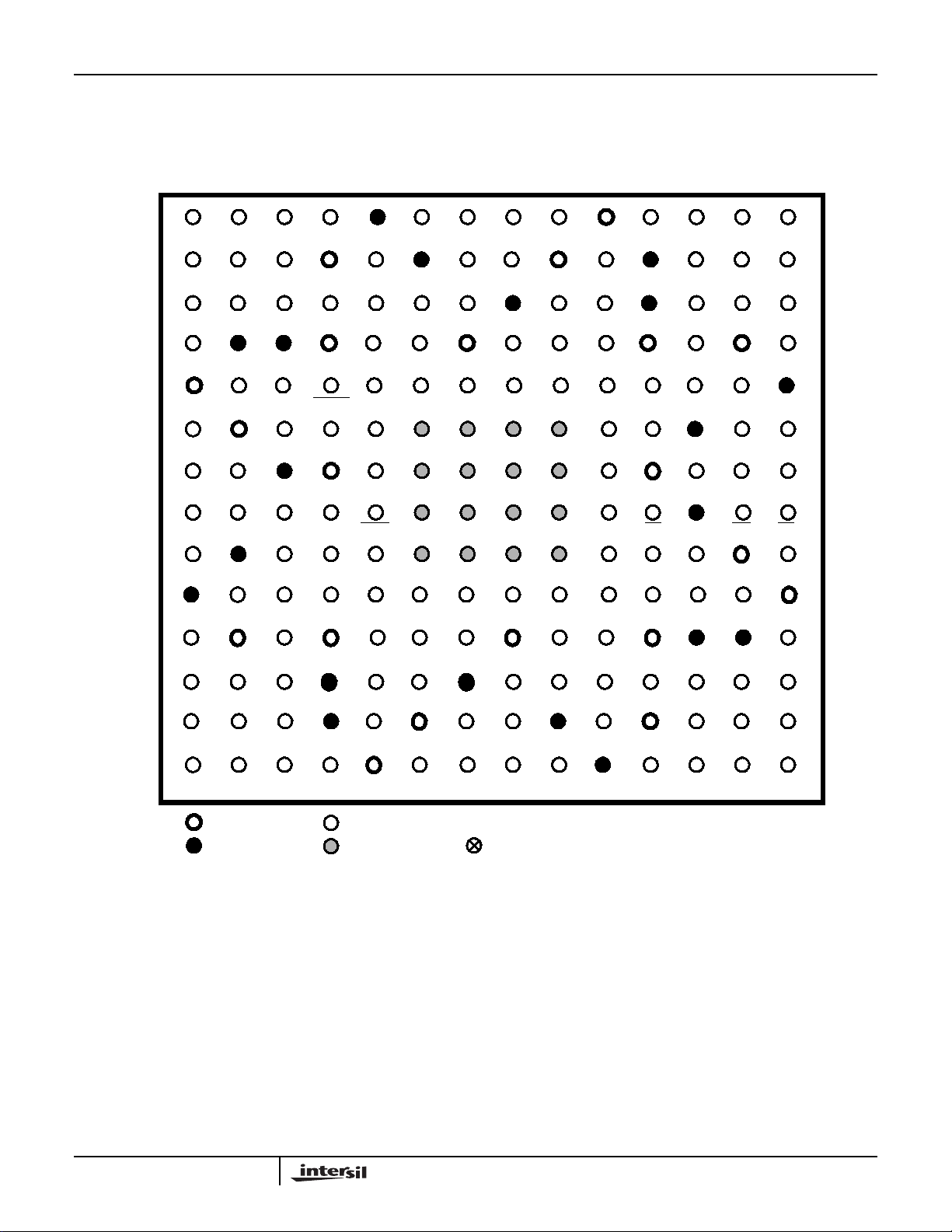

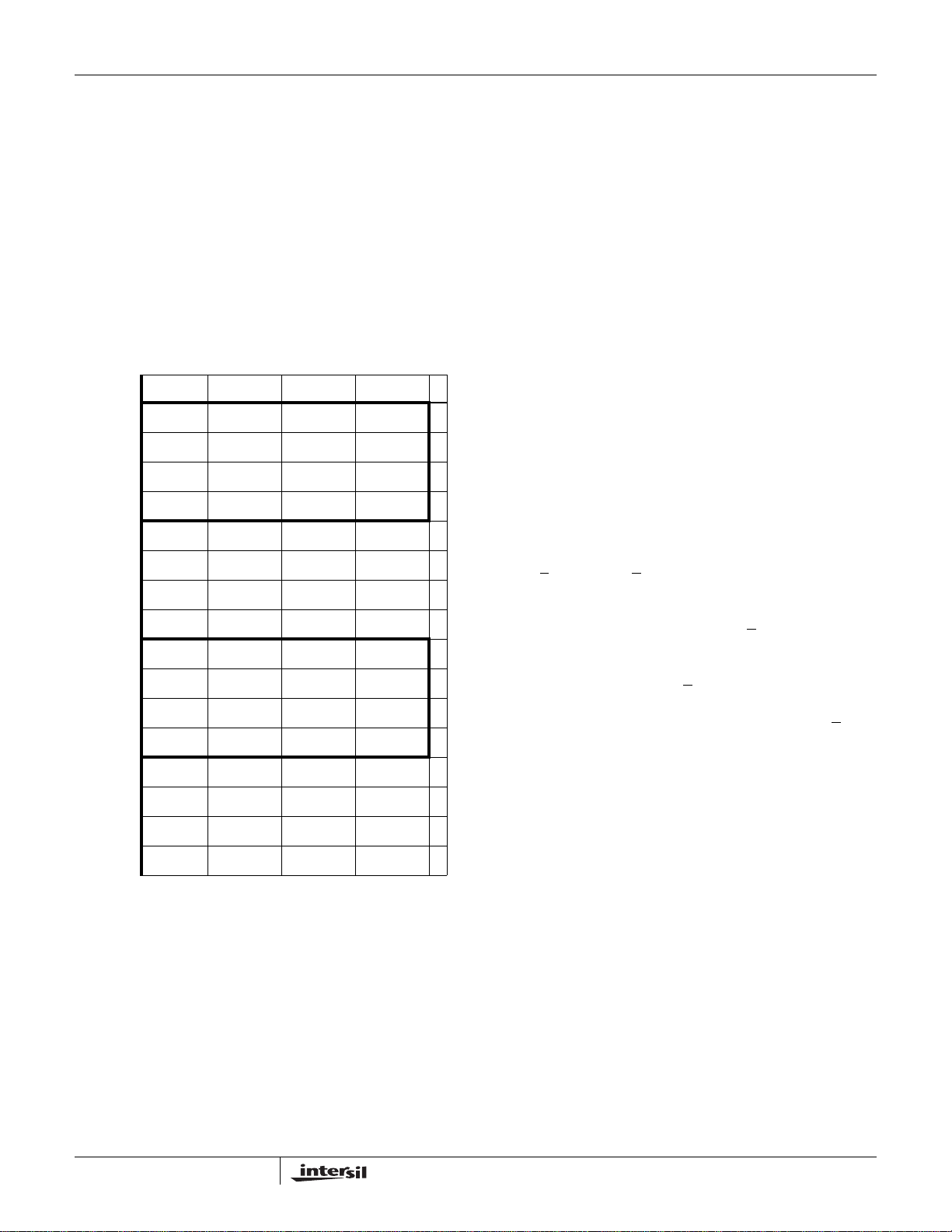

Pinout

www.BDTIC.com/Intersil

ISL5217

196 LdBGA

TOP VIEW

123456789 1110

A

IOUT14

B

IOUT15IOUT16 IOUT5

C

QOUT16

IOUT17IOUT18 P6

D

GND GND VCCIO VCCC VCCC VCCC

E

VCCCQOUT17 QOUT18

F

VCCC P1

QOUT19

G

CLK A4 A2QIN19

H

J

K

L

M

N

P

TCK GND RDQIN17 TMS

QIN15 UPDD

GND QIN14 UPDC VCCC

IIN14 TXENC SCLKB

IIN15 GND IIN7 IIN3

GND

QIN18

GND

QIN16 FSRB

QIN13

OUTEN1

OUTEN0

VCCC VCCC

TRST

TDO

QIN12

OFFBIN

QIN11

GND GNDIIN5 UPDB TXEND

VCCC GND

VCCIO I OUT0IOUT2IOUT4 P15 P12 P11IOUT13 IOUT12 IOUT10 GND IOUT8 IOUT6

IOUT1VCCIOIOUT3IOUT11 VCCIO GNDIOUT9

QOUT0QOUT3GND P14 P8QOUT15 QOUT12 QOUT9 IOUT7

QOUT1

QOUT4IOUT19 QOUT6 P4QOUT13 QOUT10

QOUT5QOUT7QOUT14 QOUT11 QOUT8 QOUT2

A6

A1

A0

SYNCO

QIN3QIN5QIN9 QIN7

FSRA

RDMODEQIN2IIN18 SCLKDQIN8 QIN6

SDB SDDQIN1IIN16 QIN4

QIN0IIN9 VCCC GND

GND P13 P10 P9

GND

FSRCIIN19 FSRDTDI

UPDA

VCCIOIIN1

SDAIIN0IIN13 IIN2 SDC TXENB SCLKAIIN12 IIN10 IIN8 IIN6 IIN4

P2 GNDRESET

P0ISTRB GND A5TRITST

CS

12

P7

A3

GNDVCCIOVCCCVCCIOVCCIO

TXENA

13 14

P3P5

WR

VCCC

GND

SCLKCIIN17 IIN11 QIN10

POWER PIN

GROUND PIN

SIGNAL PIN

THERMAL BALL

NC (NO CONNECTION)

NOTE:

Thermal balls should be connected to the ground plane.

3

FN6004.3

July 8, 2005

Page 4

ISL5217

www.BDTIC.com/Intersil

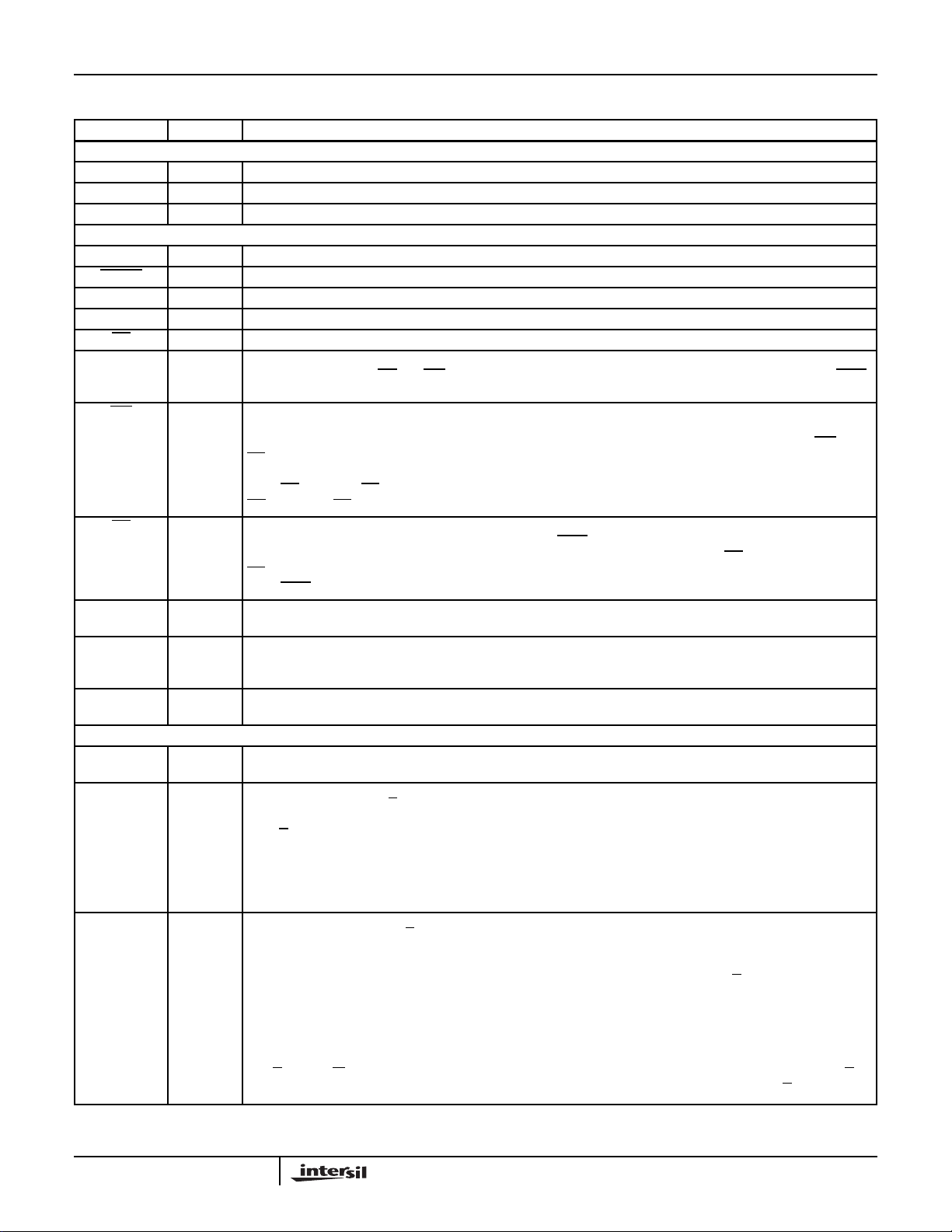

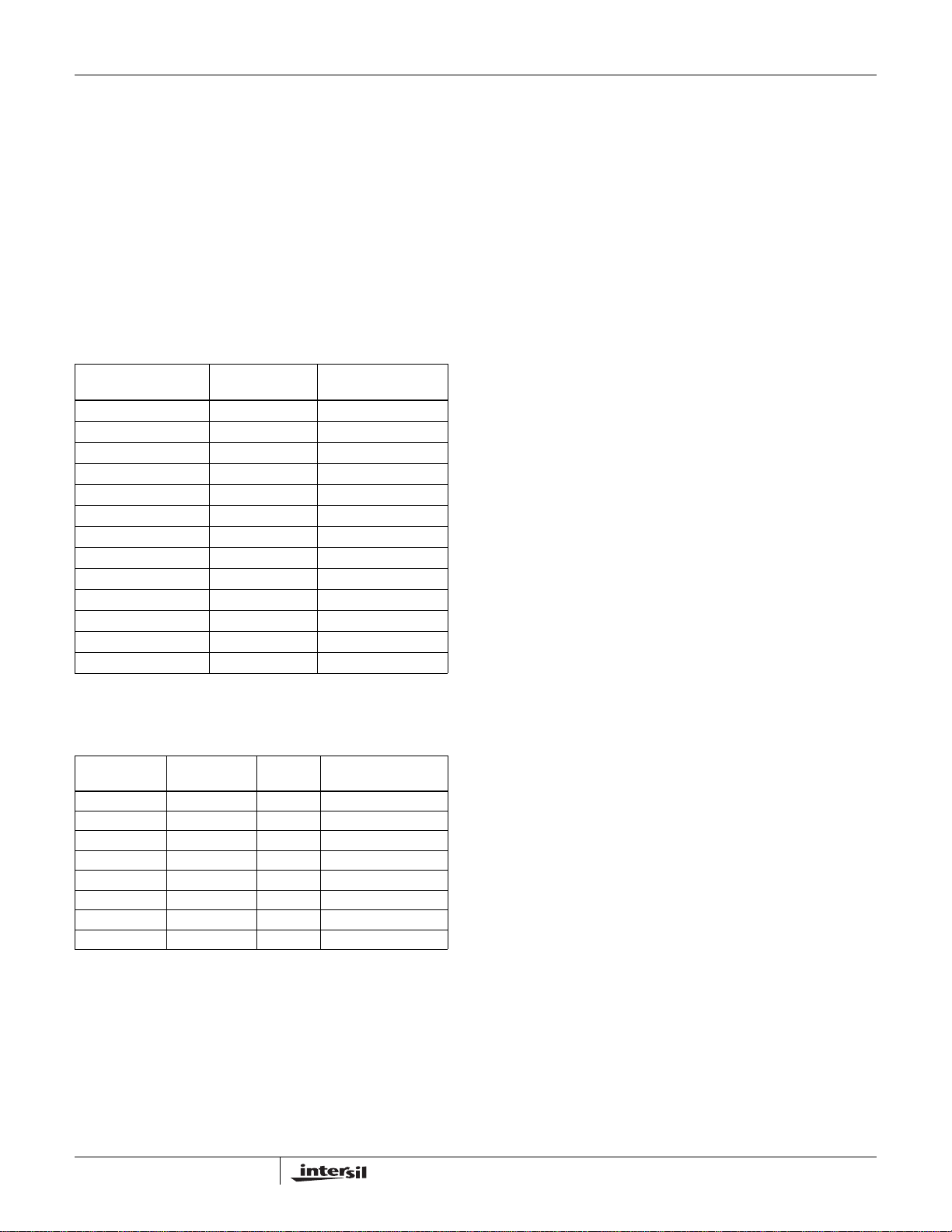

Pin Descriptions (all signals are active high unless otherwise stated)

NAME TYPE DESCRIPTION

POWER SUPPLY

VCCC - Positive Device Core Power Supply Voltag e, 2.5V ±0.125V.

VCCIO - Positive Device Input/Output Power Supply Voltage, 3.3V ±0.165V.

GND - Ground, 0V

MICROPROCESSOR INTERFACE AND CONTROL

CLK I Input Clock. All processing in the ISL5217 occurs on the rising edge of CLK.

RESET

P<15:0> I/O Data bus. Bit 15 is the MSB.

A<6:0> I Address bus. Bit 6 is the MSB.

CS

RDMODE I Read Mode. Read mode selects the Read/Write mode for the Microprocessor Interface. When low the device is

WR

RD

OFFBIN I Offset Binary. When set to 1, the output data bus format is offset binary. When set to 0 the output data bus format

OUTEN<1:0> I Output Three-state Control. OUTEN<1:0> is decoded to provide three-state control of the output data buses. When

TRITST I Tester Three-State Control. This signal determines how the OUTEN<1:0> is decoded to provide the necessary

SERIAL DATA / SYNCHRONIZATION AND FIFO STATUS

SDA, SDB,

SDC, SDD

SCLKA,

SCLKB,

SCLKC,

SCLKD

FSRA,

FSRB,

FSRC,

FSRD

I Reset. (Active Low). Asserting reset will clear all configuration registers to their default values, halting all processing.

I Chip Select. (active low). Enables device to respond to µP access. NOTE: See Appendix A, Errata Sheet.

configured for separate RD

and Data Strobe inputs. Internally pulled down.

I Write Strobe, (active low). Dual function input. The input is configured for Write Strobe when RDMODE is low. When

RDMODE is high the input is configured for Data Strobe.

Write Strobe. The data on P<15:0> is written to the destination selected by A<6:0> on the rising edge of WR

is asserted (low).

CS

Data Strobe. The data on P<15:0> is written to the destination selected by A<6:0> on the rising edge of Data strobe

when RD

RD

I Read Strobe (Active Low). Dual function input. The input is configured for Read Strobe when RDMODE is low.

When RDMODE is high the input is configured for Read/Write

Read Strobe. The data at the address selected by A(6:0) is placed on P<15:0> when RD

CS

Read/Write

is 2’s complement.

TRITST is asserted, the three-state control divides the 80-bit output into eight groups of 10-bits each. When TRITST

is deasserted, the three-state control operates on the 20-bit real and imaginary cascade out data buses.

three-state controls when in normal or tester applications. Set low for normal operation.

I Serial Data A-D. (SDX) Serial Data Input for the I and Q vectors. The processing channel selected for this data will

shift the data in on the rising edge of its serial TX clock. The data vectors are shifted in with the MSB first.

O SERIAL CLK A-D. (SCLKX

the serial data port. When symbol data is input through the µP port the output is SAMPLE CLK 0-3. The polarity of

SCLKX

Serial Clock. Programmable rate clock signal provided to the data source to shift serial data out. Programmed rates

can be CLK/(1-32), or 32x sample clock. See control word 0x17, bit 15 for shut-off conditioning.

SAMPLE CLK. Signal provided to the data source to indicate when data is being transferred from the FIFO to the

shaping filter. The SAMPLE CLK output is generated by the sample rate NCO and has approximately 50% duty

cycle. The sample is taken on the high-to-low transition.

O FRAME STROBE A-D. (FSRX

is FRAME STROBE when symbol data is input through the serial data port. When symbol data is input through the

µP port the output is FIFO READY 0-3. When control word 0x0c, bit 11 is set to one, the setting of the

FSRMode<1:0> bits in indirect address 0x407 determine the output. The polarity of FSRX

FRAME STROBE. Signal provided to the data source to initiate a serial word transfer. Alternatively selectable

through Se r ial Control 0x11, bit 1 4 to be Epoch frame strobe. Epoch is a pre-carry out of the fixed integer divider

instead of the serial frame strobe. The Epoch pre-carry out is six clocks ahead of the true carry out and can be used

to synchronize fixed integer dividers of other devices. See control word 0x17, bit 15 for shut-off conditioning.

FIFO READY. Indicates the I and Q FIFO pointer is less than the programmed FIFO depth.

UPDX

output. When 0x0c, bit 11 is set to one, and FSRMode<1:0> is set to 11, the internal channel TXENX

Table 43 for additional details.

is low and CS is asserted ( l o w ) or read from the address selected by A<6:0> placed on P<15:0> when

is high and CS is asserted (low).

is asserted (low).

Strobe. Determines the type of µP access.

is programmable.

or TXENX: When 0x0c, bit 11 is set to one, and FSRMode<1:0> is set to 10, the internal channel UPDX is

and WR strobe inputs. When high the device is configured for a common Read/Write

when

Strobe.

is asserted (low) and

) Dual function output. The output is SERIAL CLK when symbol data is input through

) Multiple Function Output. When control word 0x0c, bit 11 is set to zero, the output

is programmable.

is output. See

4

FN6004.3

July 8, 2005

Page 5

ISL5217

www.BDTIC.com/Intersil

Pin Descriptions (all signals are active high unless otherwise stated) (Continued)

NAME TYPE DESCRIPTION

TXENA,

TXENB,

TXENC,

TXEND

UPDA, UPDB,

UPDC, UPDD

SYNCO O Synchronization Output. The processing of multiple ISL5217 devices can be synchronized through software by

MODULATED DATA (80)

IOUT(19:0) O Output Data Bus A (19:0). Output bus A contains the digital modulated QUC output samples from Output

QOUT(19:0) O Output Data Bus B (19:0). The output bus contains the digital modulated QUC output samples from Output

IIN(19:0) I/O I Cascade In (19:0) or OUTPUT BUS C. Dual function I/O bus. The bus is configured for input when the output mode

QIN(19:0) I/O Q Cascade in (19:0) or Output Data Bus D. Dual function I/O bus. The bus is configured for input when the output

ISTRB O I data strobe. (active high). Used in the muxed I/Q mode. When asserted, the output data buses contain valid I data.

JTAG TEST ACCESS PORT

TMS I JTAG Test Mode Select. Internally pulled up.

TDI I JTAG Test Data In. Internally pulled up.

TCK I JTAG Tes t Clock.

TRST

TDO O JTAG Test Data Out.

I Transmit Enable A-D. (TXENX

(conditioned by control word 0x0c, bit 2), clear the data RAMs, and update the selected configuration registers upon

assertion. No additional requests for serial data will be made when TXENX

control word 0x0c, bit 3. The polarity of TXENX

with a programmable duty cycle. Two different programmable TXENX

between based on programmed cycle length. See control word 0x0c, bit 11 and Table 43 for additional details.

I Update A-D. (UPDX

the associated update mask bit is set. The polarity of UPDX

connecting the SYNCO of the master ISL5217 device to an UPDX

is programmable.

Summer/Formatter 1. The samples are updated on the rising edge of the CLK. Bit <19> is the MSB.

Summer/Formatter 2. The samples are updated on the rising edge of the CLK. Bit <19> is the MSB.

is cascade in. The bus is configured for output for all other output modes.

I Cascade In. Input bus allows multiple parts to be cascaded by routing the digital modulated signal I CAS OUT,

(Bus A), from one QUC into Output Summer/Formatter 1 of a second QUC. I CAS IN (19:0) is in 2’s complement

format and is sampled on the rising edge of CLK. Bit<19> is the MSB.

Output Data Bus C. The output bus contains the digital modulated QUC output samples from Output

Summer/Formatter 3. The samples are updated on the rising edge of the CLK. Bit <19> is the MSB.

mode is cascade in. The bus is configured for output for all other output modes.

Q Cascade in. Input bus allows multiple parts to be cascaded by routing the digital modulated signal Q CAS OUT,

(Bus B), from one QUC into Output Summer/Formatter 2 of a second QUC. Q CAS IN (19:0) is in 2’s complement

format and is sampled on the rising edge of CLK. Bit<19> is the MSB.

Output Data Bus D. The output bus contains the digital modulated QUC output samples from Output

Summer/Formatter 4. The samples are updated on the rising edge of the CLK. Bit <19> is the MSB.

I JTAG Test Reset (Active Low). Internally pulled-up. This pin should be driven by the JTAG logic to obtain a TAP

controller reset, or if JTAG is not utilized, this pin should be tied to ground for normal operation. As recommended

in the 1149.1 standard documentation the TRST

a known state within the TAP logic on the ISL5217. This avoids potential damage due to signal contention at the

circuit’s inputs and outputs.

) The processing channel selected for this input updates the selected configuration registers, if

) The processing channel selected for this enable will force a channel flush

is deasserted, unless conditioned by

is programmable. Optionally, TXENX can be internally generated

cycles can be programmed and toggled

is programmable.

pin of the ISL5217 slaves. The polarity of SYNCO

test pin should be made active soon after power-up to guarantee

5

FN6004.3

July 8, 2005

Page 6

ISL5217

www.BDTIC.com/Intersil

Functional Description

The ISL5217 Quad Programmable UpConverter (QPUC)

converts digital baseband data into modulated or frequency

translated digital samples. The QPUC can be configured to

create any quadrature amplitude shift-keyed (QASK) data

modulated signal, including QPSK, BPSK, and m-ary QAM.

The QPUC can also be configured to create both shaped

and unfiltered FM signals. A minimum of 16 bits of resolution

is maintained throughout the internal processing.

The QPUC is configured via the microprocessor data bus,

using the A<6:0> address bus, P<15:0> data bus, RD

and CS

control signals. Configuration data that is loaded via

, WR

this bus includes the individual channel’s 48-bit Sample Rate

NCO center frequency, the 32-bit Carrier NCO center

frequency, the device modulation format, gain control, input

mode control, reset control and sync control. The I and Q

baseband channels each have a 256 tap FIR filter whose

coefficients and configuration are also programmed via the

µP interface. Similarly, the control signals for the I and Q

channel interpolation filters are programmed via the µP

interface. Discussion in the following sections utilizes the

register definitions for channel 0. Channels 1-3 are similarly

configured in accordance with the Table 10 Memory Map.

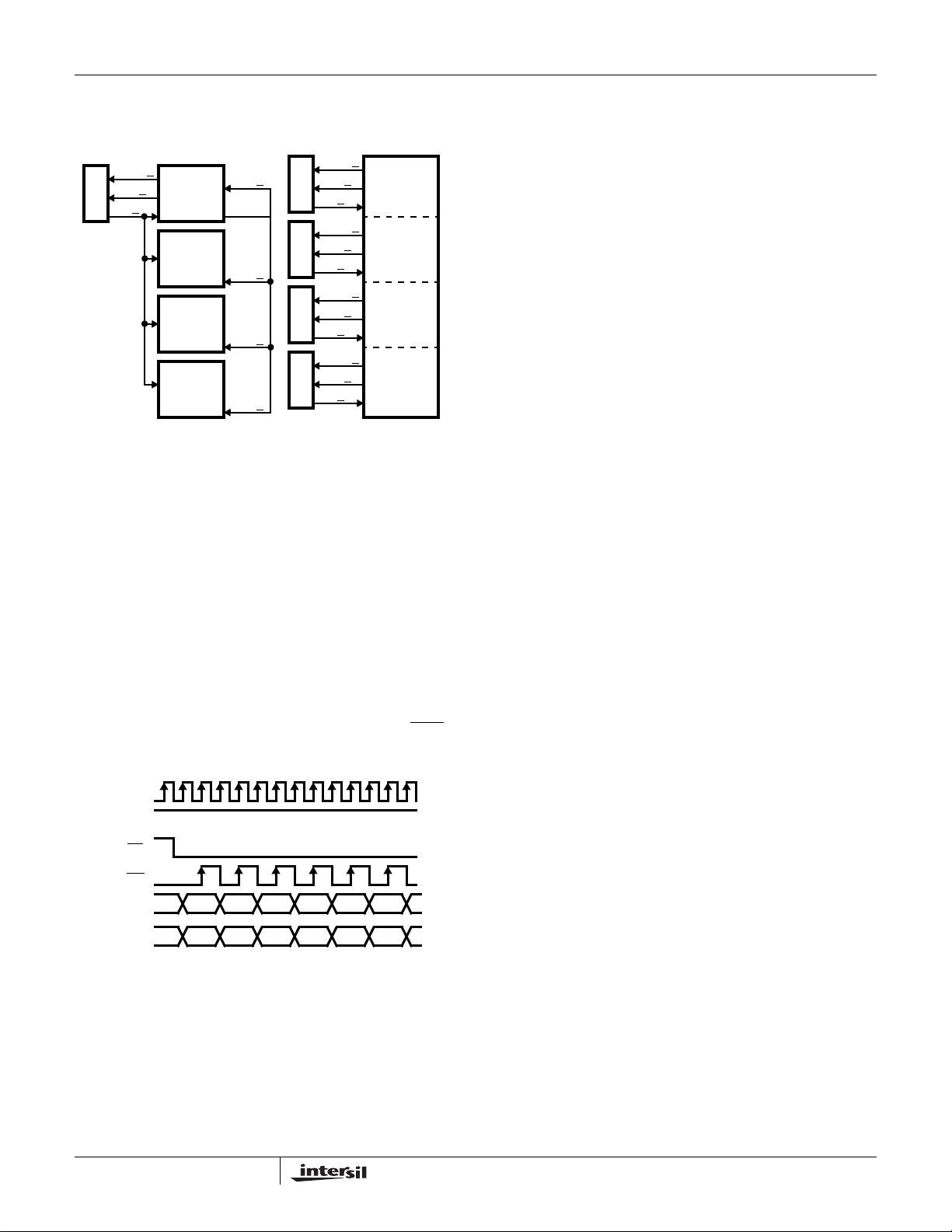

Data Input

The I/Q sample pairs can be input serially through 1 of 4

serial interfaces or in parallel through the µP addressable

registers as shown in Figure 1.

back 16-bit serial transfers can occur by setting control word

(0x17, bits 14:13) both high. The serial process begins with the

first serial clock after the start of a sample clock. The frame

strobe is asserted for one serial clock and starts the I and Q

time slot counters. The TXENX

pin or Main control (0X0c, bit 0)

S/W TX enable must be asserted to enable the frame strobe

out. Additional requests for serial data, with TXENX

deasserted, are controlled by bit 3 of control word 0x0c. The serial

interface may be programmed to be dependent or independent

of TXENX

control. The I and Q time slot counters, programmed

through 0x12, bits 9:0 and 0x13, bits 9:0, control the duration of

the serial to parallel conversion of the serial data input. The

counters are loaded to count the number of serial clocks from

the frame strobe to shift in the last data bit of that sample. The

time slot counters are 10-bits to allow multiple channels to

share a common serial data input. The MSB is always shifted

first, but the order of the I and Q serial data is flexible due to the

variability of the time slot counters. The received serial word is

MSB justified prior to loading into the FIFO holding register

based on the serial word length, programed through Serial

control (0x11, bits 3:2) to 4, 8, 12, or 16 bits.

Although each channel has control of a serial interface it may

select serial data from one of the other interfaces. Serial

control (0x11, bits 1:0) selects 1 of 4 serial data ports for the

channel. The serial data transfer format is shown in Figure 2.

SCLKX

UPDX

0x11, 3:2

SERIAL TO

0x0, 15:0

0x1, 15:0

PARALLEL

0x12, 9:0

0x13, 9:0

PARALLEL

0x11, 15

I sample (15:0)

2:1 MUX

Q sample (15:0)

2:1 MUX

0x11, 1:0

SDA

SDB

SDC

SDD

A<6:0>

P<15:0>

FIGURE 1. SINGLE CHANNEL DATA INPUT PATH

4:1 MUX

CHANNEL

µP INTERFACE

Serial

The serial mode allows the device to shift the I and Q samples

serially into the FIFO holding registers. The serial input format

is selected when Serial control (0x11, bit 15) is high. The serial

interface is three-wire interface controlled by the channel. The

serial clock and frame strobe are driven by the channel to clock

the serial data from the source into the serial data port. The

serial clock can operate at the clock rate, at a divided clock rate,

or be driven at 32x the sample clock rate. Serial control (0x11,

bits 13:8) configure the serial clock. In the 32x mode, back to

TXENX

FSRBX

SDX

INACTIVE

DON’T CARE

FIGURE 2. SERIAL DATA TRANSFER

Q<MSB>

Q<LSB>

I<MSB>

I<LSB>

The ability to select the serial input source allows multiple

QPUCs to share a single microprocessor interface with their

processing synchronized through the master QPUC SYNCO

being tied to the slave device UPDX

. Conversely, multiple

6

FN6004.3

July 8, 2005

Page 7

ISL5217

www.BDTIC.com/Intersil

microprocessors can share a single QPUC as shown in

Figure 3.

ISL5217

QPUC

CHANNEL 0

CHANNEL 1

CHANNEL 2

CHANNEL 3

µP

SCLKX

FSRX

SDX

MASTER

ISL5217

QPUC

SLAVE

ISL5217

QPUC

SLAVE

ISL5217

QPUC

SLAVE

ISL5217

QPUC

FIGURE 3. MULTIPLE CONFIGURATIONS

UPDX

SYNCO

UPDX

UPDX

UPDX

µP

µP

µP

µP

SCLKX

FSRX

SDX

SCLKX

FSRX

SDX

SCLKX

FSRX

SDX

SCLKX

FSRX

SDX

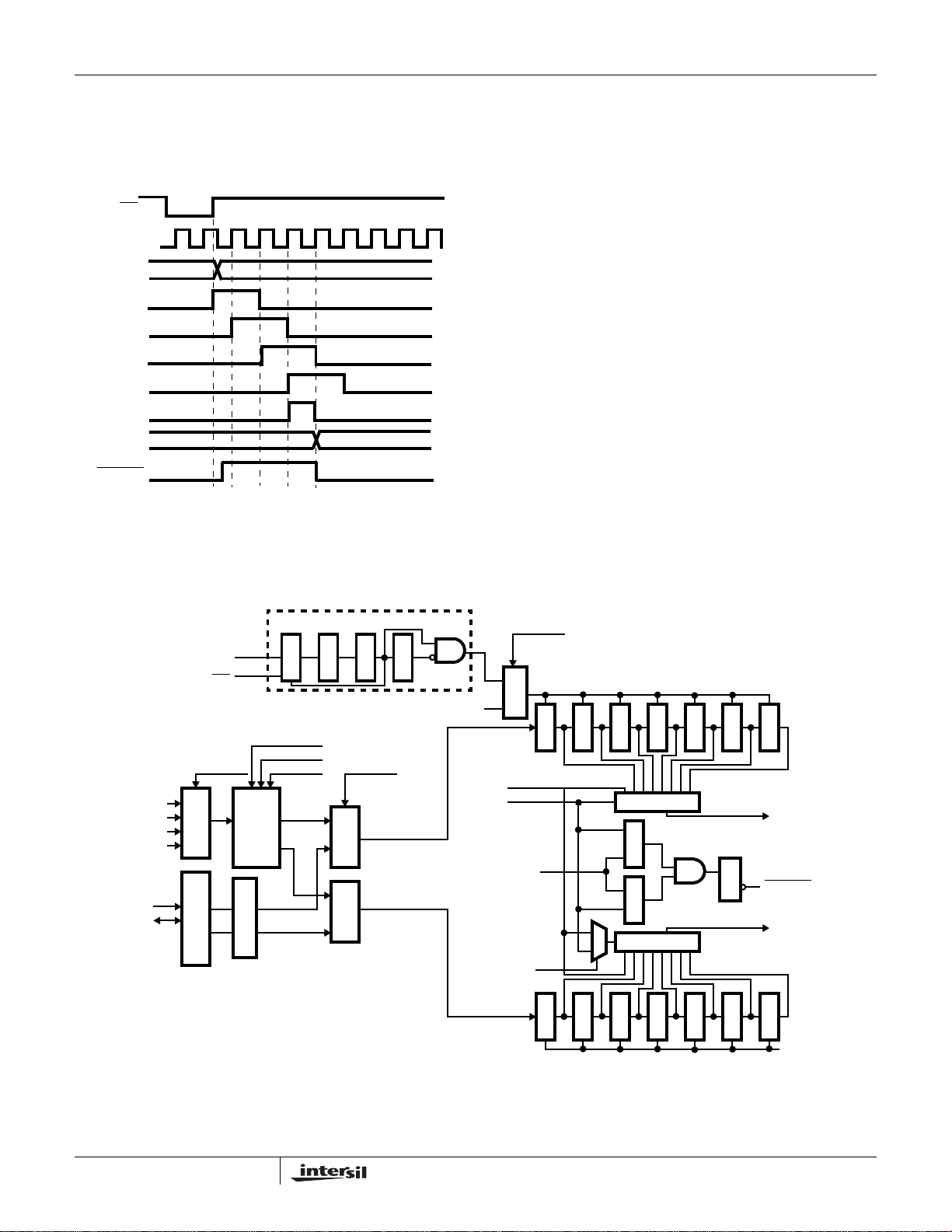

Parallel

The parallel mode allows the µP to write the I and Q

samples directly to the FIFO holding registers. The parallel

input format is selected when Serial control (0x11, bit 15) is

low. The normal µP write order is the Q sample, Control

word 0x1, followed by the I sample, Control word 0x0.

Writing to Control word 0x0 generates the update strobe to

move the data from the FIFO holding register into the first

location of the I/Q FIFO. The first location of the I/Q FIFO is

available for read back. The µP can perform back-to-back

write accesses to Control words 0x1 and 0x0, but must

maintain four f

address. This limits the maximum µP write access rate for

an I/ Q sample pair to 104MHz/4 = 26MHz. The Read/Write

format for a parallel data transfer is shown in Figure 4

CLK

RDMODE

RD

periods between accesses to the same

CLK

The input source to the FIFO is selected by Serial control

(15). The FIFO pointer is incremented every time data is

written into the FIFO. The transferring of data into the FIFO

does not occur until both I and Q have been receiv ed when

the sample data is input in a serial fashion. When the

sample data is input in a parallel f ashion, the transferring of

data into the FIFO occurs when the µP writes to Control

Word 0 (I data).

While the input source determines the write rate, the

shaping filter determines the read rate. The maximum read

rate occurs when the shaping filter constraints for Data

Span (DS) and Interpolation Phases (IP) equal four. For a

clock rate of 104MHz, the maximum read rate is

determined by f

/(DS)(IP), which is 104MHz/16 =

CLK

6.5MHz. See the Shaping Filter Section for more details.

When the Shaping Filter requires another data sample, a

request is made to the FIFO for data and the FIFO pointer

is decremented. Figure 5 indicates the timing of a request

for data from the Shaping filter to the actual appearance of

data at the FIFO output. An “empty” FIFO detection causes

zero valued data to be entered into the shaping filter. The

FIFO can be forced to enter zero v al ued data by setting the

on-line mode to false. The on -line mode is enab led by Main

control (0xc, bit 6). A “full” FIFO detection prevents data

from being pushed out of the FIFO before the filter requests

it. Writing to a full FIFO is treated as an error condition that

will result in a soft reset of the channel to prevent

transmission of erroneous data over the air. The full FIFO

channel reset can be disabled by control word 0x0c, bit 1.

A programmable FIFO depth threshold sets when the

FIFORDY signal is asserted, alerting the data source that

more data is required. The FIFORDY signal assists the

data source in maintaining the desired FIFO data depth.

The data FIFO depth threshold for both I and Q inputs is set

by Main control (0xc, bits 10:8). The SAMPLE CLK may be

used instead of FIFORDY to indicate when data has been

transferred from the FIFO to the shaping filter. See the pin

description table for additional details and Figure 5 for the

input data latency.

WR

A<6:0>

P<15:0>

FIGURE 4. PARALLEL DATA TRANSFER

01

00 01 00

Q I Q I

01 00

Q I

FIFO

The FIFO provides the interface and data storage between

the input source and the shaping filter or FM modulator. The

FIFO can hold up to seven I /Q sample pairs. The block

diagram is shown in Figure 6.

7

FN6004.3

July 8, 2005

Page 8

Data Modulation Path

www.BDTIC.com/Intersil

Three data path options are provided, one for each

modulation format. The modulation format is selected using

FIR Control (0xd, 3:2). The modulation paths are defined in

the following subsections.

ISL5217

WR

CLK

DLY DATA

DFF 1

DFF 2

DFF 3

DFF 4

Write_FIFO

REG1

FIFORDY

FIFO NEEDS

MORE DATA

1234

FIGURE 5. FIFO DATA AND ENABLE TIMING

DFF1 DFF2 DFF3 DFF4

R

>

0X11, 3:2

0X12, 9:0

0X13, 9:0

SERIAL TO

PARALLEL

0X0, 15:0

0X1, 15:0

PARALLEL

E

G

A<6:0>

P<15:0>

SDA

SDB

SDC

SDD

A(000)

WR

0X11, 1:0

4:1 MUX

CHANNEL

ΜP INTERFACE

FIFO NEEDS

MORE DATA

CLOCK SYNCHRONIZATION

R

R

E

G

>

SERIAL_WRITE_TO_FIFO

0X11, 15

2:1 MUX

2:1 MUX

R

E

E

G

G

>

>

I SAMPLE (15:0)

Q SAMPLE (15:0)

0X11, 15

2:1 MUX

ZERO’S

A(2:0)

0XC, 10:8

ALMOST EMPTY

THRESHOLD

FM ENABLED

WRITE_FIFO

R

R

R

E

E

G

G

>

>

0 1

E

G

>

R

E

G

>

8:1 MUX

COMP

COMP

8:1 MUX

R

R

E

G

>

R

E

E

G

G

>

>

IFIFO(15:0)

FIFORDY

DFF

QFIFO(15:0)

R

R

E

E

G

G

>

>

† All Registers are clocked at CLK unless shown otherwise.

FIGURE 6. I AND Q FIFO BLOCK DIAGRAM

8

R

R

E

E

G

G

>

>

R

R

E

G

>

R

E

E

G

G

>

>

WRITE_FIFO

FN6004.3

July 8, 2005

Page 9

ISL5217

www.BDTIC.com/Intersil

Modulation Mode 00 - QASK

This modulation mode configures the QPUC as a BPSK,

QPSK, OQPSK, MSK or m-QAM modulator. The block

diagram is shown in Figure 7. The data FIFO outputs are

routed to the shaping filters. Here the samples are

interpolated by 4, 8, or 16 and shaped using a FIR filter with

up to a 256 taps. The filter impulse response can span 4-16

input samples. A half (input) sample delay can be inserted in

the I/Q path after the FIR and is enabled through Main

Control (0xc, bit 13). Th e 20- bit output of the shaping filter is

routed through a gain adjust multiplier controlled by 0x0a,

bits 11:0 and into the interpolation filter. The interpolation

filter interpolates by a factor set in the resampling NCO with

the Interpolation Phases controlled by 0xd, bits 1:0. The

output of the interpolation filter is at the master clock

frequency , CLK. The samples are then mixed with the carrier

L.O. for quadrature upconversion. The output is then

summed with the cascade input signal, saturated (in the

case of overflow), and formatted for output.

I

SHAPING

Q

FILTER

FIGURE 7. QASK

GAIN

PROFILE

TO

HALFBAND

Modulation Mode 01 - FM with Bandlimiting Filter

This mode configures the QPUC as an FM modulator with

post-modulation filtering. The block diagram is shown in

Figure 8. This mode provides for FSK and FM modulation

schemes. In this mode, the I input samples drive the

frequency control section of a quadrature NCO to produce a

zero IF FM signal. The 16-bit FM quadrature signals are then

routed to the shaping FIR filter and into the interpolation filter

for bandlimiting and interpolation up to the master clock rate.

The quadrature filtered FM signals are then upconverted to

the carrier frequency by the carrier NCO and mixers. The

output is then summed with the cascade input signal,

saturated (in the case of overflow), and f o rmatted for output.

Note that pulse shaping in this mode must be provided prior

to the QPUC.

modulated quadrature samples are then up sampled in the

interpolation filter to the output sample rate. The baseband

modulated signal is then upconverted to the carrier

frequency by the carrier NCO and mixers. The output is then

summed with the cascade input signal, saturated, and

formatted for output.

In Mode 10, the amplitude out of the shaping filter needs to

be limited in order to prevent frequency excursions that

cannot be filtered out in the interpolation filter.

NOTE: THE QUALITY OF THE FM SIGNAL IS AFFECTED BY

THE AMPLITUDE SLEW RATE OUT OF THE SHAPING FILTER.

AS A RULE OF THUMB, LIMITING THIS SLEW RATE TO LESS

THAN 1/8 THE SAMPLE RATE WILL MINIMIZE THIS

DISTORTION.

SHAPING

I

FILTER

FIGURE 9. FM WITH PULSE SHAPING

FM

MODULATOR

GAIN

PROFILE

TO

FM Modulator

The FM modulator provides for frequency modulation of the

carrier center frequency by the QPUC input data. The FM

modulator is driven either directly by the QPUC I input (Mode

01) or by the output of the FIR shaping filter (Mode 10). The

input data to the FM Modulator, is defined as dφ(n)/dt, where

φ(nT) is the phase of a theoretical sinusoid described by:

sn() A (cos φ nT()]+ j sin φ nT()[]); A ≈ 1 in Modulator[=

The block diagram is shown in Figure 10. The input to the

FM modulator, dφ(n)/dt, is integrated via the NCO

accumulator. The NCO accumulator output represents

phase and is used to address a SIN/COS generator,

synthesizing a sinusoid of the form described in

Equation 1. The phase accumulator feedbac k of the NCO is

20 bits and 18 bits of the phase word are routed to the

SIN/COS generator. Eighteen bits of amplitude are

provided on the Sine and Cosine outputs.

20

(EQ. 1)

HALF BAND

I

FM

MODULATOR

FIGURE 8. FM WITH BANDLIMITING

SHAPING

FILTER

Modulation Mode 10 - FM with Pulse Shaping

GAIN

PROFILE

TO

HALF BAND

dφ(nT)/dt

01 OR 10

16 or 20

FM

MODE

FIGURE 10. FM MODULATOR BLOCK DIAGRAM

This mode configures the QPUC as a FM modulator with

pre-modulation baseband pulse shaping. The block diagram

is shown in Figure 9. The data from the FIFO (I channel only)

is routed to the FIR shaping filter. The FIR shaping filter

output drives the frequency control section of a quadrature

NCO to produce a zero IF FM signal. These 18-bit FM

The transfer function of the FM modulator is de fined by the

change in degrees per sample value, dφ(nT)/dt, where

dφ(nT)/dt is a 16-bit, twos complement, fractionally notated

frequency control word with a range from -F

+F

SAMP

/2. F

SAMP

9

φ(nT)

∑

R

E

G

>

ROM

SIN/COS

SAMP

COS[φ(nT)]

18

SIN[φ(nT)]

18

/2 to

is defined as the sample rate into the FM

FN6004.3

July 8, 2005

Page 10

ISL5217

www.BDTIC.com/Intersil

modulator. The maximum phase step that can occur in one

clock is ±180 degrees. Tab le 1 pro v ides the change in phase

weighting of the input bits.

TABLE 1. PHASE WEIGHTING

dφ(nT)/dt DEGREES/SAMPLE

1000 0000 0000 0000 -180

0000 0000 0000 0000 0

0111 1111 1111 1111 ~+180

Shaping Filter

The shaping filter provides the necessary pulse shaping

required on the input data to implement various QASK and

shaped FM modulation formats. Two identical shaping filters

(one each for the I and Q paths) are provided. The shaping

filter architecture uses a NCO controlled interpol ating FIR,

capable of 4, 8, or 16 interpolation phases. The number of

interpolation phases, (IP) is loaded into FIR Control (0xd,

bits 1:0). The span of the impulse response of the polyphase

filter can vary from 4-16 data samples. The desired sample

Data Span, (DS) value minus one is loaded into FIR Control

(0xd, bits 7:4). Thus, the required number of coefficients (or

filter span) becomes:

# Coefficients = (DS)(IP)

The Interpolation Phase also determines the rate to compute

a polyphase output by selecting the appropriate timing from

the Sample Rate NCO to drive the shaping filter at 4x, 8x, or

16x the input sample rate. The Data Span selects the

number of samples to convolve. Each convolution requires

DS reference clocks for each phase of the filter. An output is

calculated (IP) times for each input sample. To allow

sufficient processing time for each output, the reference

clock must be as follows:

CLK DS()IP()f

()≥

S

Conversely, the input sample rate requires:

f

SfCLK

where f

[IP()⁄ DS()]≤

is the frequency of the reference clock, IP is the

CLK

shaping filter interpolate rate; and DS is the number of data

samples in the filter span. For example, if f

CLK

the filter span is 16 samples, and the interpolation rate is 16,

then the maximum input sample rate, f

is 104/256 =

S

406.25kHz. Table 2 shows several examples of calculations

for FIR input sample rates based on master reference clock

rate, number of data samples, and interpolation rate. The

data exits the shaping filters at the interpolated rate.

(EQ. 2)

(EQ. 3)

(EQ. 4)

= 104MHz,

TABLE 2. EXAMPLE CALCULATIONS

EXAMPLE f

1 104MHz 16 16 104/256 = 406.25kHz

2 104MHz 16 8 104/128 = 812.5kHz

3 104MHz 16 4 104/64 = 1.625MHz

4 104MHz 10 4 104/40 = 2.600MHz

5 104MHz 8 4 104/32 = 3.250MHz

6 104MHz 4 4 104/16 = 6.500MHz

CLK

DS IP MAX f

S

The shaping filters have programmable coefficients which

must be loaded via the microprocessor interface. The QPUC

supports loading coefficients for two shaping filters, with FIR

Control (0xd, bit 8) selecting the active filter. The I and Q

shaping filters are identical and may be loaded

simultaneously or separately , allowing f or different gains and

responses through the filter if desired.

TABLE 3. FIR CONTROLS

IP

16 0 128

STARTING ADDRESS

W/FIR CONTROL (8) = ‘0’

40 8

80 8

STARTING ADDRESS

W/FIR CONTROL (8) = ‘1’

Because 16 interpolation phases are possible, the

coefficients are structured in sets of 16, one set for each

phase of the shaping filter. The convolution algorithm

sequentially steps through each of these phases, beginning

with phase 0. The coefficients for the shaping filters are

generated by designing the prototype filter at the

interpolated rate. The coefficients are then divided into

interpolation phases by taking every n

th

tap of the prototype

filter and storing the coefficient as an element of a coefficient

set. The IP value determines the addressing interval through

the prototype filter to create the coefficient sets for the filter

phases. The first coefficient set begins at address 0. The

next coefficient set begins at address 1 and continues in a

like manner for the remaining coefficient sets. For a 16 tap,

interpolate-by-4 filter, the calculations for filter 1 are:

Polyphase output 0 = (C0*D[n]) + (C4*D[n-1]) + (C8*D[n-2])

+ (C12*D[n-3])

Polyphase output 1 = (C1*D[n]) + (C5*D[n-1]) + (C9*D[n-2])

+ (C13*D[n-3])

Polyphase output 2 = (C2*D[n]) + (C6*D[n-1]) + (C10*D[n-2])

+ (C14*D[n-3])

Polyphase output 3 = (C3*D[n]) + (C7*D[n-1]) + (C11*D[n-2])

+ (C15*D[n-3])

If FIR Control (8) is set the calculations for filter 2 are:

Polyphase output 0 = (D0*D[n]) + (D4*D[n-1]) + (D8*D[n-2])

+ (D12*D[n-3])

10

FN6004.3

July 8, 2005

Page 11

ISL5217

www.BDTIC.com/Intersil

Polyphase output 1 = (D1*D[n]) + (D5*D[n-1]) + (D9*D[n-2])

+ (D13*D[n-3])

Polyphase output 2 = (D2*D[n]) + (D6*D[n-1]) + (D10*D[n-2])

+ (D14*D[n-3])

Polyphase output 3 = (D3*D[n]) + (D7*D[n-1]) + (D11*D[n-2])

+ (D15*D[n-3])

Table 4 details the coefficient address allocation for the

previous example. The interpolation phase is on the left and

the data span is across the top. The coefficient RAM address

followed by the coefficient term is listed in the table’s cell.

Table 49 details the coefficient address locations through

255.

TABLE 4. ADDRESS ALLOCATION

DS [n] DS [n-1] DS [n-2] DS [n-3]

IP0

IP1

IP2

IP3

IP4

IP5

IP6

IP7

IP8

IP9

IP10

IP11

IP12

IP13

IP14

IP15

0 CO 16C4 32C8 48C12 •

1 C1 17C5 33C9 49C13 •

2 C2 18C6 34C10 50C14 •

3 C3 19C7 35C11 51C15 •

4203652•

5213753•

6223854•

7233955•

8 D0 24D4 40D8 56D12 •

9 D1 25D5 41D9 57D13 •

10 D2 26 D6 42 D10 58 D14 •

11 D3 27 D7 43 D11 59 D15 •

12 28 44 60 •

13 29 45 61 •

14 30 46 62 •

15 31 47 63 •

The gain through the filter is:

A = (sum of coefficients) / interpolation rate.

The shaping filter contains saturation logic in the event that

the final output peaks over +/- 1.0. When using quadrature

modulation, saturation/overflow can occur when the input

values for I and Q exceed 0.707 peak. The shaping filter

coefficients may need to be reduced from full scale to

prevent saturation.

Gain Profile

The overall channel gain is controlled by both a gain profile

stage and a gain control stage, which provide identical scaling

for the I and Q upconverted data. The gain profile stage allows

transmit ramp-up and quench fading, to control the sidelobe

profile in burst mode. This is implemented through user control

of the rise and fall transitions utilizing a gain profile memory.

The gain profile memory is a 128 x 12 bit RAM which is loaded

with the desired scaling coefficients via indirect addressing of

memory spaces 0x000-0x07f. The pulse shaping is

implemented by linearly multiplying the programmed coefficient

by the shaping filter outputs at the f

The gain profile is enabled by FIR control (0xd, bit 15), with the

RAM address pointer being reset to zero on assertion of the

gain profile enable. Control of the pulse shaping is based on

TXENX

, as the TXENX rising edge causes the RAM pointer to

begin stepping through the profile until the RAM pointer

matches the Gain profile length programed into control word

(0x0b, bits 6:0). The falling edge of TXENX

process and the RAM pointer begins decrementing until it

reaches zero. The gain process is symmetric with respect to the

rising or falling edges of TXENX

profile block is set by control word (0x0b, bits 8:7) where bit 8

bypasses all latency alignment circuitry and uses TXENX

input to the channel. Setting control word (0x0b, bit 7) remov es

two edge latencies from the delay path and should be

combined with selection of DS = 3, IP = 4 in order to have

perfect symmetry through the gain profile block. The memory

coefficients may be loaded without taking the channel off-line.

This is implemented by setting the gain profile hold bit in control

word (0x0c, bit 14) which holds the last gain value and provides

access to the memory.

*IP, or coarse phase rate.

S

reverses the

. The latency through the gain

as

The loading options are programmable including read back

modes and are discussed in detail in the ‘Microprocessor

Interface’ section. Both 16-bit 2’s complement and 24-bit

floating point format are allowed. The 2’s complement

coefficient format of valid digital values ranges from 0x8001

to 0x7FFF. The value 8000 is not allowed. The 24-bit floating

point (20-bit mantissa with 4-bit exponent) mode allows an

exponent range from 0 to 15. An exponent of 0 indicates

multiplication of the coefficient by 2

-1

2

, down to a value of 15 being 2

complement, with 24-bit floating point mode enabled by

setting control word (0x17, bit 12).

0

, and an exponent of 1 is

-15

. The default mode is 2’s

11

The gain profile coefficients are programmed as unsigned

values:

Bit weight 2

Maximum 0x800 = 1.0

0x001 = 2

Minimum 0x000 = 0.0

0.2-1 2-2

... 2

-11

-11

FN6004.3

July 8, 2005

Page 12

ISL5217

www.BDTIC.com/Intersil

Gain Control

The gain control is implemented through a scaling multiplier

followed by a scaling shift. The combination of the multiplier

and shifter provide the final output gain of the channel. Gain

adjustmen t can vary from -0.0026 to -144 dBFS.

Given a desired attenuation, the scaling multiplier value,

Gain

Gain

where INT[X] is the integer part of the real number X.

Table 5 details a few scaling multiplier values and their

associated attenuations.

Given a desired attenuation, the shifting value Gain

(2:0) can be determined by a table look-up. Refer to Table 6.

GAIN

The gain control is loaded into Control Word 0xa.

0xa, bits 14:12 = Gain

0xa, bits 11:0 = Gain

(11:0) can be calculated by the following equati o n.

MULT

(11:0) = INT [10

MULT

TABLE 5. SCALING GAIN ATTENUATION

GAIN

MULT

(0xa, 11:0) GAIN (dBFS)

1111 1111 1111 -0.0026 99.97

1000 0000 0000 -6.021 50.0

0100 0000 0000 -12.041 25.0

0010 0000 0000 -18.062 12.5

0001 0000 0000 -24.082 6.25

0000 1000 0000 -30.103 3.125

0000 0100 0000 -36.124 1.5625

0000 0010 0000 -42.144 0.78125

0000 0001 0000 -48.165 0.39062

0000 0000 1000 -54.186 0.19531

0000 0000 0100 -60.205 0.097656

0000 0000 0010 -66.226 0.04828

0000 0000 0001 -72.247 0.02441

TABLE 6. GAIN SHIFT VALUES

SHIFT

(2:0) GAIN (dBFS)

000 -72.247 4096 0.02441

001 -48.165 256 0.39062

010 -30.103 32 3.125

011 -24.082 16 6.25

100 -18.062 8 12.5

101 -12.041 4 25.0

110 -6.021 2 50.0

111 0 1 100.0

|(Gain(db)| / 20 )212

SCALE BYSCALING GAIN

(2:0)

SHIFT

(11:0)

MULT

]

SCALING GAIN

(V

OUT/VIN

SHIFT

(V

OUT/VIN

)%

)%

Sampling NCO

The Sample Rate NCO provides the SAMPLE CLK and

sample clock phase information to the data input FIFO’s,

the shaping filters and the interpolation filters. The input

sample rate is set by the sample cloc k. The sample cl ock is

the MSB of the NCO accumulator and controls the

movement of sample data from the user to the shaping

filters. The coarse phase of the NCO accumulator controls

the processing of the shaping filter at 4x, 8x, or 16x the

sample clock rate. The fine phase of the NCO accumulator

controls the processing of the interpolation filter as it resamples the data from the shaping filter to the clock rate.

The block diagram is shown in Figure 11.

The sample frequency, SF, is set with 48-bit resolution. The

LSB is f

bits. Given a desired sample frequency, f

SF(47:0) can be calculated by the following equation.

SF (47:0) = INT [(f

The sample frequency, SF(47:0) is loaded 16 bits at a time

into Control Words 4, 5, and 6.

0x4, bits 15:0 = SF (47:32)

0x5, bits 15:0 = SF (31:16)

0x6, bits 15:0 = SF (15:0)

The output of the phase accumulator can be offset by phase

increments of 90 degrees without affecting the operation of

the phase accumulator. The desired offset increment is

loaded into FIR Control (0xd, bits 11:10).

Since it is not possible to represent all frequencies exactly

with an NCO, the phase accumulator length has been

extended to minimize the effect of phase error accumulation.

At an update rate of 1MHz, half an LSB of error in loading

the 48-bit accumulator is 1.8e-9. The accumulated phase

error after 1 year is 0.056 of a bit.

Leap Counter

In addition to lengthening the NCO accumulator, a 32-bit

counter is available for realizing fixed integer interpolation

rates. The carry-out of the fixed integer counter can be used

to clear the coarse and/or fine phase of the sample rate

NCO. The fixed integer counter also provides a precarry-out

that can be used to synchronize fixed integer counters in

other devices. The fixed integer counter is enabled by FIR

Control (0xd, bit 12).

In programming the FID to clear the NCO accumulator ,

consideration must be provided to ensure that FID is

programmed to clear the Error term only when the desired

error term should have been zero with an integer multiple of

the symbol rate. Selecting GSM as an example, the FID

should clear the NCO accumulator every third multiple of the

symbol rate or every 270833.333 * 3 sample clocks, as the

error term should only be zeroed during integer multiples of

/248. The internal accumulator resolution is 48

CLK

) * 2

48

]

/ f

s

CLK

the value f or

s,

12

FN6004.3

July 8, 2005

Page 13

ISL5217

www.BDTIC.com/Intersil

the symbol rate. This would clear the NCO accumulator

every 3 seconds or at a 1/3 Hz rate. The frequency of the

FID carryout can range from Fclk to Fclk/2^32. The value of

FID is determined from:

FID (31:0) = [(fclk / fco)]

Where fco is the desired frequency of the carryout, which in

the previous example is 1/3 Hz and the fclk is and integer

multiple of the sample frequency, say 65MHz. The resultant

value for the FID would be (65MHz/1/3Hz) or 195e6. The

programmed integer values for the FID are loaded 16 bits at

a time into Control Words 2 and 3.

0x2, bits 15:0 = FID (31:16)

0x3, bits 15:0 = FID (15:0)

Loading 195e6 into the FID would result in 0x2, being

0x0b9f, and 0x3 being 0x76c0.

SAMPLE FREQUENCY

ZERO

SYNCSEL

SYNCIN

MUX

WR CW3

WR CW21

RST

IP(1:0)

0 1

START

EDGE

GEN

R

E

G

>

R

E

G

>

RESET

EDGE

GEN

† ALL REGISTERS ARE

CLOCKED AT CLK

FIGURE 11. RE-SAMPLING NCO BLOCK DIAGRAM

2

EN

>

REG

SHIFTER

>

46

REG <

∑

REG

12

4, 3, OR 2

ACC

EnNCO

(CARRIER NCO)

48

SAMPCK

(MSB)

FINE

PHASE

COARSE

PHASE

The output of this filter is rounded to 20-bits. The output is

checked for saturation and limited if necessary. The data

exits the halfband filter as a parallel I<20:0> and Q<20:0>

data stream at the rate of fs*IP*2. Figure 12 shows the

frequency response of the Half-Band filter.

Interpolation Filter

The shaped sample data is input to the interpolating filter at

the interpolation rate. The Interpolator filter resamples the

shaped I and Q data to establish the final output sample rate

of the channel. The output sample rate is always the clock

rate. The Interpolator uses the fine phase values from the

Symbol Rate NCO to compute the fine interpolated samples

at the clock rate. The number of interpolated samples is set

by the following ratio: n

The nulls in the interpolation filter frequency response align

with the interpolation images of the shaping filter. The

impulse response of the Interpolation filter is shown in

Figures 13A through 13C for varying interpolation ratios.

0

-20

-40

-60

-80

MAGNITUDE (dB)

-100

-120

-140

0 0.1 0.2 0.3 0.4 0. 5 0.6 0.7 0.8 0. 9 1

NORMALIZED FREQUENCY (NYQUIST=1)

FIGURE 12. HALF BAND FILTER RESPONSE

0

INTERPOLATION FILTER RESPONSE

-20

-40

-60

MAGNITUDE (dB)

-80

= f

CLK

/ f S / IP.

IS

Fixed Coefficient 11-TAP Interpolating

-100

Half-band

Following the post-FIR gain profile block is a fixed coefficient

11-tap interpolate by 2 Half-Band filter. The default mode is

to bypass the filter with the setting of control word 0x0d, bit 9

enabling the filter. If bypassed, the data to the filter is zeroed

which reduces power consumption. The halfband filter

coefficients are:

3, 0, -25, 0, 150, 256, 150, 0, -25, 0, 3

13

-120

FIGURE 13A. INTERPOLA TION FIL TER IMPULSE RESPONSE

512 1024 1536 2048 2560 3072 3584 4096

SAMPLE TIMES

L = 16; FOUT = 4096

FN6004.3

July 8, 2005

Page 14

ISL5217

www.BDTIC.com/Intersil

0

-20

-40

-60

-80

MAGNITUDE (dB)

-100

-120

FIGURE 13B. INTERPOLA TION FILTER IMPULSE RESPONSE

-0.05

-0.1

-0.15

-0.2

-0.25

-0.3

-0.35

-0.4

-0.45

MAGNITUDE (dB)

-0.5

-0.55

-0.6

-0.65

-0.7

FIGURE 13C. INTERPOLA TION FILTER IMPULSE RESPONSE

64 128 192 256

L = 16; FOUT = 4096

0

INTERPOLATION FILTER RESPONSE

8 16243240485664

L = 16; FOUT = 4096

INTERPOLATION FILTER RESPONSE

320 384 448 512

SAMPLE TIMES

SAMPLE TIMES

Carrier NCO

Following the interpolating filter section, the samples are

modulated onto a carrier signal via a complex multiply

operation. The Carrier NCO provides the quadrature local

oscillator references to the complex mixer.

The NCO has provisions for programming the frequency and

phase offset. The NCO has a 32 bit frequency control

providing sub-hertz resolution at the maximum clock rate.

The carrier NCO phase accumulator feedback can be preset

to synchronize multiple channels. The carrier NCO has a

32-bit 2’s complement programmable frequency increment

value which can range from -2

range of -f

CLK

/2 to ~f

CLK

frequency will range from -52MHz to +52MHz.

The maximum error is 104MHz/(2

carrier frequency can be calculated from the value loaded

into Control Address 0x8 and 0x9 by:

F

CARRIER

CR 31:0()f

31

to ~231 for a NCO output

/2. For f

CLK

= 104MHz, the

CLK

32

) = 0.0242Hz. The

32–

2

××=

(EQ. 5)

where CR(31:0) is the 32-bit frequency control word which

CLK

31

to ~231 for a NCO output range of

/2. f

is the CLK frequency.

CLK

can range from -2

-f

/2 to ~f

CLK

This NCO frequency range allows for spectral inversion.

Given a desired carrier frequency, the value for CR(31:0)

loaded into the part can be calculated by:

CR 31:0()INT F

⁄ *232][=

CfCLK

(EQ. 6)

where INT[X] is the integer part of the real number X.

The vector rotation can also be controlled by the sign of the

CF value. When CF is a positive value a counterclockwise

vector rotation is produced. When CF is a negative value a

clockwise vector rotation is produced.

The carrier frequency is loaded 16 bits at a time into Control

Words 8 and 9.

0x8, bits 15:0 = CF (31:16)

0x9, bits 15:0 = CF (15:0)

The 16-bit carrier phase offset initializes the most-significant

16-bits of the phase accumulator. The least significant 16

bits of the phase accumulator are cleared. Given a desired

carrier phase offset, the value CO(31:0) can be calculated by

the following equation.

CO 31:0()INT

PhaseOffset()°

---------------------------------------------

360°

*2

32

]=

(EQ. 7)

The carrier phase offset is loaded into Control Word 0x7.

Control Word 7 (15:0) = CO (31:16).

Complex Mixer

The complex mixer m ultiplies the sin/cos terms generated by

the carrier NCO sin/cos generator with the I and Q

interpolated sample data. The mixers can be bypassed by

programming the carrier frequency to zero. This action sets

the sin/cos terms generated by the carrier NCO to 0 and 1

respectively. The block diagram of the Car rier NCO/Comple x

Mixer is shown in Figure 14.

I(20:0)

+

∑

-

+

∑

+

Re (20:0)

Im (20:0)

SIN

SIN

19

19

19

19

COS

Q(20:0)

EN OUT

Q(20:0)

COS

I(20:0)

EN OUT

FIGURE 14. VECTOR MODULATOR/MIXER BLOCK DIAGRAM

14

FN6004.3

July 8, 2005

Page 15

ISL5217

www.BDTIC.com/Intersil

The resulting complex output is given by the following

equations.

Re mixer (20:0) = I(20:0) * cos(18:0) - Q(20:0) * sin(18:0)

Im mixer (20:0) = Q(20:0) * cos(18:0) + I(20:0) * sin(18:0)

(Vector weighting for block diagram)

1

I (20:0) = 2

Q (20:0) = 21... 2

sin (18:0) = 20... 2

cos (18:0) = 20... 2

Re mixer(20:0) = 21... 2

Im mixer(20:0) = 21 ... 2

.. 2

-19

-19

-18

-18

-19

-19

Output Processing

Output processing sums the modulated output of each

channel to provide multi-carrier outputs. There are four

4-channel summers, which combined with the outputs IOUT,

QOUT, and bidire ctional outputs IIN and QIN can be

configured by the user to support eight output modes. The

output mode is determined by Device Control 0x78 bits 9:8

and Main Control 0xc, bit 7.

Output Modes

Cascade Mode: In this mode IIN<19:0> and QIN<19:0> are

configured as inputs for the real and imaginary cascade

inputs. This is the only mode where IIN and QIN are

configured as inputs.

The cascade input allows for more than four multi-channel

transmissions by summing the complex modulated signals

from other device’s with the four channel summer . A cascade

chain of four devices allows up to sixteen carriers. Each

device delays it’s 4-channel summation to align with the

cascade in from the previous device. Device Control 0x78

bits 2:1, Cascade delay <1:0>, identifies the position in the

cascade chain to select the appropriate delay. Device

Control 0x78, bit 3, Cascade input enable, zeroes the

cascade-in data when the port is not in use. The output of

the summation is saturated to prevent roll-over.

Real: Real data is output on IIN, QIN, IOUT, and QOUT.

Imag: Imaginary data is output on IIN, QIN, IOUT, and

QOUT.

Muxed I/Q: The output data alternates between real and

imaginary on clock time boundaries. The output signal

ISTRB is asserted when the output data is real. The ISTRB

is enabled by Device Control 0x78, bit 5. In this mode, the

I/Q samples are decimated by two. This is the only mode in

which the output data is decimated.

NOTE: When in Muxed I/Q mode the output order is I then

Q.

Muxed I/Q at 2x rate: The output data alternates between

real and imaginary within a clock time boundary. The output

data is real when the clock is high, and imaginary when the

clock is low. All I/Q samples are output, and there is no

decimation of the output stream. Care should be utilized to

ensure sufficient set-up time is achieved for the downstream

device in the application, as data is alternating I then Q

between clock boundaries.

Complex out 1: In this mode, complex data is output on IIN

and QIN, while real data is output on IOUT and QOUT.

Complex out 2: In this mode, real data is output on IIN and

QIN, while complex data is output on IOUT and QOUT.

Complex out 3: In this mode, complex data is output on IIN

and QIN and complex data is output on IOUT and QOUT.

TABLE 7. OUTPUT MODES

MAIN

CONTROL

0X0C, BIT 7

COMPLEX

OUTPUT

OUTPUT MODE

Cascade Mode 0 00 0 X X Input re Input im re CASout im CASout

Real 0 01 0 X X re SUM1 re SUM2 re SUM3 re SUM4

Imaginary 0 10 0 X X im SUM1 im SUM2 im SUM3 im SUM4

Muxed I/Q 0 11 0 1 X re SUM1 re SUM2 re SUM3 re SUM4

Muxed I/Q at 2X Rate 0 01 1 X 1 re SUM1 re SUM2 re SUM3 re SUM4

Complex Output Mode 1 1 (Ch. 0 only) 01 0 X X re SUM1 im SUM1 re SUM3 re SUM4

Complex Output Mode 2 1 (Ch. 2 only) 01 0 X X re SUM1 re SUM2 re SUM3 im SUM3

Complex Output Mode 3 1 (Ch. 0 and 2) 01 0 X X re SUM1 im SUM1 re SUM3 im SUM3

NOTE: re CASout is re SUM1 + re CASinput, im CASout is im SUM1 + im CAS in.

MODE

0 11 0 0 X im SUM1 im SUM2 im SUM3 im SUM4

0 01 1 X 0 im SUM1 im SUM2 im SUM3 im SUM4

15

MAIN

CONTROL

0X78, BITS 9:8

OUTPUT

MODE

MAIN

CONTROL

0X78, BIT 10

OUTPUT 2X

SELECT ISTRB CLK IIN<19:0> QIN<19:0> IOUT<19:0> QOUT<19:0>

July 8, 2005

FN6004.3

Page 16

TABLE 8. INPUT/OUTPUT MODES

www.BDTIC.com/Intersil

MAIN CONTROL 0X78, BITS

9:8 OUTPUT MODE

00 00 Input Input Output Output

00 01 Input Input Output HI-Z

00 10 Input Input HI-Z Output

00 11 Input Input HI-Z HI-Z

01,10,11 00 Output Output Output Output

01,10,11 01 Output Input Output HI-Z

01,10,11 10 Input Output HI-Z Output

01,10,11 11 Input Input HI-Z HI-Z

OUTEN

<1:0>

IIN

<19:0>

4-Channel Summers

Cascade Input

When in the complex cascade mode the 4-channel summer

re 1 and im 1 are summed with the real and imaginary

cascade inputs. The cascade input allows for more than four

multi-channel transmissions by summing the complex

modulated signals from other device’s. A cascade chain of

four devices allows up to sixteen carriers. Figure 15

illustrates cascading multiple devices. Each device delays it’ s

4-channel summation to align with the cascade in from the

previous device. Device Control 0x78, bits 2:1 identifies the

position in the cascade chain. Device Control 0x78, bit 3

zeroes the cascade-in data when the port is not in use. The

output of the summation is saturated to prevent roll-over.

µP

µP

µP

µP

SCLKX

FSRX

SDX

SCLKX

FSRX

SDX

SCLKX

FSRX

SDX

SCLKX

FSRX

SDX

MASTER

ISL5217

QPUC

SLAVE

ISL5217

QPUC

SLAVE

ISL5217

QPUC

SLAVE

ISL5217

QPUC

I OUT <19:0>

Q OUT <19:0>

SYNCO

UPDX

Q IN <19:0>

I IN <19:0>

I OUT <19:0>

Q OUT <19:0>

UPDX

Q IN <19:0>

I IN <19:0>

I OUT <19:0>

Q OUT <19:0>

UPDX

Q IN <19:0>

I IN <19:0>

I OUT <19:0>

Q OUT <19:0>

ISL5217

<19:0>

I IN<19:0>

CASZ

MOD(20:0)

QIN

20

IOUT

<19:0>

R

22

E

G

>

21

R

E

G

>

∑

SATURATE

CIRCUITRY

QOUT

<19:0>

20

I OUT<19:0>

† ALL REGISTERS ARE CLOCKED AT CLK

FIGURE 16. CASCADE INPUT BLOCK DIAGRAM

Output Formatter

The output can be formatted in either twos complement or

offset binary. The OFFBIN pin is used to select the output

format. The output ranges from 0x8001 to 0x7FFF for two’s

complement and from 0x0001 - 0xFFFF for offset binary.

Microprocessor Interface

NOTE: See Appendix A, Errata Sheet

The microprocessor interface allows the QPUC to appear as

a memory mapped peripheral to the µP. Configuration data,

I/Q sample data and RAM data can be accessed through

this interface. The interface consists of a 16 bit bidirectional

data bus, P<15:0>, seven bit address bus, A<6:0>, a write

strobe (WR

Two µP interface modes are supported through the input pin

RDMODE

read and write strobe inputs. When high the device is

configured for a common Read/Write

This mode redefines RD

into Data Strobe.

), a read strobe (RD) and a chip enable (CE).

. When low the device is configured for separate

and data strobe inputs.

into Read/Write Strobe and WR

FIGURE 15. CASCADED QPUCs

The address space is partitioned into five directly accessible

regions, one for top control and one for each of the four

channels. The Device Control space allows for configuration

parameters that effect the entire device, cascade, output

modes, and routing. The channel space allows for

configuration parameters and sample data.

The master registers for the configuration data and I/Q

sample data are located in these areas. There is a master

16

FN6004.3

July 8, 2005

Page 17

ISL5217

www.BDTIC.com/Intersil

register and slave register pair for each configuration

parameter and I/Q sample. The slave register for the I/Q

samples is the first location of the FIFO. The master

registers are clocked by the µP write strobe, are writable and

cleared by a hard reset. The slave registers are clocked by

device clock, are readable and cleared by either a hard or

soft reset. The transfer of configuration data from the master

register to the slave register can occur synchronously after

an event or immediately after a four clock synchronization

period.

Indirect addressing is used to access the gain profile RAM,

the I coefficients RAM and the Q coefficients RAM. This type

of access relies on loading the RAM data into direct address

0x14 and the RAM address into direct address 0x15. After a

four clock synchronization period of the decoded address

0x15, the contents of the RAM data register is moved to the

address pointed to by the RAM address register. The µP can

perform back-to-back accesses to the RAM data register and

RAM address register, but must maintain four f

between accesses to the same address. This limits the

maximum µP access rate for the RAM to

104MHz/4 = 26MHz. The RAM address register defines a

16-bit address space that is partitioned into pages of 256

words by indirect address <9:8>. Indirect address<15>

determines the access type, 1 = read; 0 = write.

The address map and bit field details for the microprocessor

interface is shown in the Tables 10-47. The procedures for

reading and writing to this interface are provided below.

CLK

periods

Microprocessor Read/Write Procedure

The QPUC offers the microprocessor read/write access to all

of the configuration working registers, the gain profile RAM,

the I coefficients RAM and the Q coefficients RAM.

RDMODE determines the read/write mode for the

microprocessor interface as detailed in the pin description

table. The following e xamples hav e RDMODE set low, which

configures the interface for separate RD

and WR strobes.

Configuration Read/Write Procedure

Write Access to the Configuration Master

Registers

Perform a direct write to the configuration master registers

by setting up the address A<6:0>, data P<15:0>, and

generating WR

sequence is as shown. The order of writing to the de vice

should be maintained as:

strobe. The overal l con figur ation loa ding

5. Repeat steps 2-4 for all channels.

6. Write control word 0x0c to the final configuration values.

RDMODE

RD

WR

A<6:0> 0xc

P<15:0>

FIGURE 17. CONFIGURATION WRITE TRANSFER

0x78 0x2 0x3

9000

0x4 0x5

Read Access to the Configuration Slave Registers

1. Perform a direct read of a configuration register by

dropping the RD

selected by A<6:0> onto the data bus P<15:0>.

RDMODE

RD

WR

A<6:0>

P<15:0>

FIGURE 18. CONFIGURATION READ TRANSFER

line low to transfer data from the register

0XC 0X78 0X2 0X3 0X4 0X5

HI-Z

DATA VALID

I/Q Sample Read/Write Procedure

Write Access to the I/Q Sample Master Registers

2. Enable the parallel input format by clearing bit 15 of the

Serial control register, 0x11.

3. Perform a direct write to Control word 1 by setting up th e

address A<6:0>, data P<15:0>, and generating a rising

edge on WR.

4. Perform a direct write to Control word 0 by setting up th e

address A<6:0>, data P<15:0>, and generating a rising

edge on WR.

I/Q master registers to the first location of the FIFO.

5. Wait 4 clock cycles before performing the next write to the

Q data master register.

Read Access to the I/Q Sample Slave Registers

1. Perform a direct read of the I slave register by dropping

the RD

selected by A<6:0> onto the data bus P<15:0>.

A write strobe transfers the contents of the

line low to transfer data from the slave register

1. Write the Main Control register 0x0c. 0x9000 sets the

immediate update and microprocessor hold bits.

2. Write Device Control 0x78, bit 0 to set the broadcast bit if

writing to multiple channels. Set to 0 when writing to a

single channel.

3. Write all remaining registers sequentially .

4. Load all filter and gain coefficients.

17

FN6004.3

July 8, 2005

Page 18

ISL5217

www.BDTIC.com/Intersil

Gain Profile RAM Read/Write Procedure

Write Access to the Gain Profile RAM

1. Enable the gain profile hold mode by setting bit 14 of the

Main Control register 0x0c.

2. Load the RAM data to location 0x14.

3. Load the RAM write address to location 0x15. A write

strobe transfers the contents of the register at location

0x14 into the RAM location specified by the contents of

the register at location 0x15. (Indirect address[15] =0).

4. Wait 4 clock cycles bef ore performing the next write to the

RAM data register.

5. Repeat steps 2-4.

6. Return gain control back to the channel by disabling the

gain profile hold 0x0c, bit 14.

Read Access to the Gain Profile

1. Enable the gain profile hold mode by setting bit 14 of the

Main Control register 0x0c.

2. Load the RAM read address and 0x8000 to location 0x15.

A read strobe transfers the contents of the RAM location

specified by the contents of the register at location 0x15

onto the read bus. (Indirect address[15] =1, Indirect

address[9:8] =’00’).

3. Wait 4 clock cycles bef ore performing the next write to the

RAM address register.

4. Repeat steps 2-3.

5. Return gain control back to the channel by disabling the

gain profile hold 0x0c, bit 14.

Write Access to the Coefficient RAMs When I

Equal Q

1. Enable the µP hold mode by setting bit 12 of the Main

Control register 0x0c.

2. Load the RAM data to location 0x14 with the coefficient.

3. Load the RAM write address to location 0x15. A write

strobe transfers the contents of the register at location

0x14 into the RAM location specified by the contents of

the register at location 0x15. (Indirect address[15] =0,

Indirect address[9:8] =’11’).

4. Wait 4 clock cycles before performing the next write to the

RAM data register.

5. Repeat steps 2-4.

6. Return RAM control back to the channel by disabling the

µP hold mode.

Read Access to the I Coefficient RAM

1. Enable the µP hold mode by setting bit 12 of the Main

Control register 0x0c.

2. Load the RAM read address and 0x8100 to location 0x15.

A read strobe transfers the contents of the RAM location

specified by the contents of the register at location 0x15

onto the read bus. (Indirect address[15] =1, Indirect

address[9:8] =’01’).

3. Wait 4 clock cycles before performing the next write to the

Ram address register.

4. Repeat steps 2-3.

5. Return RAM control back to the channel by disabling the

µP hold mode.

Coefficients RAM Read/Write Procedure

(16-bit 2’s Complement Format)

The RAM address used for the I and Q coefficient RAM

depends on the filter. Indirect page 3 is used when the

coefficients are equal. When the coefficients are not equal

indirect page 1 is used.

Write Access to the Coefficient RAMs When I Not

Equal Q

1. Enable the µP hold mode by setting bit 12 of the Main

Control register 0x0c.

2. Load the RAM data to location 0x14 with the Q

coefficient.

3. Load the RAM data to location 0x14 with the I coefficient.

4. Load the RAM write address to location 0x15. A write

strobe transfers the contents of the register at location

0x14 into the RAM location specified by the contents of

the register at location 0x15. (Indirect address[15] =0,

Indirect address[9:8] =’01’).

5. Wait 4 clock cycles bef ore performing the next write to the

RAM data register.

6. Repeat steps 2-5.

7. Return RAM control back to the channel by disabling the

µP hold mode.

Read Access to the Q Coefficient RAM

1. Enable the µP hold mode by setting bit 12 of the Main

Control register 0x0c.

2. Load the RAM read address and 0x8200 to location 0x15.

A read strobe transfers the contents of the RAM location

specified by the contents of the register at location 0x15

onto the read bus. (Indirect address[15] =1, Indirect

address[9:8] =’10’).

3. Wait 4 clock cycles before performing the next write to the

RAM address register.

4. After all data has been loaded, return RAM control back

to the channel by disabling the µP hold mode.

Coefficients RAM Read/Write Procedure

(24-bit Floating Point Format)

The 24-bit floating point mode must be enabled by setting bit

12 of control word 0x17. The I and Q coefficients must be

loaded separately in this mode.

Write access to the Coefficient RAMs

1. Enable the µP hold mode by setting bit 12 of the Main

Control register 0x0c and bit 12 of the Test Control

register 0x17.

2. Load the RAM data to location 0x14 with the iCoef<3:0>,

iShift<3:0>, qCoef<3:0>, qShift<3:0>.

18

FN6004.3

July 8, 2005

Page 19

ISL5217

www.BDTIC.com/Intersil

3. Load the RAM data to location 0x14 with the

qCoef<19:4>.

4. Load the RAM data to location 0x14 with the

iCoef<19:4>.

5. Load the RAM write address to location 0x15. A write

strobe transfers the contents of the three previously

loaded registers at location 0x14 into the RAM location

specified by the contents of the register at location 0x15.

(Indirect address[15] =0, Indirect address[9:8] =’01’).

6. Wait 4 clock cycles bef ore performing the next write to the

RAM data register.

7. Repeat steps 2-6.

8. Return RAM control back to the channel by disabling the

µP hold mode.

Read Access to the Coefficient RAM

1. Enable the µP hold mode by setting bit 12 of the Main

Control register 0x0c and bit 12 of the Test Control

register 0x17.

2. Load the RAM read address and 0x8X00 to location 0x15.

Three read strobes are required to transfers the contents

of the RAM location specified by the contents of the

register at location 0x15 onto the read bus. Indirect

address[15] =1, Indirect address[9:8] =’01’, reads back the

iCoef value, Indirect address[15] =1, Indirect address[9:8]

=’10’, reads back the qCoef valu e, Indirect address[15] =1,

Indirect address[9:8] =’11’, reads back the iCoef<3:0>,

iShift<3:0>, qCoef<3:0>, qShift<3:0> value.

3. Wait 4 cloc k cyc les between all of the above writes before

performing the next write to the Ram address register.

4. Repeat steps 2-3.

5. Return RAM control back to the channel by disabling the

µP hold mode.

Channel Status

The present status of the channel is latched by the single

channel µP interface into the Status 0x16 register bits 11:0.

These bits represent the channel flushed, FIR and FIFO

overflow/underflow, FIFO read address, and FIFO almost and

empty flags. 0x16 bits 10:7 and bit 3 are or’ed and latched into

the Device Top Control 0x7e. The bits in 0x7e represent the

fault status of each channel and the saturation status of each