®

ISL28138, ISL28238

Data Sheet June 28, 2007

4.5MHz, Single and Dual Precision Rail-toRail Input-Output (RRIO) Op Amps with

Very Low Input Bias Current

The ISL28138 and ISL28238 are 4.5MHz low-power single

and dual operational amplifiers. The parts are optimized for

single supply operation from 2.4V to 5.5V, allowing operation

from one lithium cell or two Ni-Cd batteries.

The parts feature an Input Range Enhancement Circuit

(IREC) which enables them to maintain CMRR performance

for input voltages greater than the positive supply. The input

signal is capable of swinging 0.25V above the positive

supply and to 100mV below the negative supply with only a

slight degradation of the CMRR performance. The output

operation is rail-to-rail.

The parts draw minimal supply current (900µA per amplifier)

while meeting excellent DC accuracy, AC performance,

noise and output drive specifications. The ISL28138 features

an enable pin that can be used to turn the device off and

reduce the supply current to less than 20µA. Operation is

guaranteed over -40°C to +125°C temperature range

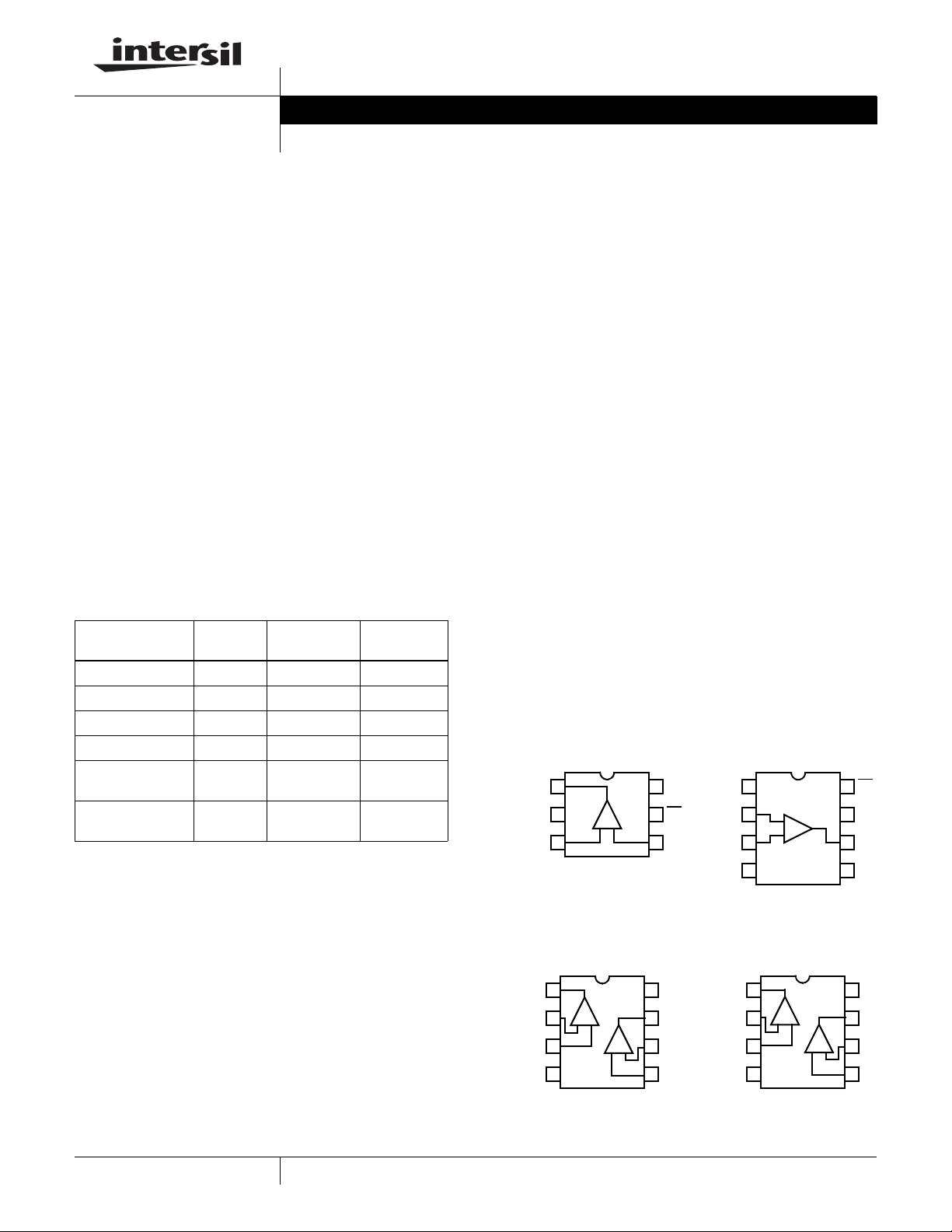

Ordering Information

PART NUMBER

(Note)

ISL28138FHZ-T7* GABR 6 Ld SOT-23 MDP0038

ISL28138FHZ-T7A* GABR 6 Ld SOT-23 MDP0038

ISL28138FBZ 28138FBZ 8Ld SO MDP0027

ISL28138FBZ-T7* 28138FBZ 8Ld SO MDP0027

Coming Soon

ISL28238FAZ-T7*

Coming Soon

ISL28238FAZ-T7*

* “-T7” and “-T7A” suffix is for tape and reel. Please refer to TB347

for details on reel specifications.

NOTE: Intersil Pb-free plus anneal products employ special

Pb-free material sets; molding compounds/die attach materials and

100% matte tin plate termination finish, which are RoHS compliant

and compatible with both SnPb and Pb-free soldering operations.

Intersil Pb-free products are MSL classified at Pb-free peak reflow

temperatures that meet or exceed the Pb-free requirements of

IPC/JEDEC J STD-020.

PART

MARKING

PACKAGE

(Pb-Free) PKG. DWG. #

8Ld SO MDP0027

8Ld MSOP MDP0043

FN6336.1

Features

• 4.5MHz gain bandwidth product

• 900µA supply current (per amplifier)

• 300µV maximum offset voltage

• 1pA typical input bias current

• Down to 2.4V single supply voltage range

• Rail-to-rail input and output

• Output sources and sinks 60mA load current

• Enable pin (ISL28138)

• -40°C to +125°C operation

• Pb-free plus anneal available (RoHS compliant)

Applications

• Low-end audio

• 4mA - 20mA current loops

• Medical devices

• Sensor amplifiers

• ADC buffers

• DAC output amplifiers

Pinouts

ISL28138

(8 LD SO)

TOP VIEW

1

2

-

+

3

V- NC

4

ISL28238

(8 LD MSOP)

TOP VIEW

1

OUT

OUT_A

(6 LD SOT-23)

1

V-

2

IN+

3

1

ISL28138

TOP VIEW

+-

ISL28238

(8 LD SO)

TOP VIEW

6

V+

EN

5

4

IN-

8

V+

NC

IN-

IN+

OUT_A

8

EN

7

V+

OUT

6

5

8

V+

IN-_A

IN-_A

2

+-

IN+_A

3

V- IN+_B

4

1

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 1-888-468-3774

All other trademarks mentioned are the property of their respective owners.

+-

| Intersil (and design) is a registered trademark of Intersil Americas Inc.

Copyright © Intersil Americas Inc. 2007. All Rights Reserved.

7

6

5

OUT_B

IN-_B

2

+-

IN+_A

3

V- IN+_B

4

+-

7

6

5

OUT_B

IN-_B

ISL28138, ISL28238

Absolute Maximum Ratings (T

Supply Voltage. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5.75V

Supply Turn On Voltage Slew Rate . . . . . . . . . . . . . . . . . . . . . 1V/μs

Differential Input Current . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5mA

Differential Input Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0.5V

Input Voltage . . . . . . . . . . . . . . . . . . . . . . . . . V-

ESD Tolerance

Human Body Model . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3kV

Machine Model. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .300V

= +25°C) Thermal Information

A

Thermal Resistance θ

6 Ld SOT-23 Package . . . . . . . . . . . . . . . . . . . . . . . 230

8 Ld SO Package . . . . . . . . . . . . . . . . . . . . . . . . . . 110

- 0.5V to V+ + 0.5V

8 Ld MSOP Package . . . . . . . . . . . . . . . . . . . . . . . . 115

Output Short-Circuit Duration . . . . . . . . . . . . . . . . . . . . . . .Indefinite

Ambient Operating Temperature Range . . . . . . . . .-40°C to +125°C

Storage Temperature Range . . . . . . . . . . . . . . . . . .-65°C to +150°C

Operating Junction Temperature . . . . . . . . . . . . . . . . . . . . . +125°C

(°C/W)

JA

Pb-free reflow profile . . . . . . . . . . . . . . . . . . . . . . . . . .see link below

http://www.intersil.com/pbfree/Pb-FreeReflow.asp

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and

result in failures not covered by warranty.

IMPORTANT NOTE: All parameters having Min/Max specifications are guaranteed. Typical values are for information purposes only. Unless otherwise noted, all tests

are at the specified temperature and are pulsed tests, therefore: TJ = TC = T

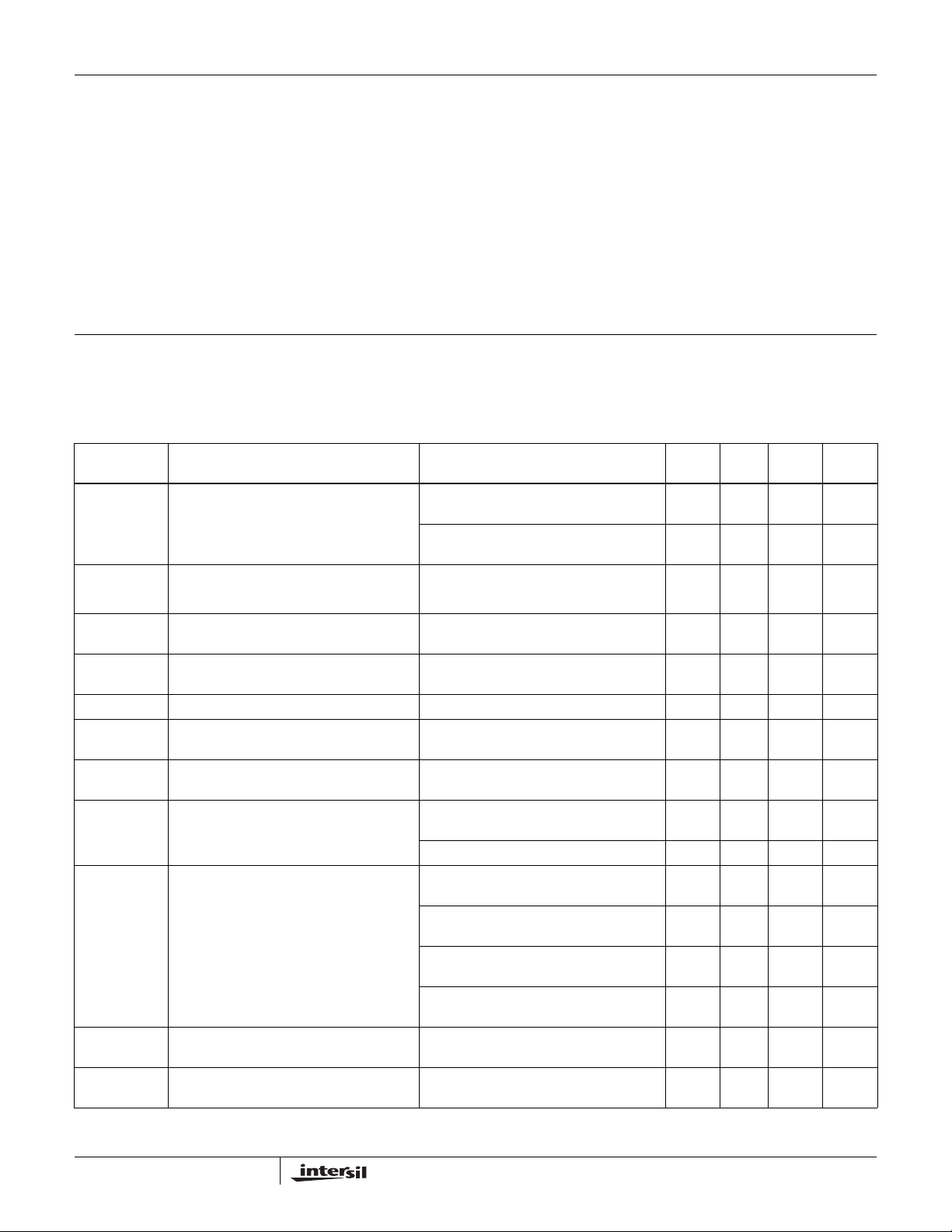

Electrical Specifications V+ = 5V, V- = 0V,V

= 2.5V, RL = Open, TA = +25°C unless otherwise specified.

CM

A

Boldface limits apply over the operating temperature range, -40°C to +125°C. Temperature data

established by characterization.

PARAMETER DESCRIPTION CONDITIONS

V

OS

Input Offset Voltage 8 Ld SO -300

6 Ld SOT-23 -550

ΔV

OS

--------------- -

ΔT

I

OS

I

B

Input Offset Voltage vs Temperature 8 Ld SO 0.6 µV/°C

Input Offset Current

T

= -40°C to +85°C

A

Input Bias Current

T

= -40°C to +85°C

A

MIN

(Note 1) TYP

-650

-750

-35

-80

-30

-80

MAX

(Note 1) UNIT

±6 300

650

±6 550

750

±535

80

±130

80

µV

µV

pA

pA

CMIR Common-Mode Voltage Range Guaranteed by CMRR 05V

CMRR Common-Mode Rejection Ratio V

= 0V to 5V 75

CM

98 dB

70

PSRR Power Supply Rejection Ratio V

A

V

VOL

OUT

Large Signal Voltage Gain VO = 0.5V to 4.5V, RL = 100kΩ to V

Maximum Output Voltage Swing Output low, RL = 100kΩ to V

= 2.4V to 5.5V 80

+

CM

V

= 0.5V to 4.5V, RL = 1kΩ to V

O

CM

CM

75

200

150

98 dB

580 V/mV

50 V/mV

368mV

I

S,ON

I

S,OFF

Output low, R

= 1kΩ to V

L

CM

50 70

110

Output high, R

Output high, R

Supply Current, Enabled 0.7

= 100kΩ to V

L

= 1kΩ to V

L

CM

CM

4.994

4.99

4.93

4.89

0.4

4.998 V

4.95 V

0.9 1.1

1.4

Supply Current, Disabled (ISL28138) 10 14

16

2

mV

mA

µA

FN6336.1

June 28, 2007

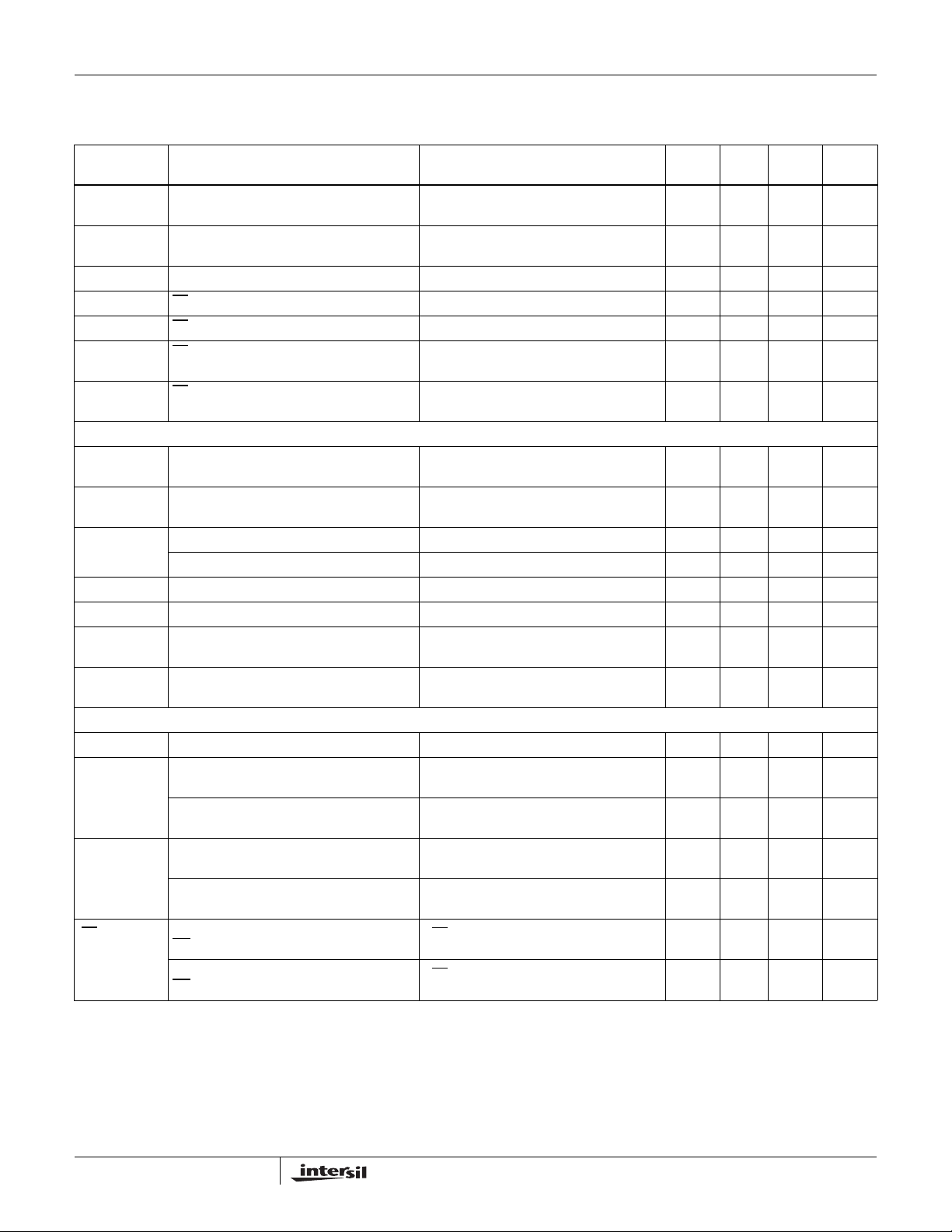

ISL28138, ISL28238

Electrical Specifications V+ = 5V, V- = 0V,V

= 2.5V, RL = Open, TA = +25°C unless otherwise specified.

CM

Boldface limits apply over the operating temperature range, -40°C to +125°C. Temperature data

established by characterization.

MIN

PARAMETER DESCRIPTION CONDITIONS

(Note 1) TYP

IO+ Short-Circuit Output Source Current RL = 10Ω 48

45

- Short-Circuit Output Sink Current RL = 10Ω 50

I

O

V

SUPPLY

V

ENH

V

ENL

I

ENH

I

ENL

Supply Operating Range V+ to V-, Guararteed by PSRR 2.4 5.5 V

EN Pin High Level (ISL28138) 2 V

EN Pin Low Level(ISL28138) 0.8 V

EN Pin Input High Curren (ISL28138) V

EN Pin Input Low Current (ISL28138) V

= V+ 1 1.5

EN

= V- 12 25

EN

45

AC SPECIFICATONS

GBW Gain Bandwidth Product A

Unity Gain

-3dB Bandwidth A

Bandwidth

e

N

Input Noise Voltage Peak-to-Peak f = 0.1Hz to 10Hz 2 µV

= 100, RF = 100kΩ, RG = 1kΩ,

V

R

= 10kΩ to V

L

=1, RF = 0Ω, V

V

R

= 10kΩ to V

L

CM

CM

OUT

= 10mV

P-P

,

Input Noise Voltage Density fO = 1kHz 26 nV/√Hz

i

N

CMRR @ 60Hz Input Common Mode Rejection Ratio V

PSRR- @

120Hz

PSRR+ @

120Hz

Input Noise Current Density fO = 1kHz 0.12 pA/√Hz

= 1V

, RL = 10kΩ to V

P-P

= 1V

= 1V

, RL = 10kΩ to V

P-P

, RL = 10kΩ to V

P-P

CM

CM

CM

Power Supply Rejection Ratio (V-) V

Power Supply Rejection Ratio (V+) V

CM

, V- = ±1.2V and ±2.5V,

+

V

SOURCE

, V- = ±1.2V and ±2.5V

+

V

SOURCE

TRANSIENT RESPONSE

SR Slew Rate

t

, tf, Large

r

Signal

, tf, Small

t

r

Signal

t

EN

Rise Time, 10% to 90%, V

Fall Time, 90% to 10%, V

Rise Time, 10% to 90%, V

Fall Time, 90% to 10%, V

OUT

OUT

OUT

OUT

Enable to Output Turn-on Delay Time, 10%

EN

to 10% V

, (ISL28138)

OUT

Enable to Output Turn-off Delay Time, 10%

EN

to 10% V

, (ISL28138)

OUT

AV = +2

,

V

= 3V

R

L

AV = +2

R

L

AV = +2

R

G

AV = +2

R

G

OUT

= 10

kΩ to V

,

V

OUT

= 10

kΩ to V

,

V

OUT

= RF = RL = 10

,

V

OUT

= RF = RL = 10

P-P

CM

= 3V

P-P

CM

= 10mV

kΩ to V

= 10mV

kΩ to V

VEN = 5V to 0V, AV = +2,

R

= RF = RL = 1

G

k to V

VEN = 0V to 5V, AV = +2,

R

= RF = RL = 1k

G

to V

, RG = RF =

, RG = RF =

,

P-P

CM

,

P-P

CM

CM

CM

10k

10k

Ω

Ω

NOTE:

1. Parts are 100% tested at +25°C. Over temperature limits established by characterization and are not production tested.

MAX

(Note 1) UNIT

75 mA

68 mA

µA

1.6

nA

30

4.5 MHz

13 MHz

P-P

85 dB

-82 dB

-100 dB

±4.8 V/µs

530 ns

530 ns

50 ns

50 ns

5µs

0.2 µs

3

FN6336.1

June 28, 2007

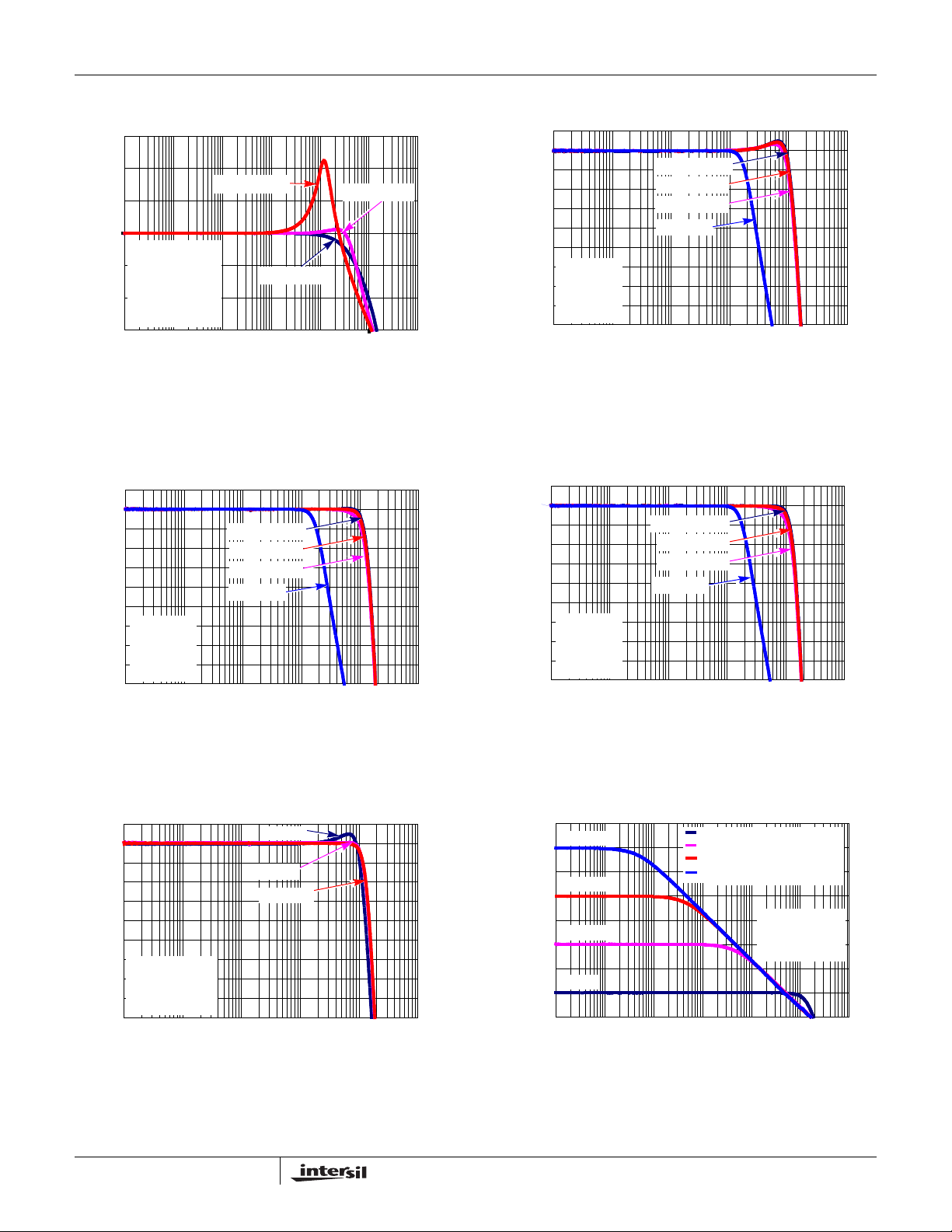

ISL28138, ISL28238

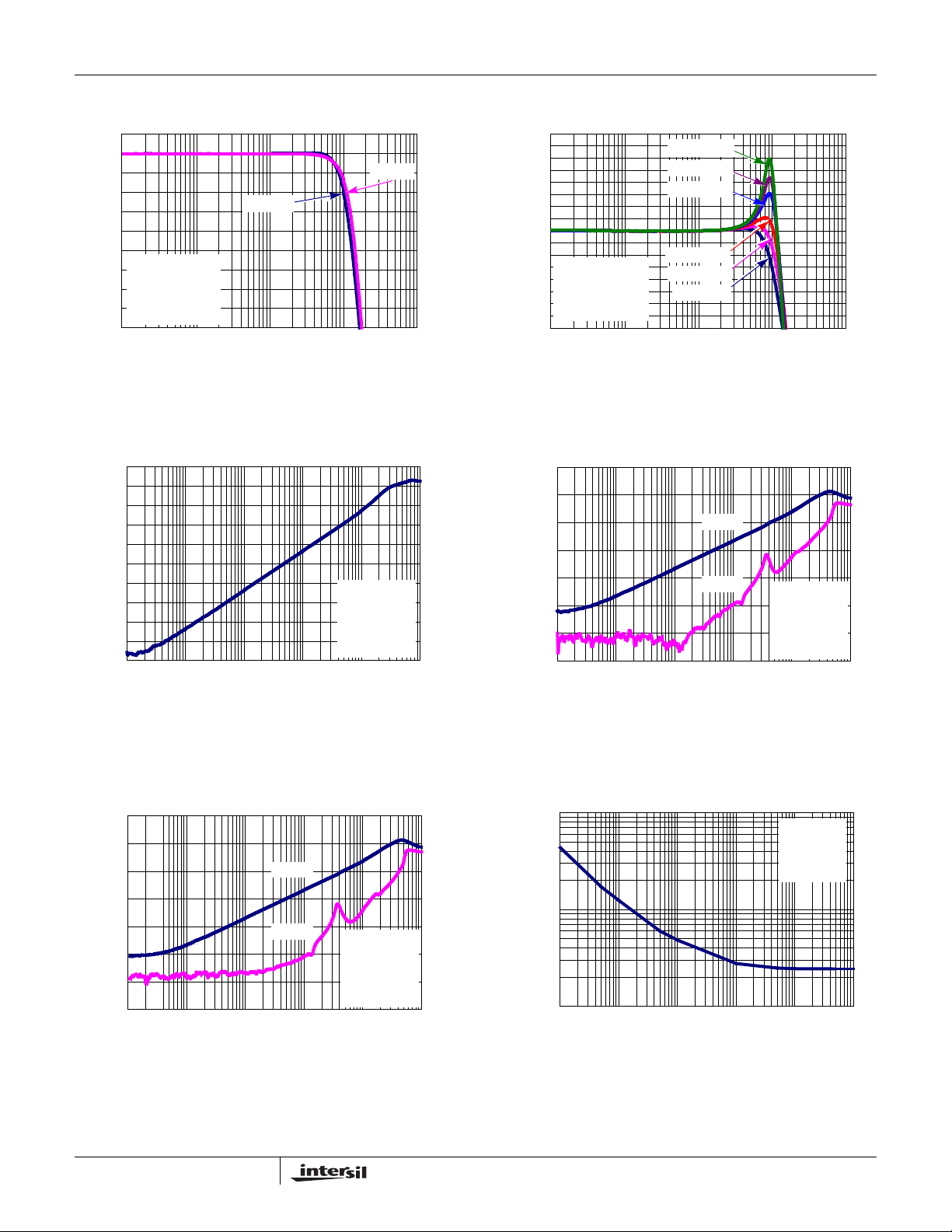

Typical Performance Curves V+ = 5V, V- = 0V,V

15

10

5

0

V+ = 5V

-5

= 1k

R

L

CL = 16.3pF

NORMALIZED GAIN (dB)

-10

= +2

A

V

V

= 10mV

OUT

-15

100 1k 10k 100k 1M 10M 100M

FIGURE 1. GAIN vs FREQUENCY vs FEEDBACK RESISTOR

VALUES R

1

0

-1

-2

-3

-4

-5

-6

V+ = 5V

= 10k

R

-7

L

NORMALIZED GAIN (dB)

= 16.3pF

C

L

-8

A

= +1

V

-9

1k 10k 100k 1M 10M 100M

FIGURE 3. GAIN vs FREQUENCY vs V

Rf = Rg = 100k

P-P

FREQUENCY (Hz)

f/Rg

V

OUT

V

OUT

V

OUT

V

OUT

FREQUENCY (Hz)

Rf = Rg = 1k

= 100mV

= 50mV

= 10mV

= 1V

Rf = Rg = 10k

, RL = 10k

OUT

= 2.5V, RL = Open, unless otherwise specified.

CM

1

0

-1

-2

-3

-4

-5

-6

V+ = 5V

= 1k

R

-7

L

NORMALIZED GAIN (dB)

= 16.3pF

C

L

-8

A

= +1

V

-9

1k 10k 100k 1M 10M 100M

V

OUT

V

OUT

V

OUT

V

OUT

FREQUENCY (Hz)

FIGURE 2. GAIN vs FREQUENCY vs V

1

0

-1

-2

-3

-4

-5

-6

V+ = 5V

= 100k

R

L

-7

NORMALIZED GAIN (dB)

= 16.3pF

C

L

-8

= +1

A

V

-9

1k 10k 100k 1M 10M 100M

V

OUT

V

OUT

V

OUT

V

OUT

FREQUENCY (Hz)

FIGURE 4. GAIN vs FREQUENCY vs V

= 100mV

= 50mV

= 10mV

= 1V

= 100mV

= 50mV

= 10mV

= 1V

OUT, RL

, RL = 100k

OUT

= 1k

1

0

-1

-2

-3

-4

-5

-6

V+ = 5V

= 10mV

V

-7

OUT

NORMALIZED GAIN (dB)

= 16.3pF

C

L

-8

AV = +1

-9

1k 10k 100k 1M 10M 100M

P-P

FIGURE 5. GAIN vs FREQUENCY vs R

RL = 1k

RL = 10k

RL = 100k

FREQUENCY (Hz)

L

4

GAIN (dB)

70

60

50

40

30

20

10

0

-10

AV = 1001

AV = 101

A

AV = 1

100

= 10

V

1k 10k 100k 1M 10M 100M

AV = 1, Rg = INF, Rf = 0

A

= 10, Rg = 1k, Rf = 9.09k

V

= 101, Rg = 1k, Rf = 100k

A

V

A

= 1001, Rg = 1k, Rf = 1M

V

FREQUENCY (Hz)

V+ = 5V

CL = 16.3pF

= 10k

R

L

= 10mV

V

OUT

P-P

FIGURE 6. FREQUENCY RESPONSE vs CLOSED LOOP GAIN

FN6336.1

June 28, 2007

ISL28138, ISL28238

Typical Performance Curves V+ = 5V, V- = 0V,V

1

0

-1

-2

-3

-4

-5

RL = 10k

-6

CL = 16.3pF

-7

NORMALIZED GAIN (dB)

A

= +1

V

-8

V

= 10mV

OUT

-9

10k 100k 1M 10M 100M

V+ = 2.4V

P-P

FREQUENCY (Hz)

FIGURE 7. GAIN vs FREQUENCY vs SUPPLY VOLTAGE

10

0

-10

-20

-30

-40

-50

CMRR (dB)

-60

-70

-80

-90

100 1k 10k 100k 1M 10M

FREQUENCY (Hz)

FIGURE 9. CMRR vs FREQUENCY; V+ = 2.4V AND 5V

V+ = 5V

V+ = 2.4V, 5V

= 1k

R

L

CL = 16.3pF

A

= +1

V

= 1V

V

CM

P-P

= 2.5V, RL = Open, unless otherwise specified. (Continued)

CM

8

7

6

5

4

3

2

1

0

-1

-2

-3

V

= 5V

+

-4

R

= 1k

L

NORMALIZED GAIN (dB)

-5

A

= +1

V

-6

V

= 10mV

OUT

-7

-8

10k 100k 1M 10M 100M

CL = 51.7pF

CL = 43.7pF

CL = 37.7pF

CL = 26.7pF

CL = 16.7pF

CL = 4.7pF

P-P

FREQUENCY (Hz)

FIGURE 8. GAIN vs FREQUENCY vs C

20

0

-20

-40

-60

PSRR (dB)

-80

-100

-120

100 1k 10k 100k 1M 10M

FREQUENCY (Hz)

PSRR-

PSRR+

FIGURE 10. PSRR vs FREQUENCY, V

L

V+, V- = ±1.2V

= 1k

R

L

CL = 16.3pF

A

= +1

V

= 1V

V

CM

, V- = ±1.2V

+

P-P

20

0

-20

-40

-60

PSRR (dB)

-80

-100

-120

100 1k 10k 100k 1M 10M

FIGURE 11. PSRR vs FREQUENCYV, V

PSRR-

PSRR+

FREQUENCY (Hz)

V+, V- = ±2.5V

= 1k

R

L

CL = 16.3pF

= +1

A

V

V

= 1V

CM

, V- = ±2.5V

+

5

P-P

1k

V+ = 5V

= 1k

R

L

= 16.3pF

C

L

A

= +1

V

100

INPUT VOLTAGE NOISE (nV/√Hz)

10

1 10 100 1k 10k 100k

FREQUENCY (Hz)

FIGURE 12. INPUT VOLTAGE NOISE DENSITY vs FREQUENCY

FN6336.1

June 28, 2007

ISL28138, ISL28238

Typical Performance Curves V+ = 5V, V- = 0V,V

CM

10

V+ = 5V

= 1k

R

L

= 16.3pF

C

L

A

= +1

V

1

INPUT CURRENT NOISE (pA/√Hz)

0.1

1 10 100 1k 10k 100k

FREQUENCY (Hz)

FIGURE 13. INPUT CURRENT NOISE DENSITY vs FREQUENCY

2.0

1.5

1.0

0.5

0

-0.5

LARGE SIGNAL (V)

-1.0

-1.5

-2.0

0123456789

V+, V- = ±2.5V

= 1k

R

L

C

= 16.3pF

L

= Rf =10k

R

g

= 2

A

V

V

= 3V

OUT

P-P

10

TIME (µs)

FIGURE 15. LARGE SIGNAL STEP RESPONSE

= 2.5V, RL = Open, unless otherwise specified. (Continued)

0

-0.5

-1.0

-1.5

-2.0

INPUT NOISE (µV)

-2.5

-3.0

V+ = 5V

= 16.3pF

C

L

= 10

R

g

R

A

R

f

= 10k

L

= 10k

V

= 100k

012345678910

TIME (s)

FIGURE 14. INPUT VOLTAGE NOISE 0.1Hz to 10Hz

0.025

0.020

V+, V- = ±2.5V

= 1k

R

0.015

SMALL SIGNAL (V)

0.010

012345678910

L

C

= 16.3pF

L

= Rf = 10k

R

g

= 2

A

V

V

OUT

= 10mV

P-P

TIME (µs)

FIGURE 16. SMALL SIGNAL STEP RESPONSE

3.5

3.0

V

EN

V

OUT

2.5

2.0

(V)

1.5

ENABLE

1.0

V

0.5

V+ = 5V

= Rf = 10k

R

g

CL = 16.3pF

A

= +2

V

= 1V

V

OUT

RL = 10k

P-P

0

-0.5

0 102030405060708090100

1.2

1

0.8

0.6

0.4

OUTPUT (V)

0.2

0

-0.2

TIME (µs)

FIGURE 17. ISL28138 ENABLE TO OUTPUT RESPONSE

6

FN6336.1

June 28, 2007

ISL28138, ISL28238

Typical Performance Curves V+ = 5V, V- = 0V,V

800

(V)

MIN

V+ = 5V

= OPEN

R

L

= 100k, Rg = 100

R

f

A

= +1k

V

600

400

200

(µV)

0

OS

V

-200

-400

-600

-800

-10123456

V

CM

FIGURE 18. INPUT OFFSET VOLT AGE vs COMMON MODE

INPUT VOLTAGE

1.2

1.1

1.0

0.9

0.8

CURRENT (μA)

0.7

MAX

MEDIAN

= 2.5V, RL = Open, unless otherwise specified. (Continued)

CM

100

80

60

40

20

(pA)

0

BIAS

-20

I

-40

-60

-80

-100

-10123456

(V)

V

CM

FIGURE 19. INPUT BIAS CURRENT vs COMMON MODE

INPUT VOLTAGE

10.5

9.5

8.5

7.5

6.5

CURRENT (μA)

5.5

4.5

MAX

MEDIAN

MIN

V+ = 5V

= OPEN

R

L

= 100k, Rg = 100

R

f

A

= +1k

V

0.6

-40 -20 0 20 40 60 80 100 120

TEMPERATURE (°C)

FIGURE 20. SUPPLY CURRENT ENABLED vs

TEMPERATURE V

600

400

200

0

(μV)

OS

-200

V

-400

-600

-800

-40-200 20406080100120

FIGURE 22. V

(SOIC PKG) vs TEMPERATURE

OS

V

= 0V, V+, V- = ±2.75V

IN

, V- = ±2.5V

+

MAX

MEDIAN

MIN

TEMPERATURE (°C)

3.5

-40 -20 0 20 40 60 80 100 120

TEMPERATURE (°C)

FIGURE 21. SUPPLY CURRENT DISABLED vs

TEMPERATURE V

800

600

400

200

(μV)

0

OS

V

-200

-400

-600

-800

-40 -20 0 20 40 60 80 100 120

FIGURE 23. V

(SOT PKG) vs TEMPERATURE

OS

V

= 0V, V+, V- = ±2.75V

IN

, V- = ±2.5V

+

MAX

MEDIAN

MIN

TEMPERATURE (°C)

7

FN6336.1

June 28, 2007

ISL28138, ISL28238

Typical Performance Curves V+ = 5V, V- = 0V,V

600

400

200

0

(μV)

OS

-200

V

-400

-600

-800

-40 -20 0 20 40 60 80 100 120

FIGURE 24. VOS (SOIC PKG) vs TEMPERATURE

V

= 0V, V+, V- = ±2.5V

IN

800

600

400

200

(μV)

0

OS

V

-200

-400

-600

-800

-40-200 20406080100120

FIGURE 26. V

(SOIC PKG) vs TEMPERATURE

OS

V

= 0V, V+, V- = ±1.2V

IN

MAX

MEDIAN

MIN

TEMPERATURE (°C)

MAX

MEDIAN

MIN

TEMPERATURE (°C)

= 2.5V, RL = Open, unless otherwise specified. (Continued)

CM

800

600

400

200

(μV)

0

OS

V

-200

-400

-600

-800

-40 -20 0 20 40 60 80 100 120

FIGURE 25. V

1000

800

600

400

(μV)

200

OS

V

0

-200

-400

-600

-40-200 20406080100120

FIGURE 27. V

(SOT PKG) vs TEMPERATURE

OS

V

= 0V, V+, V- = ±2.5V

IN

(SOT PKG) vs TEMPERATURE

OS

V

= 0V, V+, V- = ±1.2V

IN

MAX

MEDIAN

MIN

TEMPERATURE (°C)

MAX

MEDIAN

MIN

TEMPERATURE (°C)

300

250

200

150

- (pA)

100

BIAS

I

50

0

-50

-40-200 20406080100120

TEMPERATURE (°C)

FIGURE 28. I

- vs TEMPERATURE V+, V- = ±2.5V

BIAS

MAX

MEDIAN

MIN

8

250

200

150

- (pA)

100

BIAS

I

50

0

-50

-40-200 20406080100120

TEMPERATURE (°C)

FIGURE 29. I

- vs TEMPERATURE V+, V- = ±1.2V

BIAS

MAX

MEDIAN

MIN

June 28, 2007

FN6336.1

ISL28138, ISL28238

Typical Performance Curves V+ = 5V, V- = 0V,V

10

0

-10

-20

(pA)

-30

S

O

I

-40

-50

-60

-70

-40 -20 0 20 40 60 80 100 120

TEMPERATURE (°C)

FIGURE 30. IOS vs TEMPERATURE V+, V- = ±2.5V

1750

1550

1350

1150

(V/mV)

950

VOL

A

750

550

350

150

-40-200 20406080100120

TEMPERATURE (°C)

FIGURE 32. A

vs TEMPERAT URE, RL = 100k,

VOL

V

, V- = ±2.5V, VO = -2V TO +2V

+

MAX

MEDIAN

MIN

MAX

MEDIAN

MIN

= 2.5V, RL = Open, unless otherwise specified. (Continued)

CM

20

10

0

-10

(pA)

-20

S

O

I

-30

-40

-50

-60

-40 -20 0 20 40 60 80 100 120

TEMPERATURE (°C)

FIGURE 31. I

80

70

60

50

(V/mV)

VOL

A

40

30

20

-40 -20 0 20 40 60 80 100 120

FIGURE 33. A

V

vs TEMPERATURE V+, V- = ±1.2V

OS

TEMPERATURE (°C)

vs TEMPERATURE, RL = 1k

VOL

, V- = ±2.5V, VO = -2V TO +2V

+

MAX

MEDIAN

MAX

MEDIAN

MIN

MIN

140

130

120

110

100

CMRR (dB)

90

80

70

-40-200 20406080100120

FIGURE 34. CMRR vs TEMPERATURE, V

V

, V- = ±2.5V

+

MAX

MEDIAN

MIN

TEMPERATURE (°C)

= +2.5V TO -2.5V ,

CM

9

140

130

120

110

100

PSRR (dB)

90

80

70

-40-200 20406080100120

TEMPERATURE (°C)

FIGURE 35. PSRR vs TEMPERATURE, V

MAX

MEDIAN

MIN

, V- = ±1.2V TO

+

±2.75V

FN6336.1

June 28, 2007

ISL28138, ISL28238

Typical Performance Curves V+ = 5V, V- = 0V,V

4.970

4.965

4.960

(V)

4.955

OUT

V

4.950

4.945

4.940

-40 -20 0 20 40 60 80 100 120

FIGURE 36. V

75

70

65

60

(mV)

55

OUT

V

50

45

40

-40-200 20406080100120

FIGURE 38. V

MEDIAN

TEMPERATURE (°C)

HIGH vs TEMPERATUE RL = 1k,

OUT

V

, V- = ±2.5V

+

MEDIAN

TEMPERATURE (°C)

LOW vs TEMPERATUE RL = 1k,

OUT

V

, V- = ±2.5V

+

MAX

MIN

MAX

MIN

= 2.5V, RL = Open, unless otherwise specified. (Continued)

CM

4.9994

4.9992

4.9990

(V)

4.9988

OUT

V

4.9986

4.9984

4.9982

FIGURE 37. V

3.3

3.1

2.9

2.7

2.5

(mV)

2.3

OUT

V

2.1

1.9

1.7

1.5

FIGURE 39. V

MEDIAN

-40-200 20406080100120

TEMPERATURE (°C)

HIGH vs TEMPERATUE RL = 100k,

OUT

V

, V-=±2.5V

+

-40 -20 0 20 40 60 80 100 120

TEMPERATURE (°C)

LOW vs TEMPERATUE RL=100k,

OUT

V

, V- = ±2.5V

+

MAX

MIN

MAX

MIN

MEDIAN

95

90

85

80

75

70

65

60

-40 -20 0 20 40 60 80 100 120

+ OUTPUT SHORT CIRCUIT CURRENT (mA)

MAX

MEDIAN

MIN

TEMPERATURE (°C)

FIGURE 40. + OUTPUT SHORT CIRCUIT CURRENT vs

TEMPERATUE V

V

, V- = ±2.5V

+

= -2.55V, RL = 10,

IN

10

-50

-55

-60

-65

-70

-75

-80

-85

-40 -20 0 20 40 60 80 100 120

- OUTPUT SHORT CIRCUIT CURRENT (mA)

MEDIAN

MEDIAN

TEMPERATURE (°C)

MAX

MAX

MIN

MIN

FIGURE 41. - OUTPUT SHORT CIRCUIT CURRENT vs

TEMPERATUE V

V

, V- = ±2.5V

+

= -2.55V, RL = 10,

IN

June 28, 2007

FN6336.1

Pin Descriptions

V

V

ISL28138

(6 Ld SOT-23)

42

33

ISL28138, ISL28238

ISL28238

ISL28138

(8 Ld SO)

1, 5 NC Not connected

(8 Ld SO)

(8 Ld MSOP) PIN NAME FUNCTION EQUIVALENT CIRCUIT

IN2

6

3

5

IN-_A

IN-_B

IN+

IN+_A

IN+_B

inverting input

Non-inverting

input

IN-

(See circuit 1)

V+

IN+

V-

Circuit 1

2 4 4 V- Negative supply

16

1

7

6 7 8 V+ Positive supply (See circuit 2)

58

Applications Information

Introduction

The ISL28138 and ISL28238 are single and dual channel

CMOS rail-to-rail input, output (RRIO) micropower precision

operational amplifiers. The parts are designed to operate

from single supply (2.4V to 5.5V) or dual supply (±1.2V to

±2.75V). The parts have an input common mode range that

extends 0.25V above the positive rail and 100mV below the

the negative supply rail. The output operation can swing

within about 3mV of the supply rails with a 100kΩ load.

Rail-to-Rail Input

Many rail-to-rail input stages use two differential input pairs,

a long-tail PNP (or PFET) and an NPN (or NFET). Severe

penalties have to be paid for this circuit topology. As the

OUT

OUT_A

OUT_B

EN

V+

CAPACITIVELY

COUPLED

ESD CLAMP

V-

Circuit 2

Output

Circuit 3

Chip enable

EN

Circuit 4

+

OUT

V-

+

V-

input signal moves from one supply rail to another, the

operational amplifier switches from one input pair to the

other causing drastic changes in input offset voltage and an

undesired change in magnitude and polarity of input offset

current.

The ISL28138 and ISL28238 achieve input rail-to-rail

operation without sacrificing important precision

specifications and degrading distortion performance. The

devices’ input offset voltage exhibits a smooth behavior

throughout the entire common-mode input range. The input

bias current versus the common-mode voltage range gives

us an undistorted behavior from typically 100mV below the

negative rail and 0.25V higher than the V+ rail.

11

FN6336.1

June 28, 2007

ISL28138, ISL28238

Rail-to-Rail Output

A pair of complementary MOS devices are used to achieve

the rail-to-rail output swing. The NMOS sinks current to

swing the output in the negative direction. The PMOS

sources current to swing the output in the positive direction.

The ISL28138 and ISL28238 with a 100kΩ load will swing to

within 3mV of the positive supply rail and within 3mV of the

negative supply rail.

Results of Over-Driving the Output

Caution should be used when over-driving the output for long

periods of time. Over-driving the output can occur in two ways.

1) the input voltage times the gain of the amplifier exceeds the

supply voltage by a large value or 2) The output current

required is higher than the output stage can deliver. These

conditions can result in a shift in the Input Offset Voltage (V

OS

as much as 1µV/hr. of exposure under these condition.

IN+ and IN- Input Protection

All input terminals have internal ESD protection diodes to both

positive and negative supply rails, limiting the input volt age to

within one diode beyond the supply rails. They also contain

back-to-back diodes across the input terminals (Pin

Description Table - Circuit 1

). For applications where the input

differential voltage is expected to exceed 0.5V, an external

series resistor must be used to ensure the input currents

never exceed 5mA (Figure 42).

-

R

V

IN

FIGURE 42. INPUT CURRENT LIMITING

IN

+

R

L

V

OUT

Enable/Disable Feature

The ISL28138 offers an EN pin that disables the device

when pulled up to at least 2.0V. In the disabled state (output

in a high impedance state), the part consumes typically 10µA

at room temperature. By disabling the part, multiple

ISL28138 parts can be connected together as a MUX. In this

configuration, the outputs are tied together in parallel and a

channel can be selected by the EN

of the feedback resistors of the disabled amplifier must be

considered when multiple amplifier outputs are connected

together. Note that feed through from the IN+ to IN- pins

occurs on any Mux Amp disabled channel where the input

differential voltage exceeds 0.5V (e.g., active channel

V

= 1V, while disabled channel VIN = GND), so the mux

OUT

implementation is best suited for small signal applications. If

large signals are required, use series IN+ resistors, or large

value R

, to keep the feed through current low enough to

F

minimize the impact on the active channel. See “Limitations

of the Differential Input Protection” on page 12 for more

details.The EN

open, the EN

pin also has an internal pull-down. If left

pin will pull to the negative rail and the device

pin. The loading effects

will be enabled by default. When not used, the EN

pin should

either be left floating or connected directly to the V- pin.

Limitations of the Differential Input Protection

If the input differential voltage is expected to exceed 0.5V, an

external current limiting resistor must be used to ensure the

input current never exceeds 5mA. For non-inverting unity gain

applications the current limiting can be via a series IN+ resistor,

or via a feedback resistor of appropriate value. For other gain

configurations, the series IN+ resistor is the best choice, unless

the feedback (R

) and gain setting (RG) resistors are both

F

sufficiently large to limit the input current to 5mA.

Large differential input voltages can arise from several

sources:

)

1) During open loop (comparator) operation. Used this way,

the IN+ and IN- voltages don’t track, so differentials arise.

2) When the amplifier is disabled but an input signal is still

present. An R

or RG to GND keeps the IN- at GND, while

L

the varying IN+ signal creates a differential voltage. Mux

Amp applications are similar, except that the active channel

V

determines the voltage on the IN- terminal.

OUT

3) When the slew rate of the input pulse is considerably

faster than the op amp’ s slew rate. If the V

can’t keep up

OUT

with the IN+ signal, a differential voltage results, and visible

distortion occurs on the input and output signals. To avoid

this issue, keep the input slew rate below 4.8V/μs, or use

appropriate current limiting resistors.

Large (>2V) differential input voltages can also cause an

increase in disabled I

CC

.

Using Only One Channel

If the application only requires one channel of the ISL28238

the user must configure the unused channel to prevent IT

from oscillating. The unused channel will oscillate if the input

and output pins are floating. This will result in higher than

expected supply currents and possible noise injection into

the channel being used. The proper way to prevent this

oscillation is to short the output to the negative input and

ground the positive input (as shown in Figure 43).

-

+

FIGURE 43. PREVENTING OSCILLATIONS IN UNUSED

CHANNELS

12

FN6336.1

June 28, 2007

ISL28138, ISL28238

Proper Layout Maximizes Performance

To achieve the maximum performance of the high input

impedance and low offset voltage, care should be taken in

the circuit board layout. The PC board surface must remain

clean and free of moisture to avoid leakage currents

between adjacent traces. Surface coating of the circuit board

will reduce surface moisture and provide a humidity barrier,

reducing parasitic resistance on the board. When input

leakage current is a concern, the use of guard rings around

the amplifier inputs will further reduce leakage currents.

Figure 44 shows a guard ring example for a unity gain

amplifier that uses the low impedance amplifier output at the

same voltage as the high impedance input to eliminate

surface leakage. The guard ring does not need to be a

specific width, but it should form a continuous loop around

both inputs. For further reduction of leakage currents,

components can be mounted to the PC board using PTFE

standoff insulators.

HIGH IMPEDANCE INPUT

IN

FIGURE 44. GUARD RING EXAMPLE FOR UNITY GAIN

AMPLIFIER

V+

Current Limiting

The ISL28138 and ISL28238 have no internal currentlimiting circuitry. If the output is shorted, it is possible to

exceed the Absolute Maximum Rating for output current or

power dissipation, potentially resulting in the destruction of

the device.

Power Dissipation

It is possible to exceed the +150°C maximum junction

temperatures under certain load and power-supply

conditions. It is therefore important to calculate the

maximum junction temperature (T

to determine if power supply voltages, load conditions, or

package type need to be modified to remain in the safe

operating area. These parameters are related in Equation 1:

T

JMAXTMAXθJA

xPD

()+=

MAXTOTAL

where:

•P

DMAXTOTAL

is the sum of the maximum power

dissipation of each amplifier in the package (PD

•PD

for each amplifier can be calculated as shown in

MAX

Equation 2:

PD

MAX

2*VSI

SMAXVS

( - V

where:

•T

• θ

•PD

•V

•I

•V

= Maximum ambient temperature

MAX

= Thermal resistance of the package

JA

= Maximum power dissipation of 1 amplifier

MAX

= Supply voltage (Magnitude of V+ and V-)

S

= Maximum supply current of 1 amplifier

MAX

OUTMAX

= Maximum output voltage swing of the

application

= Load resistance

•R

L

) for all applications

JMAX

)

OUTMAX

×+×=

MAX

V

OUTMAX

----------------------------

R

L

(EQ. 1)

)

(EQ. 2)

13

FN6336.1

June 28, 2007

SOT-23 Package Family

ISL28138, ISL28238

2 3

0.15 DC

2X

C

SEATING

PLANE

E1

5

0.15 A-BC

2X

0.10 C

NX

(L1)

e1

A

6

N

4

D

MDP0038

SOT-23 PACKAGE FAMILY

SYMBOL

MILLIMETERS

TOLERANCESOT23-5 SOT23-6

A 1.45 1.45 MAX

A1 0.10 0.10 ±0.05

E

A2 1.14 1.14 ±0.15

b 0.40 0.40 ±0.05

321

e

0.20

B

b

NX

M

0.20 C

2X

DC A-B

c 0.14 0.14 ±0.06

D 2.90 2.90 Basic

E 2.80 2.80 Basic

E1 1.60 1.60 Basic

e 0.95 0.95 Basic

e1 1.90 1.90 Basic

L 0.45 0.45 ±0.10

L1 0.60 0.60 Reference

1 3

D

N 5 6 Reference

Rev. F 2/07

NOTES:

A2

1. Plastic or metal protrusions of 0.25mm maximum per side are not

included.

2. Plastic interlead protrusions of 0.25mm maximum per side are not

A1

included.

3. This dimension is measured at Datum Plane “H”.

4. Dimensioning and tolerancing per ASME Y14.5M-1994.

5. Index area - Pin #1 I.D. will be located within the indicated zone

(SOT23-6 only).

H

6. SOT23-5 version has no center lead (shown as a dashed line).

A

c

L

14

0°

GAUGE

PLANE

+3°

-0°

0.25

FN6336.1

June 28, 2007

Small Outline Package Family (SO)

A

D

NN

(N/2)+1

ISL28138, ISL28238

h X 45°

PIN #1

E

C

SEATING

PLANE

0.004 C

E1

B

0.010 BM CA

I.D. MARK

1

e

0.010 BM CA

(N/2)

c

SEE DETAIL “X”

L1

H

A2

GAUGE

PLANE

A1

b

DETAIL X

L

4° ±4°

MDP0027

SMALL OUTLINE PACKAGE FAMILY (SO)

INCHES

SO16

SYMBOL

(0.150”)

A 0.068 0.068 0.068 0.104 0.104 0.104 0.104 MAX -

A1 0.006 0.006 0.006 0.007 0.007 0.007 0.007 ±0.003 A2 0.057 0.057 0.057 0.092 0.092 0.092 0.092 ±0.002 -

b 0.017 0.017 0.017 0.017 0.017 0.017 0.017 ±0.003 -

c 0.009 0.009 0.009 0.011 0.011 0.011 0.011 ±0.001 D 0.193 0.341 0.390 0.406 0.504 0.606 0.704 ±0.004 1, 3

E 0.236 0.236 0.236 0.406 0.406 0.406 0.406 ±0.008 -

E1 0.154 0.154 0.154 0.295 0.295 0.295 0.295 ±0.004 2, 3

e 0.050 0.050 0.050 0.050 0.050 0.050 0.050 Basic -

L 0.025 0.025 0.025 0.030 0.030 0.030 0.030 ±0.009 -

L1 0.041 0.041 0.041 0.056 0.056 0.056 0.056 Basic -

h 0.013 0.013 0.013 0.020 0.020 0.020 0.020 Reference -

N 8 14 16 16 20 24 28 Reference -

NOTES:

1. Plastic or metal protrusions of 0.006” maximum per side are not included.

2. Plastic interlead protrusions of 0.010” maximum per side are not included.

3. Dimensions “D” and “E1” are measured at Datum Plane “H”.

4. Dimensioning and tolerancing per ASME Y14.5M-1994

SO16 (0.300”)

(SOL-16)

SO20

(SOL-20)

SO24

(SOL-24)

SO28

(SOL-28)

TOLERANCE NOTESSO-8 SO-14

A

0.010

Rev. M 2/07

15

FN6336.1

June 28, 2007

Mini SO Package Family (MSOP)

M

C

SEATING

PLANE

0.10 C

N LEADS

c

0.25 C A B

E1E

B

e

L1

SEE DETAIL "X"

D

N

1

b

A

(N/2)+1

PIN #1

I.D.

(N/2)

H

M

0.08 C A B

A

ISL28138, ISL28238

MDP0043

MINI SO PACKAGE FAMILY

SYMBOL

A 1.10 1.10 Max. A1 0.10 0.10 ±0.05 A2 0.86 0.86 ±0.09 -

b 0.33 0.23 +0.07/-0.08 -

c 0.18 0.18 ±0.05 -

D 3.00 3.00 ±0.10 1, 3

E 4.90 4.90 ±0.15 E1 3.00 3.00 ±0.10 2, 3

e 0.65 0.50 Basic -

L 0.55 0.55 ±0.15 L1 0.95 0.95 Basic -

N 8 10 Reference -

NOTES:

1. Plastic or metal protrusions of 0.15mm maximum per side are not

included.

2. Plastic interlead protrusions of 0.25mm maximum per side are

not included.

3. Dimensions “D” and “E1” are measured at Datum Plane “H”.

4. Dimensioning and tolerancing per ASME Y14.5M-1994.

MILLIMETERS

TOLERANCE NOTESMSOP8 MSOP10

Rev. D 2/07

A2

GAUGE

A1

L

DETAIL X

PLANE

3° ±3°

0.25

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems.

Intersil Corporation’s quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without

notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and

reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result

from its use. No license is granted by implicat ion or oth erwise u nde r any p a tent or p at ent r ights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com

16

FN6336.1

June 28, 2007

Loading...

Loading...