®

www.BDTIC.com/Intersil

Dual Digitally Controlled Potentiometers (XDCP™)

ISL22326

Data Sheet February 29, 2008

Low Noise, Low Power, I2C® Bus, 128 Taps

The ISL22326 integrates two digitally controlled potentiometers

(XDCP) and non-volatile memory on a monolithic CMOS

integrated circuit.

The digitally controlled potentiometers are implemented with

a combination of resistor elements and CMOS switches. The

position of the wipers are controlled by the user through the

2

I

C bus interface. Each potentiometer has an associated

volatile Wiper Register (WR) and a non-volatile Initial Value

Register (IVR) that can be directly written to and read by the

user. The contents of the WR controls the position of the

wiper. At power-up the device recalls the contents of the two

DCP’s IVR to the corresponding WRs.

The DCPs can be used as three-terminal potentiometers or

as two-terminal variable resistors in a wide variety of

applications including control, parameter adjustments, and

signal processing.

FN6176.1

Features

• Two potentiometers in one package

• 128 resistor taps

•I2C serial interface

- Three address pins, up to eight devices/bus

• Non-volatile storage of wiper position

• Wiper resistance: 70Ω typical @ V

• Shutdown mode

• Shutdown current 5µA max

• Power supply: 2.7V to 5.5V

•50kΩ or 10kΩ total resistance

• High reliability

- Endurance: 1,000,000 data changes per bit per register

- Register data retention: 50 years @ T <

• 14 Ld TSSOP or 16 Ld QFN package

• Pb-free (RoHS compliant)

CC

= 3.3V

+55°C

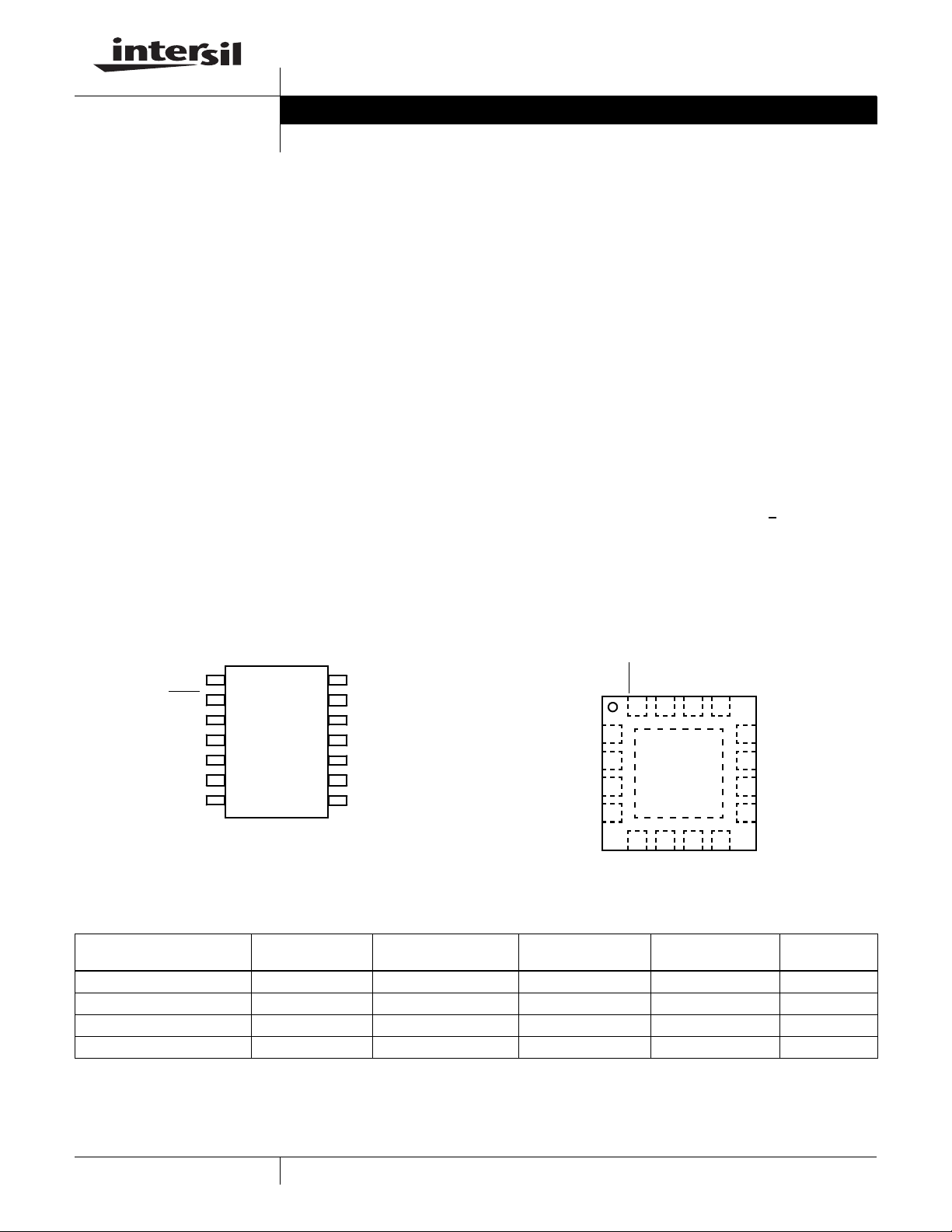

Pinouts

CC

SHDN

RH0

RL0

RW0

A2

ISL22326

(14 LD TSSOP)

TOP VIEW

1

2

3

4

5

6

7

14

A1V

13

A0

RH1

12

11

RL1

RW1

10

GND

9

SDASCL

8

RH0

RL0

RW0

NC

1

2

3

4

ISL22326

(16 LD QFN)

TOP VIEW

CC

SHDN

A2

A1

V

1516 14 13

6578

SCL

SDA

A0

GND

12

RH1

11

RL1

RW1

10

NC

9

Ordering Information

PART NUMBER

(Note) PART MARKING

ISL22326UFV14Z* 22326 UFVZ 50 -40 to +125 14 Ld TSSOP M14.173

ISL22326UFR16Z* 223 26UFZ 50 -40 to +125 16 Ld 4x4 QFN L16.4x4A

ISL22326WFV14Z* 22326 WFVZ 10 -40 to +125 14 Ld TSSOP M14.173

ISL22326WFR16Z* 223 26WFZ 10 -40 to +125 16 Ld 4x4 QFN L16.4x4A

*Add “-TK” suffix for tape and reel. Please refer to TB347 for details on reel specifications.

NOTE: These Intersil Pb-free plastic packaged products employ special Pb-free material sets; molding compounds/die attach materials and 100%

matte tin plate PLUS ANNEAL - e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations.

Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J

STD-020.

RESISTANCE OPTION

(kΩ)

TEMP. RANGE

(°C)

PACKAGE

(Pb-free) PKG. DWG. #

1

1-888-INTERSIL or 1-888-468-3774

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

| Intersil (and design) and XDCP are registered trademarks of Intersil Americas Inc.

All other trademarks mentioned are the property of their respective owners.

Copyright Intersil Americas Inc. 2006, 2008. All Rights Reserved

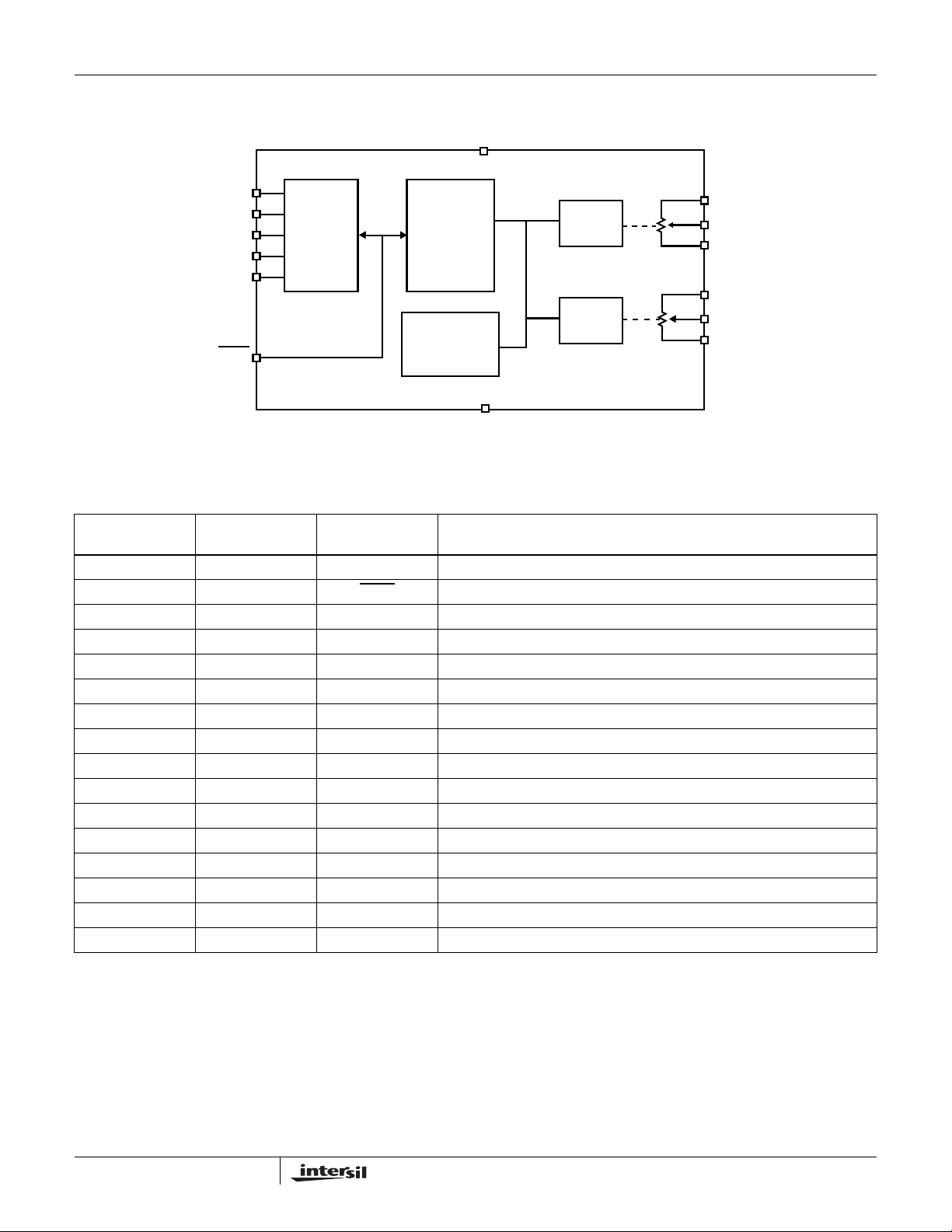

Block Diagram

www.BDTIC.com/Intersil

ISL22326

V

CC

SCL

SDA

A0

A1

A2

SHDN

I2C

INTERFACE

POWER-UP

INTERFACE,

CONTROL

AND STA TUS

LOGIC

NON-

VOLATILE

REGISTERS

GND

WR1

WR0

RH1

RW1

RL1

RH0

RW0

RL0

Pin Descriptions

TSSOP PIN

NUMBER

115V

2 16 SHDN

3 1 RH0 “High” terminal of DCP0

4 2 RL0 “Low” terminal of DCP0

5 3 RW0 “Wiper” terminal of DCP0

6 5 A2 Device address input for the I

7 6 SCL Open drain I

8 7 SDA Open drain Serial data I/O for the I

9 8 GND Device ground pin

10 10 RW1 “Wiper” terminal of DCP1

11 11 RL1 “Low” terminal of DCP1

12 12 RH1 “High” terminal of DCP1

13 13 A0 Device address input for the I

14 14 A1 Device address input for the I

*Note: PCB thermal land for QFN EPAD should be connected to GND plane or left floating. For more information refer to

http://www.intersil.com/data/tb/TB389.pdf

QFN PIN

NUMBER PIN NAME DESCRIPTION

CC

4, 9 NC No connection

EPAD* Exposed Die Pad internally connected to GND

Power supply pin

Shutdown active low input

2

C interface clock input

2

C interface

2

C interface

2

C interface

2

C interface

2

FN6176.1

February 29, 2008

ISL22326

www.BDTIC.com/Intersil

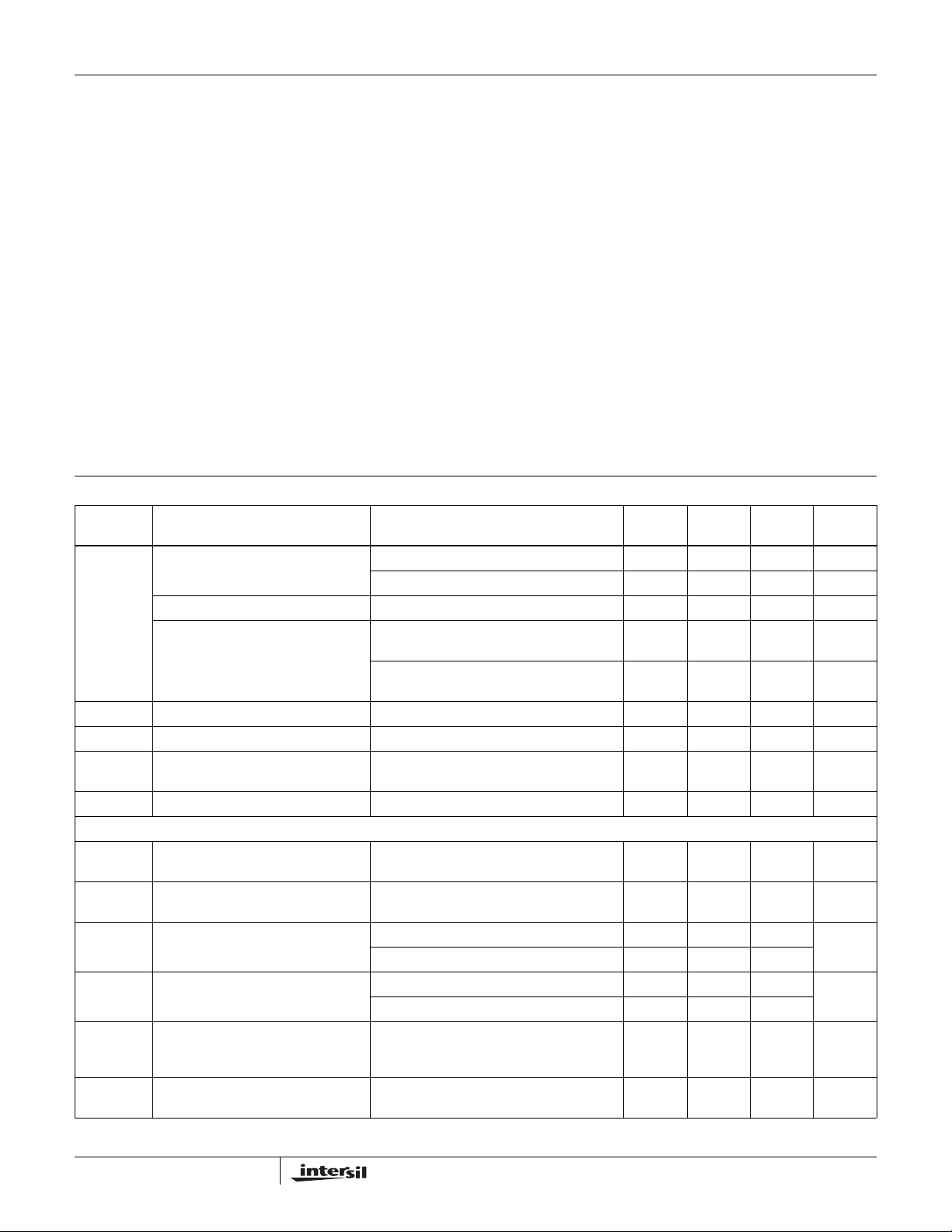

Absolute Maximum Ratings Thermal Information

Storage Temperature. . . . . . . . . . . . . . . . . . . . . . . .-65°C to +150°C

Voltage at any Digital Interface Pin

with Respect to GND . . . . . . . . . . . . . . . . . . . . -0.3V to V

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .-0.3V to +6V

V

CC

Voltage at any DCP Pin with Respect to GND. . . . . . . -0.3V to V

IW (10s) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ±6mA

Latchup (Note 3) . . . . . . . . . . . . . . . . . . Class II, Level B @ +125°C

ESD Ratings

Human Body Model . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2.5kV

Machine Model. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .350V

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and

result in failures not covered by warranty.

NOTES:

1.

θ

is measured with the component mounted on a high effective thermal conductivity test board in free air. See Tech Brief TB379 for details.

JA

2. For θ

3. Jedec Class II pulse conditions and failure criterion used. Level B exceptions are: using a max positive pulse of 6.5V on the SHDN pin, and using

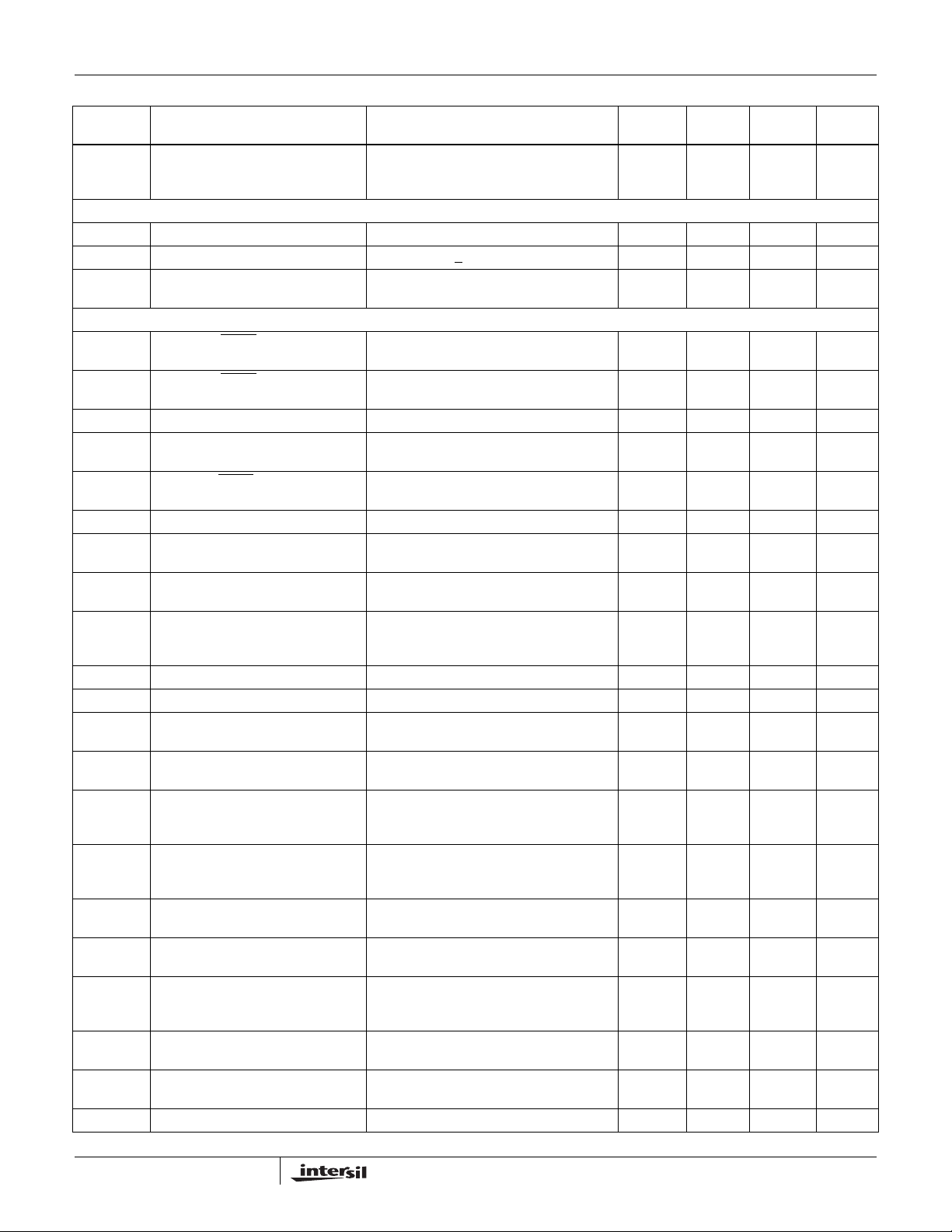

Analog Specifications Over recommended operating conditions, unless otherwise stated.

SYMBOL PARAMETER TEST CONDITIONS

R

V

C

H/CL/CW

(Note 19)

I

VOLTAGE DIVIDER MODE (0V @ R

(Note 9)

(Note 8)

ZSerror

(Note 6)

FSerror

(Note 7)

V

(Note 10)

(Note 11)

, the “case temp” location is the center of the exposed metal pad on the package underside.

JC

a max negative pulse of -0.8V for all pins.

TOTAL

R

RH

LkgDCP

INL

DNL

MATCH

TC

RH to RL Resistance W option 10 kΩ

to RL Resistance Tolerance W and U option -20 +20 %

R

H

End-to-End Temperature Coefficient W option ±50 ppm/°C

Wiper Resistance VCC = 3.3V, wiper current = VCC/R

W

, VRLVRH and VRL Terminal Voltages VRH and VRL to GND 0 V

Potentiometer Capacitance 10/10/25 pF

Leakage on DCP Pins Voltage at pin from GND to V

i; VCC @ RHi; measured at RWi, unloaded; i = 0 or 1)

L

Integral Non-linearity Monotonic over all tap positions, W and U

Differential Non-linearity Monotonic over all tap positions, W and U

Zero-scale Error W option 0 1 5 LSB

Full-scale Error W option -5 -1 0 LSB

DCP to DCP Matching Any two DCPs at same tap position, same

Ratiometric Temperature Coefficient DCP register set to 40 hex ±4 ppm/°C

V

+ 0.3

CC

CC

U option 50 kΩ

U option ±80 ppm/°C

option

option

U option 0 0.5 2

U option -2 -1 0

voltage at all RH terminals, and same voltage

at all RL terminals

Thermal Resistance (Typical, Notes 1, 2) θ

14 Lead TSSOP. . . . . . . . . . . . . . . . . . 100 N/A

16 Lead QFN . . . . . . . . . . . . . . . . . . . . 40 3.0

Maximum Junction Temperature (Plastic Package). . . . . . . .+150°C

Pb-free reflow profile . . . . . . . . . . . . . . . . . . . . . . . . . .see link below

http://www.intersil.com/pbfree/Pb-FreeReflow.asp

Recommended Operating Conditions

Temperature Range (Extended Industrial). . . . . . . .-40°C to +125°C

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2.7V to 5.5V

V

CC

Power Rating. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15mW

Wiper Current . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .±3.0mA

MIN

(Note 20)

TOTAL

CC

-1 1 LSB

-0.5 0.5 LSB

-2 2 LSB

TYP

(Note 4)

70 200 Ω

0.1 1 µA

(°C/W) θJC (°C/W)

JA

MAX

(Note 20) UNIT

(Note 17)

(Note 17)

CC

(Note 5)

(Note 5)

(Note 5)

(Note 5)

(Note 5)

V

3

FN6176.1

February 29, 2008

ISL22326

www.BDTIC.com/Intersil

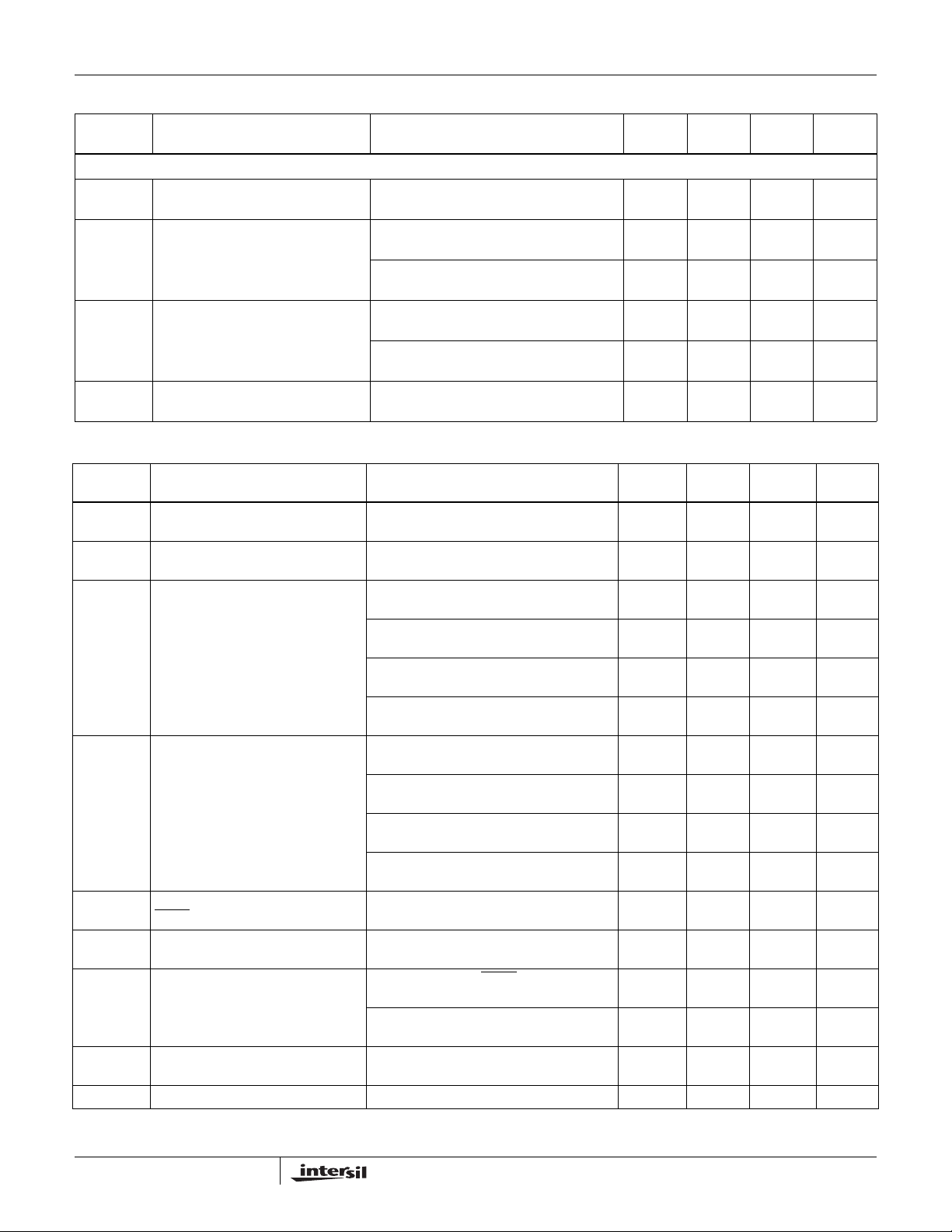

Analog Specifications Over recommended operating conditions, unless otherwise stated. (Continued)

SYMBOL PARAMETER TEST CONDITIONS

RESISTOR MODE (Measurements between RWi and RLi with RHi not connected, or between RWi and RHi with RLi not connected. i = 0 or 1)

RINL

(Note 15)

RDNL

(Note 14)

Roffset

(Note 13)

R

MATCH

(Note 16)

Integral Non-linearity DCP register set between 10h and 7Fh;

Differential Non-linearity DCP register set between 10h and 7Fh;

Offset W option 0 1 5 MI

DCP to DCP Matching Any two DCPs at the same tap position with

monotonic over all tap positions

monotonic over all tap positions, W option

DCP register set between 10h and 7Fh;

monotonic over all tap positions, U option

U option 0 0.5 2 MI

the same terminal voltages

MIN

(Note 20)

-1 1 MI

-1 1 MI

-0.5 0.5 MI

-2 2 MI

Operating Specifications Over the recommended operating conditions, unless otherwise specified.

MIN

SYMBOL PARAMETER TEST CONDITIONS

I

CC1

I

CC2

I

SB

I

SD

I

LkgDig

t

WRT

(Note 19)

t

ShdnRec

(Note 19)

Vpor Power-on Recall Voltage Minimum V

VccRamp V

VCC Supply Current (Volatile

Write/Read)

VCC Supply Current (Non-volatile

Write/Read)

VCC Current (Standby) V

VCC Current (Shutdown) V

Leakage Current, at Pins A0, A1, A2,

, SDA and SCL

SHDN

DCP Wiper Response T ime SCL falling edge of last bit of DCP data byte

DCP Recall Time from Shutdown

Mode

Ramp Rate 0.2 V/ms

CC

f

= 400kHz; SDA = Open; (for I2C, active,

SCL

read and write states)

f

= 400kHz; SDA = Open; (for I2C, active,

SCL

read and write states)

= +5.5V @ +85°C, I2C interface in

CC

standby state

= +5.5V @ +125°C, I2C interface in

V

CC

standby state

V

= +3.6V @ +85°C, I2C interface in

CC

standby state

V

= +3.6V @ +125°C, I2C interface in

CC

standby state

= +5.5V @ +85°C, I2C interface in

CC

standby state

V

= +5.5V @ +125°C, I2C interface in

CC

standby state

V

= +3.6V @ +85°C, I2C interface in

CC

standby state

= +3.6V @ +125°C, I2C interface in

V

CC

standby state

Voltage at pin from GND to V

to wiper new position

From rising edge of SHDN

stored position and RH connection

SCL falling edge of last bit of ACR data byte

to wiper stored position and RH connection

at which memory recall

occurs

CC

CC

signal to wiper

(Note 20)

-1 1 µA

2.0 2.6 V

TYP

(Note 4)

TYP

(Note 4)

1.5 µs

1.5 µs

1.5 µs

MAX

(Note 20) UNIT

MAX

(Note 20) UNIT

0.5 mA

3mA

5µA

7µA

3µA

5µA

3µA

5µA

2µA

4µA

(Note 12)

(Note 12)

(Note 12)

(Note 12)

(Note 12)

(Note 12)

4

FN6176.1

February 29, 2008

ISL22326

www.BDTIC.com/Intersil

Operating Specifications Over the recommended operating conditions, unless otherwise specified. (Continued)

MIN

SYMBOL PARAMETER TEST CONDITIONS

t

Power-up Delay VCC above Vpor, to DCP Initial Value

D

Register recall completed, and I

2

C Interface

(Note 20)

in standby state

EEPROM SPECIFICATION

EEPROM Endurance 1,000,000 Cycles

+55°C 50 Years

t

WC

EEPROM Retention Temperature T <

Non-volatile Write Cycle Time 12 20 ms

(Note 18)

SERIAL INTERFACE SPECIFICATIONS

V

V

Hysteresis

V

OL

A2, A1, A0, SHDN, SDA, and SCL

IL

Input Buffer LOW Voltage

A2, A1, A0, SHDN, SDA, and SCL

IH

Input Buffer HIGH Voltage

SDA and SCL Input Buffer Hysteresis 0.05*V

SDA Output Buffer LOW Voltage,

-0.3 0.3*V

0.7*V

CC

00.4V

Sinking 4mA

Cpin

(Note 19)

f

SCL

t

sp

t

AA

t

BUF

t

LOW

t

HIGH

t

SU:STA

t

HD:STA

t

SU:DAT

t

HD:DAT

t

SU:STO

t

HD:STO

t

DH

t

A2, A1, A0, SHDN

, SDA, and SCL Pin

Capacitance

SCL Frequency 400 kHz

Pulse Width Suppression Time at

SDA and SCL Inputs

SCL falling edge to SDA output data

valid

Time the Bus Must be Free Before the

Start of a New Transmission

Any pulse narrower than the max spec is

suppressed

SCL falling edge crossing 30% of VCC, until

SDA exits the 30% to 70% of V

window

CC

SDA crossing 70% of VCC during a STOP

condition, to SDA crossing 70% of V

during the following START condition

CC

1300 ns

Clock LOW Time Measured at the 30% of VCC crossing 1300 ns

Clock HIGH Time Measured at the 70% of VCC crossing 600 ns

START Condition Setup Time SCL rising edge to SDA falling edge; both

crossing 70% of V

CC

STAR T Condition Hold Time From SDA falling edge crossing 30% of VCC

to SCL falling edge crossing 70% of V

CC

Input Data Setup Time From SDA exiting the 30% to 70% of VCC

600 ns

600 ns

100 ns

window, to SCL rising edge crossing 30% of

V

CC

Input Data Hold Time From SCL rising edge crossing 70% of VCC

to SDA entering the 30% to 70% of V

window

STOP Condition Setup Time From SCL rising edge crossing 70% of VCC

to SDA rising edge crossing 30% of V

STOP Condition Hold Time for Read,

or Volatile Only Write

Output Data Hold Time From SCL falling edge crossing 30% of VCC,

From SDA rising edge to SCL falling edge;

both crossing 70% of V

CC

until SDA enters the 30% to 70% of V

window

SDA and SCL Rise Time From 30% to 70% of V

R

CC

CC

CC

CC

0ns

600 ns

1300 ns

0ns

20 +

0.1*Cb

t

SDA and SCL Fall Time From 70% to 30% of V

F

CC

20 +

0.1*Cb

Cb Capacitive Loading of SDA or SCL Total on-chip and off-chip 10 400 pF

CC

TYP

(Note 4)

MAX

(Note 20) UNIT

3ms

V

CC

10 pF

50 ns

900 ns

250 ns

250 ns

CC

+ 0.3 V

V

V

5

FN6176.1

February 29, 2008

ISL22326

www.BDTIC.com/Intersil

Operating Specifications Over the recommended operating conditions, unless otherwise specified. (Continued)

MIN

SYMBOL PARAMETER TEST CONDITIONS

Rpu

t

SU:A

t

HD:A

NOTES:

4. Typical values are for T

5. LSB: [V(R

incremental voltage when changing from one tap to an adjacent tap.

6. ZS error = V(RW)

7. FS error = [V(RW)

8. DNL = [V(RW)

9. INL = [V(RW)

10. V

MATCH

TC

11. for i = 16 to 112 decimal, T = -40°C to +125°C. Max( ) is the maximum value of the wiper

12. MI =

00 hex respectively.

13. Roffset = RW

Roffset = RW

14. RDNL = (RW

15. RINL = [RW

16. R

MATCH

17. for i = 16 to 112, T = -40°C to +125°C. Max( ) is the maximum value of the resistance and Min ( ) is

TC

18. t

WC

write cycle.

19. Limits should be considered typical and are not production tested.

20. Parts are 100% tested at +25°C. Temperature limits established by characterization and are not production tested.

SDA and SCL Bus Pull-up Resistor

Off-chip

A2, A1 and A0 Setup Time Before START condition 600 ns

A2, A1 and A0 Hold Time After STOP condition 600 ns

= +25°C and 3.3V supply voltage

A

– V(RW)0]/127. V(RW)

W)127

/LSB.

0

– VCC]/LSB.

127

– V(RW)

i

– i • LSB – V(RW)0]/LSB for i = 1 to 127.

i

= [V(RWx)i – V(RWy)i]/LSB, for i = 1 to 127, x = 0 to 1 and y = 0 to 1.

Max V RW()

()Min V RW()

--------------------------------------------------------------------------------------------- -

V

|RW

R

is the time from a valid STOP condition at the end of a Write sequence of I2C serial interface, to the end of the self-timed internal non-volatile

()Min V RW()

Max V RW()

– RW

127

/MI, when measuring between RW and RL.

0

/MI, when measuring between RW and RH.

127

– RW

i

– (MI • i) – RW0]/MI, for i = 16 to 127.

i

= (RW

--------------------------------------------------------------- -

– RW

i,x

Max Ri()Min Ri()–[]

Max R i()Min Ri()+[]2⁄

]/LSB-1, for i = 1 to 127. i is the DCP register setting.

i-1

i

i

|/127. MI is a minimum increment. RW

0

)/MI -1, for i = 16 to 127.

i-1

)/MI, for i = 1 to 127, x = 0 to 1 and y = 0 to 1.

i,y

127

()–

()+[]2⁄

i

10

-------------------- -

×=

+165°C

i

6

Maximum is determined by tR and t

For Cb = 400pF, max is about 2kΩ~2.5kΩ

For Cb = 40pF, max is about 15kΩ~20kΩ

and V(RW)0 are V(RW) for the DCP register set to 7F hex and 00 hex respectively . LSB is the

6

10

-------------------- -

×=

+165°C

the minimum value of the resistance over the temperature range.

voltage and Min ( ) is the minimum value of the wiper voltage over the temperature range.

and RW0 are the measured resistances for the DCP register set to 7F hex and

127

F

(Note 20)

1kΩ

TYP

(Note 4)

MAX

(Note 20) UNIT

6

FN6176.1

February 29, 2008

ISL22326

www.BDTIC.com/Intersil

SDA vs SCL Timing

SCL

t

SU:STA

(INPUT TIMING)

(OUTPUT TIMING)

SDA

SDA

A0, A1, and A2 Pin Timing

SCL

SDA

A0, A1, OR A2

t

HD:STA

t

F

START

t

SU:DAT

t

SU:A

t

HIGH

CLK 1

t

LOW

t

HD:DAT

BUF

t

HD:STO

t

SU:STO

t

HD:A

t

DH

STOP

sp

t

t

R

t

AA

t

[

Typical Performance Curves

100

VCC = 3.3V, T = +125°C

90

80

70

60

50

40

30

VCC = 3.3V, T = +20°C

20

WIPER RESISITANCE (Ω)

10

0

020406080100120

TAP POSITI ON (DECIMAL)

FIGURE 1. WIPER RESISTANCE vs T AP POSITION

[ I(RW) = V

CC/RTOTAL

] FOR 10kΩ (W)

= 3.3V, T = -40°C

V

CC

1.4

1.2

1.0

0.8

(µA)

0.6

SB

I

0.4

0.2

0

2.7 3.2 3.7 4.2 4.7 5.2

T = +125°C

T = +25°C

V

CC

FIGURE 2. STANDBY I

(V)

CC

vs V

CC

7

FN6176.1

February 29, 2008

Typical Performance Curves (Continued)

www.BDTIC.com/Intersil

0.2

T = +25°C

VCC = 2.7V

0.1

ISL22326

0.2

0.1

T = +25°C

VCC = 2.7V

0

DNL (LSB)

-0.1

VCC = 5.5V

-0.2

0 20406080100120

TAP POSITION (DECIMAL)

FIGURE 3. DNL vs TAP POSITION IN VOLTAGE DIVIDER

MODE FOR 10kΩ (W)

1.3

1.1

0.9

0.7

(LSB)

0.5

ERROR

0.3

ZS

0.1

-0.1

-0.3

-40 -20 0 20 40 60 80 100 120

FIGURE 5. ZS

10k

VCC = 5.5V

VCC = 2.7V

50k

TEMPERATURE (°C)

vs TEMPERATURE FIGURE 6. FS

ERROR

0

INL (LSB)

-0.1

VCC = 5.5V

-0.2

0 20 40 60 80 100 120

TAP POSITION (DECIMAL)

FIGURE 4. INL vs TAP POSITION IN VOL TAGE DIVIDER

MODE FOR 10kΩ (W)

0.0

-0.3

VCC = 2.7V

-0.6

(LSB)

-0.9

ERROR

ZS

-1.2

-1.5

-40 -20 0 20 40 60 80 100 120

ERROR

50k

10k

TEMPERATURE (ºC)

vs TEMPERATURE

VCC = 5.5V

0.4

0.2

0

-0.2

DNL (LSB)

-0.4

VCC = 2.7V

-0.6

16 36 56 76 96 116

VCC = 5.5V

TAP POSITION (DECIMAL)

T = +25°C

FIGURE 7. DNL vs TAP POSITION IN RHEOSTAT MODE FOR

0.4

0.2

0

-0.2

INL (LSB)

-0.4

-0.6

16 36 56 76 96 116

FIGURE 8. INL vs TAP POSITION IN RHEOST AT MODE FOR

10kΩ (W)

8

10kΩ (W)

VCC = 5.5V

TAP POSITI ON (DECIMAL)

T = +25°C

VCC = 2.7V

February 29, 2008

FN6176.1

Typical Performance Curves (Continued)

www.BDTIC.com/Intersil

1.0

0.5

CHANGE (%)

0.0

VCC = 5.5V

TOTAL

-0.5

END TO END R

-1.0

-40 -20 0 20 40 60 80 100 120

FIGURE 9. END TO END R

TEMPERATURE

VCC = 2.7V

10k

TEMPERATURE (ºC)

TOTAL

50k

% CHANGE vs

ISL22326

105

90

75

60

45

TCv (ppm/°C)

50k

30

15

0

16 36 56 76 96

10k

TAP POSITION (DECIMAL)

FIGURE 10. TC FOR VOLTAGE DIVIDER MODE IN ppm

OUTPUT

300

250

200

150

TCr (ppm/°C)

100

50

0

16 36 56 76 96

50k

TAP POSITION (DECIMAL)

10k

INPUT

WIPER AT MID POINT (POSITION 40h)

R

= 9.5kΩ

TOTAL

FIGURE 11. TC FOR RHEOSTAT MODE IN ppm FIGURE 12. FREQUENCY RESPONSE (2.6MHz)

SCL

SIGNAL AT WIPER

(WIPER UNLOADED)

WIPER MID POINT MOVEMENT

FROM 3Fh TO 40h

FIGURE 13. MIDSCALE GLITCH, CODE 3Fh TO 40h FIGURE 14. LARGE SIGNAL SETTLING TIME

9

SIGNAL AT WIPER

(WIPER UNLOADED MOVEMENT

FROM 7Fh TO 00h)

February 29, 2008

FN6176.1

ISL22326

www.BDTIC.com/Intersil

Pin Descriptions

Potentiometers Pins

RHI AND RLI (i = 0, 1)

The high (RHi) and low (RLi) terminals of the ISL22326 are

equivalent to the fixed terminals of a mechanical potentiometer.

RHi and RLi are referenced to the relative position of the wiper

and not the voltage potential on the terminals. With WRi set to

127 decimal, the wiper will be closest to RHi, and with the WRi

set to 0, the wiper is closest to RLi.

RWI (i = 0,1)

RWi is the wiper terminal and is equivalent to the movable

terminal of a mechanical potentiometer. The position of the

wiper within the array is determined by the WRi register.

SHDN

The SHDN pin forces the resistor to end-to-end open circuit

condition on RHi and shorts RWi to RLi. When SHDN

returned to logic high, the previous latch settings put RWi at

the same resistance setting prior to shutdown. This pin is

logically OR’d with SHDN bit in ACR register. I

still available in shutdown mode and all registers are

accessible. This pin must remain HIGH for normal operation.

RH

RW

RL

FIGURE 15. DCP CONNECTION IN SHUTDOWN MODE

2

Bus Interface Pins

SERIAL DATA INPUT/OUTPUT (SDA)

The SDA is a bidirectional serial data input/output pin for I

interface. It receives device address, operation code, wiper

address and data from an I

rising edge of the serial clock SCL, and it shifts out data after

each falling edge of the serial clock.

SDA requires an external pull-up resistor, since it is an open

drain input/output.

SERIAL CLOCK (SCL)

This is the serial clock input of the I

requires an external pull-up resistor, since it is an open drain

input.

DEVICE ADDRESS (A2 - A0)

The address inputs are used to set the least significant 3 bits

of the 7-bit I

address serial data stream must match with the Address

input pins in order to initiate communication with the

ISL22326. A maximum of 8 ISL22326 devices may occupy

the I

2

C interface slave address. A match in the slave

2

C serial bus.

2

C external master device at the

2

C serial interface. SCL

is

C interface is

2

C

Principles of Operation

The ISL22326 is an integrated circuit incorporating two

DCPs with their associated registers, non-volatile memory

and an I

between a host and the potentiometers and memory. The

resistor arrays are comprised of individual resistors

connected in series. At either end of the array and between

each resistor is an electronic switch that transfers the

potential at that point to the wiper.

The electronic switches on the device operate in a “make

before break” mode when the wiper changes tap positions.

When the device is powered down, the last value stored in

IVRi will be maintained in the non-volatile memory. When

power is restored, the contents of the IVRi are recalled and

loaded into the corresponding WRi to set the wipers to the

initial value.

DCP Description

Each DCP is implemented with a combination of resistor

elements and CMOS switches. The physical ends of each

DCP are equivalent to the fixed terminals of a mechanical

potentiometer (RH and RL pins). The RW pin of each DCP is

connected to intermediate nodes, and is equivalent to the

wiper terminal of a mechanical potentiometer. The position

of the wiper terminal within the DCP is controlled by volatile

Wiper Register (WR). Each DCP has its own WR. When the

WR of a DCP contains all zeroes (WR[6:0]= 00h), its wiper

terminal (RW) is closest to its “Low” terminal (RL). When the

WR register of a DCP contains all ones (WR[6:0] = 7Fh), its

wiper terminal (RW) is closest to its “High” terminal (RH). As

the value of the WR increases from all zeroes (0) to all ones

(127 decimal), the wiper moves monotonically from the

position closest to RL to the closest to RH. At the same time,

the resistance between RW and RL increases monotonically,

while the resistance between RH and RW decreases

monotonically.

While the ISL22326 is being powered up, all WRs are reset

to 40h (64 decimal), which locates RW roughly at the center

between RL and RH. After the power supply voltage

becomes large enough for reliable non-volatile memory

reading, all WRs will be reload with the value stored in

corresponding non-volatile Initial Value Registers (IVRs).

The WRs can be read or written to directly using the I

serial interface as described in the following sections. The

2

I

access the WR of DCP0 or DCP1 respectively.

Memory Description

The ISL22326 contains seven non-volatile and three volatile

8-bit registers. Memory map of ISL22326 is on Table 1. The

two non-volatile registers (IVRi) at address 0 and 1, contain

initial wiper value and volatile registers (WRi) contain current

wiper position. In addition, five non-volatile General Purpose

registers from address 2 to address 6 are available.

2

C serial interface providing direct communication

2

C

C interface Address Byte has to be set to 00h or 01h to

10

FN6176.1

February 29, 2008

ISL22326

www.BDTIC.com/Intersil

TABLE 1. MEMORY MAP

ADDRESS NON-VOLATILE VOLATILE

8— ACR

7 Reserved

6

5

4

3

2

1

0

General Purpose

General Purpose

General Purpose

General Purpose

General Purpose

IVR1

IVR0

Not Available

Not Available

Not Available

Not Available

Not Available

WR1

WR0

The non-volatile IVRi and volatile WRi registers are accessible

with the same address.

The Access Control Register (ACR) contains information

and control bits described in Table 2. The VOL bit at access

control register (ACR[7]) determines whether the access is

to wiper registers WRi or initial value registers IVRi.

TABLE 2. ACCESS CONTROL REGISTER (ACR)

VOL SHDN WIP

00000

If VOL bit is 0, the non-volatile IVRi registers are accessible. If

VOL bit is 1, only the volatile WRi are accessible. Note, value

is written to IVRi register also is written to the corresponding

WRi. The default value of this bit is 0.

The SHDN bit (ACR[6]) disables or enables Shutdown mode.

This bit is logically OR’d with SHDN

pin. When this bit is 0,

DCP is in Shutdown mode. Default value of SHDN bit is 1.

The WIP bit (ACR[5]) is read only bit. It indicates that

non-volatile write operation is in progress. It is impossible to

write to the IVRi, WRi or ACR while WIP bit is 1.

I2C Serial Interface

The ISL22326 supports an I2C bidirectional bus oriented

protocol. The protocol defines any device that sends data

onto the bus as a transmitter and the receiving device as the

receiver. The device controlling the transfer is a master and

the device being controlled is the slave. The master always

initiates data transfers and provides the clock for both

transmit and receive operations. Therefore, the ISL22326

operates as a slave device in all applications.

All communication over the I

sending the MSB of each byte of data first.

2

C interface is conducted by

Protocol Conventions

Data states on the SDA line must change only during SCL

LOW periods. SDA state changes during SCL HIGH are

reserved for indicating START and STOP conditions (see

Figure 16). On power-up of the ISL22326, the SDA pin is in

the input mode.

2

All I

C interface operations must begin with a START

condition, which is a HIGH to LOW transition of SDA while

SCL is HIGH. The ISL22326 continuously monitors the SDA

and SCL lines for the START condition and does not

respond to any command until this condition is met (see

Figure 16). A START condition is ignored during the

power-up of the device.

2

All I

C interface operations must be terminated by a STOP

condition, which is a LOW to HIGH transition of SDA while

SCL is HIGH (see Figure 16). A STOP condition at the end

of a read operation, or at the end of a write operation places

the device in its standby mode.

An ACK, Acknowledge, is a software convention used to

indicate a successful data transfer. The transmitting device,

either master or slave, releases the SDA bus after

transmitting eight bits. During the ninth clock cycle, the

receiver pulls the SDA line LOW to acknowledge the

reception of the eight bits of data (see Figure 17).

The ISL22326 responds with an ACK after recognition of a

START condition followed by a valid Identification Byte, and

once again after successful receipt of an Address Byte. The

ISL22326 also responds with an ACK after receiving a Data

Byte of a write operation. The master must respond with an

ACK after receiving a Data Byte of a read operation.

A valid Identification Byte contains 1010 as the four MSBs,

and the following three bits matching the logic values present

at pins A2, A1, and A0. The LSB is the Read/Write

value is “1” for a Read operation, and “0” for a Write operation

(see Table 3).

TABLE 3. IDENTIFICATION BYTE FORMAT

Logic values at pins A2, A1, and A0 respectively

1010A2A1A0R/W

(MSB) (LSB)

bit. Its

11

FN6176.1

February 29, 2008

SCL

www.BDTIC.com/Intersil

SDA

ISL22326

SCL FROM

MASTER

SDA OUTPUT FROM

TRANSMITTER

SDA OUTPUT FROM

RECEIVER

SIGNALS FROM

START DATA DATA STOP

STABLE CHANGE

DATA

STABLE

FIGURE 16. VALID DATA CHANGES, START AND STOP CONDITIONS

81 9

HIGH IMPEDANCE

START ACK

FIGURE 17. ACKNOWLEDGE RESPONSE FROM RECEIVER

WRITE

S

THE MASTER

T

A

IDENTIFICATION

R

T

BYTE

ADDRESS

BYTE

DATA

BYTE

HIGH IMPEDANCE

S

T

O

P

SIGNALS

FROM THE

MASTER

SIGNAL AT SDA

SIGNALS FROM

THE SLAVE

SIGNAL AT SDA

SIGNALS FROM

S

T

A

IDENTIFICATION

R

BYTE WITH

T

R/W

10100

10100

THE SLAVE

FIGURE 18. BYTE WRITE SEQUENCE

S

T

A

ADDRESS

= 0

A0A1A2 A0A1A2

BYTE

0000

A

C

K

R

T

A

C

K

FIGURE 19. READ SEQUENCE

12

0000A0A1A2 0

A

C

K

IDENTIFICATION

BYTE WITH

R/W

= 1

11100

A

C

K

A

C

K

FIRST READ

DATA BYTE

A

C

K

A

A

C

C

K

K

LAST READ

DATA BYTE

February 29, 2008

S

T

A

O

C

P

K

FN6176.1

ISL22326

www.BDTIC.com/Intersil

Write Operation

A Write operation requires a START condition, followed by a

valid Identification Byte, a valid Address Byte, a Data Byte,

and a STOP condition. After each of the three bytes, the

ISL22326 responds with an ACK. At this time, the device

enters its standby state (see Figure 18). The device can

receive more than one byte of data by auto incrementing the

address after each received byte. Note after reaching the

address 08h, the internal pointer “rolls over” to address 00h.

The non-volatile write cycle starts after STOP condition is

determined and it requires up to 20ms delay for the next

non-volatile write. Thus, non-volatile registers must be

written individually.

Read Operation

A Read operation consist of a three byte instruction followed

by one or more Data Bytes (see Figure 19). The master

initiates the operation issuing the following sequence: a

START, the Identification byte with the R/W

Address Byte, a second START, and a second Identification

byte with the R/W

the ISL22326 responds with an ACK. Then the ISL22326

transmits Data Bytes as long as the master responds with an

ACK during the SCL cycle following the eighth bit of each

byte. The master terminates the read operation (issuing a

ACK

and a STOP condition) following the last bit of the last

Data Byte (see Figure 19).

The Data Bytes are from the registers indicated by an

internal pointer. This pointer initial value is determined by the

Address Byte in the Read operation instruction, and

increments by one during transmission of each Data Byte.

After reaching the memory location 08h, the pointer “rolls

over” to 00h, and the device continues to output data for

each ACK received.

In order to read back the non-volatile IVR, it is recommended

that the application reads the ACR first to verify the WIP bit

is 0. If the WIP bit (ACR[5]) is not 0, the host should repeat

its reading sequence again.

bit set to “1”. After each of the three bytes,

bit set to “0”, an

13

FN6176.1

February 29, 2008

ISL22326

www.BDTIC.com/Intersil

Quad Flat No-Lead Plastic Package (QFN)

Micro Lead Frame Plastic Package (MLFP)

L16.4x4A

16 LEAD QUAD FLAT NO-LEAD PLASTIC PACKAGE

(COMPLIANT TO JEDEC MO-220-VGGD-10)

MILLIMETERS

SYMBOL

A 0.80 0.90 1.00 -

A1 - - 0.05 -

A2 - - 1.00 9

A3 0.20 REF 9

b 0.18 0.25 0.30 5, 8

D 4.00 BSC -

D1 3.75 BSC 9

D2 2.30 2.40 2.55 7, 8

E 4.00 BSC -

E1 3.75 BSC 9

E2 2.30 2.40 2.55 7, 8

e 0.50 BSC -

k0.25 - - -

L 0.30 0.40 0.50 8

L1 - - 0.15 10

N162

Nd 4 3

Ne 4 3

P- -0.609

θ --129

NOTES:

1. Dimensioning and tolerancing conform to ASME Y14.5-1994.

2. N is the number of terminals.

3. Nd and Ne refer to the number of terminals on each D and E.

4. All dimensions are in millimeters. Angles are in degrees.

5. Dimension b applies to the metallized terminal and is measured

between 0.15mm and 0.30mm from the terminal tip.

6. The configuration of the pin #1 identifier is optional, but must be

located within the zone indicated. The pin #1 identifier may be

either a mold or mark feature.

7. Dimensions D2 and E2 are for the exposed pads which provide

improved electrical and thermal performance.

8. Nominal dimensions are provided to assist with PCB Land

Pattern Design efforts, see Intersil Technical Brief TB389.

9. Features and dimensions A2, A3, D1, E1, P & θ are present when

Anvil singulation method is used and not present for saw

singulation.

10. Depending on the method of lead termination at the edge of the

package, a maximum 0.15mm pull back (L1) maybe present.

L minus L1 to be equal to or greater than 0.3mm.

NOTESMIN NOMINAL MAX

Rev. 2 3/06

14

FN6176.1

February 29, 2008

ISL22326

www.BDTIC.com/Intersil

Thin Shrink Small Outline Plastic Packages (TSSOP)

N

INDEX

AREA

123

0.05(0.002)

-AD

e

b

0.10(0.004) C AM BS

NOTES:

1. These package dimensions are within allowable dimensions of

JEDEC MO-153-AC, Issue E.

2. Dimensioning and tolerancing per ANSI Y14.5M-1982.

3. Dimension “D” does not include mold flash, protrusions or gate burrs.

Mold flash, protrusion and gate burrs shall not exceed 0.15mm

(0.006 inch) per side.

4. Dimension “E1” does not include interlead flash or protrusions. Interlead flash and protrusions shall not exceed 0.15mm (0.006 inch) per

side.

5. The chamfer on the body is optional. If it is not present, a visual index

feature must be located within the crosshatched area.

6. “L” is the length of terminal for soldering to a substrate.

7. “N” is the number of terminal positions.

8. Terminal numbers are shown for reference only.

9. Dimension “b” does not include dambar protrusion. Allowable dambar

protrusion shall be 0.08mm (0.003 inch) total in excess of “b” dimension at maximum material condition. Minimum space between protrusion and adjacent lead is 0.07mm (0.0027 inch).

10. Controlling dimension: MILLIMETER. Converted inch dimensions

are not necessarily exact. (Angles in degrees)

E1

-B-

SEATING PLANE

A

-C-

M

0.25(0.010) BM M

E

α

A1

0.10(0.004)

GAUGE

PLANE

0.25

0.010

A2

L

c

M14.173

14 LEAD THIN SHRINK SMALL OUTLINE PLASTIC

PACKAGE

INCHES MILLIMETERS

SYMBOL

A - 0.047 - 1.20 -

A1 0.002 0.006 0.05 0.15 -

A2 0.031 0.041 0.80 1.05 -

b 0.0075 0.0118 0.19 0.30 9

c 0.0035 0.0079 0.09 0.20 -

D 0.195 0.199 4.95 5.05 3

E1 0.169 0.177 4.30 4.50 4

e 0.026 BSC 0.65 BSC -

E 0.246 0.256 6.25 6.50 -

L 0.0177 0.0295 0.45 0.75 6

N14 147

o

α

0

o

8

o

0

o

8

NOTESMIN MAX MIN MAX

-

Rev. 2 4/06

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems.

Intersil Corporation’s quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without

notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and

reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result

from its use. No license is granted by implic atio n or other wise u nde r any p a tent or patent rights of Intersil or its subsidi aries.

For information regarding Intersil Corporation and its products, see www.intersil.com

15

FN6176.1

February 29, 2008

Loading...

Loading...