®

ISL1221

Real Time Clock/Calendar with Event Detection and Frequency Output

Data Sheet June 22, 2006

Low Power RTC with Battery Backed

SRAM and Event Detection

The ISL1221 device is a low power real time clock with

Event Detect and Time Stamp function, timing and crystal

compensation, clock/calendar, power fail indicator, periodic

or polled alarm, intelligent battery backup switching with

separate F

output and 2 Bytes of battery-backed user

OUT

SRAM.

The oscillator uses an external, low-cost 32.768kHz crystal.

The real time clock tracks time with separate registers for

hours, minutes, and seconds. The device has calendar

registers for date, month, year and day of the week. The

calendar is accurate through 2099, with automatic leap year

correction.

Ordering Information

PART

NUMBER

(Note)

ISL1221IUZ 1221Z 2.7V to 5.5V -40 to +85 10 Ld MSOP

ISL1221IUZ-T 1221Z 2.7V to 5.5V -40 to +85 10 Ld MSOP

NOTE: Intersil Pb-free products employ special Pb-free material sets;

molding compounds/die attach materials and 100% matte tin plate

termination finish, which are RoHS compliant and compatible with both

SnPb and Pb-free soldering operations. Intersil Pb-free products are

MSL classified at Pb-free peak reflow temperatures that meet or exceed

the Pb-free requirements of IPC/ JE DEC J S TD- 02 0.

PART

MARKING

V

DD

RANGE

TEMP

RANGE

(°C)

PACKAGE

(Pb-Free)

Tape and Reel

Pinout

ISL1221

(10 LD MSOP)

TOP VIEW

X1

1

X2

2

V

BAT

3

GND

4

EVIN

5 6

V

10

IRQ/EVDET

9

8

SCL

SDA

7

F

DD

OUT

FN6316.0

Features

• Real Time Clock/Calendar

- Tracks Time in Hours, Minutes, and Seconds

- Day of the Week, Day, Month, and Year

• Security and Event Functions

- Tamper detection with Time Stamp in Normal and

Battery Backed modes

- Event Detection During Battery Backed or Normal

Modes

- Selectable Event Input Sampling Rates Allows Low

Power Operation

- Selectable Glitch Filter on Event Input Monitor

• Separate F

pin with 15 Selectable Frequencies

OUT

• Single Alarm

- Settable to the Second, Minute, Hour, Day of the Week,

Day, or Month

- Single Event or Pulse Interrupt Mode

• Automatic Backup to Battery or Super Cap

• Power Failure Detection

• On-Chip Oscillator Compensation

• 2 Bytes Battery-Backed User SRAM

2

C Interface

•I

- 400kHz Data Transfer Rate

• 400nA Battery Supply Current

• Small Package

-10 Ld MSOP

• Pb-Free Plus Anneal Available (RoHS Compliant)

Applications

• Utility Meters

• Set Top Box/Modem

• POS Equipment

• Network Routers, Hubs, Switches, Bridges

• Cellular Infrastructure Equipment

• Fixed Broadband Wireless Equipment

• Test Meters/Fixtures

• Vending Machine Management

• Security and Anti Tampering Applications

- Panel/Enclosure Status

- Warranty Reporting

- Time Stamping Applications

- Patrol/Security Check (Fire or Light Equipment)

- Automotive Applications

1

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 1-888-468-3774

| Intersil (and design) is a registered trademark of Intersil Americas Inc.

All other trademarks mentioned are the property of their respective owners.

Copyright Intersil Americas Inc. 2006. All Rights Reserved

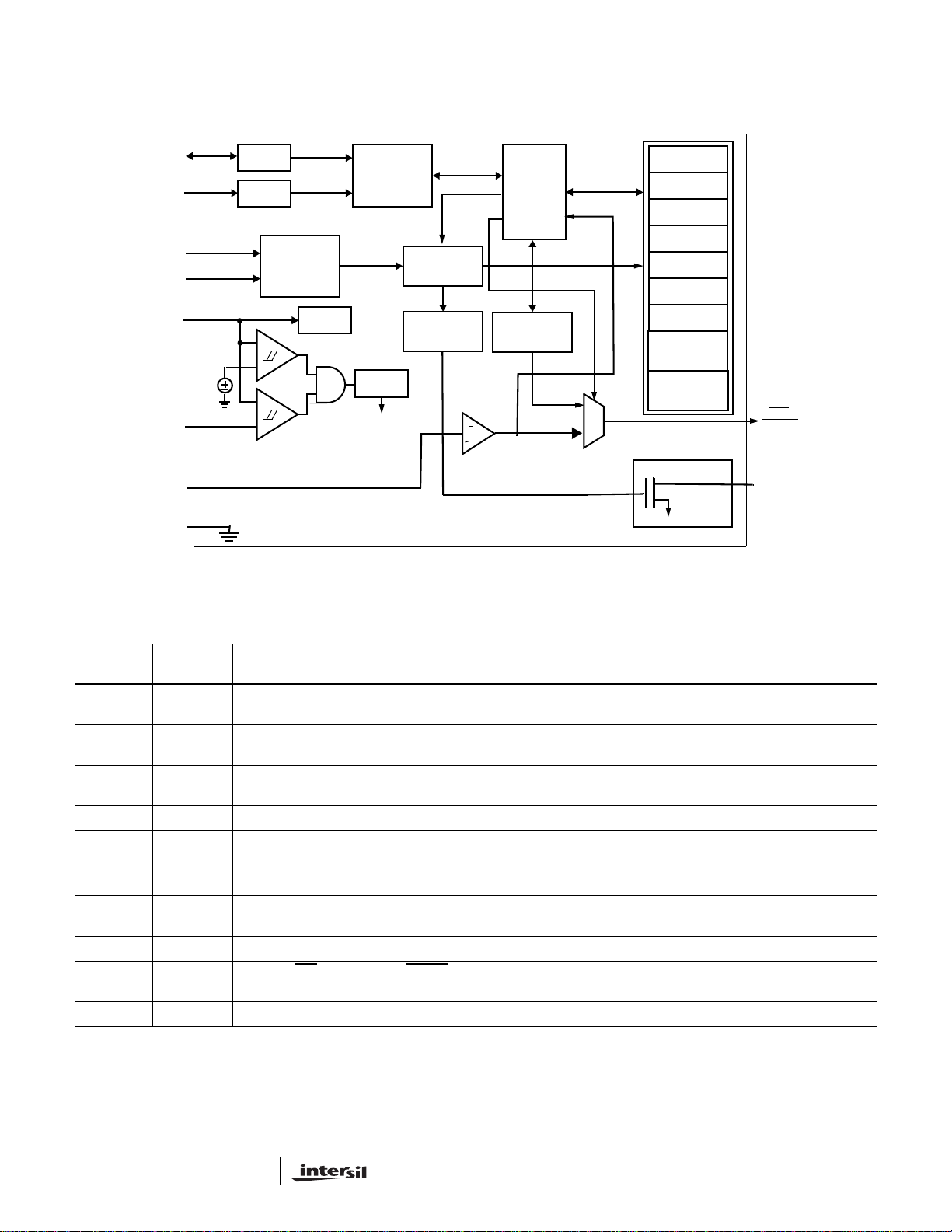

Block Diagram

ISL1221

SDA

SCL

V

DD

V

BAT

EVIN

GND

X1

X2

V

TRIP

SDA

BUFFER

SCL

BUFFER

CRYSTAL

OSCILLATOR

POR

I2C

INTERFACE

SWITCH

INTERNAL

SUPPLY

RTC

DIVIDER

FREQUENCY

OUT

CONTROL

LOGIC

ALARM

Seconds

Minutes

Hours

Day of Week

Date

Month

Year

CONTROL

REGISTERS

USER

SRAM

IRQ/

EVDET

F

OUT

Pin Descriptions

PIN

NUMBER SYMBOL DESCRIPTION

1X1X1. The X1 pin is the input of an inverting amplifier and is intended to be connected to one pin of an external

32.768kHz quartz crystal. X1 can a l s o be d r i v e n di r e c t l y from a 3 2 .7 6 8 k H z s o ur c e .

2X2X2. The X2 pin is the output of an inverting amplifier and is intended to be connected to one pin of an external

32.768kHz quartz crystal. X2 should be left open when X1 is driven from external source.

3V

BAT

4GNDGround.

5EVINEvent Input (EVIN). The EVIN is an input pin that is used to detect an externally monitored event. When a high signal

6F

OUT

7SDASerial Data (SDA). SDA is a bidirectional pin used to transfer serial data into and out of the device. It has an open

8SCLSerial Clock (SCL). The SCL input is used to clock all serial data into and out of the device.Open drain output.

9IRQ

10 V

/EVDET Interrupt (IRQ)/Event Detect (EVDET) Output. Multi-functional pin that can be used as interrupt for Alarm and Event

DD

V

This input provides a backup supply voltage to the device. V

BAT.

the V

supply fails. This pin should be tied to ground if not used.

DD

supplies power to the device in the event that

BAT

is present at the EVIN pin an “event” is detected.

Frequency Output F

, Frequency output pin, 15 selectable frequencies. Open drain output.

OUT

drain output and may be wire OR’ed with other open drain or open collector outputs.

Detect. Open Drain Output.

V

Power supply.

DD.

2

FN6316.0

June 22, 2006

ISL1221

Absolute Maximum Ratings Thermal Information

Voltage on VDD, V

(respect to ground). . . . . . . . . . . . . . . . . . . . . . . . . . -0.5V to 7.0V

Voltage on X1 and X2 Pins

(respect to ground). . . . . . . . . . . .-0.5V to V

Maximum Junction Temperature (Plastic Package). . . . . . . . . 150°C

Storage Temperature. . . . . . . . . . . . . . . . . . . . . . . .-65°C to +150°C

Lead Temperature (Soldering, 10s) . . . . . . . . . . . . . . . . . . . . .300°C

ESD Rating (Human Body Model). . . . . . . . . . . . . . . . . . . . . . .>2kV

ESD Rating (Machine Model . . . . . . . . . . . . . . . . . . . . . . . . . .>175V

Output Current Sink (F

CAUTION: Stresses above those listed in “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress only rating and operation of the

device at these or any other conditions above those indicated in the operational sections of this specification is not implied .

NOTE:

is measured with the component mounted on a high effective thermal conductivity test board in free air. See Tech Brief TB379 for details.

1. θ

JA

, SCL, SDA, and IRQ/EVDET Pins

BAT

-0.5V to V

, IRQ . . . . . . . . . . . . . . . . . . . . . . . . 3mA

OUT

DD

BAT

+ 0.5 (V

+ 0.5 (VDD Mode)

Mode)

BAT

θ

Thermal Resistance (Typical, Note 1)

JA

(°C/W)

10Ld MSOP Package. . . . . . . . . . . . . . . . . . . . . . . . 120

Moisture Sensitivity (see Technical Brief TB363). . . . . . . . . . Level 2

Recommended Operating Conditions

Ambient Temperature . . . . . . . . . . . . . . . . . . . . . . . . .-40°C to 85°C

V

Voltage. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2.7V to 5.5V

DD

V

Voltage. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1.8V to 5.5V

BAT

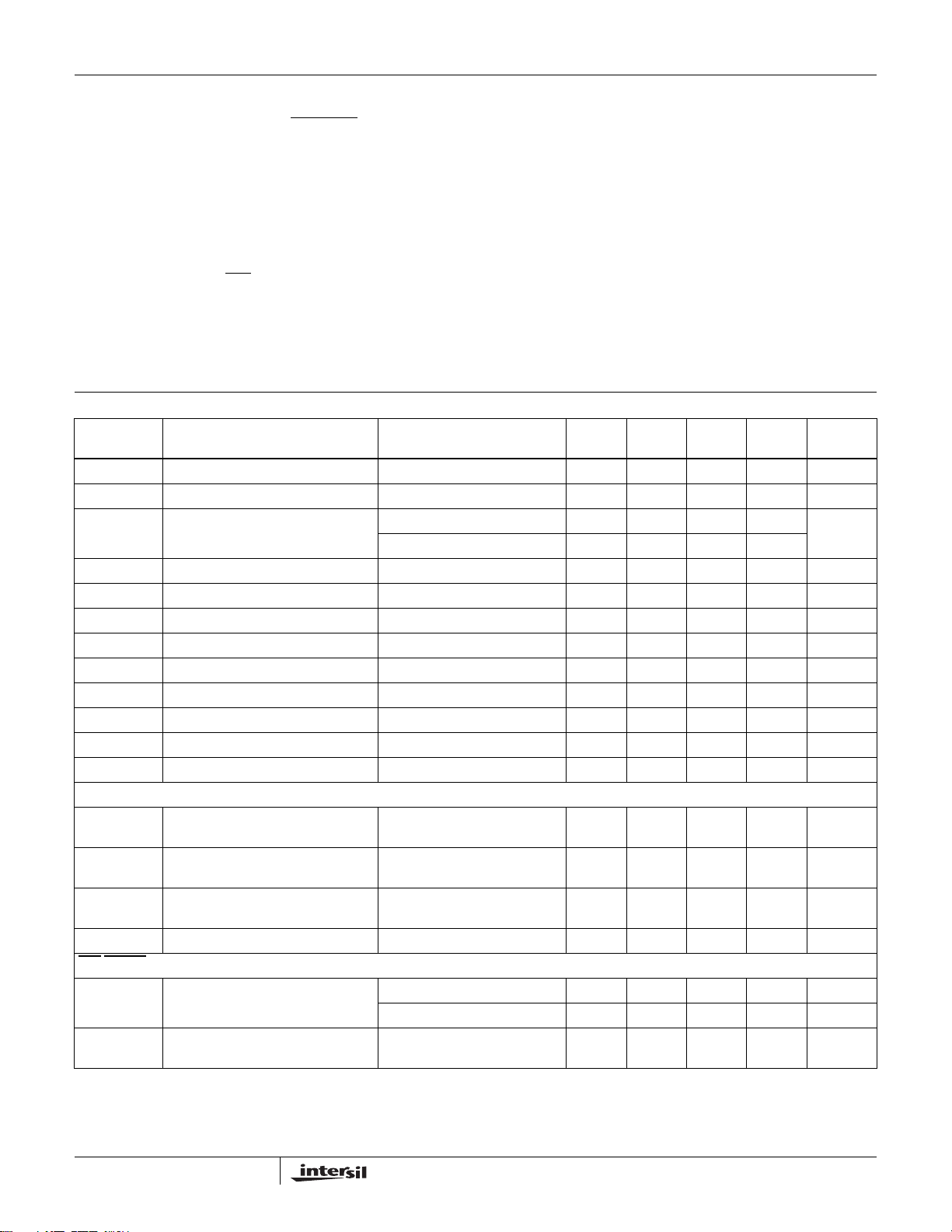

DC Operating Characteristics – RTC Test Conditions: V

= +2.7 to +5.5V, Temperature = -40°C to +85°C, unless otherwise stated.

DD

SYMBOL PARAMETER CONDITIONS MIN

V

DD

V

BAT

I

DD1

I

DD2

I

DD3

I

BAT

I

BATLKG

I

LI

I

LO

V

TRIP

V

TRIPHYS

V

BATHYS

Main Power Supply 2.7 5.5 V

Battery Supply Voltage 1.8 5.5 V

Supply Current VDD = 5V 2 6 µA 2, 3

V

= 3V 1.2 4 µA

DD

Supply Current With I2C Active VDD = 5V 40 120 µA 2, 3

Supply Current (Low Power Mode) VDD = 5V, LPMODE = 1 1.4 5 µA 2, 8

Battery Supply Current V

Battery Input Leakage VDD = 5.5V, V

= 3V 400 950 nA 2

BAT

= 1.8V 100 nA

BAT

Input Leakage Current on SCL 100 nA

I/O Leakage Current on SDA 100 nA

V

Mode Threshold 1.6 2.2 2.64 V

BAT

V

Hysteresis 10 35 60 mV

TRIP

V

Hysteresis 10 50 100 mV

BAT

EVIN

V

IL

V

IH

-0.3 0.3 x

0.7 x

V

DD

Hysteresis 0.05 x

V

DD

I

EVPU

IRQ

/EVDET and F

V

OL

I

LO

EVIN Pullup Current V

OUT

= 3V 1.5 µA 6

SUP

Output Low Voltage VDD = 5V, IOL = 3mA 0.4 V

= 2.7V, IOL = 1mA 0.4 V

V

DD

Output Leakage Current VDD = 5.5V

V

= 5.5V

OUT

TYP

(Note 5) MAX UNITS NOTES

V

V

DD

VDD +

V

0.3

V

100 400 nA

3

FN6316.0

June 22, 2006

ISL1221

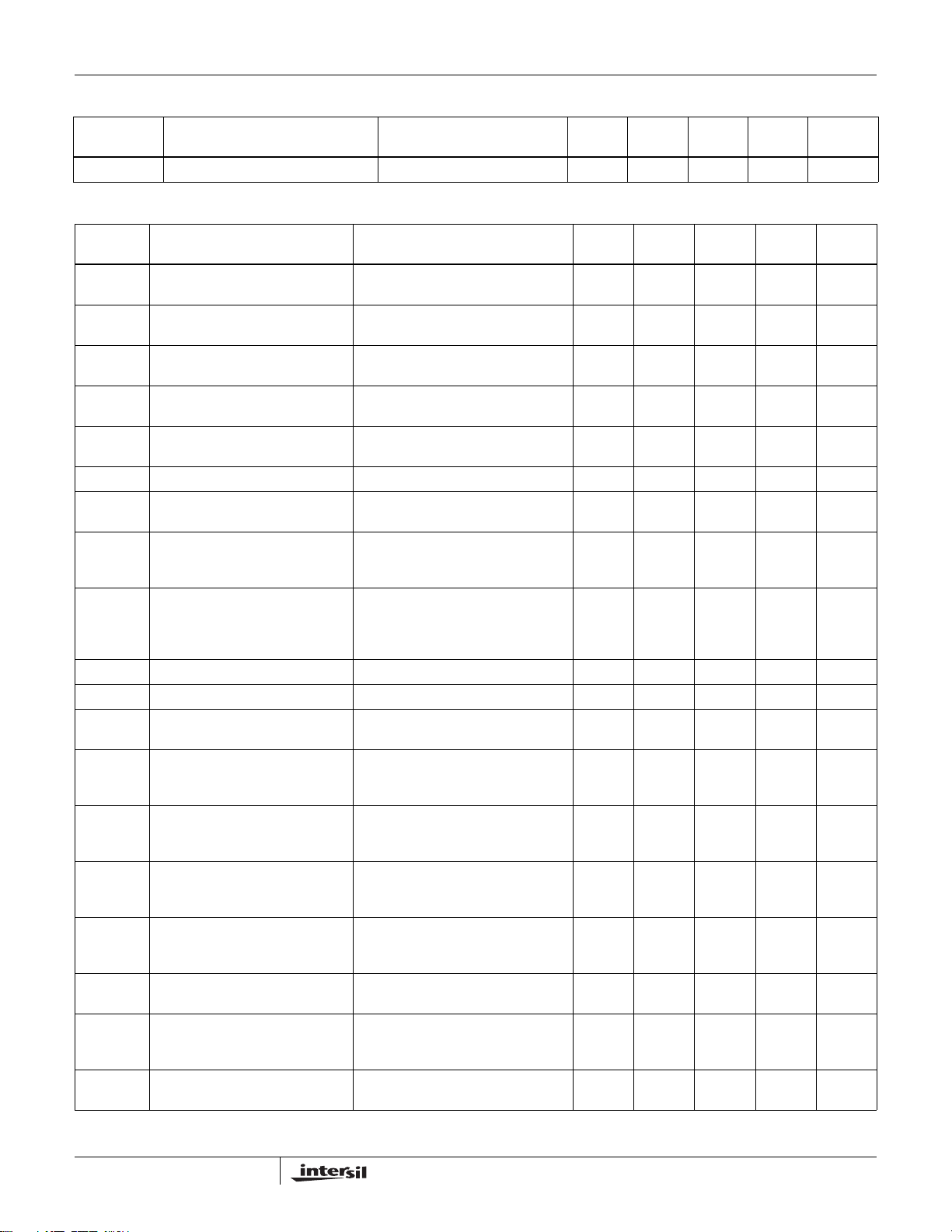

Power-Down Timing Test Conditions: V

= +2.7 to +5.5V, Temperature = -40°C to +85°C, unless otherwise stated.

DD

SYMBOL PARAMETER CONDITIONS MIN

V

DD SR-

I2C Interface Specifications Test Conditions: V

VDD Negative Slew rate 10 V/ms 4

= +2.7 to +5.5V, Temperature = -40°C to +85°C, unless otherwise specified.

DD

SYMBOL PARAMETER TEST CONDITIONS MIN

V

IL

V

IH

SDA and SCL Input Buffer LOW

Voltage

SDA and SCL Input Buffer HIGH

Voltage

Hysteresis SDA and SCL Input Buffer

Hysteresis

V

OL

Cpin SDA and SCL Pin Capacitance T

f

SCL

t

IN

t

AA

SDA Output Buffer LOW Voltage,

VDD = 5V, IOL = 3mA 0.4 V

Sinking 3mA

= 25°C, f = 1MHz, VDD=5V,

A

V

=0V, V

IN

OUT

=0V

SCL Frequency 400 kHz

Pulse Width Suppression Time at

SDA and SCL Inputs

SCL falLing Edge to SDA Output

Data Valid

Any pulse narrower than the max spec

is suppressed.

SCL falling edge crossing 30% of VDD,

until SDA exits the 30% to 70% of V

DD

window.

t

BUF

t

LOW

t

HIGH

t

SU:STA

t

HD:STA

t

SU:DAT

t

HD:DAT

t

SU:STO

t

HD:STO

t

DH

t

R

Time the Bus Must be Free Before

the Start of a New Transmission

SDA crossing 70% of VDD during a

STOP condition, to SDA crossing 70%

of V

during the following START

DD

condition.

Clock LOW Time Measured at the 30% of VDD crossing. 1300 ns

Clock HIGH Time Measured at the 70% of VDD crossing. 600 ns

START Condition Setup Time SCL rising edge to SDA falling edge.

Both crossing 70% of V

DD

.

START Condition Hold Time From SDA falling edge crossing 30%

of V

to SCL falling edge crossing

DD

70% of V

DD

.

Input Data Setup Time From SDA exiting the 30% to 70% of

V

window, to SCL rising edge

DD

crossing 30% of V

DD.

Input Data Hold Time From SCL falling edge crossing 30% of

V

to SDA entering the 30% to 70%

DD

of V

window.

DD

STOP Condition Setup Time From SCL rising edge crossing 70% of

V

, to SDA rising edge crossing 30%

DD

of V

.

DD

STOP Condition Hold Time From SDA rising edge to SCL falling

edge. Both crossing 70% of V

DD

.

Output Data Hold Time From SCL falling edge crossing 30% of

V

, until SDA enters the 30% to 70%

DD

of V

window.

DD

SDA and SCL Rise Time From 30% to 70% of V

DD.

TYP

(Note 5) MAX UNITS NOTES

TYP

(Note 5) MAX UNITS NOTES

-0.3 0.3 x

V

0.7 x

V

DD

VDD +

0.3

0.05 x

V

DD

DD

V

V

V

10 pF

50 ns

900 ns

1300 ns

600 ns

600 ns

100 ns

0 900 ns

600 ns

600 ns

0ns

20 +

300 ns 7

0.1 x Cb

4

FN6316.0

June 22, 2006

ISL1221

I2C Interface Specifications Test Conditions: V

= +2.7 to +5.5V, Temperature = -40°C to +85°C, unless otherwise specified.

DD

TYP

SYMBOL PARAMETER TEST CONDITIONS MIN

t

F

SDA and SCL Fall Time From 70% to 30% of V

DD.

20 +

(Note 5) MAX UNITS NOTES

300 ns 7

0.1 x Cb

Cb Capacitive Loading of SDA or SCL Total on-chip and off-chip 10 400 pF 7

Rpu SDA and SCL Bus Pull-up Resistor

Off-chip

Maximum is determined by t

For Cb = 400pF, max is about

and tF.

R

1kΩ 7

2~2.5kΩ. For Cb = 40pF, max is about

15~20kΩ

NOTES:

2. IRQ

and F

and EVDET Inactive.

OUT

3. LPMODE = 0 (default).

4. In order to ensure proper timekeeping, the V

specification must be followed.

DD SR-

5. Typical values are for T = 25°C and 3.3V supply voltage.

6. V

7. These are I

= VDD if in V

SUP

2

C specific parameters and are not directly tested, however they are used during device testing to validate device specification.

8. A write to register 08h should only be done if V

DD

Mode, V

SUP

= V

BAT

if in V

DD

Mode.

BAT

> V

, otherwise the device will be unable to communicate using I2C.

BAT

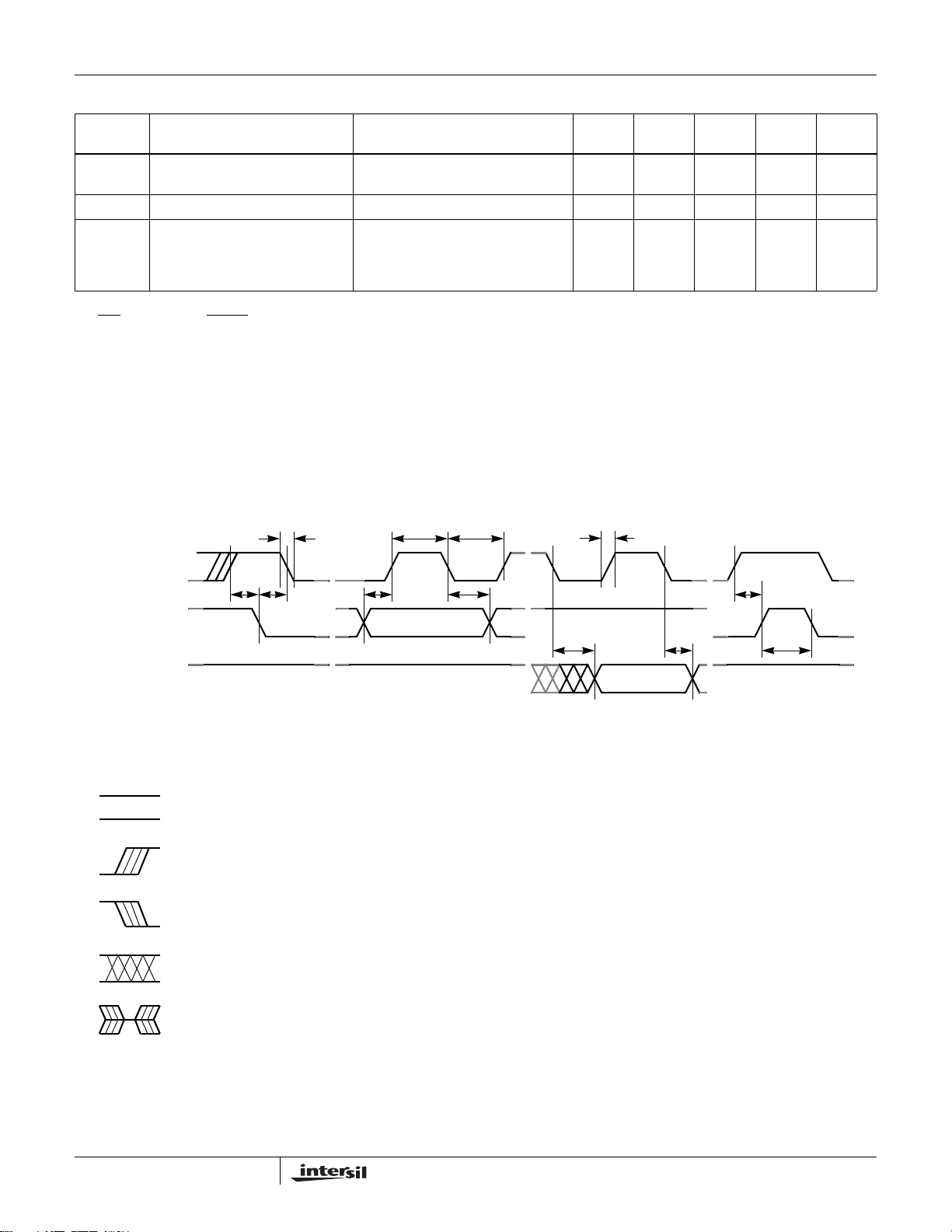

SDA vs. SCL Timing

t

F

t

HIGH

t

LOW

t

R

SCL

t

(INPUT TIMING)

(OUTPUT TIMING)

SDA

SDA

SU:STA

t

HD:STA

Symbol Table

WAVEFORM INPUTS OUTPUTS

Must be steady Will be steady

May change

from LOW

to HIGH

May change

from HIGH

to LOW

Don’t Care:

Changes Allowed

N/A Center Line is

t

SU:DAT

Will change

from LOW

to HIGH

Will change

from HIGH

to LOW

Changing:

State Not Known

High Impedance

t

HD:DAT

t

SU:STO

t

DH

t

AA

t

BUF

5

FN6316.0

June 22, 2006

ISL1221

VDD

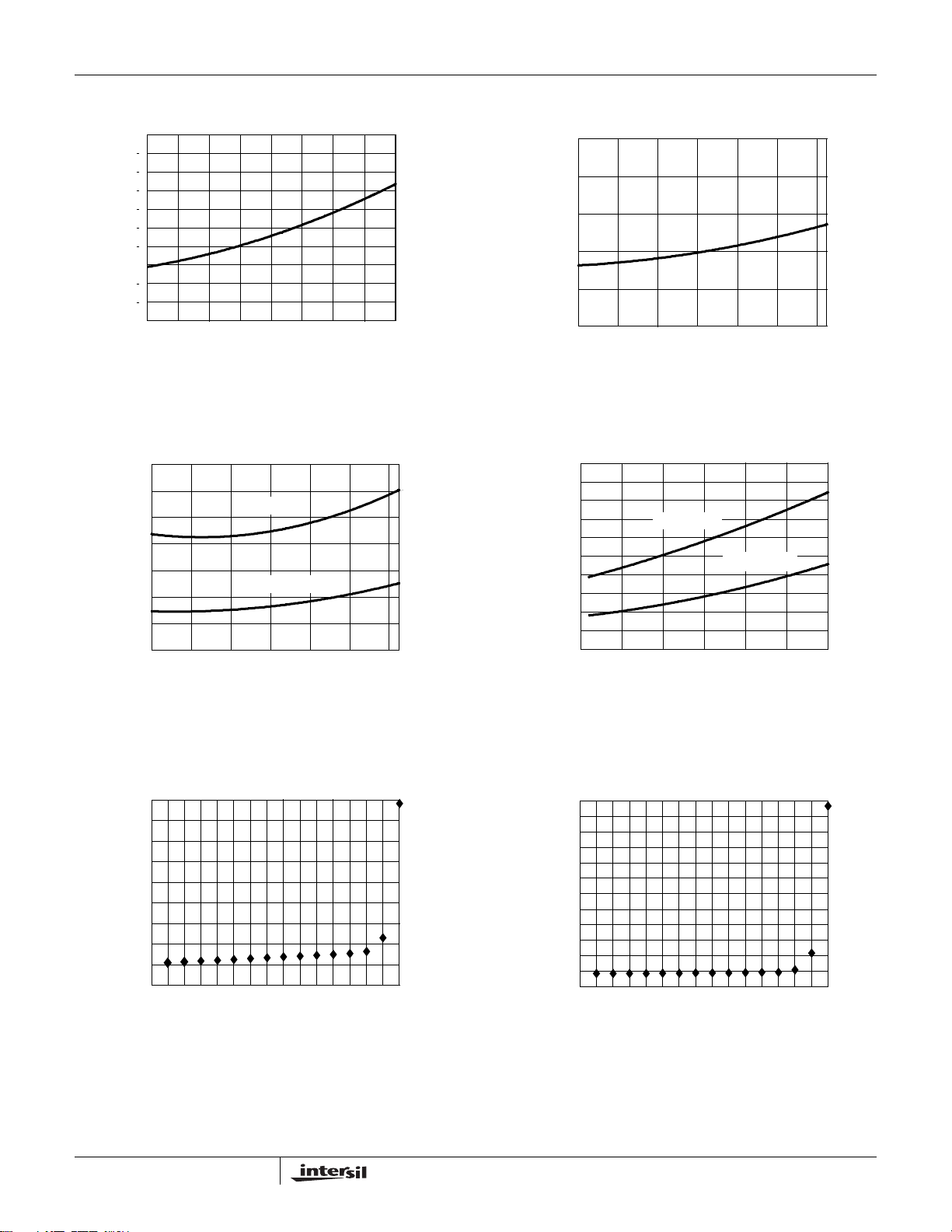

Typical Performance Curves Temperature is +25°C unless otherwise specified

1E-6

900E-9

800E-9

700E-9

600E-9

500E-9

BAT (A)

I

400E-9

300E-9

200E-9

100E-9

000E+0

1.5 2.0 2.5 3.0 3.5 4.0 4.5 5.0 5.5

(V)

V

BAT

2.4E-06

2.2E-06

2.0E-06

1.8E-06

(A)

1.6E-06

DD1

I

1.4E-06

1.2E-06

1.0E-06

FIGURE 1. I

-40-200 20406080

TEMPERATURE (°C)

FIGURE 3. I

DD1

vs V

BAT

VDD= 5V

VDD= 3.3V

vs TEMPERATURE FIGURE 4. I

BAT

1E-6

800E-9

600E-9

BAT (A)

I

400E-9

200E-9

000E+0

FIGURE 2. I

2.4E-6

2.2E-6

2.0E-6

1.8E-6

1.6E-6

(A)

1.4E-6

DD1

I

1.2E-6

1.0E-6

800.0E-9

600.0E-9

400.0E-9

-40-200 20406080

TEMPERATURE (°C)

vs TEMPERATURE AT V

BAT

LPMODE = 0

LPMODE = 1

2.53.03.54.04.55.05.5

V

(V)

DD

vs VDD WITH LPMODE ON AND OFF

DD1

BAT

= 3V

(A)

DD1

I

2.1E-6

2.0E-6

1.9E-6

1.8E-6

1.7E-6

1.6E-6

1.5E-6

1.4E-6

1.3E-6

1.2E-6

1/8

1/32

1/16

FIGURE 5. I

1/4

DD1

1

1/2

F

OUT (Hz)

vs F

6

2

OUT

4

AT V

3.0E-6

2.9E-6

2.8E-6

2.7E-6

2.6E-6

2.5E-6

(A)

2.4E-6

DD1

2.3E-6

I

2.2E-6

2.1E-6

2.0E-6

1.9E-6

8

16

64

32

= 3.3V FIGURE 6. I

DD

1024

4096

32768

1.8E-6

1

4

2

8

16

64

1/16

DD1

F

OUT (Hz)

vs F

OUT

1/2

1/4

1/8

1/32

32

AT VDD = 5V

4096

1024

June 22, 2006

32768

FN6316.0

D

ISL1221

Typical Performance Curves Temperature is +25°C unless otherwise specified (Continued)

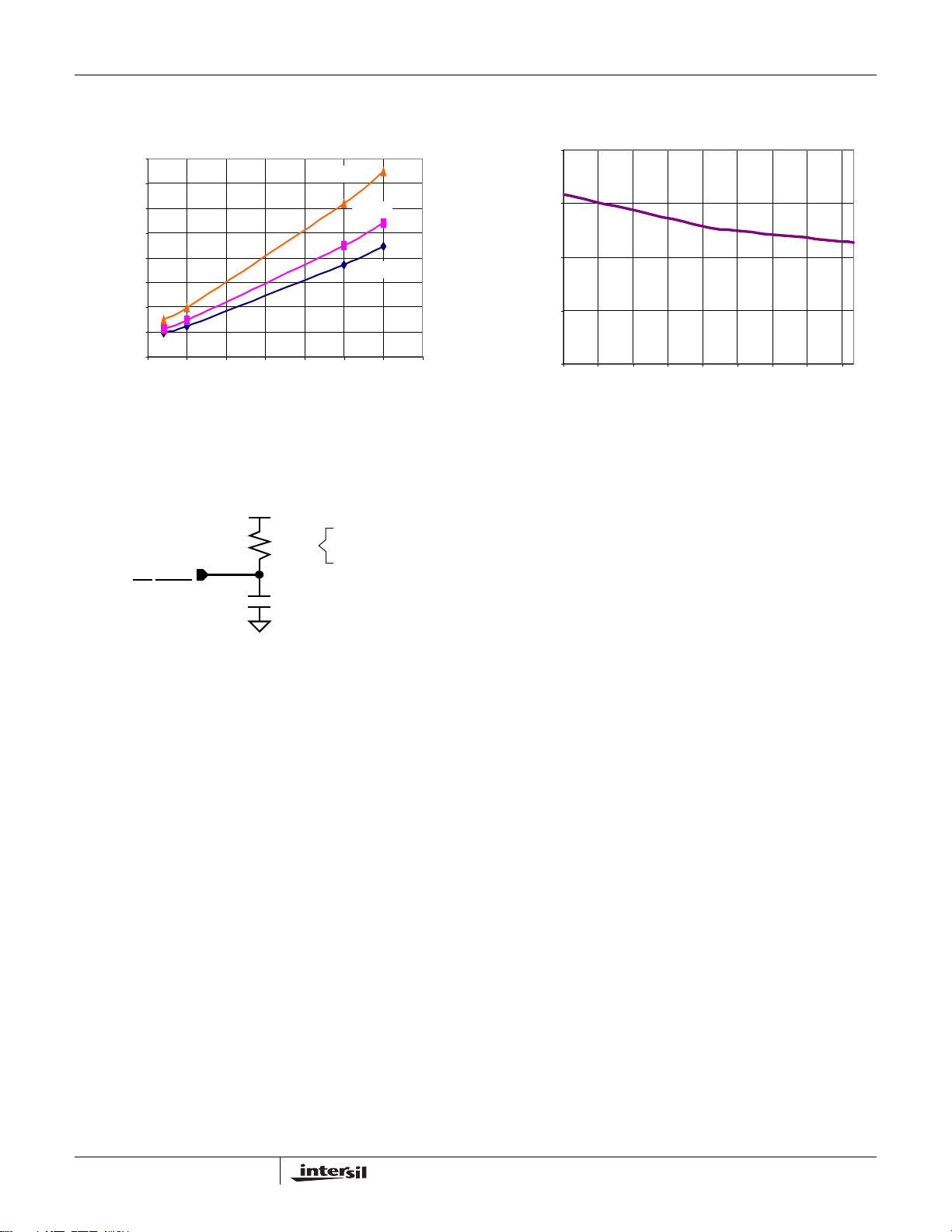

8.00E-06

7.00E-06

6.00E-06

5.00E-06

4.00E-06

PULLUP

I

3.00E-06

2.00E-06

1.00E-06

0.00E+00

2.533.544.555.56

V

D

FIGURE 7. EVIN I

EQUIVALENT AC OUTPUT LOAD CIRCUIT FOR V

SDA

AND

/EVDET

IRQ

FIGURE 9. STANDARD OUTPUT LOAD FOR TESTING THE

DEVICE WITH V

5.0V

DD

PULLUP

1533Ω

100pF

= 5.0V

-40°C

+25°C

vs V

DD

FOR VOL= 0.4V

AND I

+85°C

DD

= 3mA

OL

= 5V

5.0E-07

4.0E-07

3.0E-07

PULLUP

I

2.0E-07

1.0E-07

-40 -25 -10 5 20 35 50 65 80

Temperature

FIGURE 8. I

vs TEMPERATURE AT V

PULLUP

BAT

= 1.8V

hours, minutes, and seconds. The device has calendar

registers for date, month, year and day of the week. The

calendar is accurate through 2099, with automatic leap year

correction.

The ISL1221's alarm can be set to any clock/calendar value

for a match. For example, every minute, every Tuesday or at

5:23 AM on March 21. The alarm status is available by

checking the Status Register, or the device can be

configured to provide a hardware interrupt via the IRQ pin.

There is a repeat mode for the alarm allowing a periodic

interrupt every minute, every hour, every day, etc.

General Description

The ISL1221 device is a low power Real Time Clock with

Security and Event function, Time Stamp in both normal and

battery modes, timing and crystal compensation,

clock/calendar, power fail indicator, periodic or polled alarm,

intelligent battery backup switching, and battery-backed user

SRAM.

The Event Detection function can be used for tamper

detection, security or other chassis or generic system

monitoring. Upon a valid event detection, the ISL1221 sets

the Event Detection bit (EVT bit) in the status register, stores

time stamp information on board memory, and, can

optionally: 1) Issue an Event Output signal (EVDET pin), 2)

At the time the event occurred, stop the RTC registers from

advancing. The event monitor and time stamp functions in

both main VDD and battery back up modes. The event

monitor can also be configured for various input detection

rates to optimize power consumption for the application. In

addition, the Event Monitor pin (EVIN) has a selectable glitch

filter to avoid switch de-bouncing.

The oscillator uses an external, low-cost 32.768kHz crystal.

The real time clock tracks time with separate registers for

The device also offers a backup power input pin. This V

BAT

pin allows the device to be backed up by battery or

SuperCap with automatic switchover from V

entire ISL1221 device is fully operational from V

DD

to V

DD

. The

BAT

=2.7V to

5.5V and the clock/calendar portion of the device remains

fully operational in battery backup mode down to 1.8V

(Standby Mode).

Pin Description

X1, X2

The X1 and X2 pins are the input and output, respectively, of

an inverting amplifier. An external 32.768kHz quartz crystal

is used with the ISL1221 to supply a timebase for the real

time clock. Internal compensation circuitry provides high

accuracy over the operating temperature range from

-40°C to +85°C. This oscillator compensation network can

be used to calibrate the crystal timing accuracy over

temperature either during manufacturing or with an external

temperature sensor and microcontroller for active

compensation. The device can also be driven directly from a

32.768kHz source at pin X1.

7

FN6316.0

June 22, 2006

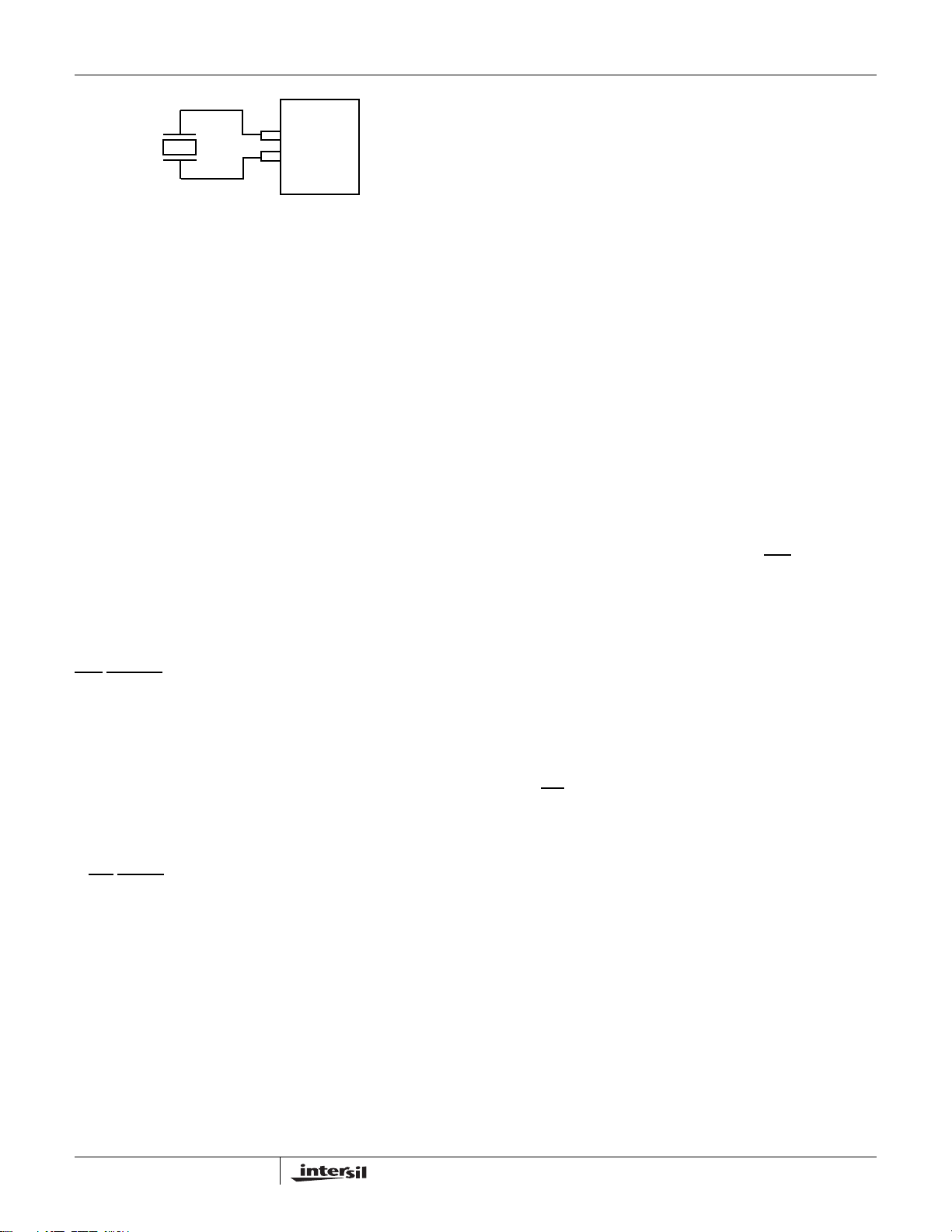

X1

X2

FIGURE 10. RECOMMENDED CRYSTAL CONNECTION

V

BAT

This input provides a backup supply voltage to the device.

V

supplies power to the device in the event that the VDD

BAT

supply fails. This pin can be connected to a battery, a Super

Cap or tied to ground if not used.

EVIN (Event Input)

The EVIN pin is an input that is used to detect an externally

monitored event. When a high signal is present at the EVIN

pin, an “event” is detected. This input may be used for

various monitoring functions, such as the opening of a

detection switch on a chassis or door. The event detection

circuit can be user enabled or disabled (see EVEN bit) and

provides the option to be operational in battery backup

modes (see EVBATB bit). When the event detection is

disabled the EVIN pin is gated OFF. See functional

Description for more details.

F

(Frequency Output)

OUT

The F

pin outputs a clock signal which is related to the

OUT

crystal frequency. The frequency output is user selectable

and enabled via the I

2

C bus. It is an open drain active low

output. When not used, the output is high.

IRQ/EVDET (Alarm/Event Detect Output)

This dual function pin can be used as an interrupt alarm or

event detect output pin. Checking the status register will

show the type of interrupt, Alarm or Event Detect.

• Interrupt Mode. The pin provides an interrupt signal

output. This signal notifies a host processor that an alarm

has occurred and requests action. It is an open drain

active low output.

• The output will go low when an event is detected at the

EVIN pin. If the event detection function is enabled, the

/EVDET output will go low and stay low until the EVT

IRQ

bit is cleared (see EVIN pin description).

Serial Clock (SCL)

The SCL input is used to clock all serial data into and out of

the device. The input buffer on this pin is always active (not

gated). It is disabled when the backup power supply on the

V

pin is activated to minimize power consumption.

BAT

Serial Data (SDA)

SDA is a bidirectional pin used to transfer data into and out

of the device. It has an open drain output and may be ORed

with other open drain or open collector outputs. The input

buffer is always active (not gated) in normal mode.

ISL1221

An open drain output requires the use of a pull-up resistor.

The output circuitry controls the fall time of the output signal

with the use of a slope controlled pull-down. The circuit is

designed for 400kHz I

when the backup power supply on the V

2

C interface speeds. It is disabled

pin is activated.

BAT

VDD, GND

Chip power supply and ground pins. The device will operate

with a power supply from V

capacitor is recommended on the V

=2.7V to 5.5VDC. A 0.1µF

DD

pin to ground.

DD

Functional Description

Power Control Operation

The power control circuit accepts a VDD and a V

Many types of batteries can be used with Intersil RTC

products. For example, 3.0V or 3.6V Lithium batteries are

appropriate, and battery sizes are available that can power

the ISL1221 for up to 10 years. Another option is to use a

Super Cap for applications where V

is interrupted for up

DD

to a month. See the Applications Section for more

information.

Normal Mode (VDD) to Battery Backup Mode

(V

)

BAT

To transition from the VDD to V

following conditions must be met:

Condition 1:

V

< V

DD

where V

- V

BAT

BATHYS

BATHYS

≈ 50mV

Condition 2:

VDD < V

where V

TRIP

TRIP

≈ 2.2V

Battery Backup Mode (V

(V

)

DD

The ISL1221 device will switch from the V

when one

Condition 1:

Condition 2:

of the following conditions occurs:

V

> V

DD

where V

VDD > V

where V

+ V

BAT

BATHYS

+ V

TRIP

TRIPHYS

BATHYS

≈ 50mV

TRIPHYS

≈ 30mV

mode, both of the

BAT

) to Normal Mode

BAT

BAT

input.

BAT

to VDD mode

8

FN6316.0

June 22, 2006

Loading...

Loading...