Intersil IRFF9120 Datasheet

IRFF9120

Data Sheet June 1999

4A, 100V, 0.60 Ohm, P-Channel Power

MOSFET

This P-Channel enhancement mode silicon gate power

field effect transistor is designed for applications such as

switching regulators, switching converters, motor drivers,

relay drivers, and drivers for high power bipolar switching

transistors requiring high speed and low gate drive power.

These types can be operated directly from integrated

circuits.

Formerly developmental type TA17501.

Ordering Information

PART NUMBER PACKAGE BRAND

IRFF9120 TO-205AF IRFF9120

NOTE: When ordering, use the entire part number.

File Number

Features

• 4A, 100V

DS(ON)

= 0.60Ω

•r

• Single Pulse Avalanche Energy Rated

• SOA is Power-Dissipation Limited

• Nanosecond Switching Speeds

• Linear Transfer Characteristics

• High Input Impedance

Symbol

D

G

S

2287.2

Packaging

JEDEC TO-205AF

DRAIN

(CASE)

SOURCE

GATE

4-94

CAUTION: These devices are sensitive to electrostatic discharge; follow proper ESD Handling Procedures.

http://www.intersil.com or 407-727-9207

| Copyright © Intersil Corporation 1999

IRFF9120

Absolute Maximum Ratings T

= 25oC, Unless Otherwise Specified

C

IRFF9120 UNITS

Drain to Source Voltage (Note 1). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . V

Drain to Gate Voltage (RGS = 20kΩ) (Note 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . V

DGR

Continuous Drain Current, TC = 25oC. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . I

Pulsed Drain Current (Note 3) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . I

Gate to Source Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . V

Maximum Power Dissipation, (Figure 14) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . P

DS

D

DM

GS

D

-100 V

-100 V

-4 A

-16 A

±20 V

20 W

Linear Derating Factor (Figure 14). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0.16 W/oC

Single Pulse Avalanche Energy Rating (Note 4) . . . . . . . . . . . . . . . . . . . . . . . . . . . . E

Operating and Storage Temperature . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . TJ,T

AS

STG

Maximum Temperature for Soldering

Leads at 0.063in (1.6mm) from Case for 10s. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . T

Package Body for 10s, See Techbrief 334 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . T

CAUTION: Stresses above those listed in “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress only rating and operationofthe

device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

L

pkg

370 mJ

-55 to 150

300

260

o

C

o

C

o

C

NOTE:

1. TJ= 25oC to 125oC.

Electrical Specifications T

= 25oC, Unless Otherwise Specified

C

PARAMETER SYMBOL TEST CONDITIONS MIN TYP MAX UNITS

Drain to Source Breakdown Voltage BV

Gate Threshold Voltage V

GS(TH)

Zero Gate Voltage Drain Current I

On-State Drain Current (Note 2) I

D(ON)VDS

Gate to Source Leakage Forward I

Gate to Source Leakage Reverse IG

Drain to Source On-State Resistance (Note 2) r

DS(ON)VGS

Forward Transconductance (Note 2) g

Turn-On Delay Time t

D(ON)VDD

Rise Time t

Turn-Off Delay Time t

D(OFF)

Fall Time t

Total Gate Charge

(Gate to Source + Gate to Drain)

Q

G(TOT)VGS

Gate to Source Charge Q

Gate to Drain “Miller” Charge Q

Input Capacitance C

Output Capacitance C

Reverse Transfer Capacitance C

Internal Drain Inductance L

Internal Source Inductance L

DSSVGS

DSS

GSS

SS

fs

r

f

GS

GD

ISS

OSS

RSS

D

S

= 0V, ID = 250µA -100 - - V

VDS = VGS, ID = 250µA -2.0 - -4.0 V

VDS = Max Rating, VGS = 0V - - -250 µA

= Max Rating x 0.8, VGS = 0V, TJ = 125oC - - -1000 µA

V

DS

> I

D(ON)

x r

DS(ON)MAX

, VGS = -10V -4 - - A

VGS = -20V - - -100 nA

VGS= 20V - - 100 nA

= 10V, ID = -2A - 0.5 0.6 Ω

VDS > I

≅ 0.5BV

(Figure 18) MOSFET Switching Times are

Essentially Independent of Operating

Temperature

D(ON)

x r

DS(ON) Max

, ID= 4A, RG = 9.1Ω

DSS

, ID = 2A 1.25 2 - S

-2550ns

- 50 100 ns

- 50 100 ns

- 50 100 ns

= 10V, ID = 4A, VDS = 0.8 Max BV

DSS

-1622nC

(See Figure 18 for Test Circuit) Gate Charge

is Essentially Independent of Operating

Temperature

-9-nC

-7-nC

VGS = 0V, VDS = 25V, f = 1.0MHz,

See Figure 10

- 300 - pF

- 200 - pF

-50-pF

Measured from the

Drain Lead, 5.0mm

(0.2in) From Header

to Center of Die

Measured from the

Modified MOSFET

Symbol Showing the

Internal Device

Inductances

D

- 5.0 - nH

-15-nH

Source Lead, 5.0mm

(0.2in) from Header to

Source Bonding Pad

G

Junction to Case R

Junction to Ambient R

4-95

S

θJC

Typical Socket Mount - - 175oC/W

θJA

- - 6.25oC/W

IRFF9120

Source to Drain Diode Specifications

PARAMETER SYMBOL TEST CONDITIONS MIN TYP MAX UNITS

Continuous Source Current I

Pulse Source Current (Note 3) I

Source to Drain Diode Voltage (Note 2) V

SD

SM

SD

Diode Reverse Recovery Time t

Reverse Recovery Charge Q

RR

NOTES:

2. Pulse test: Pulse width ≤ 300µs, Duty Cycle 2%.

3. Repetitive rating: Pulse width limited by maximum junction temperature. See Transient Thermal Impedance Curve (Figure 3).

4. VDD= 25V, starting TJ= 250oC, L = 34.7mH, RG= 25Ω, peak IAS = 4.0A. See Figures 15 and 16)

Modified MOSFET

Symbol Showing the

Integral Reverse

D

- - -4 A

- - -16 A

P-N Junction

Rectifier

G

S

TJ = 25oC, ISD = -4A, VGS = 0V - - -1.5 V

TJ = 150oC, ISD = 4A, dISD/dt = 100A/µs - 230 - ns

rr

TJ = 150oC, ISD = -4A, dISD/dt = 100A/µs - 1.3 - µC

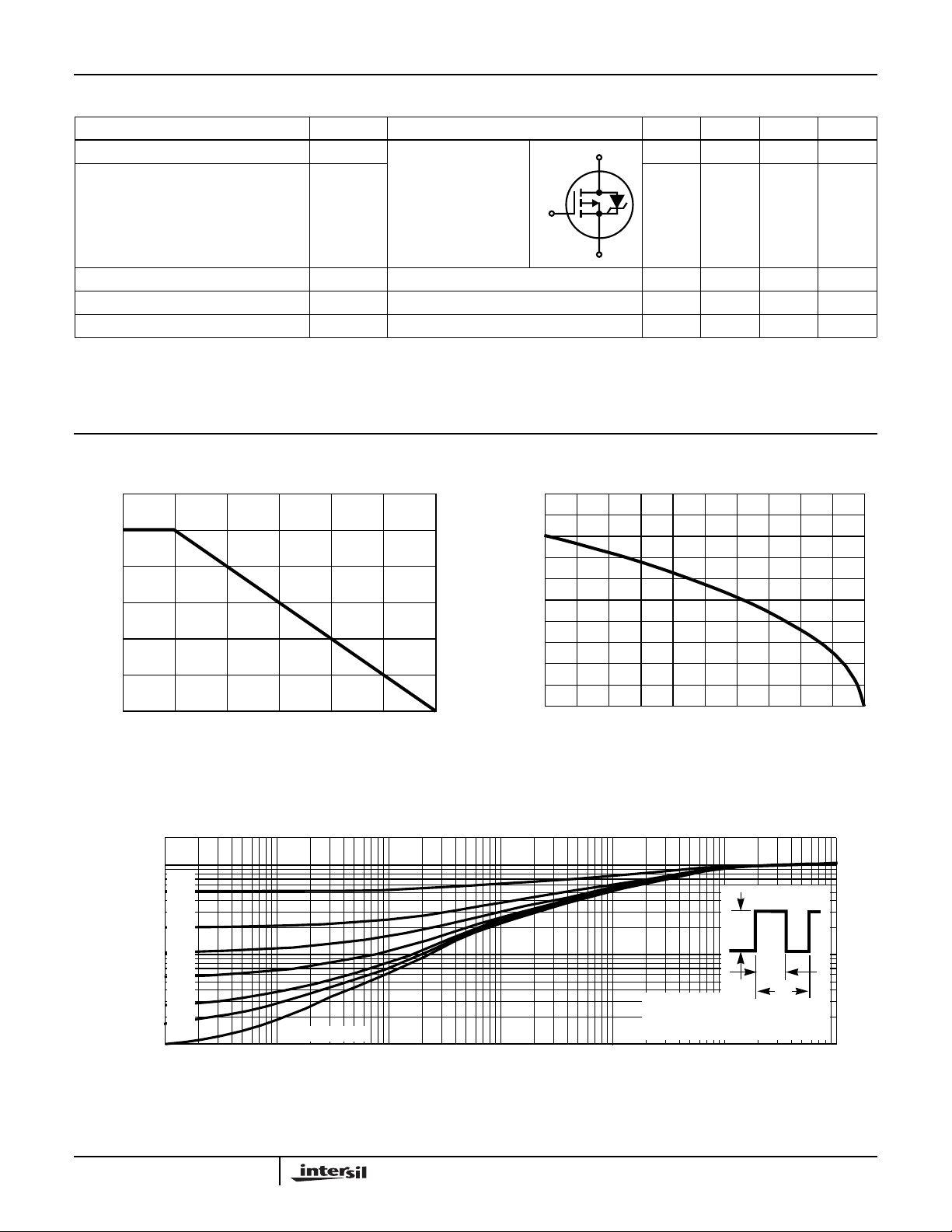

Typical Performance Curves

1.2

1.0

0.8

0.6

0.4

0.2

POWER DISSIPATION MULTIPLIER

0

0 50 100 150

TC, CASE TEMPERATURE (oC)

FIGURE 1. NORMALIZED POWER DISSIPATION vs CASE

TEMPERATURE

1.0

0.5

0.2

0.1

0.1

, NORMALIZED

θJC

Z

THERMAL IMPEDANCE

0.01

0.05

0.02

0.01

-5

10

SINGLE PULSE

-4

10

-3

10

t1, RECTANGULAR PULSE DURATION (s)

-5

-4

-3

-2

, DRAIN CURRENT (A)

D

I

-1

0

25 50 100

TC, CASE TEMPERATURE (oC)

FIGURE 2. MAXIMUM CONTINUOUS DRAIN CURRENT vs

CASE TEMPERATURE

P

DM

t

1

t

θJC

1/t2

x R

2

θJC

NOTES:

DUTY FACTOR: D = t

PEAK TJ = PDM x Z

-2

10

-1

10

1

12575

+ T

150

C

10

FIGURE 3. NORMALIZED MAXIMUM TRANSIENT THERMAL IMPEDANCE

4-96

Loading...

Loading...