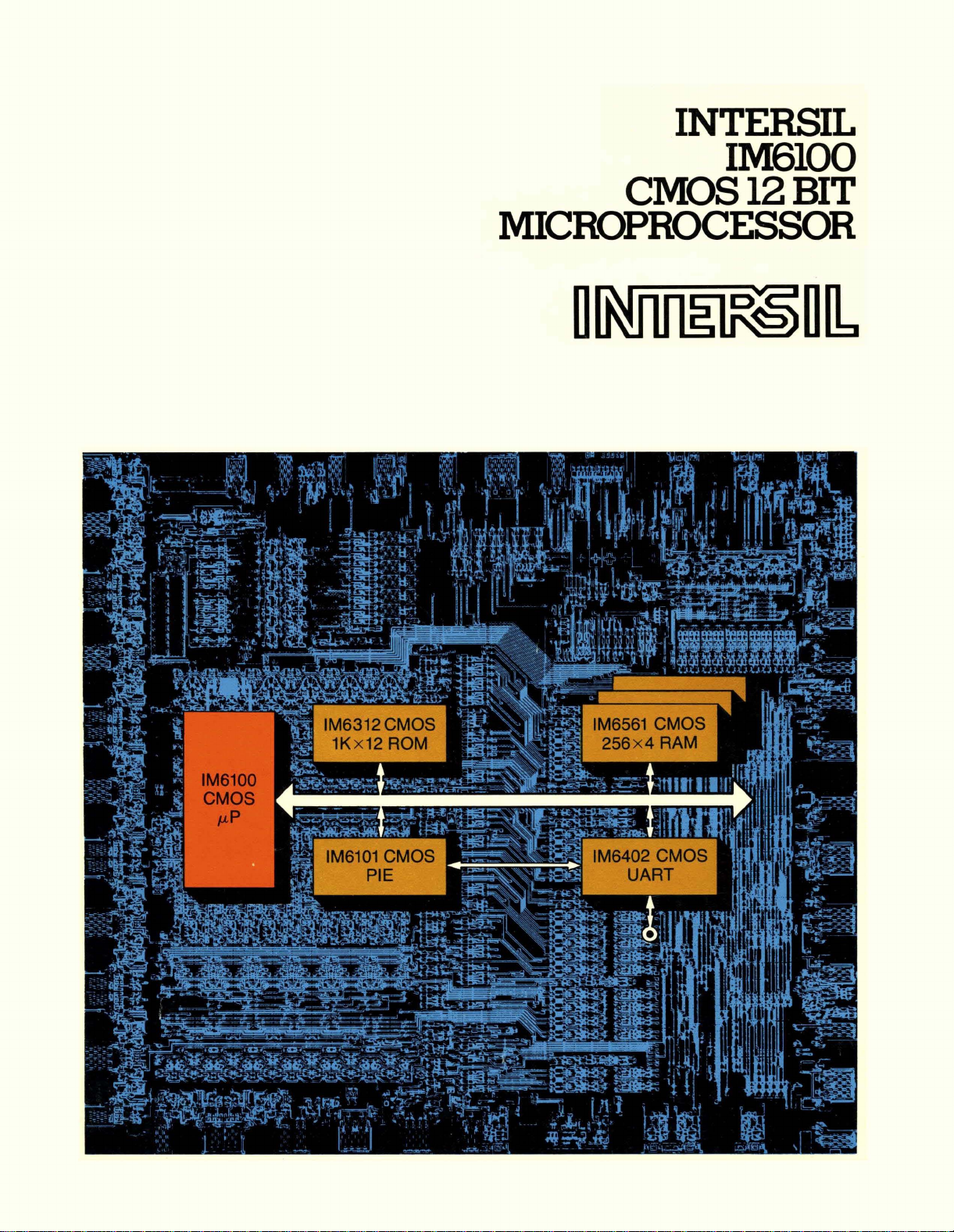

Page 1

INTERSIL

IM6100

CMOS

MICROPROCESSOR

12

BIT

D

Page 2

CONTENTS

Introduction

Section

12

Section

Section

Section

Section V:

I:

IntersillM6100

Bit Microprocessor

Introduction

Pin

Assignments

Specifications

Architecture

Memory

Operate

Input/Output

Internal

PDP-8/E

Applications

II: Intercept Prototyping System

Introduction

Specifications

Intercept

Software

Appendix

III: Intercept

IV: Intersil Data Sheets

IM6101/6101A

IM6312/6312A

IM6402/6403

IM6508/6518

IM6508C/6518C

IM6524/6524-1

IM6551

16561

IM56S06/56S26

ROM 4096

8052/7101

8052A/7103A

CMOS RAM Reliability Report

............................................

CMOS

.................................

......................................

..................................

....................................

......................................

and Processor

Instructions

Transfer

Priority

Compatibility

Structure

......................................

.........................

.....................................

Modules

and

Hardware

I-Edge

Jr.

CMOS

CMOS

CMOS/LSI UART

CMOS

CMOS RAM, 1024

CMOS RAM, 256

CMOS

Electronically

Bit

....................................

31;2

Digit

41;2

Instructions

...............................

Instructions

.........................

.............................

.................................

Options

Connector

Tutorial System

.........................

Parallel Interface

ROM, 1024

RAM, 1024

RAM, 1024 Bit

AID

Pair

Digit

Pair

.........................

..................

...................

Pin

Assignments

.................

Word x 12

.....................

Bit

.................

Bit

Bit

.................

Programmable

........................

................

................

~

.....

Element

Bit

...............

................

...............

'.' . . .

.....

.....

......

..

. 105

3

5

6

8

9

10

12

14

18

23

25

26

29

30

31

32

34

36

37

43

44

59

63

69

75

77

83

87

89

97

1

Page 3

2

Page 4

INTRODUCTION

Since its

become a company

In

this

publication,

advanced linear

bipolar, MOS, metal-gate CMOS

all

are

advantage

thinking

technologies

performance

developed

lntersil over

resulting in packing densities which surpass

metal gate process

proved 2: 1.

process,

RAMs, has lead

microprocessor.

length, parallel

plement

of

internal

at

Two

el

The

external

instruction

supply

The

nal

and peripheral devices.

represented

The

Mass

The

Digital

circuitry

any

speed

pins are available

iminating

crystal can be removed and

and

device design

components

founding

of

addition

that,

company,

product.

through

arithmetic.

clock

to

lntersil has developed

products

in lntersil's line,

because

many

produced

and

greater

Silicon

IM6100

Equipment

Gate

two

years ago, offers a

3:

production

previously

to

and

transfer

is

between

the

need

generator. A 12-bit

is

performed

in

2.5psec

is

required

on

July

26,

1967,

many

products

the

digital CMOS devices

and

they

were developed

of

the

by lntersil will

efficiency and flexibility

CMOS process, which was

1.

Additionally,

experience

announced

the

practicality

IM6100A are single address,

microprocessors using 12-bit,

The

processors recognize

Corporation's

completely

DC

and

the

to

allow

for

clock

in 5psec

by

the

optimized

for

and processes.

and

semiconductor

and

silicon-gate CMOS processes

with

the

different

with

static

maximum

for

generators

the

by

IM6100A

to

minimize

interfacing

kinds

work

together

semiconductor

circuit

the

256

of

introducing

PDP8/E

and

is

operating

an

external

and

processor

memory-accumulator

the

IM6100 using a

using a

the

with

lntersil, Inc. has

covered

markets

by

performance

Silicon

and

the

minicomputer.

designed

in

a line

memories.

significant

a single

of

devices

for

enhanced

of

developed

structure

the

conventional

Gate

1024

bit

the

fixed

two's

instruction

to

frequency.

crystal

level

translators.

clocked

+10

volt

number

standard

detail

forward-

the

of

memory

in

of

TTL

design

and

final

at

is

im-

CMOS

CMOS

IM6100

word

com-

set

The

operate

thereby

by an

ADD

+5

volt

supply.

exter-

described

product.

reserves

circuitry

in

this

3

lntersil

cannot

other

No

other

the

right

and

document.

assume responsibility

than

circuitry

circuit

to

change

specifications

entirely

patent

without

of

any

for

use

of

any

circuitry

embodied

licenses are implied. lntersil

notice

I ntersil

at

product

in

an lntersil

any

time

represented

the

Page 5

4

Page 6

SECTION

INTERSIL

IM6100

I:

CMOS

12

BIT

MICROPROCESSOR

5

Page 7

INTRODUCTION

IM6100

Since its founding on July 26, 1967, INTERSIL INC. has offered

its customers advanced products utilizing the semiconductor industry's most

ture of

in 1972, offers a semiconductor structure resulting in packing densities which surpass the

tionally, circuit performance is improved 2:1.

ess, through

has

technologically sophisticated processes for the manufac-

practical, economical devices.

The Silicon Gate

Mass production experience with the

lead to the practicality of introducing the IM6100 microprocessor.

MICROPROCESSOR

CMOS process, which was developed at Intersil

conventional metal gate process 3:1. Addi-

Silicon Gate CMOS proc-

previously announced 256 and 1024 bit CMOS RAMs,

The IM6100 is a single address, fixed word length, parallel transfer microprocessor using 12-bit, two's

processors recognize the instruction set of

ration's PDP8/E minicomputer. The

static and is designed to operate at any speed between DC and the

maximum operating frequency.

external crystal thereby eliminating the need for clock generators

and

level translators. The crystal can be removed and the processor

clocked

accumulator ADD instruction, using a + 5 volt supply, is performed in

5p,sec by the IM6100, in 6p,sec by the IM6100C and in 2.5p,sec by the

IM6100A using a +10 volt supply. The device design is optimized to

minimize the number of

with standard memory and

by

an

external

Two

clock

external components required for interfacing

peripheral devices.

complement arithmetic. The

Digital Equipment Corpo-

internal circuitry is completely

pins are available to allow for an

generator. A 12-bit

memory-

6

Page 8

FEATURES

APPLICATIONS

DESIGN

o Silicon Gate Complementary MOS

o Fully Static-O to 8 MHz

o Single Power Supply

IM6100/C

IM6100A

o Crystal Controlled

o Low Power Dissipation <

o Single Power Supply 4V

o TTL Compatible at 5 Volts

o Excellent Noise Immunity

o

-55°C

INTERFACE

o

Memory-Any

o Control Panel

o Switch Register

o Asynchronous

Communication

o 64 I/O Devices with PDP-8/E Compatible Interface

o Device Controlled Input-Output

o All Control Signals Produced By The CPU

o Power-on Initialize

ARCHITECTURAL

o Executes PDP-8/E, Instruction Set

o Direct, Indirect, and Autoindexed Memory Addressing

o 12-Bit Memory Accumulator ADD Instruction

IM6100 5fLsec

IM6100A 2.5fLsec @ +10 volts/8.0 MHz

IM6100C 6fLsec @

o

Input-Output Instruction

IM6100 8.5fLsec

IM6100A 4.25fLseC @ +10 volts/8 MHz

IM6100C 10.2fLsec @

o Single-Clock, Single-Instruction Capability

o Direct Memory Access (DMA)

o Interrupt

o Dedicated Control Panel Features

Vee=5

volts

Vee=10

to +125°C Operation

volts

On

Chip Timing

10

~

Speed

CPU-Memory

@

+5

+5

@

+5

+5

mW @ 4 MHz @ 5 volts

Vee ~ 11V

and

CPU-Device

volts/4.0 MHz

volts/3.3 MHz

volts/4.0 MHz

volts/3.3 MHz

o Intelligent Computer Terminals

o POS Terminals

o Portable Terminals

o Aerospace/Satellite System

o Automotive Systems

o Remote Data Acquisition Systems

o Process Control

o Instrumentation

o Medical Electronics

o Displays

o Traffic Control

o Navigation

7

Page 9

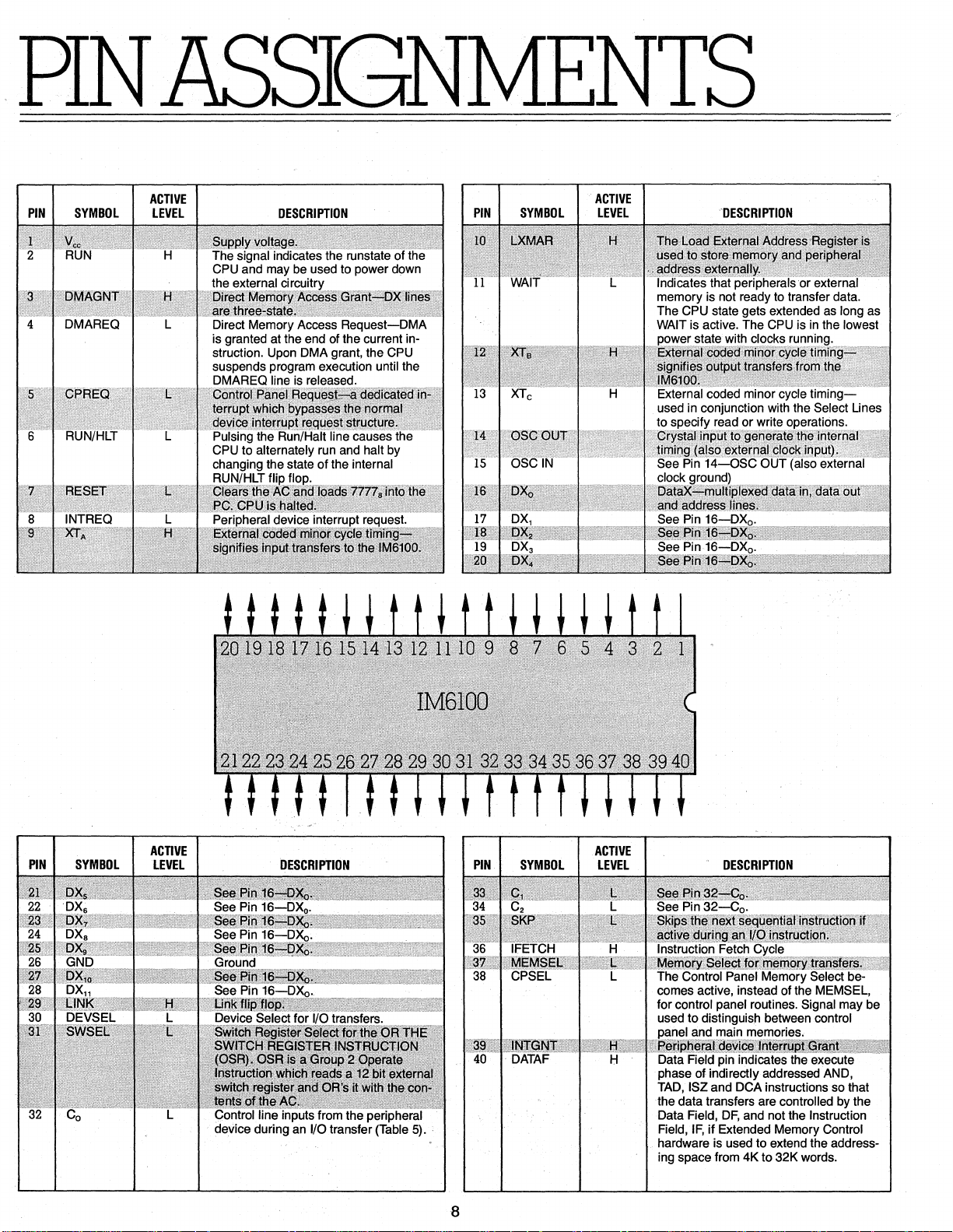

PIN

ASSIGNMENTS

;',

,',

<',

Data Field pin

phase

TAD,

the data transfers are controlled by the

Data

Field,

hardware is used to extend the address-

ing space from

,

of.

indirectly addressed AND,

ISZ and DCA instructions so that

Field,

DF,

IF,

and not the Instruction

if

Extended Memory Control

4K

to

32K

words.

Page 10

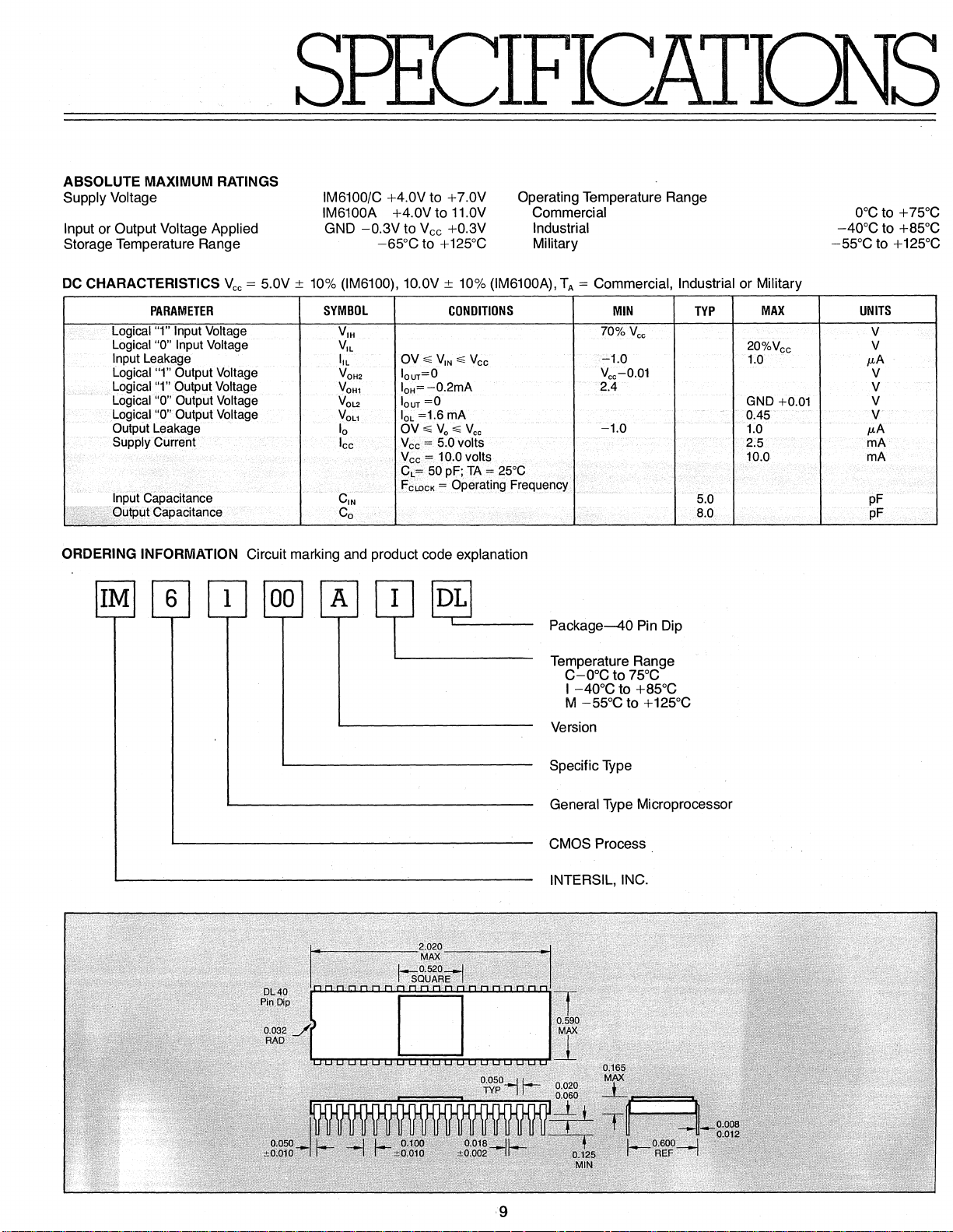

ABSOLUTE MAXIMUM RATINGS

Supply Voltage

or Output Voltage Applied

Input

Storage Temperature Range

DC

CHARACTERISTICS

Vee

= 5.0V ±

SPECIFICATIONS

IM6100/C +4.0V to +7.0V

IM6100A +4.0V

GND

-0.3V

-65°C

10%

(IM6100), 10.0V ± 10% (IM6100A),

to 11.0V

to

Vee

to +125°C

+0.3V

Operating Temperature Range

Commercial

Industrial

Military

TA

= Commercial, Industrial or Military

O°C

-40°C

-55°C

to +75°C

to +85°C

to +125°C

PARAMETER

Logical "1" Input Voltage V

Logical

"0"

Input Leakage

Logical "1" Output Voltage

Logical "1" Output Voltage

Logical

Logical

Output Leakage

Supply Current

Input Capacitance

Output Capacitance

.".

Input Voltage

"0"

Output Voltage

"0"

Output Voltage

SYMBOL

IH

V

IL

IlL

V

OH2

V

OH1

V

OL2

V

OL1

10

lec

C

IN

Co

CONDITIONS

OV ~ VIN ~ Vee

10ur=0

IOH=-0.2mA

lour

=0

10L

=1.6

OV ~ V

Vee

Vee

CL= 50 pF;

F

mA

~

Vee

o

= 5.0 volts

= 10.0 volts

TA

= Operating Frequency

eLDeK

= 25°C

ORDERING INFORMATION Circuit marking and product code explanation

MIN

70%

Vee

-1.0

O

01

Vee-

.

2.4

-1.0

Package-40

Pin Dip

Temperature Range

C-O°C

I

M

-40°C

-55°C

to 75°C

to +85°C

to +125°C

Version

TYP

5.0

8.0

MAX

20%V

ee

1.0

GND +0.01

0.45

1.0

2.5

10.0

UNITS

V

V

/LA

V

V

V

V

p,A

mA

mA

pF

pF

Specific

Type

General Type Microprocessor

CMOS Process

INTERSIL, INC.

9

Page 11

ARCHITECTURE

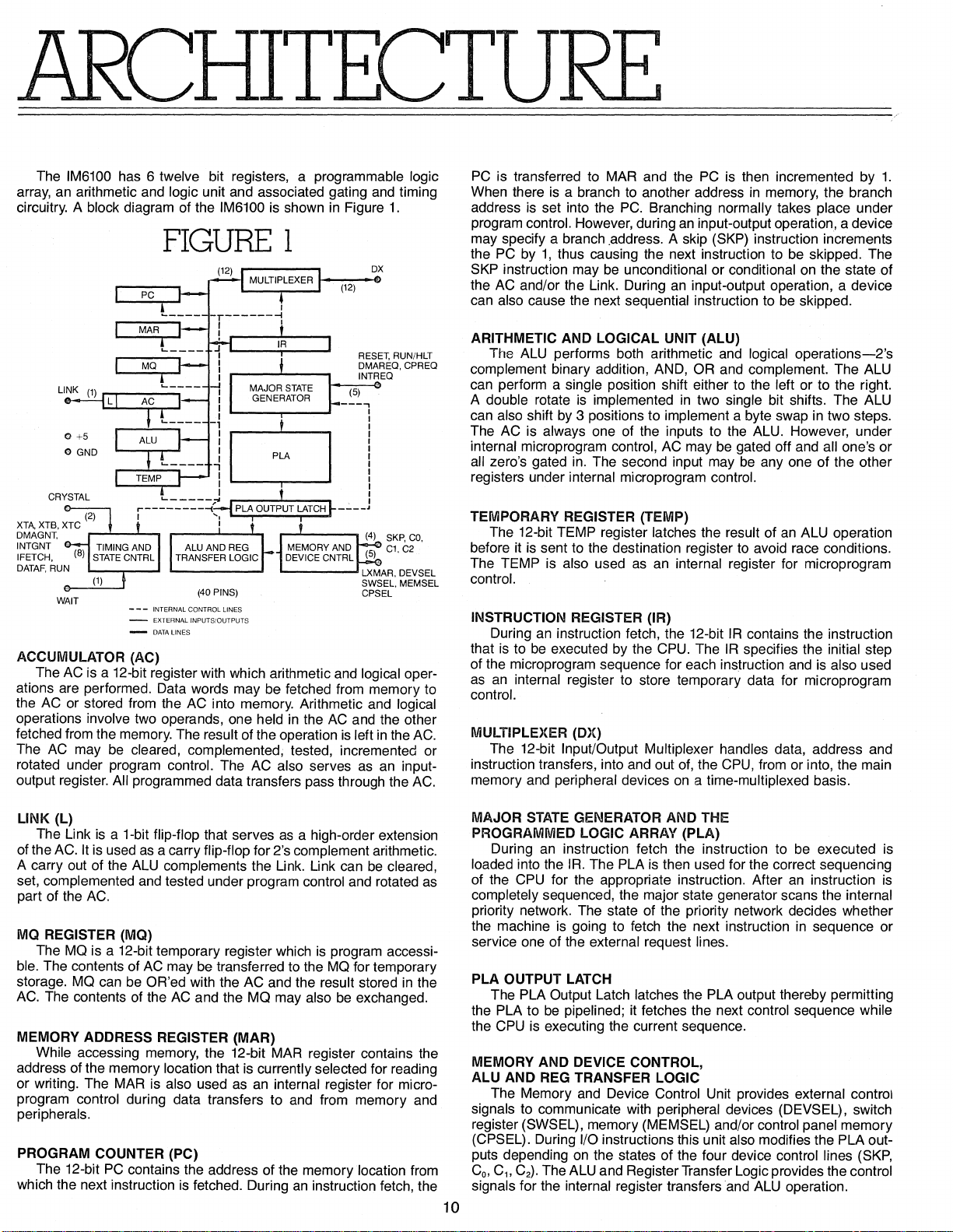

The IM6100 has 6 twelve bit registers, a programmable logic

array, an arithmetic and logic unit and associated gating and timing

circuitry. A

XTA,

XTB, XTC

DMAGNT,

INTGNT

IFETCH,

DATAF,

block diagram of the IM6100 is shown

FIGURE

LINK

(1)

,......,.

___

-,

in

1

~L.;;L;.J..I_:..:r_~

o +5

()

GND

CRYSTAL

(2)

,....--'----.1.--,

RUN

WAIT

....-_--1_--1...,

(40 PINS)

- - - INTERNAL CONTROL LINES

- EXTEHNAL INPUTS/OUTPUTS

- DATA

LINES

Figure

DX

(12)

RESET, RUN/HLT

DMAREQ,CPREO

INTREQ

(5)

---.,

I

I

I

I

I

I

I

I

I

I

I

I

I

____

J

1.

SKP,

C1,

C2

CO,

ACCUMULATOR (AC)

The AC is a 12-bit register with which arithmetic and logical oper-

ations are performed. Data words may be fetched from memory to

the AC or stored from the AC into memory. Arithmetic and

operations involve two operands, one held in the

fetched from the memory. The

The AC may

be

cleared, complemented, tested, incremented or

rotated under program

output register.

All programmed data transfers pass through the

result of the operation

control. The AC also serves

AC

is

logical

and the other

left

in

the AC.

as

an

input-

AC,

PC

is transferred to MAR and the

When there

address

program

is

a branch to another address

is

set into the

PC.

Branching normally takes place under

control. However, during

may specify a branch .address. A skip

the

PC

by

1,

SKP instruction may

thus causing the next instruction to

be

unconditional or conditional

the AC and/or the Link. During

can

also cause the next sequential instruction to be skipped.

PC

is then incremented by

in

memory, the branch

an

input-output operation, a device

(SKP) instruction increments

be

skipped. The

on

the state of

an

input-output operation, a device

ARITHMETIC AND LOGICAL UNIT (ALU)

The ALU performs both arithmetic and logical

operations-2's

complement binary addition, AND, OR and complement. The ALU

can perform a

A

double rotate

can

also shift

The AC is

single position shift either to the left or to the right.

is

implemented

by

3 positions to implement a byte swap

in

two single bit shifts. The ALU

in

two steps.

always one of the inputs to the ALU. However, under

internal microprogram control, AC may be gated off and all one's or

all zero's gated

registers under

TEMPORARY REGISTER

The 12-bit TEMP register

before it

is

The TEMP is

in,

The second input may

be

anyone

of the other

internal microprogram control.

(TEMP)

latches the result of

an

ALU operation

sent to the destination register to avoid race conditions.

also used

as

an

internal register for microprogram

control.

INSTRUCTION REGISTER (IR)

During an instruction fetch, the 12-bit

that

is

to

be

executed by the CPU. The

of the microprogram sequence for each instruction and

as

an

internal register to store temporary data for microprogram

IR

contains the instruction

IR

specifies the initial step

is

also used

control.

MULTIPLEXER (DX)

The 12-bit Input/Output Multiplexer handles data, address and

instruction transfers, into and out of, the CPU, from or into, the main

memory and

peripheral devices

on

a time-multiplexed basis.

1.

LINK (L)

is

The Link

of the AC.

a 1-bit flip-flop that serves

It

is used

as

a carry flip-flop for 2's complement arithmetic.

A carry out of the ALU complements the Link. Link can

as

a high-order extension

be

cleared,

set, complemented and tested under program control and rotated as

part of the AC.

MQ

REGISTER (MQ)

MQ

The

ble. The contents of AC may

storage.

AC.

is a 12-bit temporary register which

be

transferred to the

MQ

can

be

OR'ed with the AC and the result stored

The contents of the AC and the MQ may also

is

program accessi-

MQ

for temporary

be

exchanged.

in

the

MEMORY ADDRESS REGISTER (MAR)

While accessing memory, the 12-bit MAR register contains the

address of the memory

or writing. The MAR is

program

control during data transfers to and from memory and

location that is currently selected for reading

also used

as

an

internal register for micro-

peripherals.

PROGRAM COUNTER (PC)

PC

The 12-bit

which the next instruction

contains the address of the memory location from

is

fetched. During

an

instruction fetch, the

MAJOR

PROGRAMMED

loaded into the

of the CPU for the appropriate instruction. After

During

STATE

GENERATOR AND THE

LOGIC ARRAY (PLA)

an

instruction fetch the instruction to be executed is

IR.

The PLA

is

then used for the correct sequencing

an

instruction

completely sequenced, the major state generator scans the internal

priority network. The state of the priority network decides whether

the machine is going to fetch the next instruction

service one of the

external request lines.

in

sequence or

PLA OUTPUT LATCH

The PLA Output Latch

the PLA to

be

pipelined; it fetches the next control sequence while

latches the PLA output thereby permitting

the CPU is executing the current sequence.

MEMORYANDDE~CECONTRO~

ALU AND REG TRANSFER LOGIC

The Memory and Device Control Unit provides external control

signals to communicate with peripheral devices (DEVSEL), switch

register

(SWSEL), memory (MEMSEL) and/or control panel memory

(CPSEL). During I/O instructions this unit also modifies the PLA outputs depending

Co,

C

C

,

1

signals

2

for the internal register transfers

on

)·

The ALU and Register Transfer Logic provides the control

the states of the four device control lines

and

ALU operation.

10

is

(SKP,

Page 12

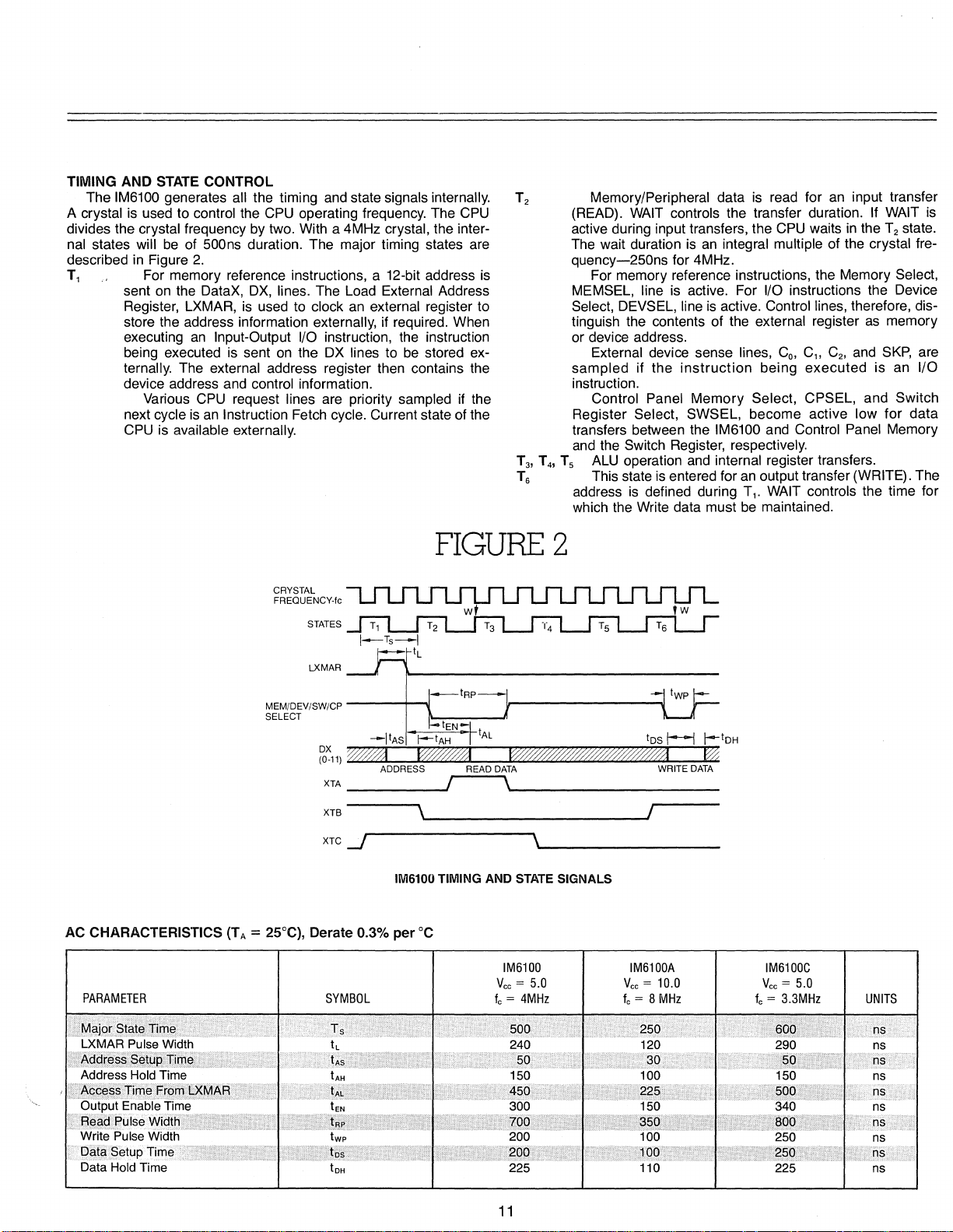

TIMING AND

STATE

CONTROL

The IM6100 generates all the timing and state signals internally.

A crystal

is

used to control the CPU operating frequency. The

CPU

divides the crystal frequency by two. With a 4MHz crystal, the internal states will

described

T1

be

in

of 500ns duration. The major timing states are

Figure

2.

For memory reference instructions, a 12-bit address is

on

sent

the DataX,

Register, LXMAR,

store the address information

executing

an

being executed is sent

DX,

lines. The Load External Address

is

used to clock

an

external register to

externally, if required. When

Input-Output I/O instruction, the instruction

on

the DX lines to

be

stored externally. The external address register then contains the

device address and

Various

next cycle

CPU

is

an

control information.

request lines are priority sampled

if

the

Instruction Fetch cycle. Current state of the

CPU is available externally.

T 2 Memory/Peripheral data

WAIT

(READ).

controls the transfer duration. If WAIT

active during input transfers, the

is

an

The wait duration

quency-250ns

for 4MHz.

integral multiple of the crystal fre-

For memory reference instructions, the Memory

MEMSEL, line

Select, DEVSEL, line

is active. For I/O instructions the Device

is

active. Control lines, therefore, distinguish the contents of the

or device address.

External device sense lines,

sampled if the

instruction

instruction.

Control Panel Memory Select, CPSEL, and Switch

Register Select, SWSEL, become active low for data

IM6100 and Control Panel Memory

and

internal register transfers.

T

Ts

transfers between the

and the

•

T

Ts

,

3

ALU

4

This state is entered for

address

Switch Register, respectively.

operation

is

defined during T1. WAIT controls the time for

which the Write data must

is

read for

CPU

external register

Co,

an

input transfer

waits

in

the

C1, C2, and

T2

as

memory

SKP,

being executed is an I/O

an

output transfer (WRITE). The

be

maintained.

is

state.

Select,

are

CRYSTAL

FREQUENCY·!e

STATES

LXMAR

MEMIDEVISWICP

SELECT

XTB

XTC

---+--.J

-1

IM6100 TIMING AND

AC CHARACTERISTICS (T A = 25°C), Derate 0.3% per

PARAMETER

SYMBOL

FIGURE

2

\~------------------~I

\~-----------------

STATE

SIGNALS

°C

IM6100

Vee = 5.0

fe = 4MHz

IM6100A

Vee = 10.0

fe

= 8

MHz

IM6100C

Vee = 5.0

fe = 3.3MHz

UNITS

MajorStqteTime

LXMAR Pulse Width

·Addre~s$etupTi.f11e

Address Hold Time

r\GcessTimeFromLXMAR

Output Enable

Pulse Width

Read

Write

Pulse Width

Data Setup Time

Hold Time

Data

Time·

tDH

500

240

50

150

450

300

700

200

200

225

11

Page 13

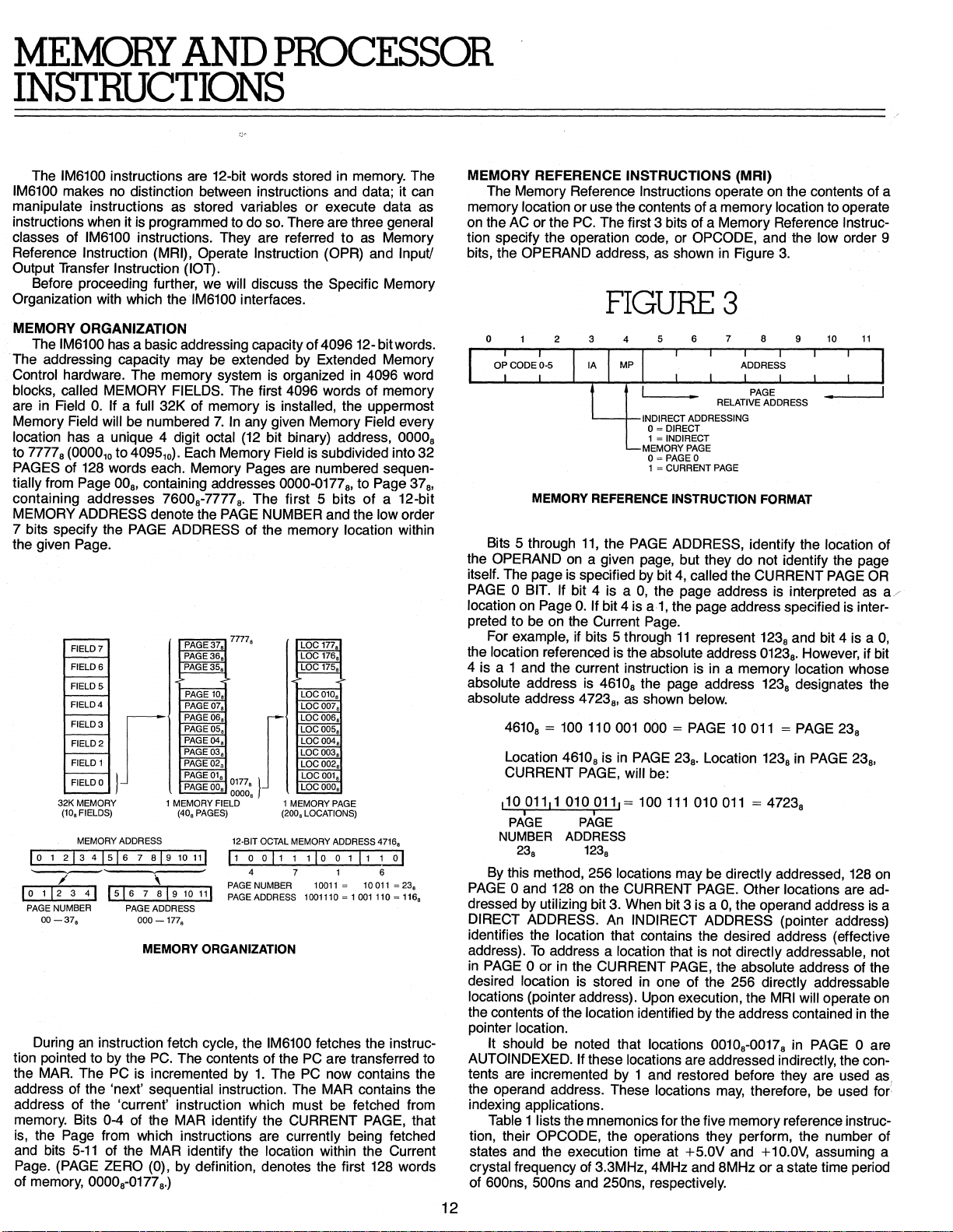

MEMORY

AND

PROCESSOR

INSTRUCTIONS

The

IM6100 makes no distinction between instructions

IM6100

manipulate instructions

instructions when it

classes

Reference

Output

Transfer Instruction (lOT).

Before proceeding further,

instructions are 12-bit words stored in memory. The

and

as

is

stored variables or execute data

programmed to do

so.

There are three general

of IM6100 instructions. They are referred to

data; it can

as

Memory

Instruction (MRI), Operate Instruction (OPR) and Input!

we

will discuss the Specific Memory

as

Organization with which thelM6100 interfaces.

MEMORY ORGANIZATION

The IM6100

The addressing capacity may

Control hardware. The memory system

has

a basic addressing capacity of 409612-bit words.

be

extended by Extended Memory

is

organized

in

4096 word

blocks, called MEMORY FIELDS. The first 4096 words of memory

are

in

Field

O.

If a full 32K of memory

Memory Field will

be

numbered

7.

location has a unique 4 digit octal

to

77778

(000010

PAGES of

tially from Page

containing addresses

to 4095

128

words each. Memory Pages are numbered sequen-

OOe,

).

Each Memory Field

10

containing addresses

7600e-7777e. The first 5 bits of a 12-bit

is

installed, the uppermost

In

any given Memory Field every

(12

bit binary) address, 0000

is

subdivided into 32

0000-0177a,

to Page 37e,

MEMORY ADDRESS denote the PAGE NUMBER and the low order

7 bits specify the

PAGE

ADDRESS of the memory location within

the given Page.

7777,

PAGE

FIELD

7

FIELD 6

FIELDS.

4

FIELD

3

FIELD

FIELD 2

1

FIELD

FIELD 0

32K MEMORY

(10,FIELDS)

MEMORY ADDRESS

I 0 1 2 I 3 4

1516 7 819

~

10 1 12 3 41

PAGE

NUMBER

00

-37,

During

tion pointed to

the

MAR.

1516 7 819

PAGE

an

instruction fetch cycle, the

by

the

The PC is incremented

address of the 'next'

\

ADDRESS

000-177,

MEMORY ORGANIZATION

PC.

sequential instruction. The MAR contains the

37,

PAGE

36,

PAGE

35,

PAGE

10,

PAGE

07,

PAGE

06,

PAGE

OS,

PAGE

04,

PAGE

03,

PAGE

02,

PAGE

01,

PAGE

00,

1 MEMORY FIELD 1 MEMORY

(40,

10

~~~~:

PAGES)

12-BIT

111

1100111

4 7 1 6

PAGE

10

111

PAGE

NUMBER 1

ADDRESS 1001110 ~ 1 001110 ~ 116,

The contents of the

by

address of the 'current' instruction which must

memory. Bits

is,

the Page from which instructions are currently being fetched

and

bits

Page.

(PAGE ZERO (0), by definition, denotes the first

of memory,

0-4

of

the MAR identify' the CURRENT PAGE, that

5-11

of the MAR identify the location within the Current

OOOOe-Ol77

e.)

LOC

LOC

LOC

LOC010,

LOC007,

LOC006,

LOC

LOC

f

LOC

LOC002,

I

~gg

(200,

LOCATIONS)

OCTAL

MEMORY ADDRESS 4716,

do

IM6100

1.

fetches the instruc-

PC

The

PC

177,

176,

175,

005,

004,

003,

~~~:

PAGE

0111

1:=£]

0011 ~ 10011 ~ 23,

are transferred to

now contains the

be

fetched from

128

words

MEMORY REFERENCE INSTRUCTIONS (MRI)

The Memory Reference Instructions operate

memory

on

location or use the contents of a memory location to operate

the AC or the

PC.

The first 3 bits of a Memory Reference Instruction specify the operation code,

bits, the

OPERAND address,as shown

FIGURE

o 2

8

MEMORY REFERENCE INSTRUCTION FORMAT

Bits 5 through

the OPERAND

itself. The page

PAGE

0 BIT. If bit 4 is a

location

on

Page

preted to be on the Current

For example, if bits 5 through

the location referenced

4 is a 1 and the current instruction

absolute address

absolute address 4723e,

4610

e

Location

CURRENT

11001111

i ,

PAGE PAGE

NUMBER

23

8

By this method, 256 locations may

PAGE

0 and

dressed by utilizing bit 3. When bit 3 is a

DIRECT ADDRESS.

3

4

L--t-INDIRECT

11,

the PAGE ADDRESS, identify the location of

on

a given page, but they do not identify the page

is

specified

O.

If bit 4 is

is

the absolute address

is

4610e the page address

as

=

100

110

001

4610e is

010011

ADDRESS

128

in

PAGE,

will be:

= 100111 010011 = 4723

1

123

8

on

the CURRENT

An

INDIRECT ADDRESS (pointer address)

or

OPCODE,

in

5

6

ADDRESSING

o

~

DIRECT

1 = INDIRECT

MEMORY PAGE

0=

PAGE 0

1 = CURRENT PAGE

by

bit

4,

called the CURRENT

0,

the page address is interpreted

al,

the page address specified

Page.

11

represent 123e and bit 4 is a

is

in

shown below.

000 = PAGE

PAGE

23e. Location 123e in

be

PAGE.

on

the contents of a

and

Figure

the low order 9

3.

3

7

8

9

.

0123

However, if bit

a memory location whose

10

directly addressed,

0,

the operand address

8

designates the

123

e

011 = PAGE

e

Other locations

identifies the location that contains the desired address (effective

address).

in

desired

locations (pointer address). Upon execution, the

the contents of the location identified

PAGE

To

address a location that

0 or

in

location

the CURRENT

is

stored in one of the 256 directly addressable

is

not directly addressable, not

PAGE,

the absolute address of the

MRI

by

the address contained

will operate

pointer location.

It should

be noted that locations

0010

-0017

e

in

e

AUTOINDEXED. If these locations are addressed indirectly, the contents are incremented

the operand address. These locations

by

1 and restored before they are used

may,

therefore,

indexing applications.

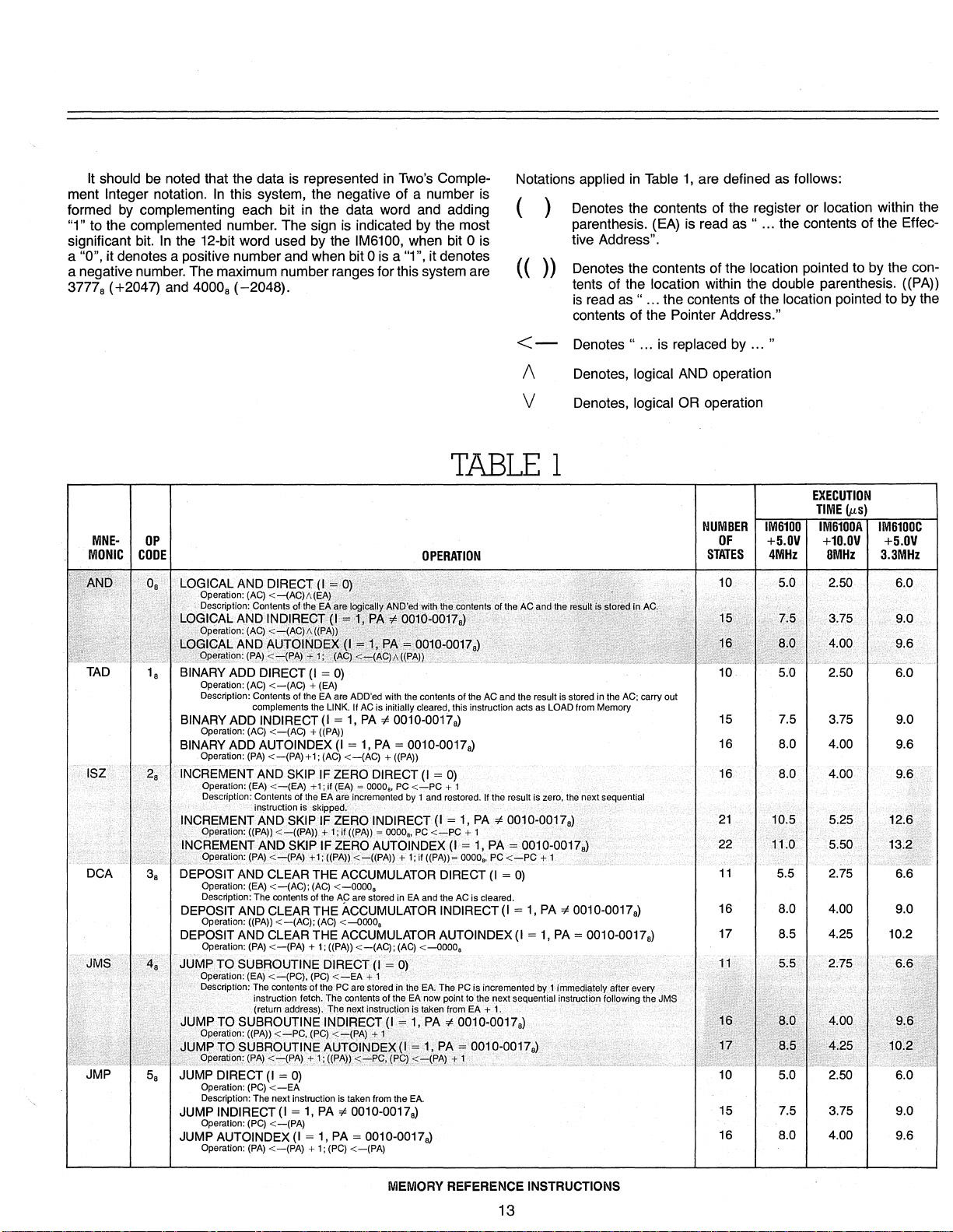

Table

tion, their

states

1 lists the mnemonics for the five memory reference instruc-

OPCODE, the operations they perform, the number of

and

the execution time at +5.0V and +10.0V, assuming a

crystal frequency of 3.3MHz, 4MHz and 8MHz or a state time period

of

600ns, 500ns

and

250ns, respectively.

12

10

PAGE

PAGE

PAGE

be

11

OR

as

is

inter-

0,

23

e

23e,

128

on

are

ad-

is

on

in

the

0 are

as.

used for

a -

a

Page 14

It

should be noted that the data is represented

ment Integer notation.

In

this system, the negative of a number is

in

Two's Comple-

formed by complementing each bit in the data word and adding

"1" to the complemented number. The sign is indicated by the most

In

significant bit.

a

"0", it denotes a positive number and when bit 0 is a "1", it denotes

the 12-bit word used by the IM6100, when bit 0 is

a negative number. The maximum number ranges for this system are

37778 (+2047) and

40008 (-2048).

Notations applied

( )

Denotes the contents of the register or location within the

parenthesis. (EA) is read as

in

Table

1,

are defined as follows:

" ... the contents of the Effec-

tive Address".

« »

Denotes the contents of the location pointed to by the contents of the location within the double parenthesis.

is

read as " ... the contents of the location pointed to by the

contents of the Pointer

Aqdress."

< - Denotes" ... is replaced by ... "

«PA»

DCA

TABLE

BINARY ADD DIRECT (I =

Operation: (AC)

Description: Contents of the EA are ADD'ed with the contents of the AC

BINARY ADD INDIRECT (I =

Operation:

BINARY ADD AUTOINDEX (I = 1, PA = 0010-0017a)

Operation:

~TI·T'7.""C··:':

..•..

<-(AC)

complements the

(AC)

<-(AC)

(PA)

<-(PA)+I;

....

.•

'mSl[ruClI:on

+<1'N·*J;«I?~\j)l::::..f~(PA))·

3a DEPOSIT AND CLEAR THE ACCUMULATOR DIRECT (I =

Operation:

Description: The contents of the

DEPOSIT AND CLEAR

Operation: ((PA))

DEPOSIT AND CLEAR THE ACCUMULATOR AUTOINDEX (I =

Operation:

(EA)

<-(AC);

(PA)

<-(PAl + 1;

<-(AC);

0)

+ (EA)

LINK.

If

AC

is initially cleared, this instruction acts

1,

+ ((PA))

SKIP IFZERODII::U:CT (I =

IS,:sKlppeQ.:':T:,

(AC)

THE

PA"# 0010-0017.)

(AC)

<-(AC)

+ «PA))

0)

. 0000" PC

'e)n.crennentec

~OINCHRI:Cl"(,

'-"".=

.-'~';';;;"''''''

<-0000,

AC

are stored in

ACCUMULATOR INDIRECT (I = 1, PA

(AC)

<-0000,

<-,-PC

+ 1 .

by

1 and restored. If the result is zero,

uuuu.

.1= 1, PA4.001Q-OQ17a)'{

PC'~

" .

(1:= 1

«PA))", 0000"

and the

AC

<-0000,

,+ ~ ';,

NDEX

',1

;if

EA

.•

,PA='cib10~001T

PC<-:--:!,~

is cleared.

1\

Denotes, logical AND operation

V Denotes, logical OR operation

1

and

the result

is

stored in the AC; carry out

as

LOAD from Memory

. .

,,"'"

'

the

next sequential

','

'~;T:~,';T'

:T',T

,""

,',

,:"i:,~;'{:0,~!,:,,:)'

t!'.;:i:'.i;;u.';'

0)

1,

PA

,'(~'"

,;(:'

40010-0017

= 0010-0017

)

a

a)

10

15

16

1,6

11

16

17

5.0

7.5

8.0

5.5

8.0

8.5

2.50

3.75

4.00

2.75

4.00

4.25

IM6100C

+5.0V

3.3MHz

6.0

9.0

9.6

6.6

9.0

10.2

JMP

5.

JUMP DIRECT (I =

Opemtion: (PC)

Description: The next instruction

JUMP INDIRECT (I =

Opemtion: (PC)

JUMP AUTOINDEX (I = 1, PA = 0010-0017

Opemtion:

<-EA

<-(PAl

(PA)

<-(PAl + 1;

0)

is

1,

PA

4 0010-0017.)

(PC)

taken

from

the

EA.

<-(PAl

a)

MEMORY REFERENCE INSTRUCTIONS

13

10

15

16

5.0

7.5

8.0

2.50

3.75

4.00

6.0

9.0

9.6

Page 15

OPERATE

INSTRUCTIONS

The Operate Instructions, which have

consists of 3 groups of microinstructions. Group 1 microinstructions,

which are identified

perform

link. Group 2 micro instructions, which are identified by the presence

of a 1

of the

instruction. Group 3 microinstructions have a 1

bit

the AC and

logical operations

in

bit 3 and a 0 in bit

accumulator and then conditionally skip the next sequential

11

and are used to perform logical operations

MO.

The basic OPR instruction format is shown

by

the presence of a 0 in bit

on

the contents of the accumulator and

11,

are used primarily to test the contents

an

OPCODE of

in

on

in

Figure 4.

78

(111),

3,

are used to

bit 3 and a 1 in

the contents

of

FIGURE

3 4

2

A

1

I

MICROINSTRUCTION

GROUP 1

GROUP 2

GROUP

BASIC OPR INSTRUCTION FORMAT

I

0

1

: 1 :

Operate microinstructions from any group may be microprogram-

med

with other operate microinstructions of the same group. The

actual code for a microprogrammed combination of two, or more,

logical

OR

microinstructions is the bitwise

individual microinstructions. When more than one operation

programmed into a

in

a prescribed sequence, with logical sequence number 1 microinstructions performed first,

tions performed second,

tions performed third and

logical sequence number, within a given group of microinstructions,

are performed

single instruction, the operations are performed

logical sequence number 2 microinstruc-

logical sequence number 3 microinstruc-

so

on.

simultaneously.

of the octal codes for the

Two

operations with the same

4

5

3 1 1

7 8 9 10

6

o -t

An

1

0

:

11

B I

is

micro-

i4

Page 16

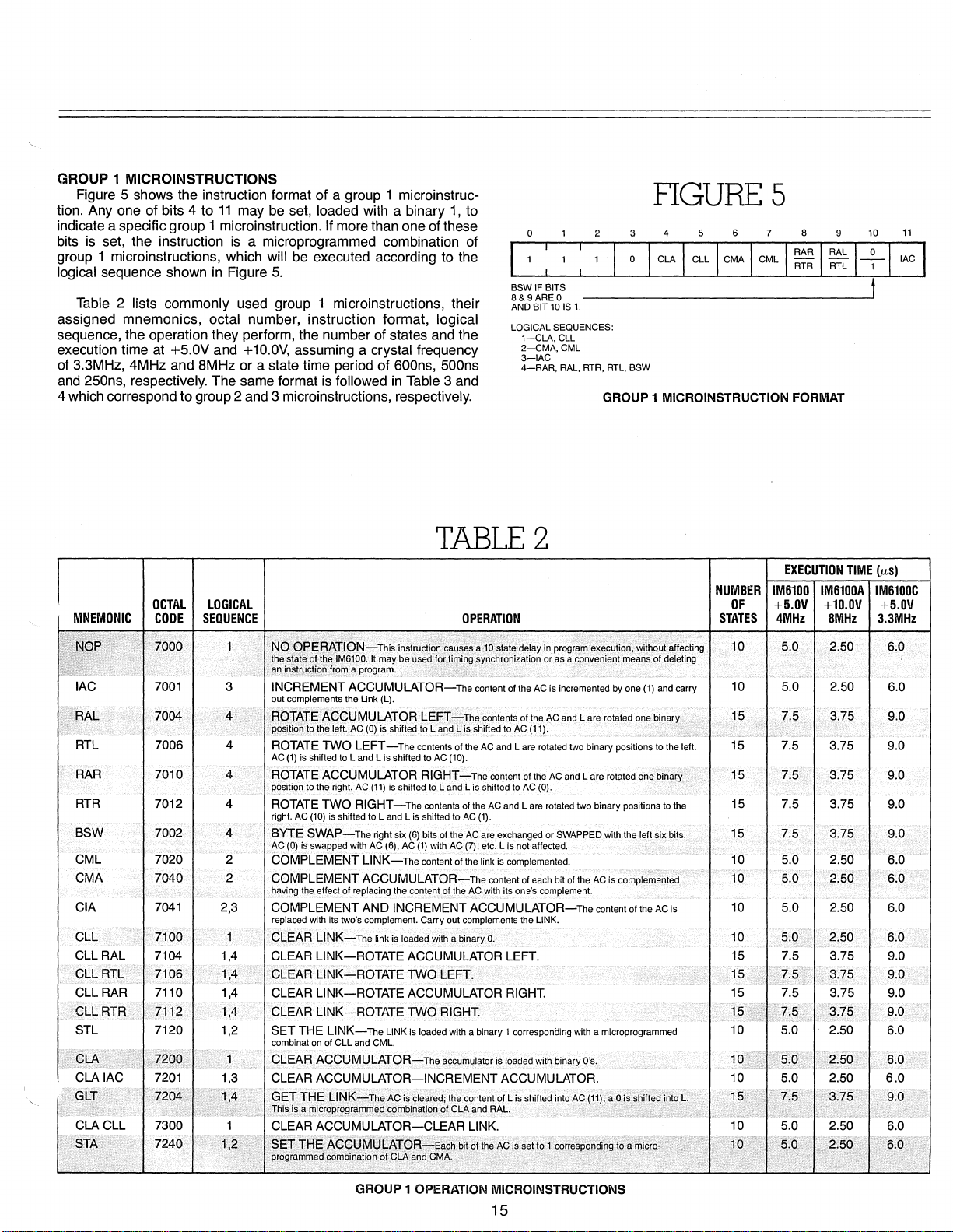

GROUP 1 MICROINSTRUCTIONS

Figure 5 shows the instruction format

tion.

Anyone

of bits 4 to

11

may be set, loaded with a binary

indicate a specific group 1 microinstruction.

bits

is

set, the instruction

is

a microprogrammed combination of

of

a group 1 microinstruc-

1,

If more than one of these

to

group 1 microinstructions, which will be executed according to the

logical sequence shown

in

Figure

5.

Table 2 lists commonly used group 1 microinstructions, their

assigned mnemonics, octal number, instruction format, logical

sequence, the operation they perform, the number of states and the

execution time at

of

3.3MHz, 4MHz and 8MHz or a state time period of 600ns, 500ns

and 250ns, respectively. The same format is followed

+5.0Vand

+10.0V, assuming a crystal frequency

in

Table 3 and

4 which correspond to group 2 and 3 microinstructions, respectively.

o 2

BSW

IF

BITS

8 & 9

ARE

AND

BIT

10

LOGICAL

SEQUENCES:

1-CLA.CLL

2-CMA.CML

3-IAC

4-RAR,

FIGURE

3 4

0

IS

1.

RAL,

RTR,

RTL,

BSW

GROUP 1 MICROINSTRUCTION FORMAT

5 6 7 8 9

5

10

11

RTR

SSW

CML

CMA

CIA

CLL

4

4

2

RPTjI,TE

I(osition.tothe left.

ROTATE

AC

ROTATE

position

ROTATE

right.

BYTE

AC

COMPLEMENT

COMPLEMENT

having

COMPLEMENT

replaced

CLEAR

CLEAR

CLEAR

CLEAR

CLEAR

SET

combination

CLEARAgCUMU

CLEAR

GET

This

ACCU

MU

LATOR

AC

(0)

is shifted

TWO

(1)

is

to

AC

SWAP-The

(0)

is

the

THE

TI-iE

i~a

LEFT

Shifted

to

Land L is shifted

ACCUMULATOR

the right.

AC

(11)

TWO

RIGHT-The

(to)

is

shifted

to

Land L is

swapped

effect of replacing the content

with

LINK-The

LINK-ROTATE

LINK-ROTATE

LINK-ROTATE

LINK-ROTATE

of

ACCUMULATOR-INCREMENT

rnicroprograrnmedcombirationofCLA

right six

with

AC

LINK-The

ACCUMULATOR-The

AND

its

two's

complement. Carry out complements the

link

LINK-The

CLL

and

CML.

LATOR-The

IJNl)--,TheACisclea,red;theconlent

LEF[

to

Land

-The

contents

to

RIGHT-The

is

shifted

to

contents

shifted

(6)

bits

(6),

AC

(1)

with

content

INCREMENT

is

loaded

ACCUMULATOR

TWO

ACCUMULATOR

TWO

LINK

is

loaded

TABLE

OPERATION

-The.

contents of the

L.is shifted

of

AC

(10).

Land L is shifted

to

of

the

AC (7),

of

of

the

with

abinary.O.

LEFT.

RIGHT.

with

accumulator

to

AC

the

AC

and L are

content

of

to

AC

of

the

AC

and L are

AC

(1).

AC

are exchanged

etc.

L is

not

the link

is

complemented.

content

AC

ACCUMULATOR-The

a binary 1 corresponding

and

of

with

its on9's complement.

LEFT.

RIGHT.

is

loaded

ACCUMULATOR.

of

L is shifted into AC(11),

RAL.

2

AC

and L are rotated one

(11).

rotated

two

binary positions to the left.

the

AC

and

L are rotated one binary

(0). .

rotated

two

binary positions

or

SWAPPED

affected.

each bit

LINK.

with

binary a's.

with the lett sixbits.

of

the

AC

is complemented

content

with

a microprogrammed

of

the ACis

NUMBER

OF

STATES

EXECUTION

IM6100

+5.0V

4MHz

TIME

IM6100A

+10.0V

BMHz

(MS)

IM6100C

+5.0V

3.3MHz

6.0

6.0

9.0

9.0

3.75

to

the

3.75 9.0

9,0

3.75 9.0

GROUP 1 OPERATION MICROINSTRUCTIONS

15

Page 17

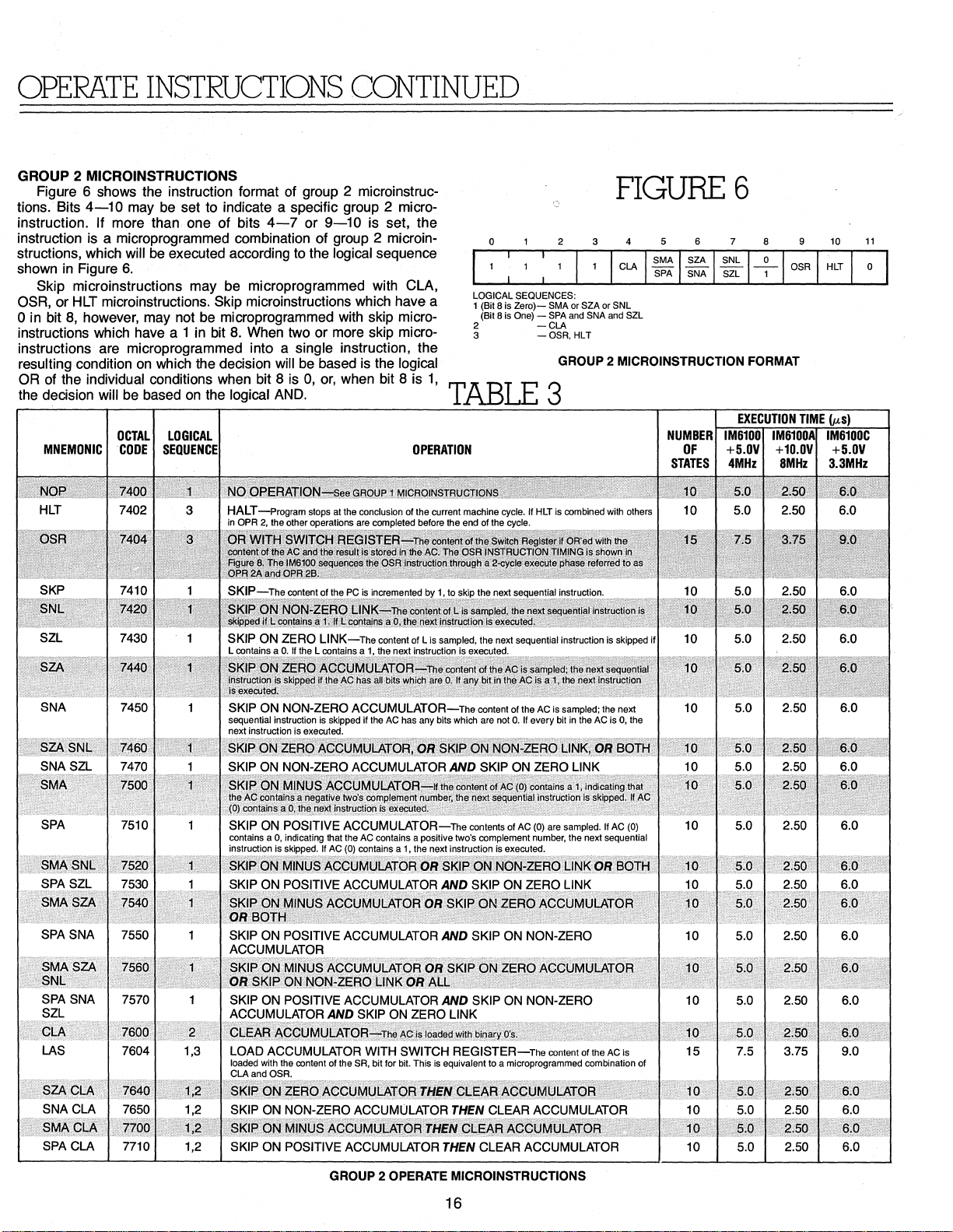

OPERATE

GROUP 2 MICROINSTRUCTIONS

Figure 6 shows the instruction format of group 2 microinstructions. Bits

instruction.

instruction is a microprogrammed combination of group 2 microinstructions, which

shown in Figure

Skip microinstructions may be microprogrammed with CLA,

OSR, or HLT microinstructions. Skip microinstructions which have a

o in bit

instructions which have a 1 in bit

instructions are microprogrammed into a single instruction, the

resulting condition

OR

the decision will be based on the logical AND.

4-10

If more than one of bits

8,

however, may not be microprogrammed with skip micro-

of the individual conditions when bit 8 is

INSTRUCTIONS

may be set to indicate a specific group 2 micro-

4-7

will

be

executed according to the logical sequence

6.

8.

When two or more skip micro-

on

which the decision will be based is the logical

CONTINUED

or

9-10

is set, the

0,

or,

when bit 8 is

o 2 3 4 5 6 7 8 9 10

LOGICAL SEQUENCES:

1 (Bit 8 is

(Bit 8 is One) -

2

3

1,

TABLE

FIGURE

Zero)-

SMA

or

SZA or SNL

SPA

and SNA and SZL

-CLA

-OSR.

HLT

GROUP 2 MICROINSTRUCTION FORMAT

3

6

11

MNEMONIC

OCTAL

CODe

OPERATION

SPA CLA

7710 1,2

SKIP ON POSITIVE ACCUMULATOR

GROUP 2 OPERATE MICROINSTRUCTIONS

THEN

CLEAR ACCUMULATOR 10

16

5.0 2.50

6.0

Page 18

GROUP 3 MICROINSTRUCTIONS

Figure 7 shows the instruction format of group 3 microinstructions

which requires bits 3 and

set to indicate a specific group 3 microinstruction.

of the bits

is

set, the instruction is a microprogrammed combination

of group 3 microinstructions

Figure

7.

OCTAL

MNEMONIC

CODE

11

to contain a

1.

Bits 4, 5 or 7 may be

If more than one

following the logical sequence listed in

LOGICAL

SEQUENCE

0

1

I

LOGICAL

l-CLA

2-MOA.

3-ALL

TABLE

OPERATION

: 1 :

SE~UENCE:

MOL

OTHERS

4

FIGURE

2 3

1 I 1

GROUP 3 MICROINSTRUCTION FORMAT

4

CLA

5 6 7

>OAI

7

8 9

MO<

EXECUTION

NUMBER

STATES

OF

IM6100

+5.0V

4.0MHz

IM6100A

+10.0V

8.0MHz

TIME

10

*Oon't Care

(ILS)

IM6100C

+5.0V

3.3MHz

11

CLASWP

7721

NO

OPERATION-See

MQ

REGISTER

original content of the

MQ

REGISTER

tent

of

the

AC

content

SWAP

interchanged

CLEI)RI)CCtJMm.~1}c:5R

CLEAR

loaded

CLEARAccofVjULAfORANClL.OACl

TOR

3

CLEAR

REGISTER-The

MO

and the resu.ltis 10adedintotre.AC,

of

the.MOisr~t~in~(j;Ihis.in~tr~ctio!)Pr8vi~!,,,tl)eprog"lrlJlT)er

ACCUMULATOR

accomplishing a microprogrammed combination

ACCUMULATOR

with

binary

·.·.·Thi~i¢~ui~~le"tto.1).lT)i~rOh((Jgm~~~d·

ACCUMULATOR

is

loaded

into

the

Group

1 Microinstructions 10

LOAD-The

MQ

is lost.

INT9.A,.CCU~LJL}\"'9R-The

O's.

This

content

AC

and the

GROUP 3 OPERATE MICROINSTRUCTIONS

AND

is

equivalent

of

the

;

AND

AND

AC

MO

content

MQ

MQ

to

SWAP

is

is

cleared.

FIGURE

,

LXMAR

lfl

MEMSEL~~--~::::::j::::::::::::::t::::::::::::j

I

SWSEL:

I

DX I

®

~%~~W~~~~~~~~~~

CD

® ®

CD

Instruction

®

Address

Instruction ~ CPU

of

the

AC

is

loaded

into

contentCl(lheMO.isOR·ed

T.he

Origin~1

cont~nt

REGISTER-The

REGISTER-The

a microprogrammed

MOREGiSTER

D8mbin~tiOn

ACCUMULATOR

cleared. The content

of

MOA

combinalion

of.Gli\~n~MgA:'j

of

the

8

®

Switch

Register. ~ CPU

the

MO,

the

AC

is

cleared and the 10

with

AC

and

AC

and

MQ

OPR2B

the con-

the original

operation.

MO

and

MO

MOL.

are

are

of

\h~!lGislostbyt

withar.incl~sive.()R

content

of

the

and

MOL.

content

of

the

of

CLA

INfbACdJfVjOCA-'

AND

:

L.J

~~~

Data

10

5.0 2.50 6.0

5.0 2.50 6.0

5.0 2.50 6.0

5.0

5.0

2.50

6.0

2.50 6.0

5.0 2.50 6.0

5.0 2.50

6.0

5.0 2.50 6.0

OSR INSTRUCTION TIMING

17

Page 19

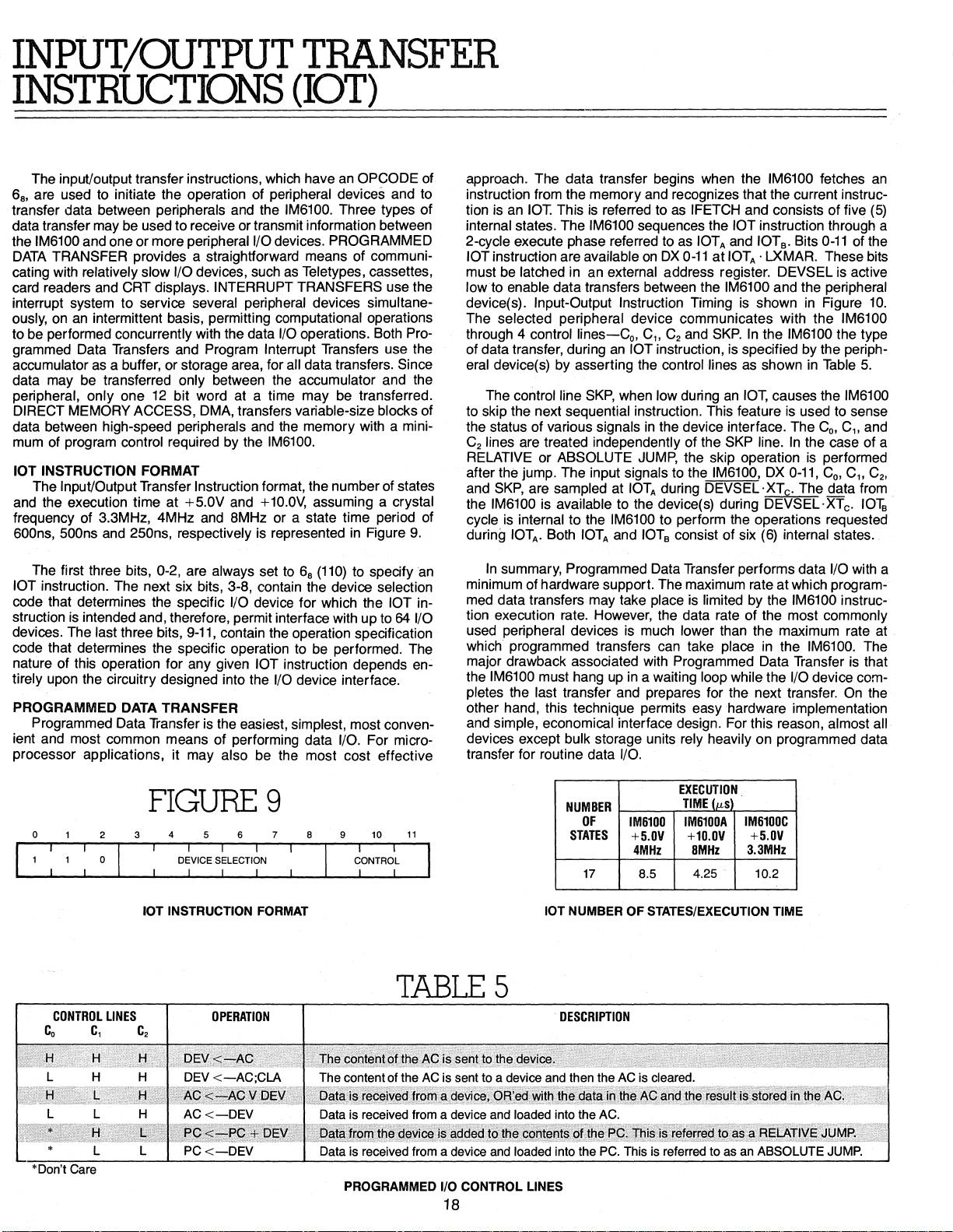

INPUT/OUTPUT

TRANSFER

INSTRUCTIONS

The input/output transfer instructions, which have

6

,

are used to initiate the operation of peripheral devices and to

a

transfer data between peripherals and the

data transfer may be used to receive or transmit information between

IM6100 and one or more peripheral I/O devices. PROGRAMMED

the

DATA

TRANSFER provides a straightforward means of communicating with relatively slow

card readers and CRT displays.

interrupt system to service several peripheral devices simultaneously, on

to be performed concurrently with the data

grammed Data Transfers and Program

accumulator as a buffer, or storage area, for

data may be transferred only between the accumulator and the

peripheral, only one

DIRECT MEMORY ACCESS, DMA, transfers variable-size blocks of

data between high-speed peripherals and the memory with a minimum of program control required by the

lOT INSTRUCTION FORMAT

and the execution time at

frequency of 3.3MHz, 4MHz and 8MHz or a state time period of

600ns, 500ns and 250ns, respectively is represented

an

intermittent basis, permitting computational operations

Input/Output Transfer Instruction format, the number of states

The

I/O devices, such

INTERRUPT TRANSFERS use the

12

bit word at a time may be transferred.

+5.0V

and +10.0V, assuming a crystal

(lOT)

an

OPCODE of

IM6100. Three types of

as

Teletypes, cassettes,

I/O operations. Both Pro-

Interrupt Transfers use the

a"

data transfers. Since

IM6100.

in

Figure

9.

approach. The data transfer begins when the IM6100 fetches

instruction from the memory and recognizes that the current instruc-

lOT.

This

is

tion is an

internal states. The

2-cycle execute phase referred to as

lOT instruction are available

must be latched in an external address register.

low to enable data transfers between the IM6100 and the peripheral

device(s).

The selected peripheral device communicates with the IM6100

through 4 control

of data transfer, during

eral device(s) by asserting the control lines

The control line

to skip the next sequential instruction. This feature

the status of various signals

C

lines are treated independently of the SKP line.

2

RELATIVE or ABSOLUTE JUMP, the skip operation

after the jump. The input signals to the

and

the

cycle is internal to the IM6100 to perform the operations requested

during

Input-Output Instruction Timing

SKP,

are sampled at

IM6100 is available to the device(s) during

IOTA'

Both

referred to as IFETCH and consists of five (5)

IM6100 sequences the lOT instruction through a

IOTA

lines-Co,

an

SKP,

when low during

IOTA

and

on

DX

0-11

C"

C2 and

lOT instruction, is specified by the periph-

in

the device interface. The

IOTA

during DEVSEL· XTc. The data from

lOTs

consist of six

and lOTs. Bits

at

IOTA' LXMAR. These bits

is

shown

SKP.

In the IM6100 the type

as

shown in Table

an

lOT,

causes the IM6100

IM6100, DX

DEVSEL·XT

(6)

0-11

DEVSEL is active

in

Figure

is

used to sense

Co,

In

the case of a

is

performed

0-11,

Co,

internal states.

of the

C"

C"

.

c

an

10.

5.

and

C

lOTs

,

2

The first three bits, 0-2, are always set to 6a (110)

lOT instruction. The next six bits, 3-8, contain the device selection

code that determines the specific

struction is intended and, therefore, permit interface with up to

devices. The last three bits,

code that determines the specific operation to be performed. The

nature of this operation for any given

tirely upon the circuitry designed into the

PROGRAMMED DATA TRANSFER

Programmed Data Transfer is the easiest, simplest, most convenient and most common means of performing data

processor applications, it may also be the most cost effective

FIGURE

o 2 3

4 5 6 7

lOT INSTRUCTION FORMAT

I/O device for which the lOT in-

9-11,

contain the operation specification

lOT instruction depends en-

I/O device interface.

9

to specify an

I/O. For micro-

9

8

10

64

I/O

11

TABLE

CONTROL

Co

C,

LINES

C

2

OPERATION

In

summary, Programmed Data Transfer performs data I/O with a

minimum of hardware support. The maximum rate at which program-

+5.DV

3.3MHz

10.2

IM6100 instruc-

IM6100. The

On

the

a"

med data transfers may take place is limited by the

tion execution rate. However, the data rate of the most commonly

used peripheral devices is much lower than the maximum rate at

which programmed transfers can take place in the

major drawback associated with Programmed Data Transfer is that

IM6100 must hang

the

pletes the last transfer and prepares for the next transfer.

other hand, this technique permits easy hardware implementation

and simple, economical interface design. For this reason, almost

devices except bulk storage units rely heavily on programmed data

transfer for routine data

lOT NUMBER

up

NUMBER

OF

STATES

17

in a waiting loop while the I/O device com-

I/O.

EXECUTION

TIME

(ILS

IM6100

+5.0V

4MHz

OF

IM6100A

+10.0V

8MHz

8.5

4.25

STATES/EXECUTION TIME

IM6100C

5

DESCRIPTION

'Don't

Care

L L

PC

<-DEV

:t~~;6oote~{0ftn~~Cis.

The content of the AC is sent to a device and then the AC is cleared.

i

tq~tli'i~

~ei~ly~gfr()rn

s'etlt,

tothed~vi~.i

a~~SiG~;;gFi:~d'Wjih~hie'g~t~

irrth~f.<::ar(j

theresuitiisstor,i(fioih~,A.C.

REl:A'-i~E;.JUM,B··

Data is received from a device and loaded into the PC. This is referred to as an ABSOLUTE JUMP.

PROGRAMMED

I/O CONTROL LINES

18

i

Page 20

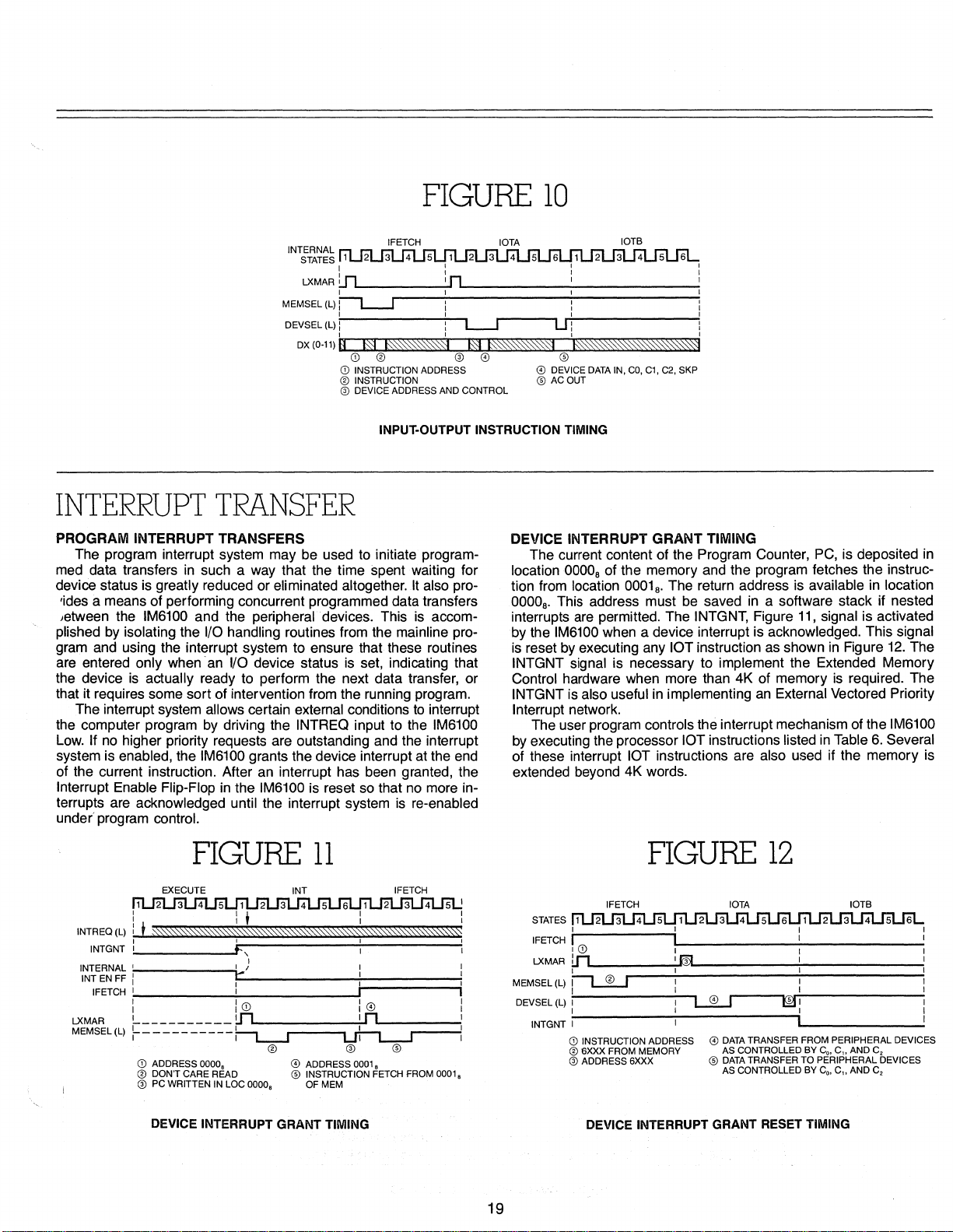

FIGURE

10

IFETCH

1

________

~:n

~----------~--------------~

L-1

t§l

~~~~~

o ® @ @ ®

INPUT-OUTPUT INSTRUCTION TIMING

~

INTERRUPT

TRANSFER

INTERNAL

STATES

, I

~MARUl,--

MEMSEL (L)

DEVSEL (L) : :

1 -

~.-------:----------------+:----------------i

1

DX(0.11)H

o INSTRUCTION ADDRESS @ DEVICE

® INSTRUCTION ® AC OUT

@ DEVICE ADDRESS AND CONTROL

PROGRAM INTERRUPT TRANSFERS

The program interrupt system may be used to initiate program-

in

med data transfers

device status is greatly reduced or eliminated altogether.

such a way that the time spent waiting for

It

also pro'ides a means of performing concurrent programmed data transfers

,etween the

IM6100 and the peripheral devices. This is accomplished by isolating the I/O handling routines from the mainline program and using the interrupt system to ensure that these routines

are entered only when

is

the device

actually ready to perform the next data transfer, or

an

I/O device status is set, indicating that

that it requires some sort of intervention from the running program.

The interrupt system

the computer program

Low.

If

no

higher priority requests are outstanding and the interrupt

system is enabled, the

allows certain external conditions

by

driving the INTREQ input to the IM6100

to

interrupt

IM6100 grants the device interrupt at the end

of the current instruction. After an interrupt has been granted, the

Interrupt Enable Flip-Flop

terrupts are acknowledged until the interrupt system

in

the IM6100 is reset so that no more in-

is

re-enabled

under program control.

IOTA

~'----------------i

U :

&~~~~

'~~~~",~~\~~\~

DATA

IN,

CO,

C1,

C2, SKP

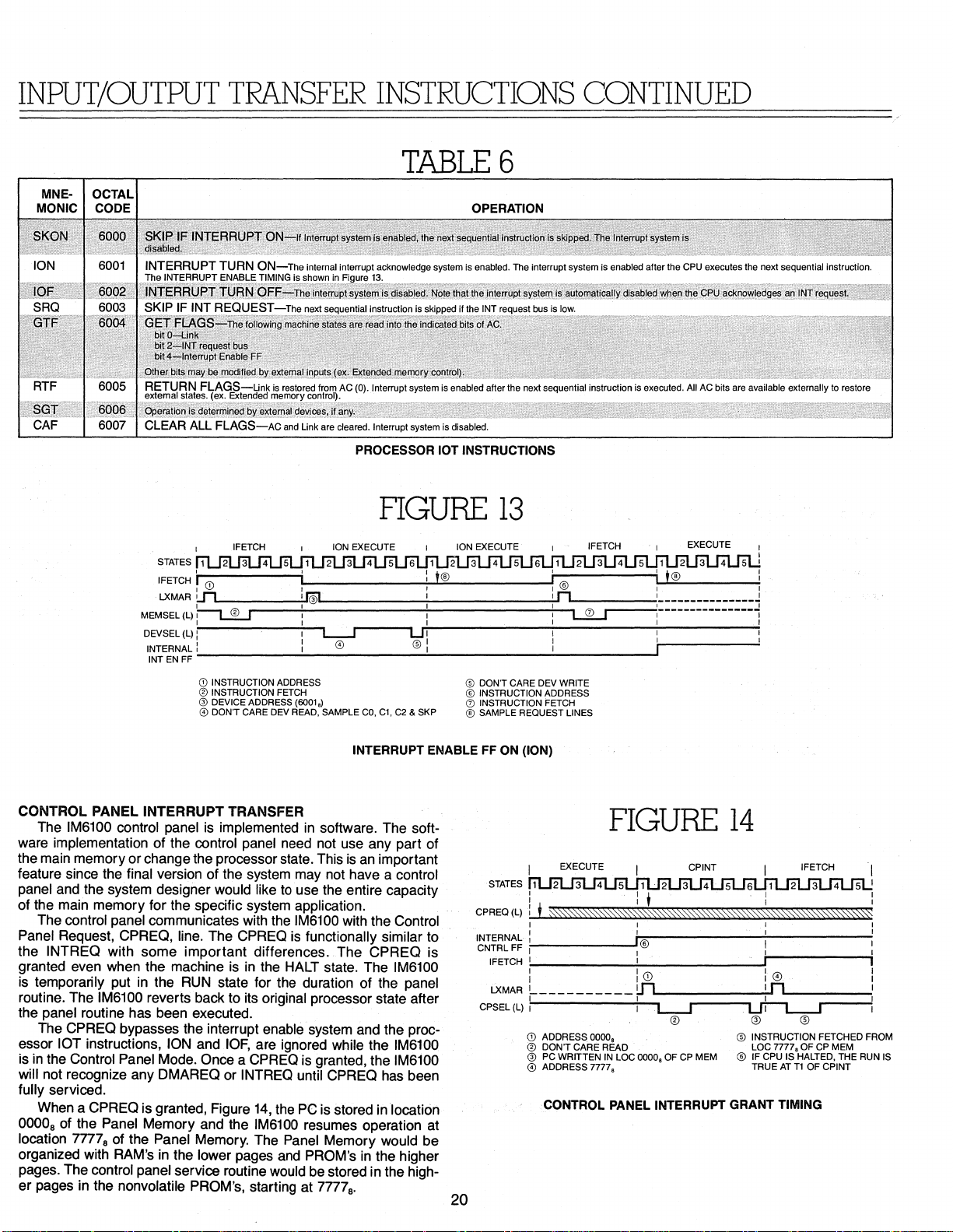

DEVICE INTERRUPT GRANT TIMING

The current content of the Program Counter,

location

tion from location

0000

interrupts

by the

is reset by executing any

00008 of the memory and the program fetches the instruc-

,

0001

The return address is available in location

,

This address must be saved

8

are

permitted. The INTGNT, Figure

8

in

a software stack if nested

IM6100 when a device interrupt is acknowledged. This signal

lOT instruction as shown

PC,

is deposited in

11,

signal is activated

in

Figure

INTGNT signal is necessary to implement the Extended Memory

is

Control hardware when more than 4K of memory

INTGNT is also useful in implementing

an

External Vectored Priority

required. The

Interrupt network.

The user program controls the interrupt mechanism of the

by

executing the processor lOT instructions listed

of these interrupt

lOT instructions are also used if the memory is

in

Table

6.

extended beyond 4K words.

12.

The

IM6100

Several

FIGURE

EXECUTE

INT

EN

FF : 1

IFETCH , I

INTERNAL

t=====J=======J======~

~

o ADDRESS 0000,

® DON'T CARE READ

@ PC WRITTEN IN LOC 0000,

DEVICE INTERRUPT GRANT TIMING

11

INT

________

®

@ ADDRESS 0001,

® INSTRUCTION FETCH FROM 0001,

OFMEM

:@

~:n~

__

I

@ ®

IFETCH

~==~

19

STATES

IFETCH I

~MAR

MEMSEL(L)

DEVSEL (L)

INTGNT I

FIGURE

IFETCH

1

1

10

lI1'--

________

1

~

I I

!..,

-----------:.---.~r----...,@r.,---------------:

, 1

o INSTRUCTION ADDRESS @

® 6XXX FROM MEMORY AS CONTROLLED BY

@ ADDRESS 6XXX ®

DEVICE INTERRUPT GRANT RESET TIMING

~

L----------.;.-----------i

12

IOTA

,

IL.

____________

DATA

TRANSFER FROM PERIPHERAL DEVICES

DATA

TRANSFER TO PERIPHERAL DEVICES

AS CONTROLLED

BY

Co,

Co,

C"

C"

AND

AND

C,

C,

---..:

Page 21

INPUT/OUTPUT

TRANSFER

INSTRUCTIONS

CONTINUED

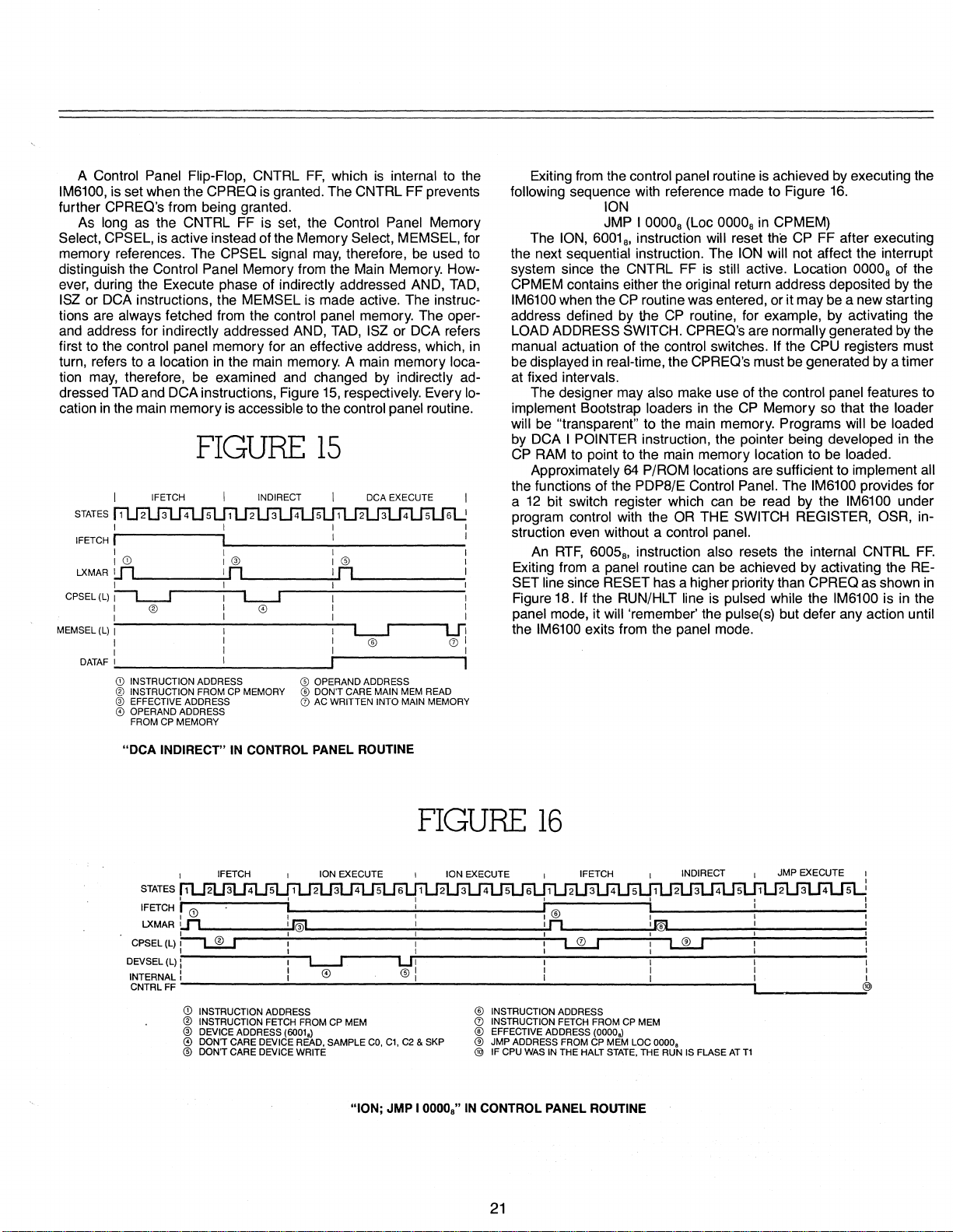

TABLE

PROCESSOR lOT INSTRUCTIONS

FIGURE

STATES

IFETCH

~MARur1~;_;:::::f:~~®~::::::::::::±:::::::::::::~~~;_;:::~'

MEMSEL

(L)

DEVSEL

(L)

INTERNAL i : ® ® i

INTENFF~-----~-------~------~-----~

IFETCH

1 1 2

r!

(iQ);------jiL

~:

I I I I I

i I

ION

EXECUTE

______

L-'

..J...~

______

I

U I :

ION

6

13

EXECUTE

IFETCH

J_;;;_-----L,

LS2.....J

EXECUTE

.tt®~8~

___

::::::::::::::::~

1-1

-----....:

~,

I

CD

INSTRUCTION

® INSTRUCTION

®

DEVICE

® DONT

ADDRESS

CARE

DEV

ADDRESS

FETCH

(6001,)

READ,

SAMPLE

CO,

C1,

C2 & SKP

INTERRUPT ENABLE FF ON (ION)

CONTROL PANEL INTERRUPT TRANSFER

The IM6100 control panel is implemented in software. The software implementation

the main memory

of

the control panel need not use any part of

or

change the processor state. This

is

an

important

feature since the final version of the system may not have a control

panel and

system designer would like

to

use the entire capacity

the

of the main memory for the specific system application.

The control panel communicates with the

Panel Request, CPREQ,

the

INTREQ with some

line, The CPREQ is functionally similar to

important

granted even when the machine is in the HALT state, The

IM6100 with the Control

differences.

The

CPREQ is

IM6100

is temporarily put in the RUN state for the duration of the panel

routine. The

IM6100 reverts back to its original processor state after

the panel routine has been executed.

The CPREQ bypasses the interrupt enable system and the proc-

essor lOT instructions, ION and

IOF,

are ignored while the IM6100

is in the Control Panel Mode. Once a CPREQ is granted, the IM6100

will

not recognize any DMAREQ or INTREQ until CPREQ has been

fully serviced.

14,

When a CPREQ is granted, Figure

OOOOa

of the Panel Memory and the IM6100 resumes operation at

location

7n7

a of the Panel Memory. The Panel Memory would be

the PC is stored in location

organized with RAM's in the lower pages and PROM's in the higher

pages. The control panel service routine would be stored in the

er pages in the nonvolatile PROM's, starting at

7n7

.

a

high-

® DONT

CARE

DEV

®

INSTRUCTION

® INSTRUCTION

®

SAMPLE

STATES

CPREQ(L)

INTERNAL :

CNTRL

FF

IFETCH

~MAR

CPSEL (L) I I .

WRITE

ADDRESS

FETCH

REQUEST

LINES

EXECUTE

W-~~~~~~~~~~~~~~~~~~~~

--------hI®5""""------II------~

;-

~-----+'

~1~~::::~~~1l~-~::::::~~:r1~-~::::~

CD

ADDRESS 0000,

® DONT CARE

®

PC

WRITTEN

o ADDRESS 7777,

CONTROL PANEL INTERRUPT

20

FIGURE

I

I

I I

------....:...~I------l

I Q) : 0

L.....J

CPINT

14

.

ur-L....J

IFETCH

® ® ®

READ

IN

LOC

0000,

OF

CP

® INSTRUCTION FETCHED

LOC 7777,

® IF

MEM

CPU

TRUE

GRANT

OF

IS

HALTED,

AT

T1

OF

TIMING

CP

MEM

THE

CPINT

FROM

RUN

IS

Page 22

A Control Panel Flip-Flop,

IM6100,

further

Select,

is set when the CPREO is granted. The

CPREO's from being granted.

As long as the

CPSEl,

CNTRl

is active instead of the Memory Select, MEMSEl, for

memory references. The

CNTRl

FF,

which

is

CNTRl

FF

is set, the Control Panel Memory

CPSEl

signal

may,

therefore,

internal

FF prevents

be

used

to

the

distinguish the Control Panel Memory from the Main Memory. How-

ever, during the Execute phase of indirectly addressed AND,

ISZ

or DCA instructions, the

MEMSEl

is made active. The instruc-

TAD,

tions are always fetched from the control panel memory. The oper-

and

address for indirectly addressed AND,

first to the control panel memory for

turn, refers

tion

dressed

cation

to

a location

may,

therefore, be examined and changed by indirectly ad-

TAD

and DCA instructions, Figure

in

the main memory is accessible to the control panel routine.

in

the main memory. A main memory loca-

FIGURE

INDIRECT

_____

I@

I~rl~

____

L--l

CP

MEMORY

STATES

IFETCH

~MAR

CPSEL(L)

MEMSEL

DATAF

IFETCH

1

I

1,--------,1-

I I I

I~

Ul~

_____

I I I 1

~

I ® 0 I I

I I I

(L)

I '----J LJi

I ®

I I

;",,1

____________

(7)

INSTRUCTION ADDRESS

® INSTRUCTION

@ EFFECTIVE ADDRESS

o OPERAND ADDRESS

FROM

CP

MEMORY

FROM

....

TAD,

an

effective address, which,

ISZ or DCA refers

15,

respectively. Every

15

DCA

EXECUTE

--,-

________

I®

~Ir1~

______

-----'I--------I

--'

® OPERAND ADDRESS

® DON'T

CARE

MAIN

(7)

AC WRITTEN INTO

MEM

MAIN

(7)

READ

MEMORY

~

I

Exiting

from

the control panel routine

following sequence with reference made to Figure

is

achieved by executing the

16.

ION

OOOOa

(loc

OOOOa

in

JMP I

The

ION,

6001

instruction will reset the CP FF after executing

,

the next sequential instruction. The

to

system since the

a

CNTRl

FF

is

still active. location

CPMEM)

ION

will not affect the interrupt

CPMEM contains either the original return address deposited

IM6100 when the

address defined by

lOAD

ADDRESS SWITCH. CPREO's are normally generated

in

manual actuation of the control switches.

be displayed

CP

routine was entered, or it may be a new starting

the

CP

routine, for example, by activating the

If the CPU registers must

in

real-time, the CPREO's must be generated by a timer

at fixed intervals.

lo-

The designer may also make use of the control panel features to

in

the

CP

implement Bootstrap loaders

Memory

so

will be "transparent" to the main memory. Programs will be loaded

by DCA

CP

I POINTER instruction, the pointer being developed

RAM

to

point to the main memory location to be loaded.

64

Approximately

P/ROM locations are sufficient to implement all

the functions of the PDP8/E Control Panel. The IM6100 provides for

a

12

bit switch register which can be read by the

program control with the

struction even without a control panel.

.

An

RTF,

6005

a

Exiting from a panel routine can

OR

THE SWITCH REGISTER, OSR, in-

instruction also resets the internal

,

be

achieved by activating the RE-

SET line since RESET has a higher priority than CPREO as shown

Figure 18. If the RUN/HlT line is pulsed while the IM6100 is

panel mode, it will 'remember' the pulse(s) but defer any action until

IM6100

the

I

exits from the panel mode.

OOOOa

of the

by

the

by

the

that the loader

in

the

IM6100

under

CNTRl

FF.

in

in

the

"DCA

INDIRECT" IN CONTROL PANEL ROUTINE

FIGURE

ION

STATES

1

EXECUTE

5

IFETcHr'~~~~----L-------~-----------f'7.®~---------Li----------~L-

~MARLI1~;_;:::::~~::::::::::::~::::::::::::~I:r1~~;_;:::::j:~~~~~~::::+=::::::::::~

CPSEL

(L)

~

DEVSEL (L):-:

INTERNAL: 0 ® i :

CNTRLFF~----------~--------------~--------------~----------~----------_;

1 1

-------------:--...,L-Jr-----,W..:-I----------------:--------------:-------------i--------------:

~ INSTRUCTION

® INSTRUCTION

@ DEVICE ADDRESS

o DON'T CARE DEVICE

® DON'T CARE

ADDRESS

FETCH

(6001,)

DEVICE

FROM

READ.

WRITE

CP

MEM

SAMPLE

CO.

C1.

"ION; JMP I 0000

:

C2 & SKP

ION

EXECUTE

2

® INSTRUCTION ADDRESS

(7)

INSTRUCTION

® EFFECTIVE

®

JMP

®

IF

IN

CONTROL PANEL ROUTINE

"

8

ADDRESS

CPU

WAS

16

L2...J

FETCH

ADDRESS

FROM

IN

THE

IFETCH

FROM

(0000,)

CP

HALT

CP

MEM

STATE.

I LJ2...j

MEM

LOC

0000,

THE

RUN

INDIRECT

IS

FLASE

____________

AT

T1

EXECUTE

JMP

__________

~

I

~®

21

Page 23

INPUT/OUTPUT

TRANSFER

INSTRUCTIONS

CONTINUED

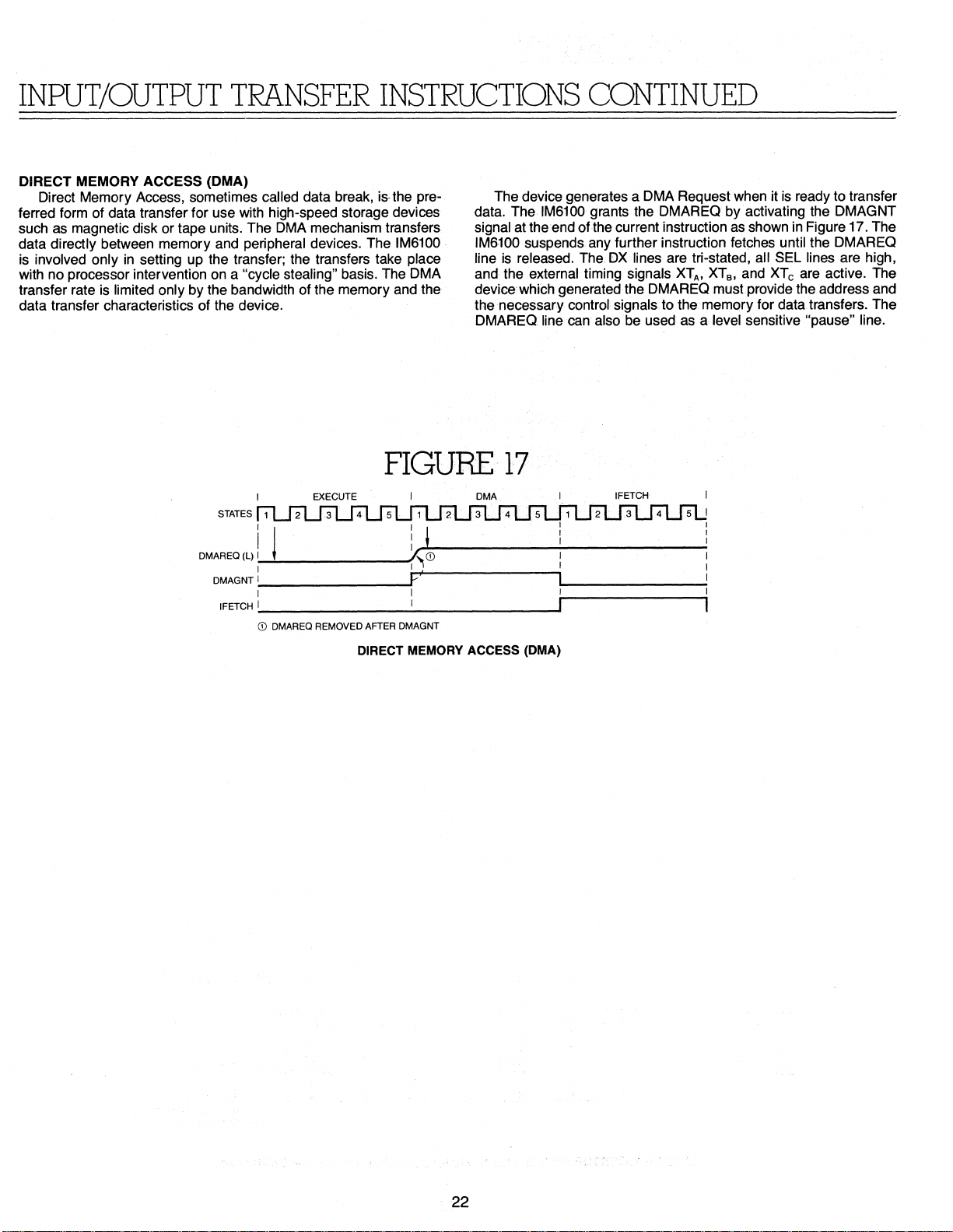

DIRECT MEMORY ACCESS (DMA)

Direct Memory Access, sometimes

ferred form

such as magnetic disk

data

is involved only

with

transfer rate is limited only

data transfer characteristics

of

data transfer for use with high-speed storage devices

directly between memory and peripheral devices. The IM6100

no

processor intervention on a "cycle stealing" basis. The

or

tape units. The DMA mechanism transfers

in

setting up the transfer; the transfers take place

by

the bandwidth

of

the device.

called data break,

STATES

1

of

the memory and the

EXECUTE

is-

the pre-

DMA

data. The

signal at the end

IMS100 suspends any further instruction fetches until the DMAREQ

line

and the

device which generated the

the necessary

DMAREQ.line can also be used as a level sensitive "pause" line.

FIGURE

DMA

The device generates a DMA Request when it

IM6100 grants the DMAREQ

of

the current instruction as shown in Figure 17. The

is

released. The. DX lines are tri-stated, all SEL lines are high,

external timing signals

control signals. to the memory for

XT

DMAREQmustprovide

by

,

XT

B

A

is

activating the DMAGNT

and

,

ready to transfer

XTc

are active.

the address and

data

transfers.

17

IFETCH

The

The

DIRECT MEMORY ACCESS (OMA)

22

Page 24

INTERNAL

PRIORITY

STRUCTURE

After

an

generator scans the

The state of the priority network decides the next sequence of the

IM6100.

The request lines,

INTREO, are sampled

time

T1.

request

tion preceded

an

autoindexed

cycle instruction. The worst case response time

states,

When the

generator

a maximum

is

powered on, must span

34

clocks for the counter

cycles (20 to

lines.

The internal priority

INTREO,

instruction

The worst case response time of the

is,

therefore, the time required to execute the longest instruc-

by

ISZ,

14

fLs

at 5 volts.

IM6100

is

undefined. The generator

of

34 clock pulses. The request inputs,

24

clocks) for the state generator to sample the request

and IFETCH.

is

completely sequenced, the major state

internal priority network

RESET,

in

any 6-state execution cycle. For the

22

is initially powered up, the state

is

CPREO, RUN/HLT, DMAREO

the last cycle

states, preceded

at

least

58

to

initialize and a maximum

RESET,

CPREO, RUN/HLT, DMAREO,

as

shown

of

an

instruction execution, at

IM6100

by

any 6-state execution

is

automatically initialized with

clock pulses to

in

to

IM6100,

is,

therefore,

of

as

the

be

recognized,

of

two

Figure 18.

an

external

this

the timing

IM6100

IM6100

and

28

IFETCH

If

no

external requests are pending, the

instruction pointed

active during the cycle

devices

functional class of the current instruction. For example, the external

memory extension hardware must know when JMP or JMS instruc-

tions

is

the

AUTOINDEX Memory Reference Instructions

state sequence to generate the Effective Address,

operand. The subsequent sequence, referred

phase,

EXECUTE phase

Microinstruction consists of

cycle EXECUTE phase.

have

OPR instructions.

T

(WRITE).

instructions are identical. The Device Address

available

tions.

can control the C-lines for data transfers to implement Get Flags

(GTF), Return Flags (RTF), and Clear All Flags (CAF) instructions.

External Control of the C-lines

internal lOT instructions since the flag bits may

inside

can

are

fetched to implement the Extended Memory Control.

The Programmable Logic

IM6100

is

controlled

an

optional second cycle, depending

4,

and

T

5,

The state sequence for internal (processor)

in

External hardware, for example Extended Memory Control,

and

outside the

to

by

the contents of the

in

which the instruction

monitor

to execute the fetched instruction. All INDIRECT and

with

the External Address Register for internal lOT instruc-

OX,

0-2, during IFETCH·XTA to

Array,

PLA, in the

by

the functional class

of

AND,

TAD,

DCA,

only one cycle. ISZ and lOT have a 2-

OPR Group 1 and Group 2 Microinstructions

An

IM6100

an

optional sixth state, T

IM6100.

cycle consists of 5 states, T

is

necessary to implement these

IM6100

PC.

JMS, JMP

on

fetches the next

The IFETCH line

is

fetched. External

IM6100

go

through a common

to

as

of

the instruction. The

and

the microcoding of the

6,

for Output Transfers

and

and

be

the EXECUTE

Control bits are

distributed both

is

determine the

sequences

EA,

of the

OPR Group 3

,

T

2, T 3,

1

external lOT

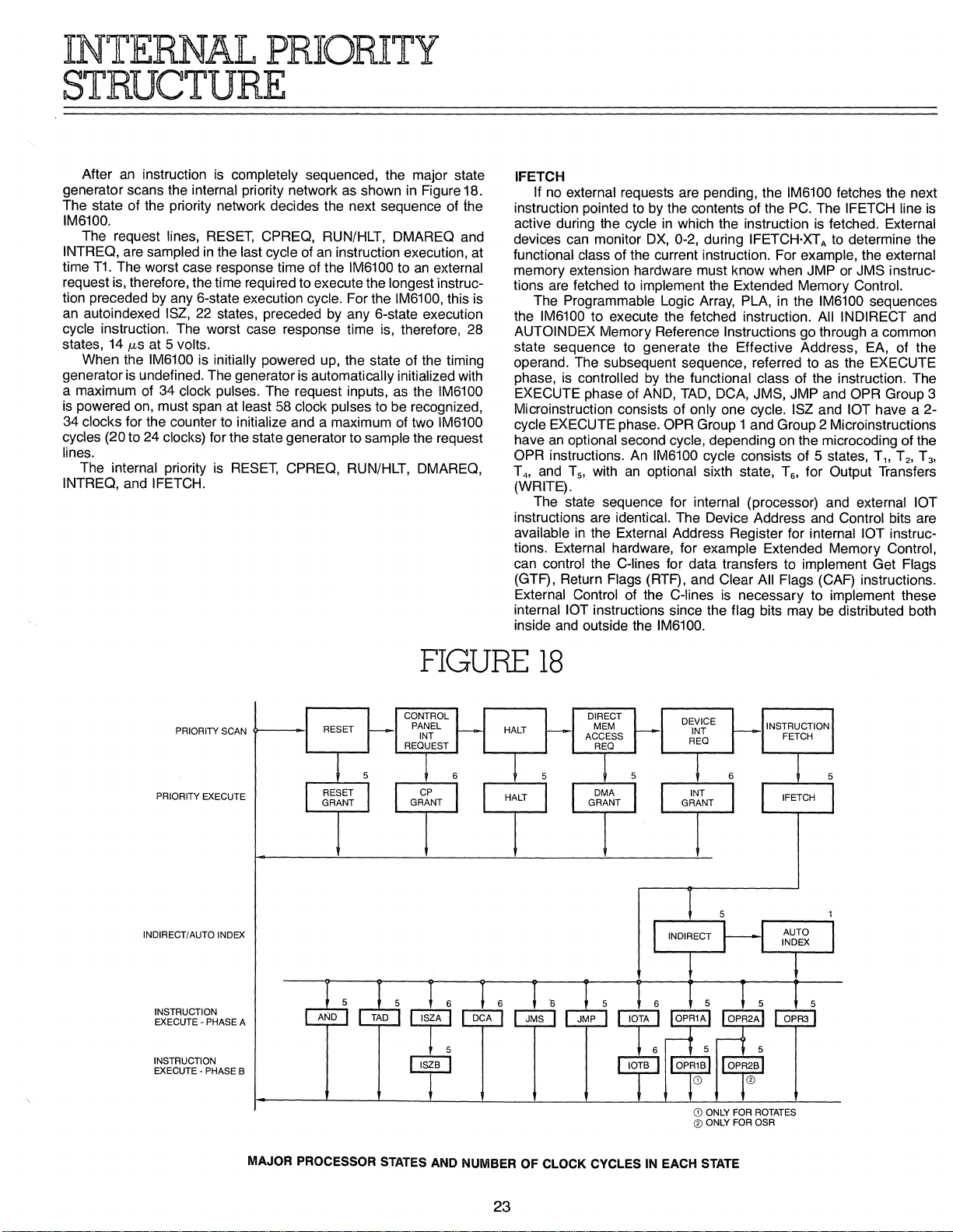

PRIORITY SCAN

PRIORITY EXECUTE

INDIRECT/AUTO INDEX

INSTRUCTION

EXECUTE·

INSTRUCTION

EXECUTE· PHASE

PHASE A

B

1>---1

RESET

FIGURE

HALT

~

18

5

G8

6

1

I

lor

6

T

DEVICE

INT

REO

GT

5

IOTBI

IOTBI

CD

CD

ONLY FOR

CD

ONLY FOR OSR

6

5

5

CD

T

ROTATES

MAJOR PROCESSOR STATES AND NUMBER OF CLOCK CYCLES IN EACH STATE

23

Page 25

INTERNAL

PRIORITY

STRUCTURE

CONTINUED

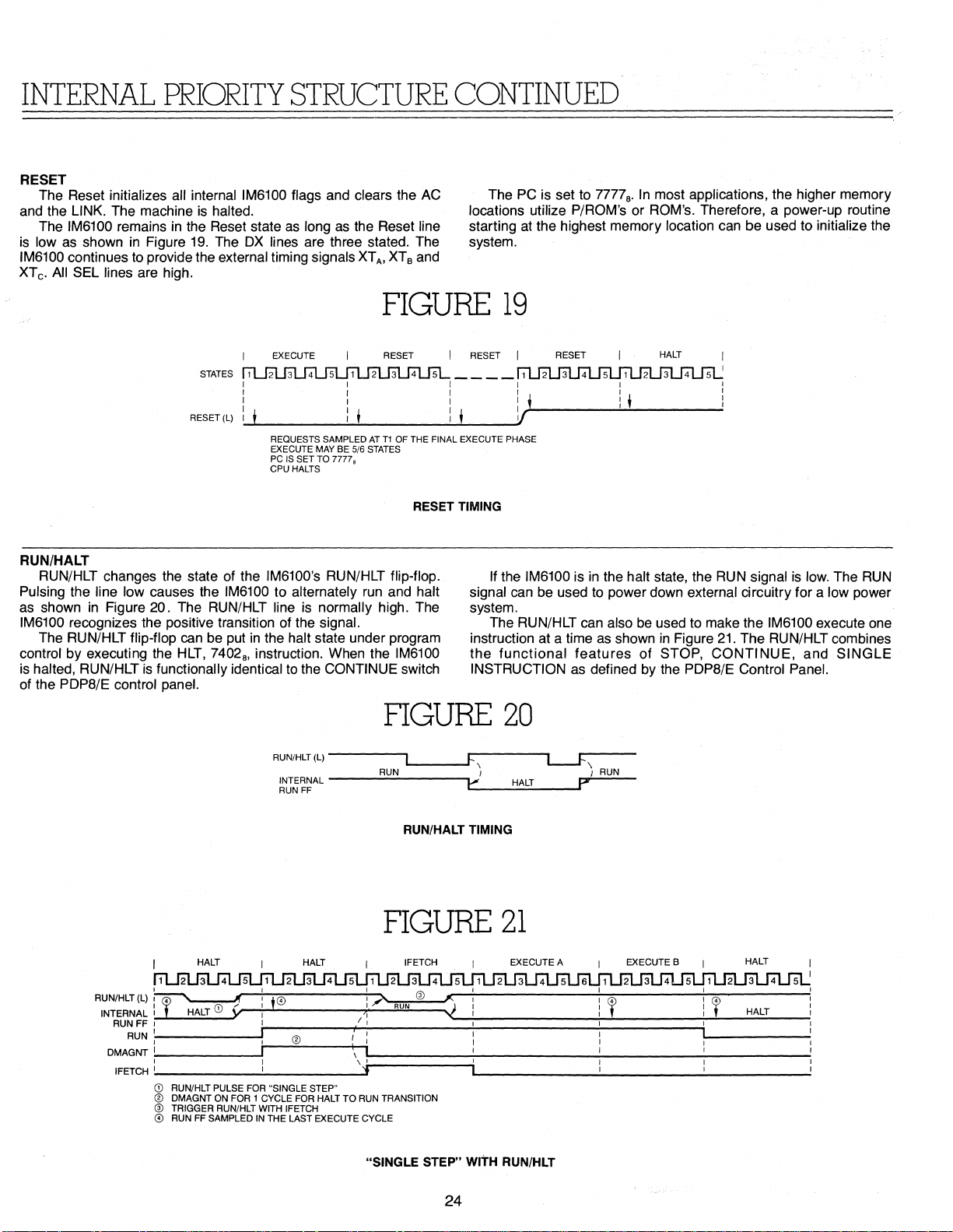

RESET

The Reset initializes all internal IM6100 flags and clears the

and the LINK. The machine

IM6100 remains

The

is

low

as

IM6100 continues

shown

XT

c.

All SEL lines are high.

in

Figure

to

provide the external timing signals XT

is

halted.

in

the Reset state

19.

The

as

long

as

the Reset line

OX

lines are three stated. The

A

,

XT Band

FIGURE

EXECUTE RESET RESET

STATES

~

RESET (L)

__________

REQUESTS SAMPLED

EXECUTE

PC

IS

SET TO 7777"

CPU HALTS

RUN/HALT

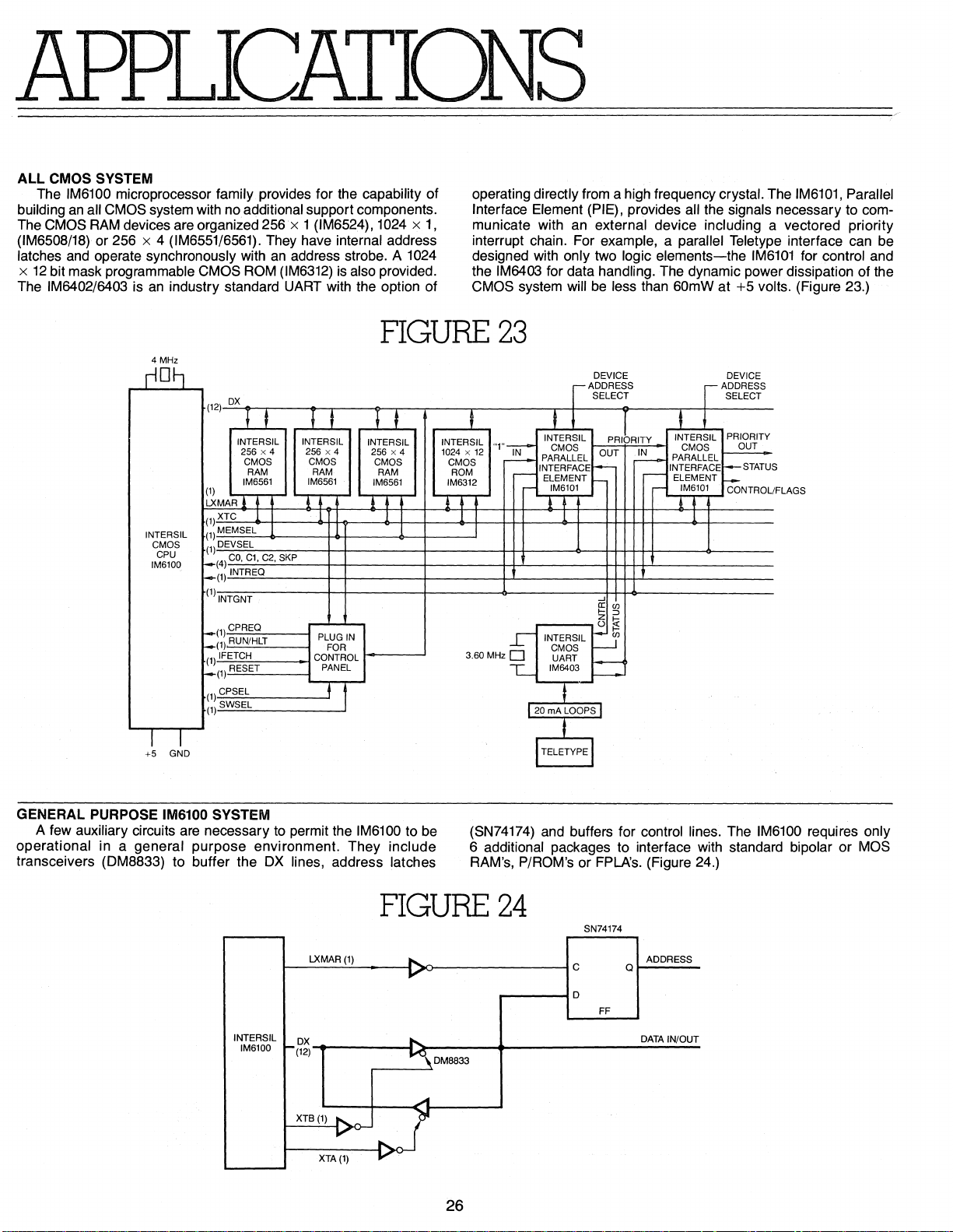

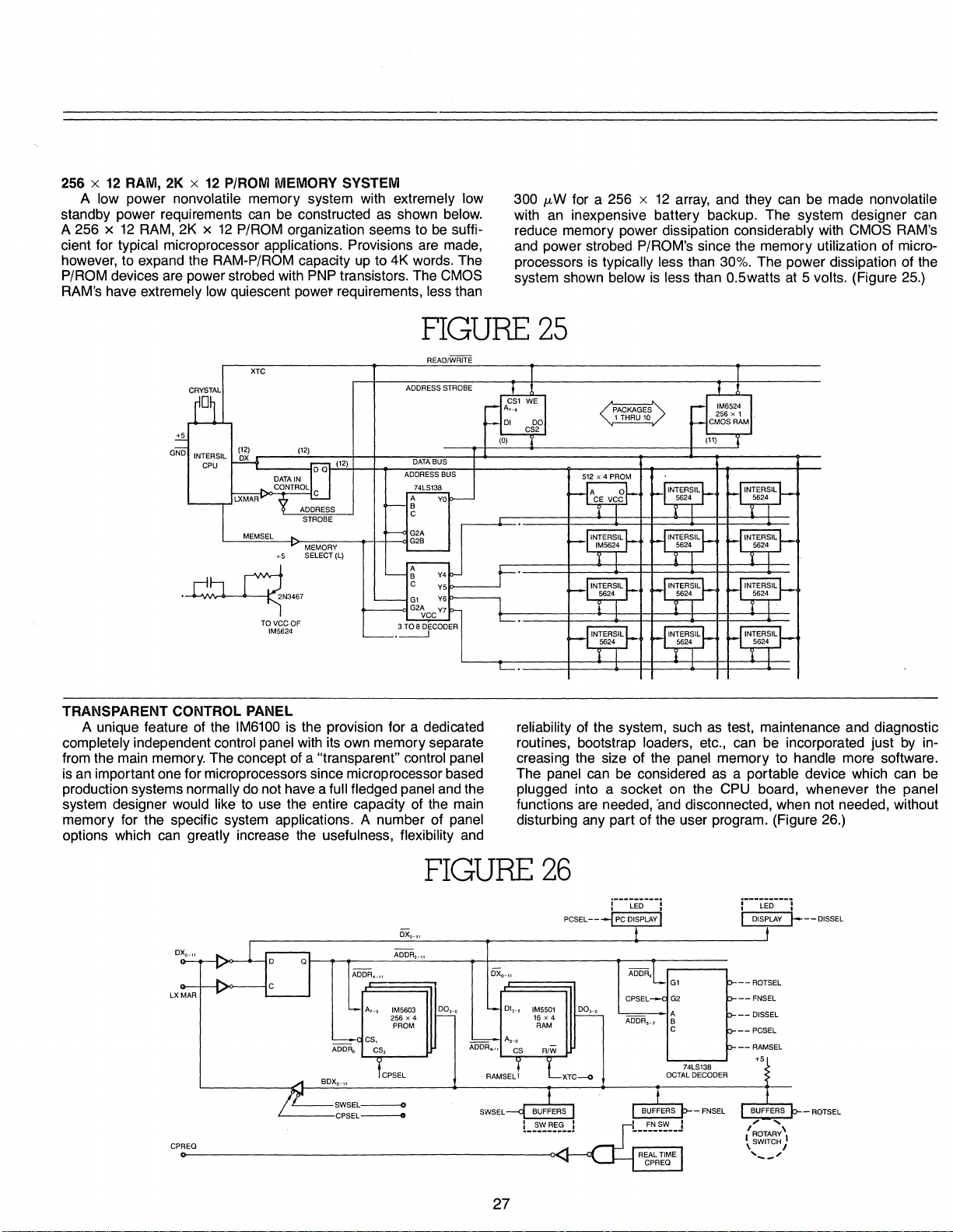

RUN/HLT changes the state of the IM6100's RUN/HLT flip-flop.