Intersil Corporation ICM7231, ICM7232 Datasheet

August 1997

ICM7231, ICM7232

Numeric/Alphanumeric Triplexed

LCD Display Drivers

Features

• ICM7231 Drives 8 Digits of 7 Segments with Two

Independent Annunciators Per Digit Address and Data

Input in Parallel Format

• ICM7232 Drives 10 Digits of 7 Segments with Two

Independent Annunciators Per Digit Address and Data

Input in Serial Format

• All Signals Required to Drive Rows and Columns of

Triplexed LCD Display are Provided

• Display Voltage Independent of Power Supply

• On-Chip Oscillator Provides All Display Timing

• Total Power Consumption Typically 200µW, Maximum

500µW at 5V

• Low-Power Shutdown Mode Retains Data With 5µW

Typical Power Consumption at 5V, 1µW at 2V

• Direct Interface to High-Speed Microprocessors

Description

The ICM7231 and ICM7232 family of integrated circuits are

designed to generate the voltage levels and switching waveforms required to drive triplexed liquid-crystal displays.

These chips also include input buffer and digit address

decoding circuitry allowing six bits of input data to be

decoded into 64 independent combinations of the output

segments of the selected digit.

The family is designed to interface to modern highperformance microprocessors and microcomputers and

ease system requirements for ROM space and CPU time

needed to service a display.

Ordering Information

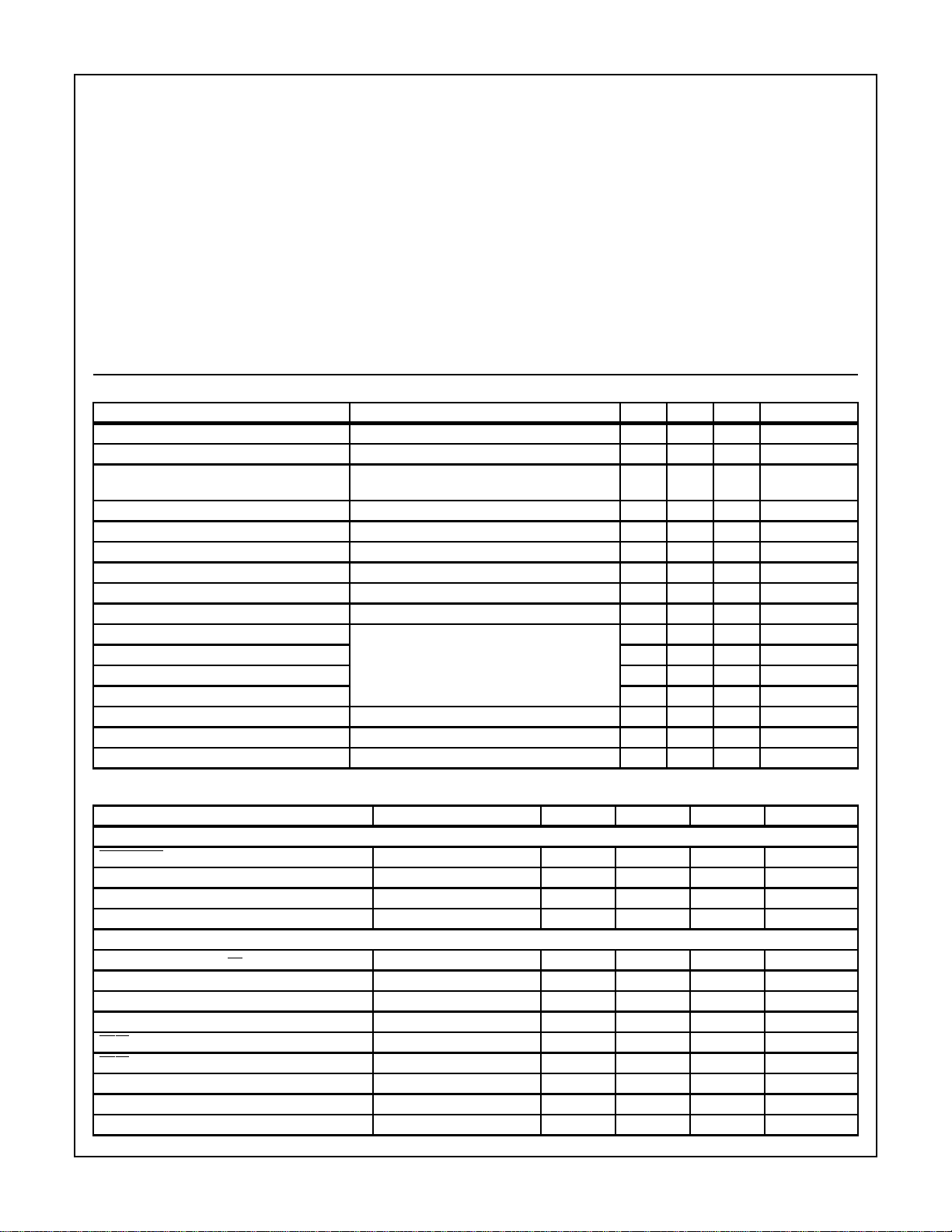

PART NUMBER TEMP. RANGE (oC) PACKAGE NUMBER OF DIGITS INPUT FORMAT PKG. NO.

ICM7231BFIJL -25 to 85 40 Ld CERDIP 8 Digit Parallel F40.6

ICM7231BFIPL -25 to 85 40 Ld PDIP 8 Digit Parallel E40.6

ICM7232BFIPL -25 to 85 40 Ld PDIP 10 Digit Serial E40.6

ICM7232CRIPL -25 to 85 40 Ld PDIP 10 Digit Serial E40.6

NOTE:

All versions intended for triplexed LCD displays.

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

http://www.intersil.com or 407-727-9207

| Copyright © Intersil Corporation 1999

9-19

File Number 3161.1

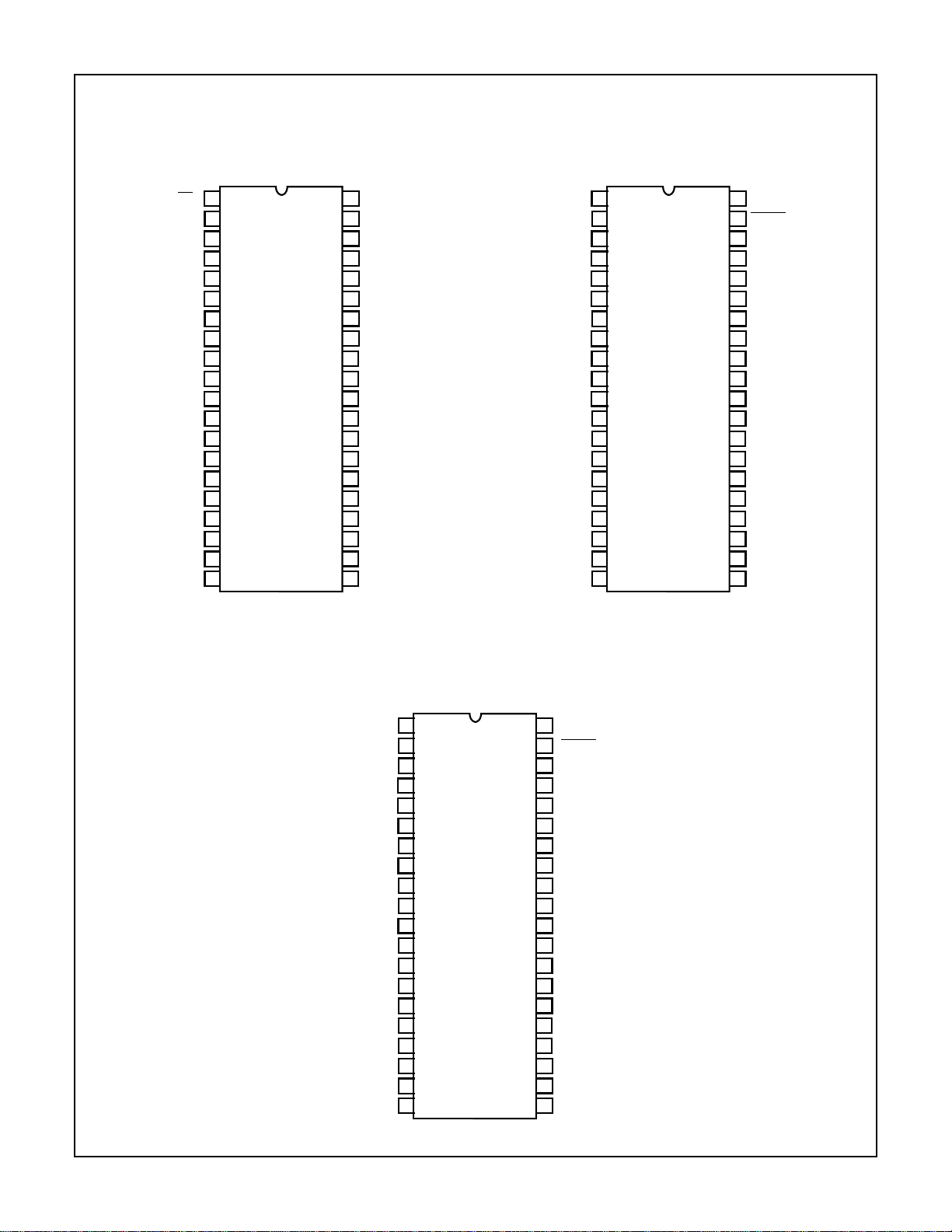

Pinouts

ICM7231BF

(PDIP, CERDIP)

TOP VIEW

ICM7231, ICM7232

ICM7232AF, BF

(PDIP, CERDIP)

TOP VIEW

CS

V

DISP

BP1

BP2

BP3

b1, c1, an11

a1, g1, d1

f1, e1, an21

b2, c2, an12

a2, g2, d2

f2, e2, an22

b3, c3, an13

a3, g3, d3

f3, e3, an23

b4, c4, an14

a4, g4, d4

f4, e4, an24

b5, c5, an15

a5, g5, d5

f5, e5, an25

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

40

V

DD

A2

39

A1

38

A0

37

V

36

SS

BD3

35

BD2

34

BD1

33

BD0

32

AN2

31

AN1

30

f8, a8, an28

29

a8, g8, d8

28

b8, c8, an18

27

f7, e7, an27

26

a7, g7, d7

25

b7, c7, an17

24

f6, e6, an26

23

a6, g6, d6

22

b6, c6, an16

21

DATA CLOCK

INPUT

V

DISP

BP1

BP2

BP3

b1, c1, an11

a1, g1, d1

f1, e1, an21

b2, c2, an12

a2, g2, d2

f2, e2, an22

b3, c3, an13

a3, g3, d3

f3, e3, an23

b4, c4, an14

a4, g4, d4

f4, e4, an24

b5, c5, an15

a5, g5, d5

f5, e5, an25

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

40

V

DD

WRITE INPUT

39

DATA INPUT

38

DATA ACCEPTED

37

OUTPUT

36

V

SS

35

f10, e10, an210

34

a10, g10, d10

33

b10, c10, an110

32

f9, e9, an29

31

a9, g9, d9

30

b9, c9, an19

29

f8, a8, an28

a8, g8, d8

28

b8, c8, an18

27

f7, e7, an27

26

25

a7, g7, d7

24

b7, c7, an17

23

f6, e6, an26

22

a6, g6, d6

21

b6, c6, an16

DATA CLOCK

INPUT

V

DISP

BP1

BP2

BP3

b1, c1, an11

a1, g1, d1

f1, e1, an21

b2, c2, an12

a2, g2, d2

f2, e2, an22

b3, c3, an13

a3, g3, d3

f3, e3, an23

b4, c4, an14

a4, g4, d4

f4, e4, an24

b5, c5, an15

a5, g5, d5

f5, e5, an25

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

ICM7232CR

(PDIP)

TOP VIEW

40

V

DD

WRITE INPUT

39

DATA INPUT

38

DATA ACCEPTED

37

OUTPUT

36

V

SS

b6, c6, an16

35

a6, g6, d6

34

f6, e6, an26

33

b7, c7, an17

32

a7, g7, d7

31

30

f7, e7, an27

29

b8, c8, an18

28

a8, g8, d8

27

f8, a8, an28

26

b9, c9, an19

a9, g9, d9

25

f9, e9, an29

24

b10, c10, an110

23

a10, g10, d10

22

f10, e10, an210

21

9-20

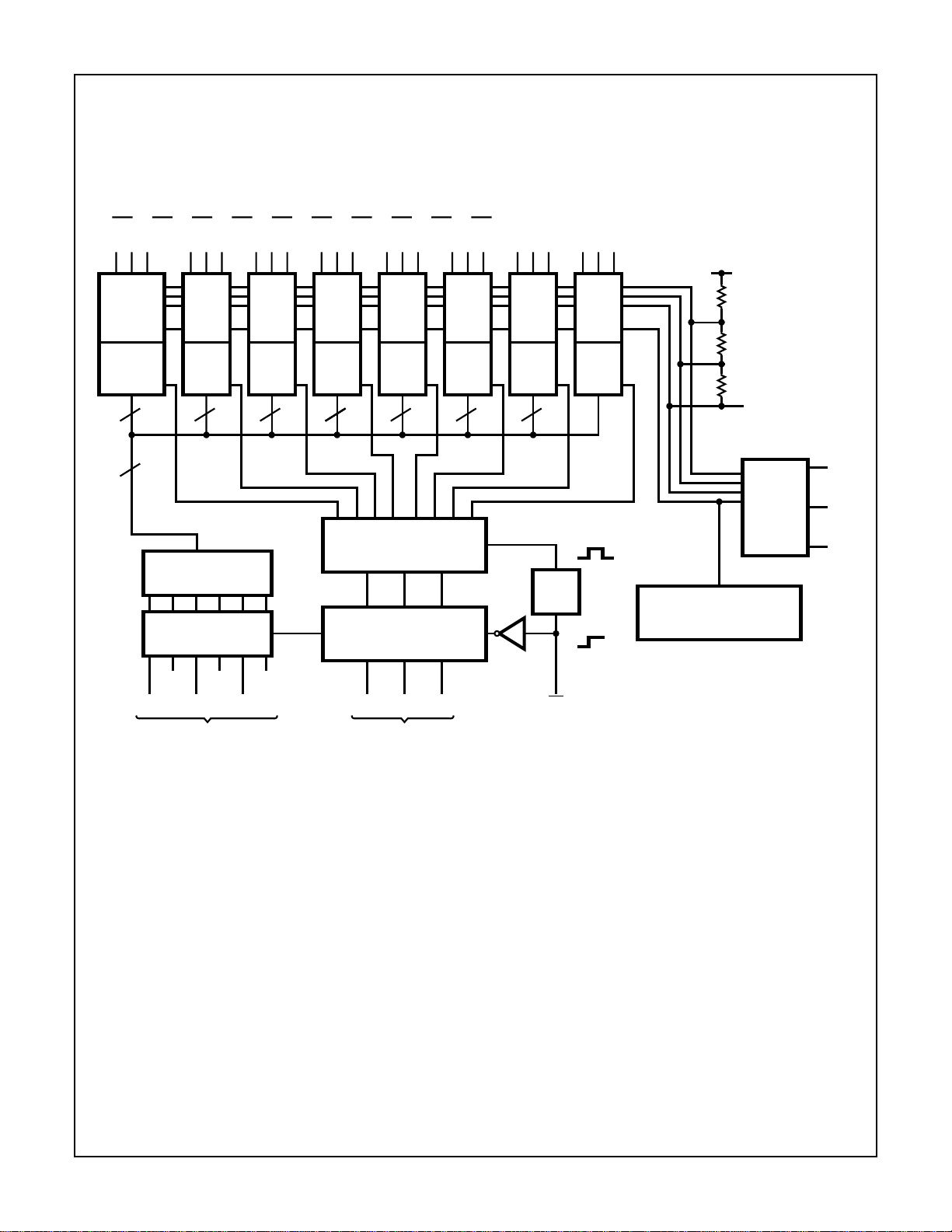

ICM7231, ICM7232

Functional Block Diagrams

ICM7231

D8 D7 D6 D5 D4 D3 D2 D1

f2, e2, an22

SEGMENT

LINE

DRIVERS

3 WIDE

OUTPUT

LATCHES

9 WIDE

99

9 999999

a2, g2, d2

b2, c2, an12

f1, e1, an21

a1, g1, d1

b1, c1, an11

V

DD

ON CHIP

DISPLAY

V

H

VOLTAGE

LEVEL

GENERATOR

V

L

V

DISP

PIN 2 (INPUT)

9

ADDRESS

DAT A

DECODER

DATA INPUT

LATCHES

AN2 BD1 BD3

AN1 BD0 BD2

EN

DECODER

ADDRESS

LATCHES

ADDRESS INPUTSDATA INPUTS

NOTE: See Figure 13 for display segment connections.

DIGIT

INPUT

BP1

COMMON

LINE

DRIVERS

EN

ONE

SHOT

EN

A2A1A0

CS

DISPLAY

TIMING

GENERATOR

BP2

BP3

9-21

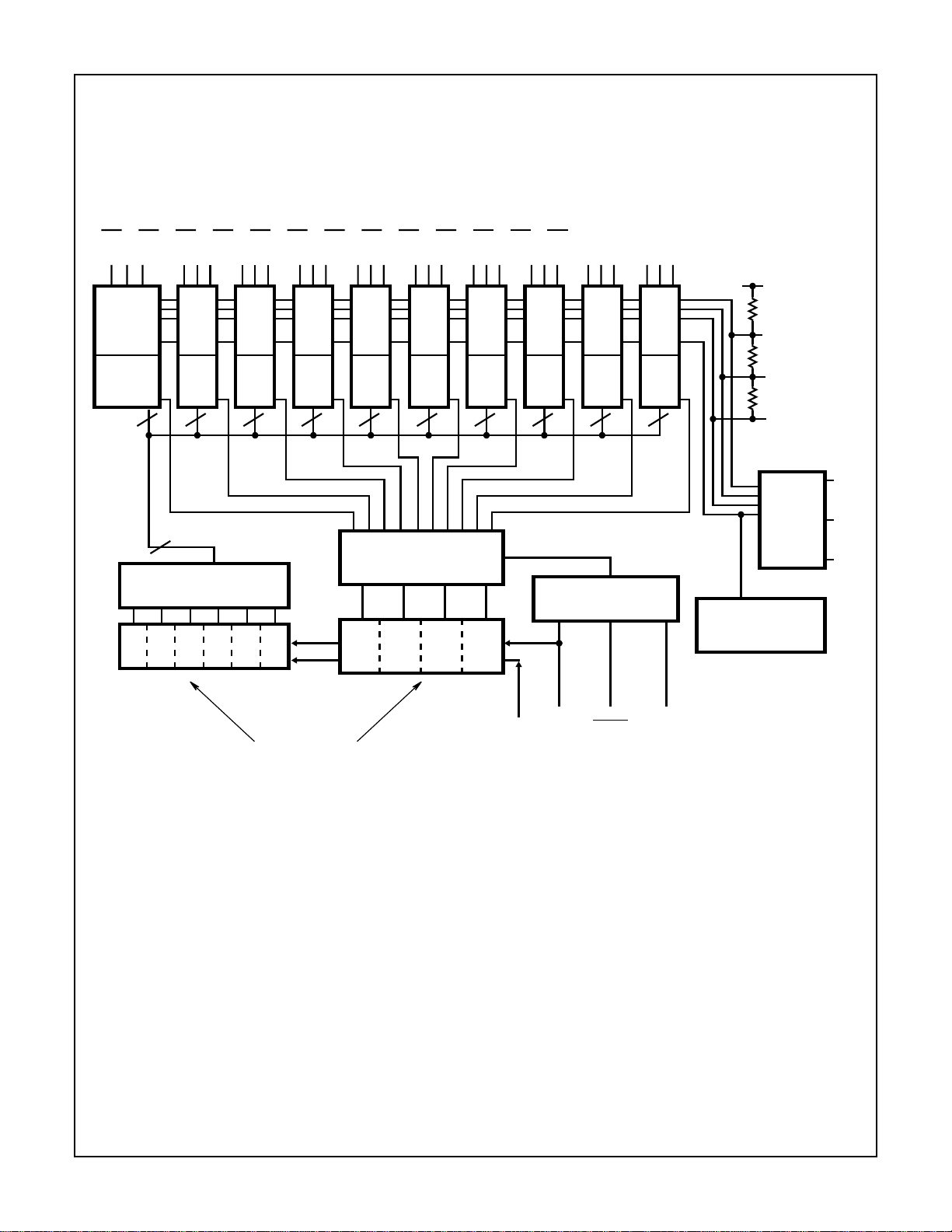

ICM7231, ICM7232

Functional Block Diagrams

(Continued)

ICM7232

9

9

D9 D8

f2, e2, an22

a2, g2, d2

9 9 9 9 9 9 9 9 9

DAT A

DECODER

DIGIT

ADDRESS

DECODER

A2A1A0 A3

EN

SERIAL INPUT

CONTOL LOGIC

CLOCK

DAT A

D10 D7 D6 D5 D4 D3 D2 D1

SEGMENT

LINE

DRIVERS

3 WIDE

OUTPUT

LATCHES

9 WIDE

AN1 BD0 BD2AN2 BD1 BD3

b2, c2, an12

f1, e1, an21

a1, g1, d1

b1, c1, an11

V

DD

ON CHIP

DISPLAY

V

H

VOLTAGE

LEVEL

GENERATOR

V

L

V

DISP

PIN 2 (INPUT)

BP1

COMMON

LINE

DRIVERS

DISPLAY

TIMING

GENERATOR

BP2

BP3

SHIFT REGISTER

SHIFTS RIGHT TO LEFT

ON RISING EDGE OF DATA CLOCK

NOTE: See Figures 13 and 14 for display segment connections.

DAT A

DAT A

INPUT

CLOCK

INPUT OUTPUT

WRITE

INPUT

DAT A

ACCEPTED

9-22

ICM7231, ICM7232

Absolute Maximum Ratings Thermal Information

Supply Voltage (VDD - VSS). . . . . . . . . . . . . . . . . . . . . . . . . . . .6.5V

Input Voltage (Note 1). . . . . . . . . . . . . . . . . . . .VSS - 0.3 ≤ VIN≤ 6.5

Display Voltage (Note 1). . . . . . . . . . . . . . . . . . . .0.3 ≤ V

DISP

≤ +0.3

Operating Conditions

Temperature Range . . . . . . . . . . . . . . . . . . . . . . . . . . -25oC to 85oC

CAUTION: Stresses above those listed in “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress only rating and operation

of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

NOTES:

1. Due to the SCR structure inherent in these devices, connecting any displa y terminal or the displa y voltage terminal to a voltage outside

the power supply to the chip may cause destructive device latchup. The digital inputs should never be connected to a voltage less than

-0.3V below ground, but maybe connected to voltages above VDD but not more than 6.5V above VSS.

2. θJA is measured with the component mounted on an evaluation PC board in free air.

Thermal Resistance (Typical, Note 2) θJA (oC/W) θJC (oC/W)

PDIP Package. . . . . . . . . . . . . . . . . . . 60 N/A

CERDIP Package . . . . . . . . . . . . . . . . 50 12

Maximum Junction Temperature

Ceramic Package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .175oC

Plastic Package. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 150oC

Maximum Storage Temperature Range . . . . . . . . . .-65oC to 150oC

Maximum Lead Temperature (Soldering, 10s) . . . . . . . . . . . .300oC

Electrical Specifications V+ = 5V +10%, V

= 0V, TA = -25oC to 85oC, Unless Otherwise Specified

SS

PARAMETER TEST CONDITIONS MIN TYP MAX UNITS

Power Supply Voltage, V

Data Retention Supply Voltage, V

Logic Supply Current, I

Shutdown Total Current, I

Display Voltage Range, V

Display Voltage Setup Current, I

Display Voltage Setup Resistor Value, R

DD

DD

S

DISP

DD

DISP

Guaranteed Retention at 2V 2 1.6 - V

Current from VDDto Ground Excluding Display.

V

= 2V

DISP

V

Pin 2 Open - 1 10 µA

DISP

VSS ≤ V

V

DISP

One of Three Identical Resistors in String 40 75 - kΩ

DISP

≤ V

DISP

DD

= 2V, Current from VDDto V

On-Chip - 15 30 µA

DISP

DC Component of Display Signals (Sample Test Only) Display Frame Rate, f

Input Low Level, V

Input High Level, V

Input Leakage, I

Input Capacitance, C

Output Low Level, V

Output High Level, V

DISP

IL

IH

ILK

IN

OL

OH

Operating Temperature Range, T

AC Specifications V

DD

OP

= 5V +10% VSS = 0V, -25oC to 85oC

See Figure 5 60 90 120 Hz

ICM7231, Pins 30 - 35, 37 - 39, 1

ICM7232, Pins 1, 38, 39 (Note 2)

Pin 37, ICM7232, IOL = 1mA - - 0.4 V

VDD = 4.5V, IOH = -500µA 4.1 - - V

Industrial Range -25 - +85

PARAMETER TEST CONDITIONS MIN TYP MAX UNITS

PARALLEL INPUT (ICM7231) See Figure 1

Chip Select Pulse Width, t

Address/Data Setup Time, t

Address/Data Hold Time, t

Inter-Chip Select Time, t

ICS

CS

DS

DH

(Note 1) 500 350 - ns

(Note 1) 200 - - ns

(Note 1) 0 -20 - ns

(Note 1) 3 - - µs

SERIAL INPUT (ICM7232) See Figures 2, 3

Data Clock Low Time, t

Data Clock High Time, t

Data Setup Time, t

Data Hold Time, t

Write Pulse Width, t

CL

CL

DS

DH

WP

Write Pulse to Clock at Initialization, t

Data Accepted Low Output Delay, t

Data Accepted High Output Delay, t

Write Delay After Last Clock, t

CWS

WLL

ODL

ODH

(Note 1) 350 - - ns

(Note 1) 350 - - ns

(Note 1) 200 - - ns

(Note 1) 0 -20 - ns

(Note 1) 500 350 - ns

(Note 1) 1.5 - - µs

(Note 1) - 200 400 ns

(Note 1) - 1.5 3 µs

(Note 1) 350 - - ns

4.5 >4 5.5 V

- 30 100 µA

0-VDDV

1

/

1% (VDD - V

4

DISP

- - 0.8 V

2.0 - - V

- 0.1 1 µA

-5- pF

o

C

)

9-23

Loading...

Loading...