HSP9501

Data Sheet January 1999 File Number

Programmable Data Buffer

The HSP9501 is a 10-Bit wide programmable data buffer

designed for use in high speed digital systems.Two different

modes of operation can be selected through the use of the

MODSEL input. In the delay mode, a programmable data

pipeline is created which can provide 2 to 1281 clock cycles

of delay between the input and output data. In the data

recirculate mode, the output data path is internally routed

back to the input to provide a programmable circular buffer.

The length of the buffer or amount of delay is programmed

through the use of the 11-bit LengthControl Input Port (LC0-

10) and the Length Control Enable (

is applied to the LC0-10 inputs,

next selected clock edge loads the new count value into the

Length Control Register. The delay path of the HSP9501

consists of two registers with a programmable delay RAM

between them, therefore, the value programmed into the

Length Control Register is the desired length - 2. The range

of values which can be programmed into the Length Control

Register are from 0 to 1279, which in turn results in an

overall range of programmable delays from 2 to 1281.

Clock select logicisprovided to allow theuseofapositive or

negative edge system clock as the CLK input to the

HSP9501. The active edge of the CLK input is controlled

through the use of the CLKSEL input. All synchronous timing

(i.e., data setup, hold, and output delays) are relative to the

clock edge selected by CLKSEL. An additional clock enable

input (

CLKEN) provides a means of disabling the internal

clock and holding the existing contents temporarily. All

outputs of the HSP9501 are three-state outputs to allow

direct interfacing to system or multi-use busses.

The HSP9501 is recommended for digital video processing

or any applications which require a programmable delay or

circular data buffer.

LCEN). An 11-bit value

LCEN is asserted, and the

2786.4

Features

• DC to 32MHz Operating Frequency

• Programmable Buffer Length from 2 to 1281 Words

• Supports Data Words to 10-Bits

• Clock Select Logic for Positive or Negative Edge

System Clocks

• Data Recirculate or Delay Modes of Operation

• Expandable Data Word Width or Buffer Length

• Three-State Outputs

• TTL Compatible Inputs/Outputs

• Low Power CMOS

Applications

• Sample Rate Conversion

• Data Time Compression/Expansion

• Software Controlled Data Alignment

• Programmable Serial Data Shifting

• Audio/Speech Data Processing Video/Image Processing

Video/Image Processing

• 1-H Delay Line of 910 NTSC, 1135 PAL or 1280 Samples:

- High Resolution Monitor Delay Line

- Comb Filter Designs

- Progressive Scanning Display

- TV Standards Conversion

- Image Processing

Ordering Information

TEMP.

PART NUMBER

HSP9501JC-25 0 to 70 44 Ld PLCC N44.65

HSP9501JC-32 0 to 70 44 Ld PLCC N44.65

HSP9501JC-2596 0 to 70 44 Ld PLCC

RANGE (oC) PACKAGE

Tape and Reel

PKG.

NO.

N44.65

191

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

http://www.intersil.com or 407-727-9207 | Copyright © Intersil Corporation 1999

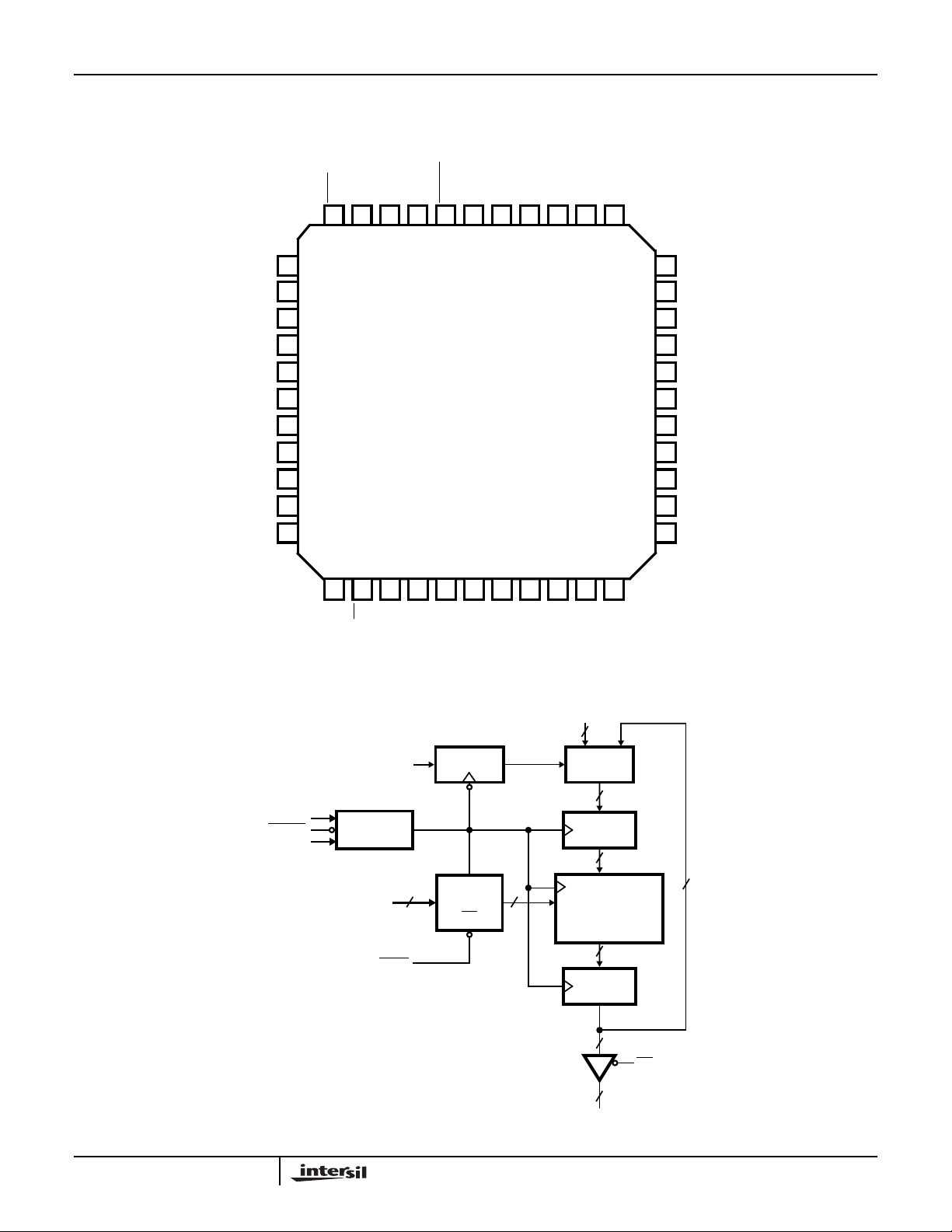

Pinout

HSP9501

44 LEAD PLCC

TOP VIEW

DO0

DO1

DO2

DO3

DO4

V

CC

GND

DO5

DO6

DO7

DO8

CLKSEL

LCEN

7

8

9

10

11

12

13

14

15

16

17

18 19 20 21 22 23 24 25 26 27 28

OE

DO9

NC

LC0

NC

LC1

CLK EN

LC10

CLK

LC9

LC2

LC8

LC3

LC7

LC4

LC6

LC5

DI9

MODSEL

4065 321444342414

NC

39

DI0

38

DI1

37

DI2

36

DI3

35

DI4

34

V

CC

33

GND

32

DI5

31

DI6

30

DI7

29

DI8

Block Diagram

CLKSEL

CLKEN

CLK

MODSEL

CLOCK

GENERATOR

LC0 -10

LCEN

11

REGISTER

REGISTER

EN

DI 0 -9

10

MUX

10

REGISTER

10

11

PROGRAMMABLE

DELAY RAM

0-1279 DELAYS

10

REGISTER

10

10

DO0-9

10

OE

192

HSP9501

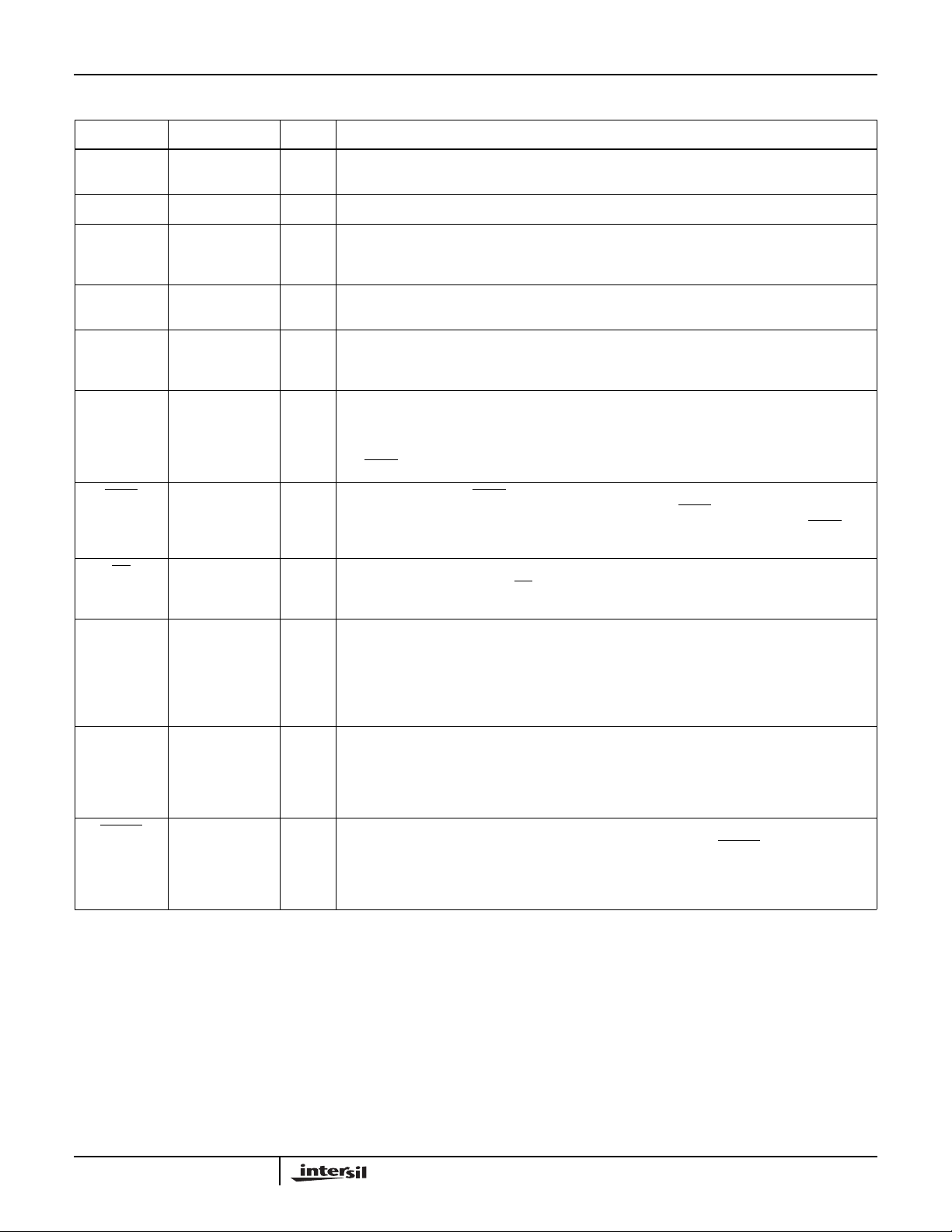

Pin Descriptions

NAME PIN NUMBER TYPE DESCRIPTION

V

CC

GND 13, 33 The device ground.

CLK 1 I Input Clock. This clock signal is used to control the datamovementthroughtheprogrammablebuff-

DIO-9 27, 29-32, 35-39 I Data Inputs. This 10-bit input port is used to provide the input data. When MODSEL is low, data

DO0-9 7-11, 14-18 O Data Outputs. This 10-bit port provides the output data from the Internal Delay Registers. Data

LC0-10 20-26, 41-44 I Length Control Inputs. These inputs are used to specify the number of clock cycles of delay be-

LCEN 6 I Length Control Enable. LCEN is used in conjunction with LC0-10 and CLK to load a new length

OE 19 I Output Enable. This input controls the state of the DO0-9 output port. A low on this control line en-

12, 34 The +5V power supply pin. A 0.1µF capacitor between the VCC and GND pin is

recommended.

er. It is also the signal which latches the input data, length control word and mode select. Input

setup and hold times with respect to the clock must be met for proper operation.

on the DI0-9 inputs is latched on the clock edge selected by CLKSEL.

latched into the DI0-9 inputs will appear at the DO0 9 outputs on the Nth clock cycle, where N is

the total delay programmed.

tween the DI0-9 inputs and the DO0-9 outputs. An integer value between 0 and 1279 is placed on

the LC0-10 inputs, and the total delay length (N) programmed is the LC0-10 value plus 2. In order

to properly load an active length control word, the value must be presented to the LC0-10 inputs

and LCEN must be asserted during an active clock edge selected by CLKSEL.

control word. An 11-bit value is loaded on the LC0-10 inputs, LCEN is asserted, and the next selected clock edge will load the new count value. Since this operation is synchronous, LCEN must

meet the specified setup/hold times with respect to CLK for proper operation.

ables the port for output. When OE is high, the output drivers are in the high impedance state. Internal latching or transfer of data is not affected by this input.

MODSEL 40 I Mode Select. This input is used to control the mode of operation of the HSP9501. A low on MOD-

SEL causes the device to latch new data at the DI0-9 inputs on every clock cycle, and operate as

a programmablepipeline register.When MODSEL is high, the HSP9501 is in the recirculate mode,

and will operate as a programmablelength circular buffer.This control signal may be used in a synchronous fashion during device operation, however,care must be taken to ensure the required setup/hold times with respect to CLK are met.

CLKSEL 5 I Clock Select Control. This input is used to determine which edge of the CLK signal is used for con-

trolling all internal events. A low on CLKSEL selects the negative going edge, therefore, all setup,

hold, and output delay times are with respect to the negative edge of CLK. When CLKSEL is high,

the positive going edge is selected and all synchronous timing is with respect to the positive edge

of the CLK signal.

CLKEN 2 I Clock Enable. This control signal can be used to enable or disable the CLK input. When low, the

CLK input is enabled and will operate in a normal fashion. A high on CLKEN will disable the CLK

input and will “hold'' all internal operations and data. This control signal may also be used in a synchronousfashion,however,setup and holdrequirements with respect to CLK must be met for proper device operation. This signal takes effect on the clock following the one that latches it in.

193

Loading...

Loading...