Intersil Corporation HS-82C08RH Datasheet

February 1996

HS-82C08RH

Radiation Hardened

8-Bit Bus Transceiver

Features

• Devices QML Qualified in Accordance With

MIL-PRF-38535

• Detailed Electrical and Screening Requirements are

Contained in SMD# 5962-95714 and Intersil’ QM Plan

• Radiation Hardened

5

- Total Dose 1 x 10

- Latch-Up Immune EPI-CMOS > 1 x 10

RAD (Si)

12

RAD (Si)/s

• Bidirectional Three-State Input/Outputs

• Low Propagation Delay Time

• Low Power Consumption

• Single Power Supply +5V

• Electrically Equivalent to Sandia SA2997

o

• Military Temperature Range -55

C to +125oC

Description

The Intersil HS-82C08RH is a radiation-hardened octal bus

transceiver with three-state outputs. It is manufactured using

a self-aligned, junction isolated CMOS process and is

designed for use with the HS-80C08RH radiation-hardened

microprocessor. The HS-82C08RH allows asynchronous

two-way communication between data buses. The direction

of data flow is determined by the logic level on the transmit/

receive (T/

data flow from Port A to Port B of the device. Conversely, a

logic low on the T/

Port A. The Output Enable input disables both ports by

placing them in the high impedance state.

The HS-82C08RH is ideally suited for a wide variety of

buffering applications in radiation-hardened microcomputer

systems.

R) input. A logic high on the T/R input specifies

R input specifies data flow from Port B to

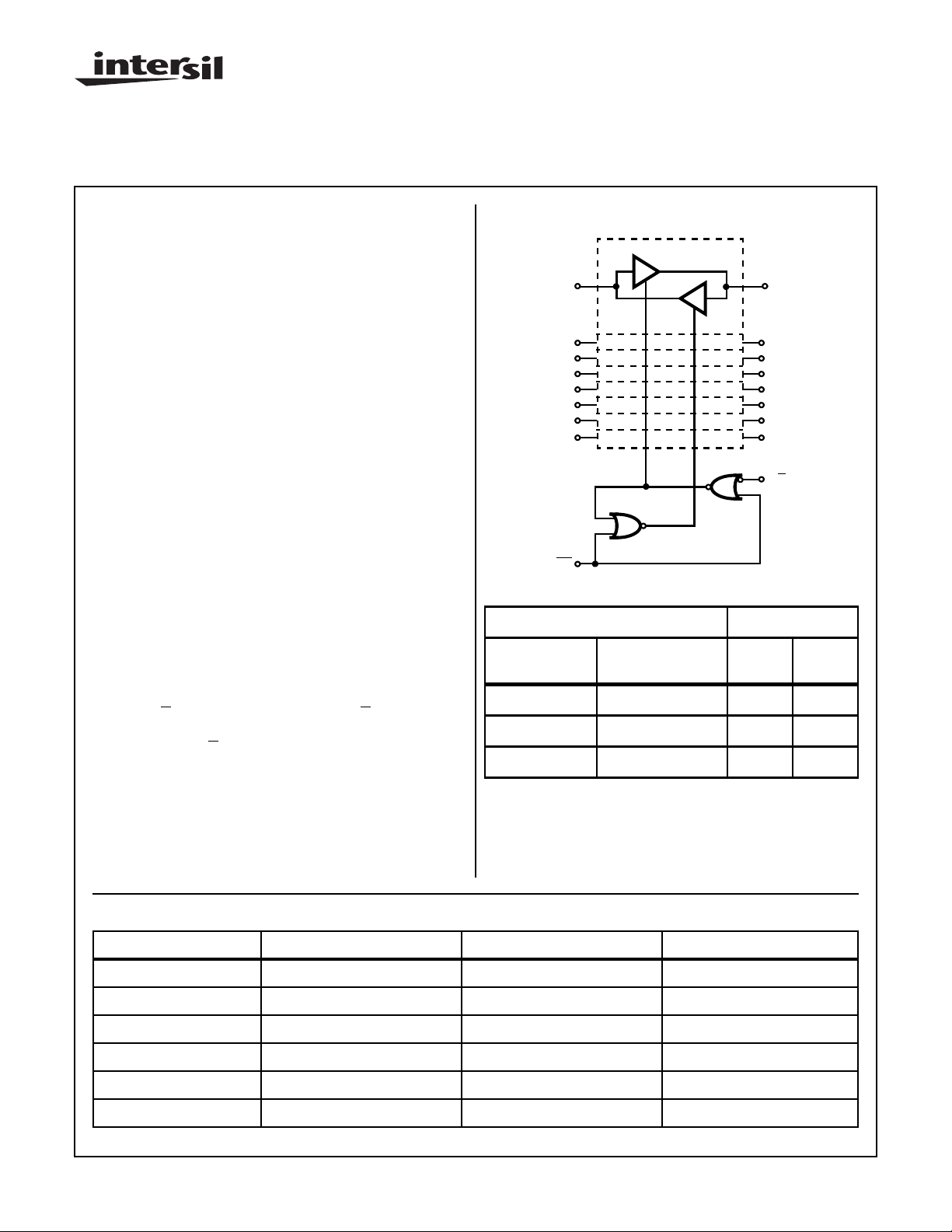

Functional Diagram

A0

A1

A2

A3

PORT

A4

A

A5

A6

A7

OE

TRUTH TABLE

INPUTS OPERATION

OUTPUT

ENABLE

0 0 Out In

0 1 In Out

1 X High Z High Z

X = Don’t Care

TRANSMIT

/RECEIVE PORT A PORT B

B1

B2

B3

B4

B5

B6

B7

T/

B0

R

PORT

B

Ordering Information

PART NUMBER TEMPERATURE RANGE SCREENING LEVEL PACKAGE

5962R9571401QRC -55oC to +125oC MIL-PRF-38535 Level Q 20 Lead SBDIP

5962R9571401QXC -55oC to +125oC MIL-PRF-38535 Level Q 20 Lead Ceramic Flatpack

5962R9571401VRC -55oC to +125oC MIL-PRF-38535 Level V 20 Lead SBDIP

5962R9571401VXC -55oC to +125oC MIL-PRF-38535 Level V 20 Lead Ceramic Flatpack

HS1-82C08RH/SAMPLE +25oC SAMPLE 20 Lead SBDIP

HS9-82C08RH/SAMPLE +25oC SAMPLE 20 Lead Ceramic Flatpack

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

http://www.intersil.com or 407-727-9207

| Copyright © Intersil Corporation 1999

1

Spec Number

File Number 3040.2

518057

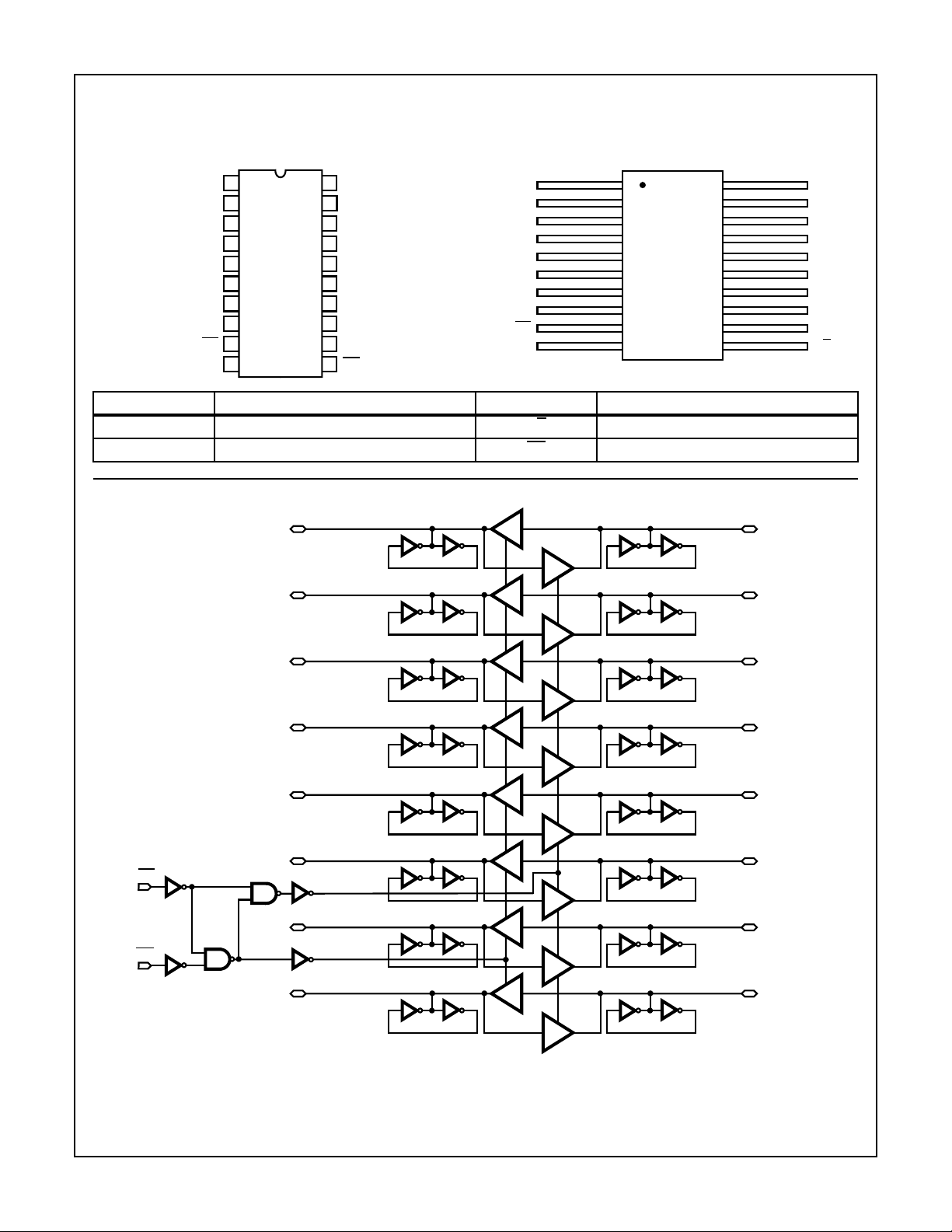

Pinouts

20 LEAD CERAMIC DUAL-IN-LINE

METAL-SEAL PACKAGE (SBDIP) MIL-STD-1835, CDIP2-T20

TOP VIEW

HS-82C08RH

20 LEAD CERAMIC METAL SEAL

FLATPACK PACKAGE (FLATPACK) MIL-STD-1835, CDFP4-F20

TOP VIEW

A0

A1

A2

A3

A4

A5

A6

A7

OE

GND

1

2

3

4

5

6

7

8

9

10

VDD

20

B0

19

B1

18

B2

17

B3

16

B4

15

B5

14

B6

13

12

B7

11

T/R

A0

A1

A2

A3

A4

A5

A6

A7

OE

GND

120

2

3

4

5

6

7

8

9

10

PIN DESCRIPTION PIN DESCRIPTION

A0-A7 Local Bus Data I/O Pins T/

R Transmit/Receive Input

B0-B7 System Bus Data I/O Pins OE Active Low Output Enable

Logic Diagram

A0

A1

1

2

TSB

TSB

TSB

TSB

VDD

19

18

17

16

15

14

13

12

11

19

B0

18

B1

B0

B1

B2

B3

B4

B5

B6

B7

T/

R

TSB

TSB

TSB

TSB

TSB

TSB

TSB

TSB

TSB

TSB

TSB

TSB

17

B2

16

B3

15

B4

14

B5

13

B6

12

B7

OE

T/R

3

A2

4

A3

5

A4

6

A5

9

11

A6

A7

B ENABLE

7

A ENABLE

8

NOTE: An Important caveat that is applicable to CMOS devices in general is that unused inputs should never be left floating. This rule applies

to inputs connected to a three-state bus. The need for external pull-up resistors during three-state bus conditions is eliminated by the

presence of regenerative latches on the following HS-82C08RH pins. A0-7 and B0-7 The functional block diagram depicts one of

these pins with the regenerative latch. When the CMOS driver assumes the high impedance state, the latch holds the bus in whatever

logic state (high or low) it was before the three-state condition. A transient drive current of ±1.5mA at VDD/2 ±0.5V for 10ns is required

to switch the latch. Thus, CMOS device inputs connected to the bus are not allowed to float during three-state conditions.

Spec Number 518057

2

Loading...

Loading...