Intersil Corporation HS-6664RH-T Datasheet

1

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

www.intersil.com or 407-727-9207

| Copyright © Intersil Corporation 1999

Satellite Applications Flow™ (SAF) is a trademark of Intersil Corporation.

HS-6664RH-T

Radiation Hardened 8K x 8 CMOS PROM

Intersil’sSatellite Applications FlowTM(SAF) devices are fully

tested and guaranteed to 100kRAD total dose. These QML

Class T devices are processed to a standard flow intended

to meet the cost and shorter lead-time needs of large

volume satellite manufacturers, while maintaining a high

level of reliability.

The Intersil HS-6664RH-T is a radiation hardened 64K

CMOS PROM, organized in an 8K word by 8-bit format. The

chip is manufactured using a radiation hardened CMOS

process, and utilizes synchronous circuit design techniques

to achieve high speed performance with very low power

dissipation.

On-chip address latches are provided, allowing easy

interfacing with microprocessors that use a multiplexed

address/data bus structure. The output enable control (

G)

simplifies system interfacing by allowing output data bus

control in addition to the chip enable control (

E). All bits are

manufactured storing a logical “0” and can be selectively

programmed for a logical “1” at any bit location.

Specifications

Specifications for Rad Hard QML devices are controlled by

the Defense Supply Center in Columbus (DSCC). The SMD

numbers listed below must be used when ordering.

Detailed Electrical Specifications for the HS-666s4RH-T

are contained in SMD 5962-95626. A “hot-link” is provided

from our website for downloading.

www.intersil.com/spacedefense/ne wsafc lasst.asp

Intersil’s Quality Management Plan (QM Plan), listing all

Class T screening operations, is also available on our

website.

www.intersil.com/quality/manuals.asp

Features

• QML Class T, Per MIL-PRF-38535

• Radiation Performance

- Gamma Dose (γ) 1 x 10

5

RAD(Si)

- No Latch-Up, SEU LET >100MeV/mg/cm

2

• Transient Output Upset >5 x 108 RAD (Si)/s

• Fast Access Time - 35ns (Typical)

• Single 5V Power Supply, Synchronous Operation

• Single Pulse 10V Field Programmable NiCr Fuses

• On-Chip Address Latches, Three-State Outputs

• Low Standby Current <500µA (Pre-Rad)

• Low Operating Current <15mA/MHz

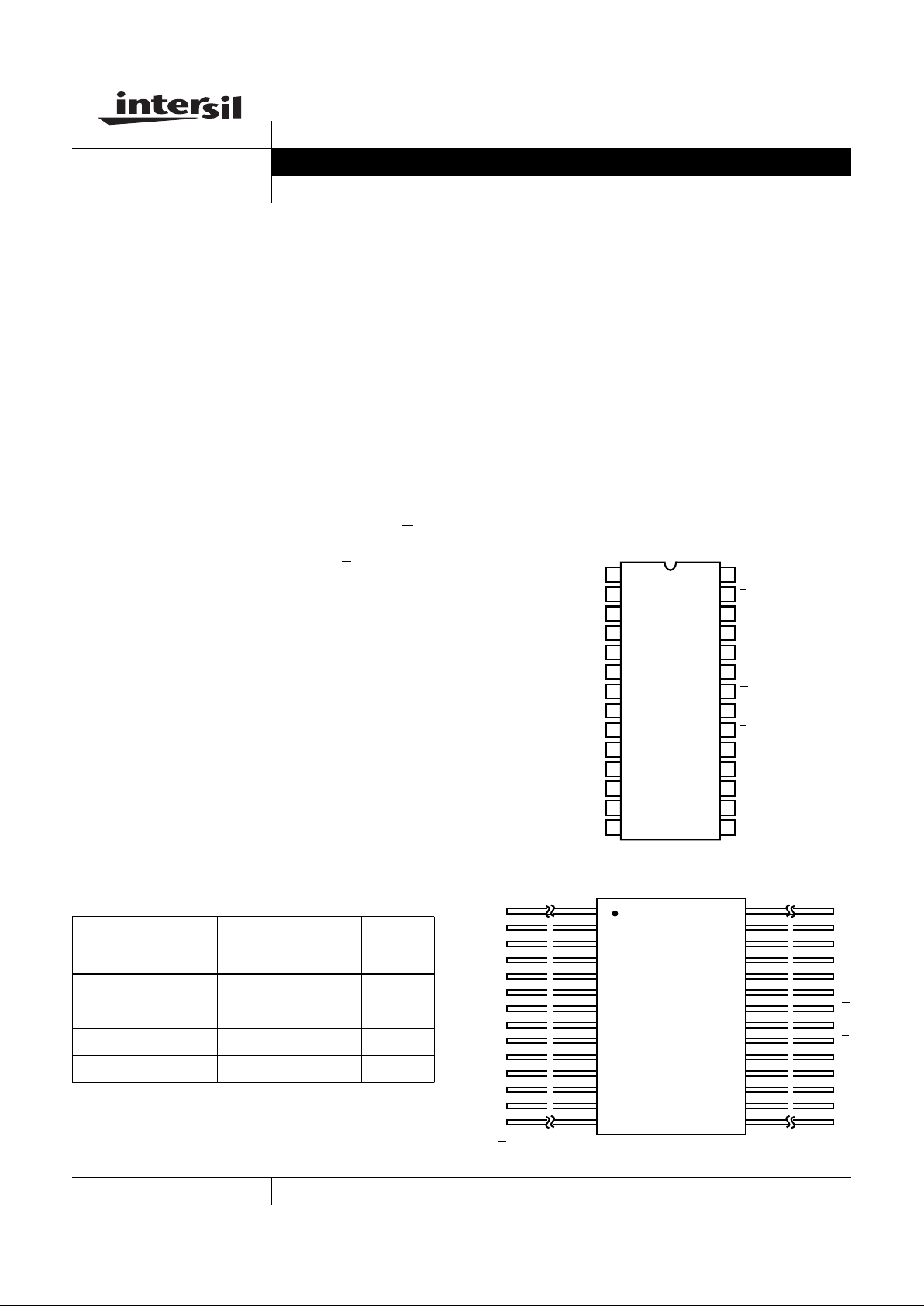

Pinouts

HS1-6664RH-T (SBDIP), CDIP2-T28

TOP VIEW

HS9-6664RH-T (FLATPACK), CDFP3-F28

TOP VIEW

Ordering Information

ORDERING

INFORMATION

PART

NUMBER

TEMP.

RANGE

(oC)

5962R9562601TXC HS1-6664RH-T -55 to 125

HS1-6664RH/Proto HS1-6664RH/Proto -55 to 125

5962R9562601TYC HS9-6664RH-T -55 to 125

HS9-6664RH/Proto HS9-6664RH/Proto -55 to 125

NOTE:

Minimumorderquantity for -T is 150 units through

distribution, or 450 units direct.

NC

A12

A7

A6

A5

A4

A3

A2

A1

A0

DQ0

DQ1

DQ2

GND

V

DD

NC

A8

A9

A11

A10

DQ7

DQ6

DQ5

DQ4

DQ3

P †

G

E

28

27

26

25

24

23

22

21

20

19

18

17

16

15

1

2

3

4

5

6

7

8

9

10

11

12

13

14

1

2

3

4

5

6

7

8

9

10

11

12

13

14

28

27

26

25

24

23

22

21

20

19

18

17

16

15

NC

A12

A7

A6

A5

A4

A3

A2

A1

A0

DQ0

DQ1

DQ2

GND

V

DD

NC

A8

A9

A11

A10

DQ7

DQ6

DQ5

DQ4

DQ3

P †

G

E

† P must be hardwired at all times to VDD, except during programming.

Data Sheet July 1999 File Number

4609.1

2

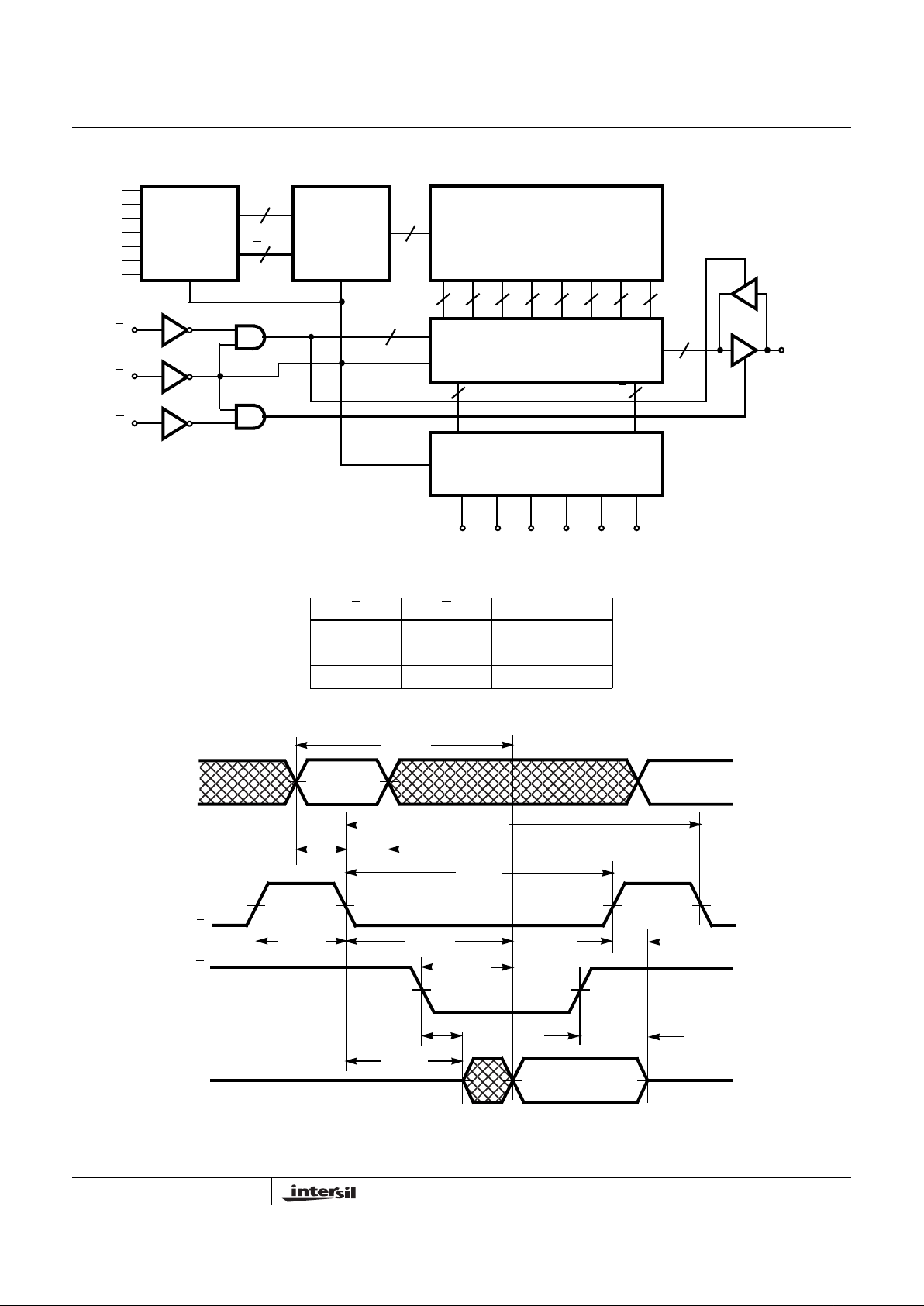

Functional Diagram

Timing Waveform

TRUTH TABLE

E G MODE

0 0 Enabled

0 1 Output Disabled

1 X Disabled

256 X 256

MATRIX

32 32 32 32 32 32 32 32

256

GATED ROW

DECODER

LATCHED

ADDRESS

REGISTER

8

MSB

A2

A3

A4

A5

A6

A7

A8

LSB

GATED COLUMN DECODER

PROGRAMMING, AND DATA

OUTPUT CONTROL

A

A

8

EE

8

LATCHED ADDRESS

REGISTER

E

E

A

5

A

5

8

1 OF 8

A0 A10 A9 A11 A12

MSB LSB

† P

E

G

Q0 - Q7

A1

† P must be hardwired at all times to VDD,

except during programming.

VALID

DAT A

TELQX

TGLQX

1.5V 1.5V

TGHQZ

TGLQV

1.5V1.5V

TEHQZ

1.5V

1.5V

TELEH

TEHEL

TELQV

TELAX

TAVEL

TELEL

VALID

ADDRESS

1.5V 1.5V

TAVQV

VALID

ADDRESSES

TS

3.0V

0V

0V

3.0V

0V

3.0V

ADDRESSES

DAT A

OUTPUT

G

E

Q0 - Q7

FIGURE 1. READ CYCLE

HS-6664RH-T

Loading...

Loading...