Intersil Corporation HS-3182 Datasheet

HS-3182

March 1997

Features

• TTL and CMOS Compatible Inputs

• Adjustable Rise and Fall Times via Two External

Capacitors

• Programmable Output Differential Voltage via V

Input

• Operates at Data Rates Up to 100 Kilobits/Sec

• Output Short Circuit Proof and Contains Over-Voltage

Protection

• Outputs are Inhibited (0 Volts) If DATA (A) and DATA

(B) Inputs are Both in the “Logic One” State

• DATA (A) and D A TA (B) Signals are “AND’d” with Cloc k

and Sync Signals

• Full Military Temperature Range

Ordering Information

TEMPERA TURE

PACKAGE

SBDIP -40oC to +85oC HS1-3182-9+ D16.3

SMD# -55oC to +125oC 5962-8687901EA D16.3

CLCC -55oC to +125oC HS4-3182-8 J28.A

SMD# -55oC to +125oC 5962-86879013A J28.A

RANGE PART NUMBER

-55oC to +125oC HS1-3182-8 D16.3

ARINC 429 Bus Interface Line Driver Circuit

Description

The HS-3182 is a monolithic dielectrically isolated bipolar differential line driver designed to meet the specifications of ARINC

429. This Device is intended to be used with a companion chip,

REF

PKG.

NO

HS-3282 CMOS ARINC Bus Interface Circuit, which provides

the data formatting and processor interface function.

All logic inputs are TTL and CMOS compatible. In addition to

the DATA (A) and DATA (B) inputs, there are also inputs for

CLOCK and SYNC signals which are AND’d with the DATA

inputs. This feature enhances system performance and allows

the HS-3182 to be used with devices other than the HS-3182.

Three power supplies are necessary to operate the

HS-3182: +V = +15V ± 10%, -V = -15V ± 10%, and V

± 5%. V

swing such that V

V

= 5V ± 5%, but a separate power supply may be used for

1

V

REF

is used to program the differential output voltage

REF

(DIFF) = ± 2V

OUT

. Typically, V

REF

which should not exceed 6V.

The driver output impedance is 75Ω± 20% at 25

= 5V

1

REF

o

C. Driver

output rise and fall times are independently programmed

through the use of two external capacitors connected to the

C

and CB inputs. Typical capacitor values are CA = CB =

A

75pF for high-speed operation (100KBPS), and C

= CB =

A

300pF for low-speed operation (12 to 14.5KBPS). The outputs are protected against over-voltage and short circuit as

shown in the Block Diagram. The HS-3182 is designed to

operate with a case temperature range of -55

o

or 0

C to +70oC.

o

C to +125oC,

=

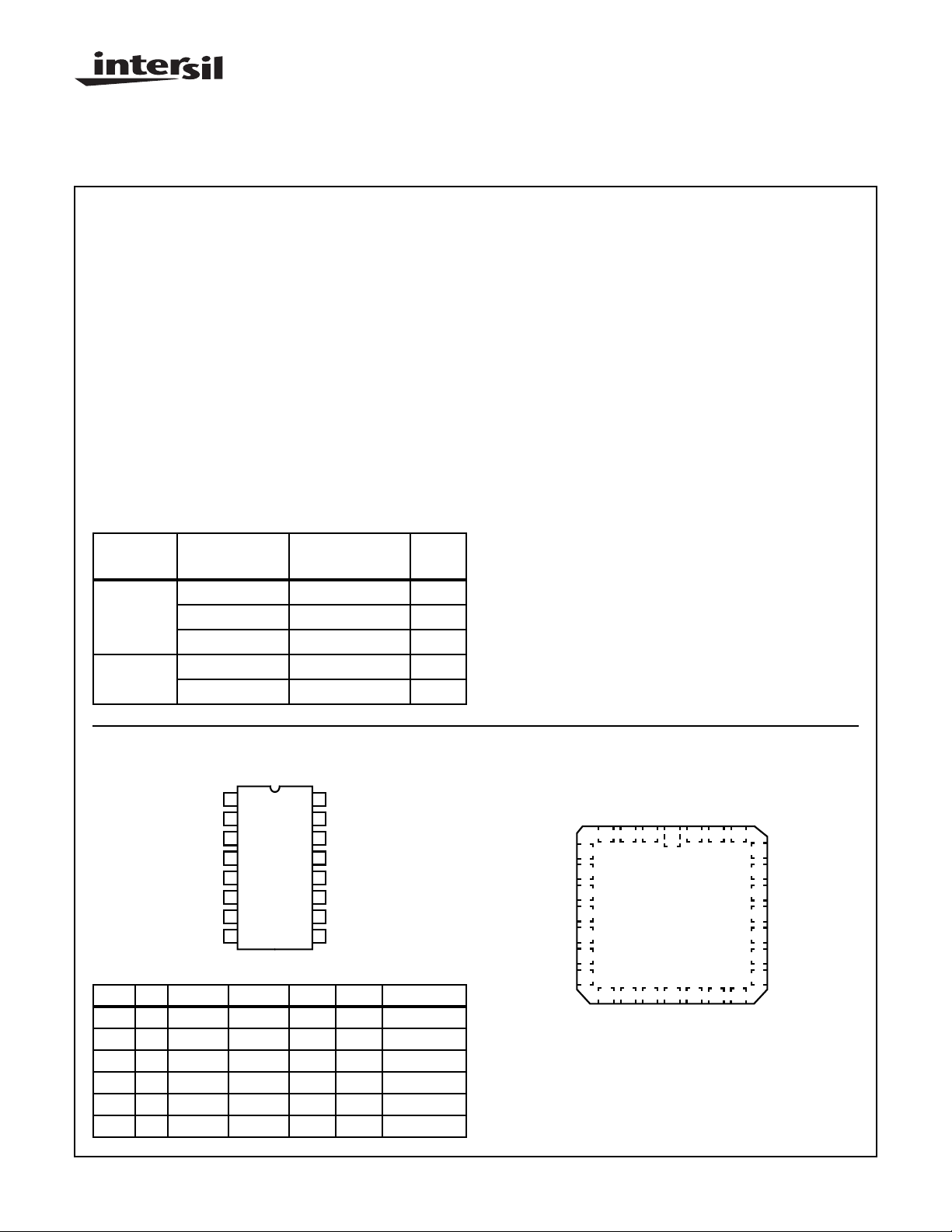

Pinouts

DATA (A)

SYNC CLK DATA (A) DATA (B) A

X L X X 0V 0V Null

L X X X 0V 0V Null

H H L L 0V 0V Null

HH L H -V

HH H L +V

H H H H 0V 0V Null

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

http://www.intersil.com or 407-727-9207

HS-3182 (SBDIP)

1

V

REF

2

GND

3

SYNC

4

5

C

A

6

A

OUT

-V

7

8

GND

TOP VIEW

V

16

1

15

NC

14

CLK

13

DATA (B)

12

C

B

11

B

OUT

10

NC

9

+V

TRUTH TABLE

OUTBOUT

REF+VREF

REF-VREF

| Copyright © Intersil Corporation 1999

COMMENTS

Low

High

5-178

NC

DATA (A)

NC

NC

C

NC

NC

A

SYNC

5

6

7

8

9

10

11

NC

HS-3182 (CLCC)

TOP VIEW

REFV1

V

GND

NC

3 2 14

OUT

A

28 27 26

14 15 16 17 1812 13

-V

+V

GND

NC

NC

25

CLK

NC

24

DATA (B)

23

C

22

B

21

NC

20

NC

19

NC

NC

OUT

B

File Number 2963.1

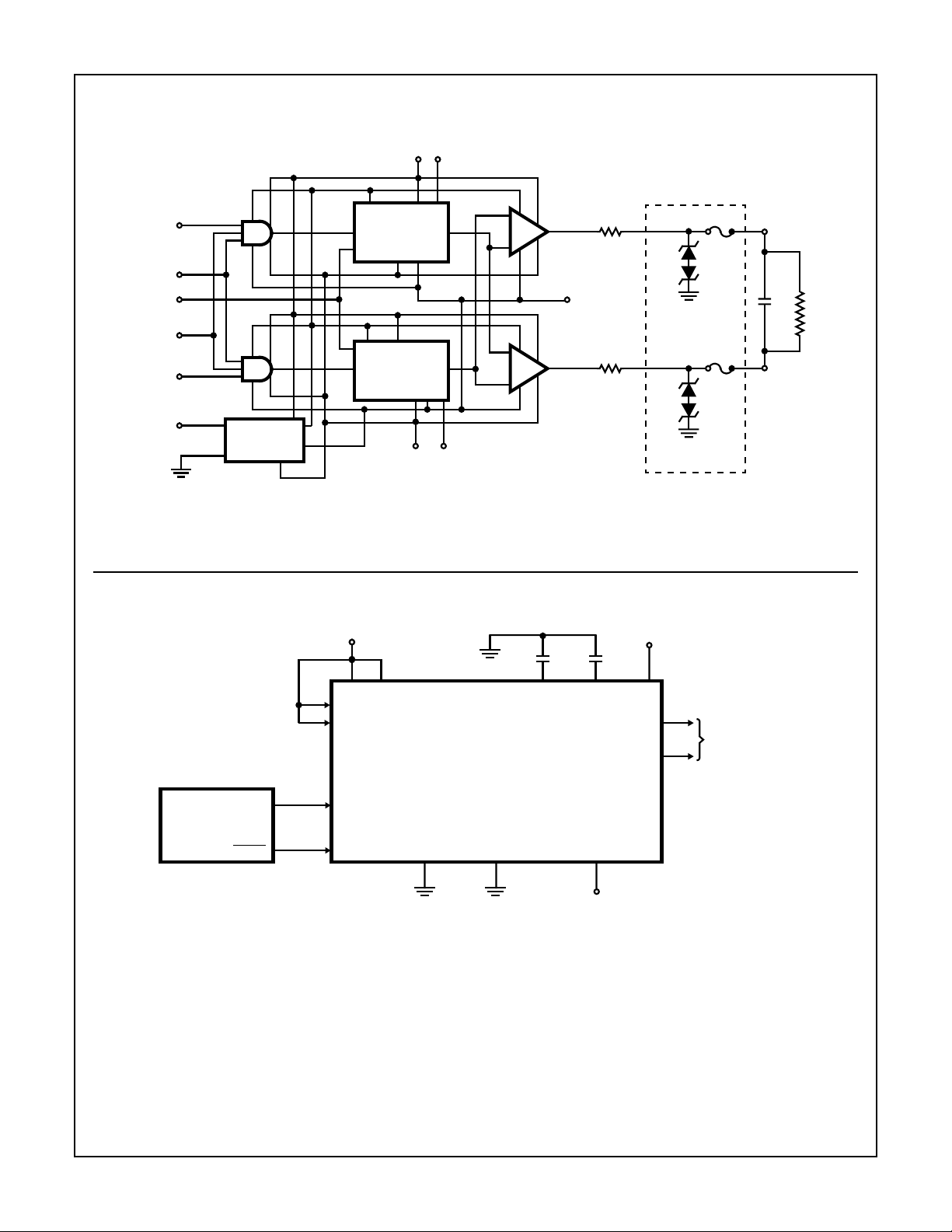

Block Diagram

V

REF

SYNC

V

(4)

(14)

(1)

(3)

(13)

(16)

1

(2)

DATA (A)

CLOCK

DATA (B)

CURRENT

REGULATOR

(9) (5)

+V C

LEVEL SHIFTER

AND SLOPE

CONTROL (A)

LEVEL SHIFTER

AND SLOPE

CONTROL (B)

-V C

(7) (12)

HS-3182

A

B

OUTPUT

DRIVER

(A)

(8)

OUTPUT

DRIVER

(B)

GND

R

OUT/2

R

OUT/2

OVER-VOLTAGE

PROTECTION

(6)

F

A

A

OUT

C

L

R

L

F

B

B

OUT

(11)

Typical Application

PIN NUMBERS INDICATED BY ( )

(14)

(3)

31

(4)

32

(13)

HS-3282

CMOS ARINC

CIRCUIT

429D0

429D0

+5V

(1)(16)

V

1VREF

CLOCK

SYNC

DATA (A)

DATA (B)

C

HS-3182

ARINC DRIVER

CIRCUIT

16 LEAD DIP

GNDGND -V

C

A

(12)(5)

C

A

-15V

NOTE: The rise and fall time of the outputs are set to ARINC specified values by CAand CB. Typical CA = CB = 75pF for high speed and

300pF for low speed operation. The output HI and low levels are set to ARINC specifications by V

(9)

+15V

C

B

+V

B

A

OUT

B

OUT

(7)(8)(2)

PIN NUMBER 10, 15 = NC

REF

.

TO BUS

(SEE

NOTE)

5-179

Loading...

Loading...