Intersil Corporation HMU16-883 Datasheet

HMU16/883

April 1997

Features

• This Circuit is Processed in Accordance to MIL-STD883 and is Fully Conformant Under the Provisions of

Paragraph 1.2.1.

• 16 x 16-Bit Parallel Multiplier with Full 32-Bit Product

• High-Speed (45ns) Clocked Multiply Time

• Low Power CMOS Operation

-I

-I

= 500µA Maximum

CCSB

= 7.0mA Maximum at 1MHz

CCOP

• HMU16/883 is Compatible with the AM29516, LMU16,

IDT7216, and the CY7C516

• Supports Two’s Complement, Unsigned Magnitude

and Mixed Mode Multiplication

• TTL Compatible Inputs/Outputs

• Three-State Outputs

Ordering Information

TEMP. RANGE

PART NUMBER

HMU16GM-45/883 -55 to 125 68 Ld CPGA N68.95

HMU16GM-60/883 -55 to 125 68 Ld CPGA N68.95

(oC) PACKAGE

PKG.

NO.

16 x 16-Bit CMOS Parallel Multiplier

Description

The HMU16/883 is a high speed, low power CMOS 16 x 16-bit

parallel multiplier ideal for fast, real time digital signal processing applications. The 16-bit X and Y operands may be

independently specified as either two’s complement or

unsigned magnitude format, thereby, allowing mixed mode

multiplication operations.

Additional inputs are provided to accommodate format

adjustment and rounding of the 32-bit product. The Format

Adjust control allows the user to select a 31-bit product with

the sign bit replicated in the LSP. The round control provides

for rounding the most significant portion of the result by adding one to the most significant bit of the LSP.

Two 16-bit Output Registers (MSP and LSP) are provided to

hold the most and least significant portions of the result,

respectively. These registers may be made transparent for

asynchronous operation through the use of the Feedthrough

Control (FT). The two halves of the product may be routed to

a single 16-bit three-state output port via the output multiplexer control, and in addition, the LSP is connected to the Yinput port through a separate three-state buffer.

The HMU16/883 utilizes independent clock signals (CLKX,

CLKY, CLKL, CLKM) to latch the input operands and output

Product Registers. This configuration maximizes throughput

and simplifies bus interfacing. All outputs of the HMU16/883

also offer three-state control for multiplexing onto multi-use

system busses.

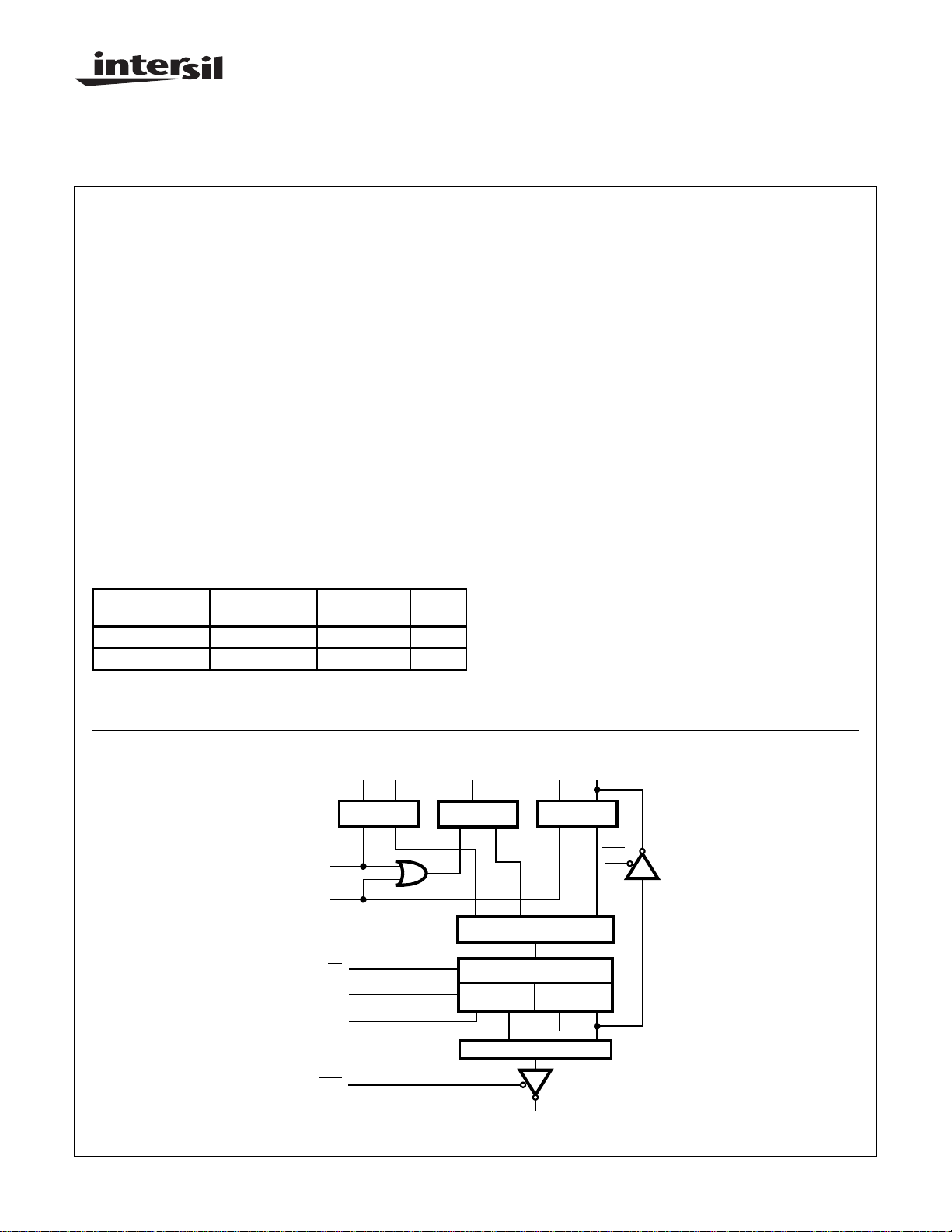

Functional Diagram

TCX RND

X0-15

REGISTER

CLKX

CLKY

FA

FT

CLKM

CLKL

MSPSEL

OEP

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

http://www.intersil.com or 407-727-9207

| Copyright © Intersil Corporation 1999

REGISTER

MULTIPLIER ARRAY

FORMAT ADJUST

MSP

REGISTER

MULTIPLEXER

3-29

TCY

REGISTER

REGISTER

P16-31/P0-15

Y0-15/P0-15

OEL

LSP

File Number 2804.2

HMU16/883

Absolute Maximum Ratings Thermal Information

Supply Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .+8.0V

Input or Output Voltage Applied . . . . . . . . GND -0.5V to VCC +0.5V

ESD Classification . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Class 1

Operating Conditions

Voltage Range . . . . . . . . . . . . . . . . . . . . . . . . . . . . . +4.5V to +5.5V

Temperature Range . . . . . . . . . . . . . . . . . . . . . . . . . -55oC to 125oC

CAUTION: Stresses above those listed in “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress only rating and operation

of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

NOTE:

1. θJA is measured with the component mounted on an evaluation PC board in free air.

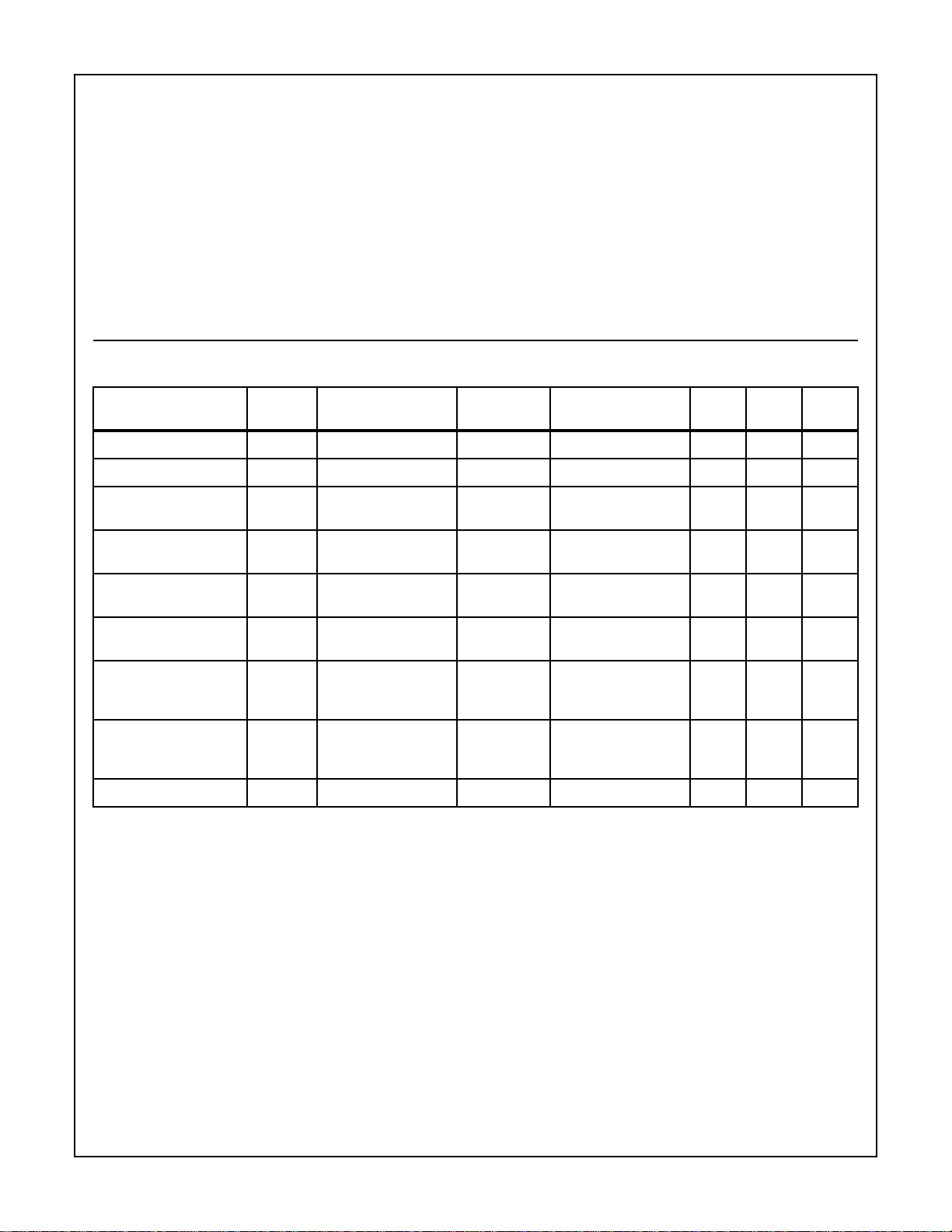

TABLE 1. HMU16/883 DC ELECTRICAL PERFORMANCE SPECIFICATIONS

Device Guaranteed and 100% Tested

Thermal Resistance (Typical, Note 1) θJA (oC/W) θJC (oC/W)

CPGA Package . . . . . . . . . . . . . . . . . . 42.69 10.0

Maximum Junction Temperature. . . . . . . . . . . . . . . . . . . . . . . . 175oC

Maximum Storage Temperature Range . . . . . . . . . .-65oC to 150oC

Maximum Lead Temperature (Soldering 10s) . . . . . . . . . . . . . 300oC

Die Characteristics

Gate Count . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4500 Gates

TEST

PARAMETER SYMBOL

Logical One Input Voltage V

Logical Zero Input Voltage V

Output HIGH Voltage V

Output LOW Voltage V

Input Leakage Current I

Output or I/O Leakage

Current

Standby Power Supply

Current

Operating Power Supply

Current

Functional Test FT (Note 4) 7, 8 -55 ≤ TA≤ 125 - -

NOTES:

2. Interchanging of force and sense conditions is permitted.

3. Operating supply current is proportional to frequency, typical rating is 5mA/MHz.

4. Tested as follows: f = 1MHz, VIH (clock inputs) = 3.0, VIH (all other inputs) = 2.6, VIL = 0.4, VOH≥ 1.5V, and VOL≤ 1.5V.

IH

IL

OHIOH

OL

I

I

O

I

CCSBVIN

I

CCOP

CONDITIONS

VCC = 5.5V 1, 2, 3 -55 ≤ TA≤ 125 2.2 - V

VCC = 4.5V 1, 2, 3 -55 ≤ TA≤ 125 - 0.8 V

= -400µA

VCC = 4.5V (Note 2)

IOL = +4.0mA

VCC = 4.5V (Note 2)

VIN = VCC or GND

VCC = 5.5V

V

= VCC or GND

OUT

VCC = 5.5V

= VCC or GND,

VCC = 5.5V,

Outputs Open

f = 1.0MHz,

VIN = VCC or GND

VCC = 5.5V (Note 3)

GROUP A

SUBGROUPS TEMPERATURE (oC) MIN MAX UNITS

1, 2, 3 -55 ≤ TA≤ 125 2.6 - V

1, 2, 3 -55 ≤ TA≤ 125 - 0.4 V

1, 2, 3 -55 ≤ TA≤ 125 -10 +10 mA

1, 2, 3 -55 ≤ TA≤ 125 -10 +10 mA

1, 2, 3 -55 ≤ TA≤ 125 - 500 mA

1, 2, 3 -55 ≤ TA≤ 125 - 7.0 mA

3-30

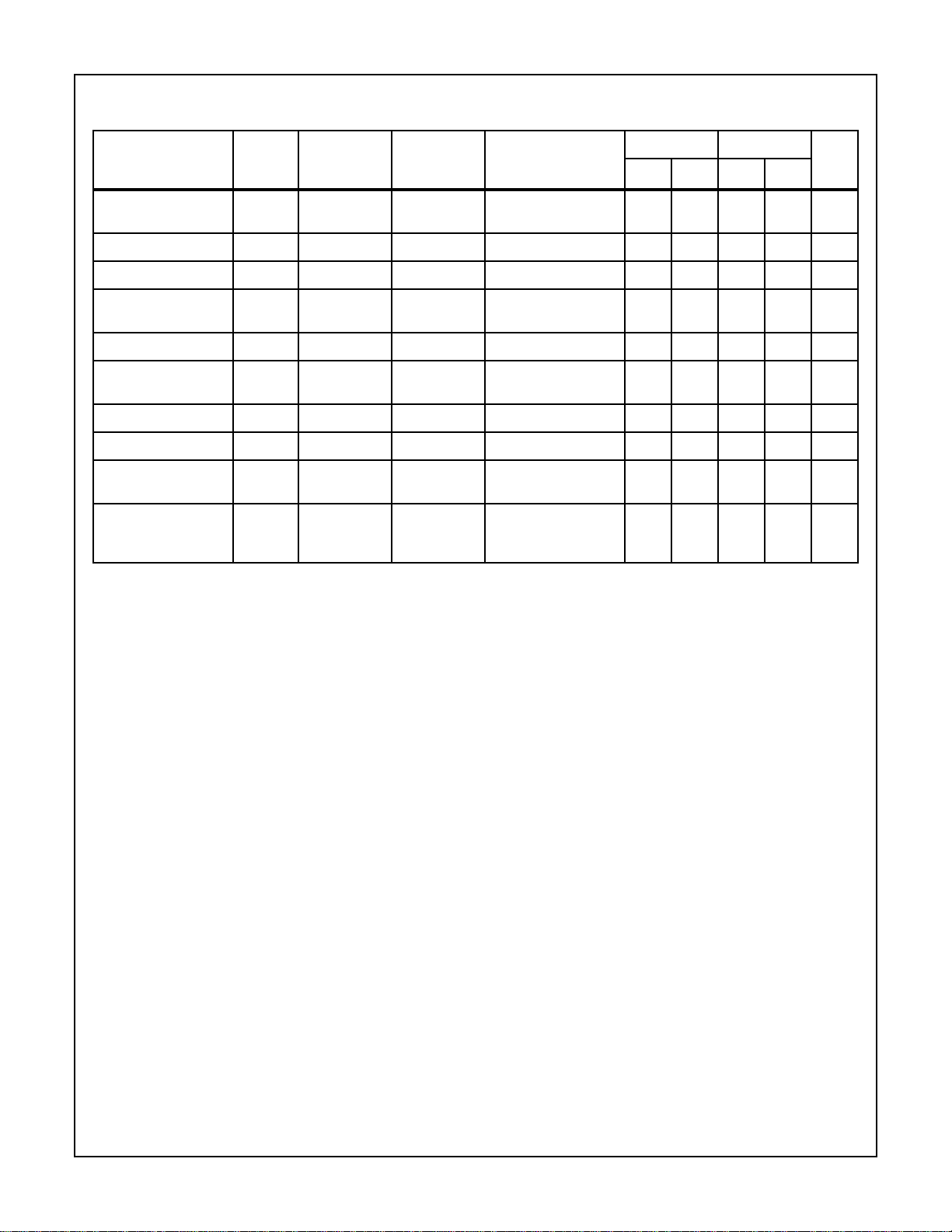

TABLE 2. HMU16/883 AC ELECTRICAL PERFORMANCE SPECIFICATIONS

Device Guaranteed and 100% Tested

HMU16/883

PARAMETER SYMBOL

Unclocked Multiply

t

MUC

(NOTE 5)

TEST

CONDITIONS

GROUP A

SUBGROUPS

TEMPERATURE

(oC)

9, 10, 11 -55 ≤ TA≤ 125 - 70 - 90 ns

-45 -60

UNITSMIN MAX MIN MAX

Time

Clocked Multiply Time t

X, Y, RND Setup Time t

Clock HIGH Pulse

MC

t

PWH

S

9, 10, 11 -55 ≤ TA≤ 125 - 45 - 60 ns

9, 10, 11 -55 ≤ TA≤ 125 18 - 20 - ns

9, 10, 11 -55 ≤ TA≤ 125 15 - 20 - ns

Width

Clock LOW Pulse Width t

MSPSEL to Product

PWL

t

PDSEL

9, 10, 11 -55 ≤ TA≤ 125 15 - 20 - ns

9, 10, 11 -55 ≤ TA≤ 125 - 25 - 30 ns

Out

Output Clock to P t

Output Clock to Y t

Three-State Enable

PDP

PDY

t

ENA

(Note 6) 9, 10, 11 -55 ≤ TA≤ 125 - 25 - 30 ns

9, 10, 11 -55 ≤ TA≤ 125 - 25 - 30 ns

9, 10, 11 -55 ≤ TA≤ 125 - 25 - 30 ns

Time

Clock Low Hold Time

t

HCL

(Note 7) 9, 10, 11 -55 ≤ TA≤ 125 0 - 0 - ns

CLKXY Relative to

CLKML

NOTES:

5. AC Testing as follows: VCC = 4.5V and 5.5V. Input levels 0V and 3.0V; timing reference levels = 1.5V; output load per test load circuit,

with V1 = 4V, R1 = 500Ω and CL = 40pF.

6. Transition is measured at ±200mV from steady state voltage; output loading per test load circuit with V1 = 1.5V, R1 = 500Ω and CL = 40pF.

7. To ensure the correct product is entered in the Output Registers; new data may not be entered into the Input Registers before the Output

Registers have been clocked.

3-31

Loading...

Loading...