Intersil Corporation HM-6561-883 Datasheet

HM-6561/883

March 1997

Features

• This Circuit is Processed in Accordance to MIL-STD883 and is Fully Conformant Under the Provisions of

Paragraph 1.2.1.

• Low Power Standby. . . . . . . . . . . . . . . . . . . . 50µW Max

• Low Power Operation . . . . . . . . . . . . . 20mW/MHz Max

• Fast Access Time. . . . . . . . . . . . . . . . . . . . . . 200ns Max

• Data Retention . . . . . . . . . . . . . . . . . . . . . . . .at 2.0V Min

• TTL Compatible Input/Output

• High Output Drive - 1 TTL Load

• On-Chip Address Registers

• Common Data In/Out

• Three-State Output

• Easy Microprocessor Interfacing

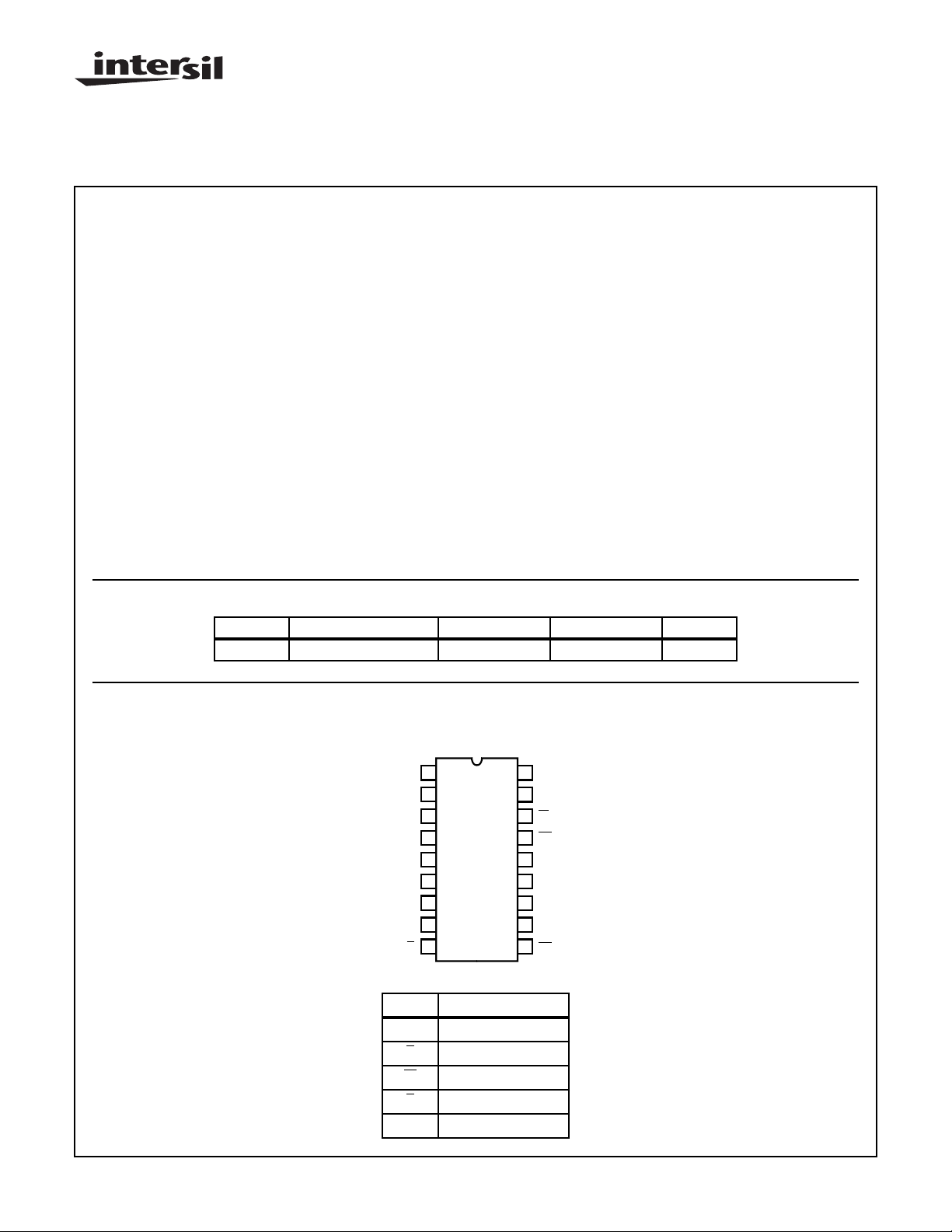

Ordering Information

256 x 4 CMOS RAM

Description

The HM-6561/883 is a 256 x 4 static CMOS RAM fabricated

using self-aligned silicon gate technology. Synchronous

circuit design techniques are employed to achieve high performance and low power operation.

On-chip latches are provided for address and data outputs

allowing efficient interfacing with microprocessor systems.

The data output buffers can be forced to a high impedance

state for use in expanded memory arrays. The data inputs

and outputs are multiplexed internally for common I/O bus

compatibility.

The HM-6561/883 is a fully static RAM and may be

maintained in any state for an indefinite period of time. Data

retention supply voltage and supply current are guaranteed

over temperature.

Pinout

PACKAGE TEMPERA TURE RANGE 220ns 300ns PKG. NO.

CERDIP -55oC to +125oC HM1-6561B/883 HM1-6561/883 F18.3

HM-6561/883 (CERDIP)

TOP VIEW

1

A3

2

A2

A1

3

4

A0

A5

5

A6

6

A7

7

GND

8

9

E

PIN DESCRIPTION

A Address Input

E Chip Enable

W Write Enable

S Chip Select

DQ Data In/Out

18

VCC

A4

17

16

W

15

S1

14

DQ3

13

DQ2

12

DQ1

DQ0

11

10

S2

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

http://www.intersil.com or 407-727-9207

| Copyright © Intersil Corporation 1999

6-117

File Number 2990.1

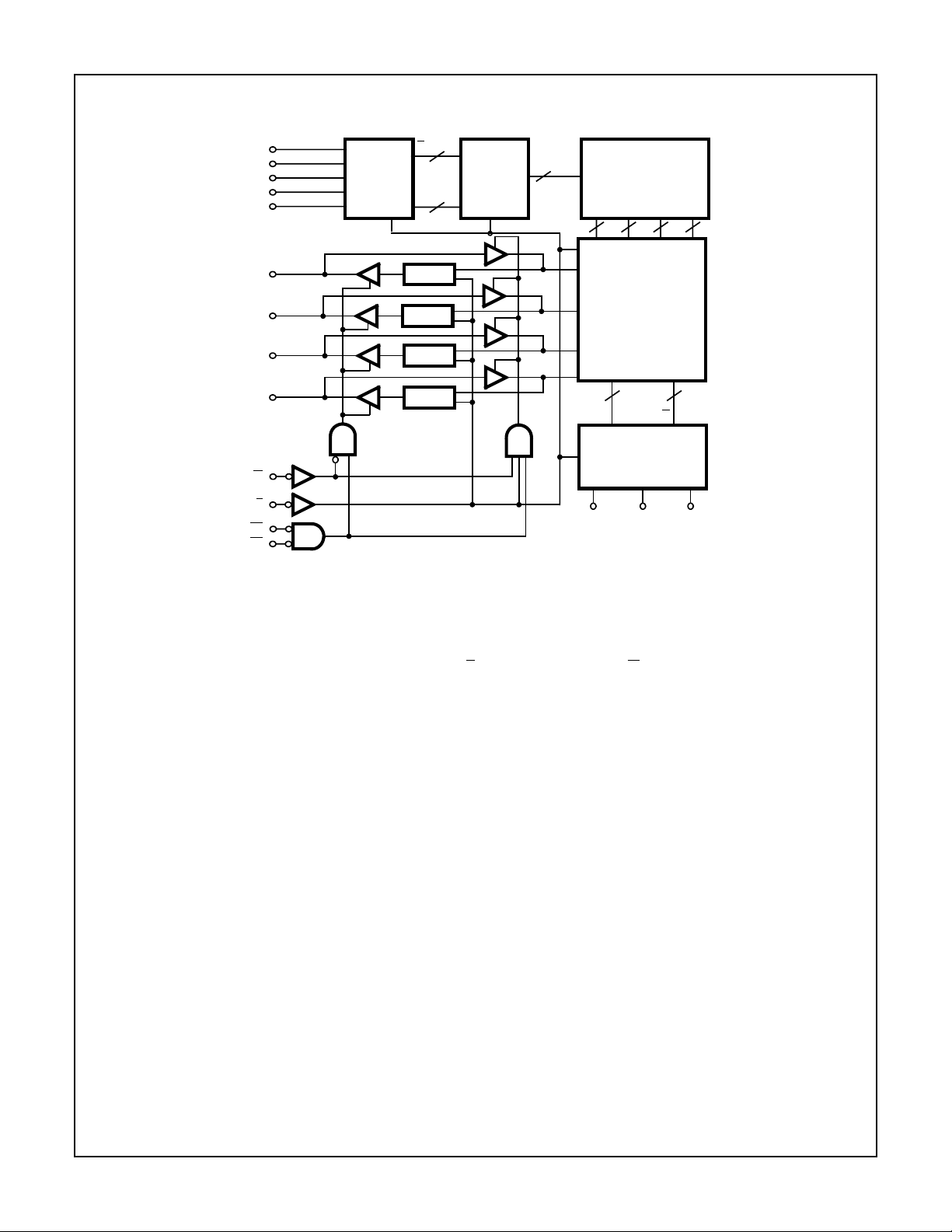

Functional Diagram

HM-6561/883

L

LATCH

LATCH

LATCH

LATCH

A

A

5

5

GATED

ROW

DECODER

D

L

D

L

D

L

D

L

32

G

A

A

A

A

G

GATED COLUMN

DECODER

AND DATA I / O

A A

L

LATCHED ADDRESS

REGISTER

A2

A0

A1

A5

A6

A7

DQ0

DQ1

DQ2

DQ3

S1

S2

LATCHED

ADDRESS

REGISTER

A Q

A Q

A Q

A Q

W

E

NOTES:

1. All lines positive logic-active high.

2. Three-state Buffers: A high → output active.

3. Data Latches: L high → Q = D and Q latches on falling edge of L.

4. Address Latches and Gated Decoders: Latch on falling edge of E and gate on falling edge of E.

32 x 32

MATRIX

8 888

33

A3

A4

6-118

HM-6561/883

Absolute Maximum Ratings Thermal Information

Supply Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .+7.0V

Input or Output Voltage. . . . . . . . . . . . . . . GND -0.3V to VCC +0.3V

ESD Classification . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Class 1

CAUTION: Stresses above those listed in “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress only rating and operation

of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

Operating Conditions

Operating Voltage Range. . . . . . . . . . . . . . . . . . . . . +4.5V to +5.5V

Operating Temperature Range. . . . . . . . . . . . . . . .-55oC to +125oC

Input Low Voltage. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0V to +0.8V

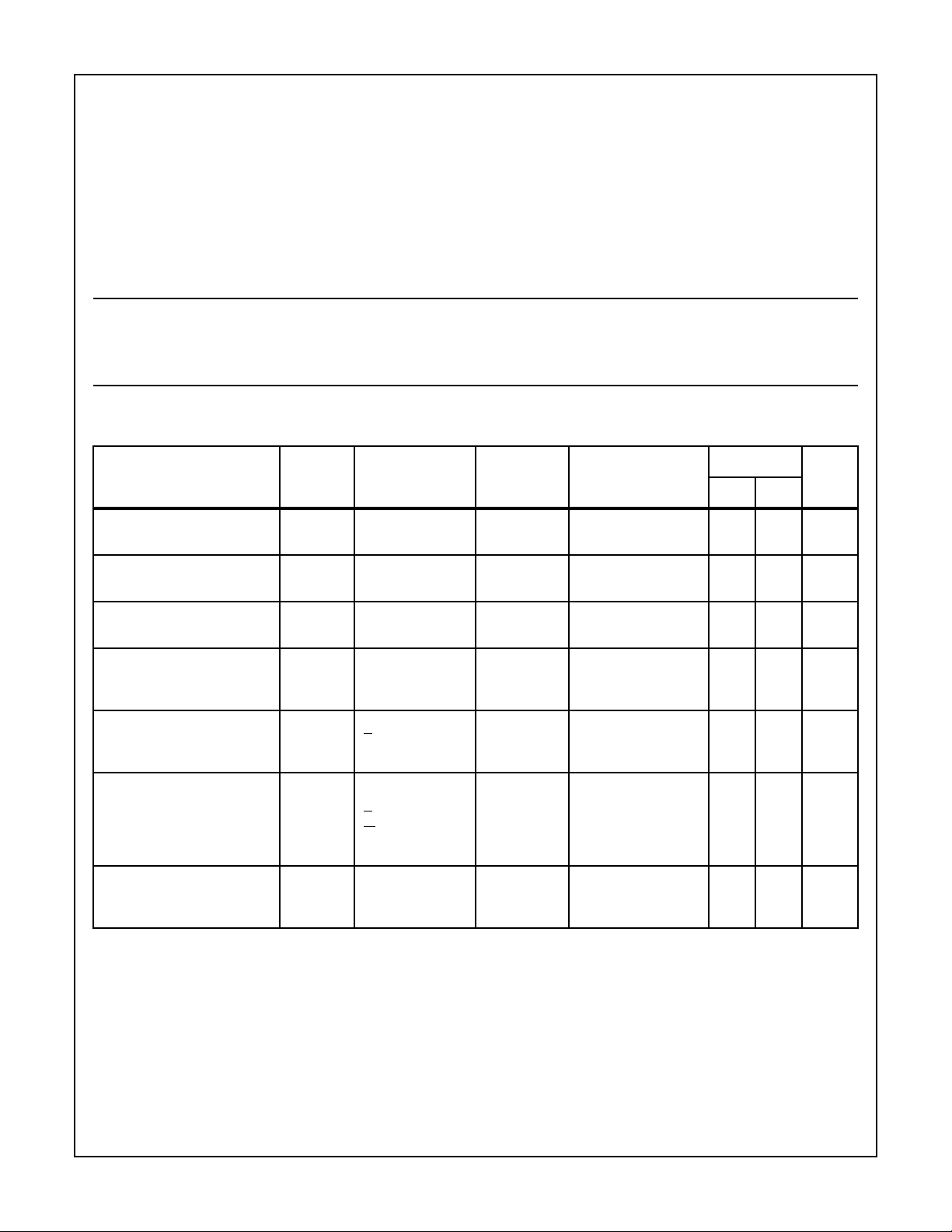

TABLE 1. HM-6561/883 DC ELECTRICAL PERFORMANCE SPECIFICATIONS

Device Guaranteed and 100% Tested

(NOTE 1)

PARAMETER SYMBOL

CONDITIONS

Thermal Resistance θ

CERDIP Package . . . . . . . . . . . . . . . . 74oC/W 18oC/W

Maximum Storage Temperature Range . . . . . . . . .-65oC to +150oC

Maximum Junction Temperature. . . . . . . . . . . . . . . . . . . . . .+175oC

Maximum Lead Temperature (Soldering 10s). . . . . . . . . . . .+300oC

JA

θ

JC

Die Characteristics

Gate Count . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1944 Gates

Input High Voltage. . . . . . . . . . . . . . . . . . . . . . . .VCC - 2.0V to VCC

Input Rise and Fall Time. . . . . . . . . . . . . . . . . . . . . . . . . . 40ns Max

LIMITS

GROUP A

SUBGROUPS TEMPERATURE

UNITSMIN MAX

Output Low Voltage VOL VCC = 4.5V,

IOL = 1.6mA

Output High Voltage VOH VCC = 4.5V,

IOH = -0.4mA

Input Leakage Current II VCC = 5.5V,

VI = GND or VCC

Input/Output Leakage Current IIOZ VCC = 5.5V,

VIO = GND or

VCC

Data Retention Supply Current ICCDR VCC = 2.0V,

E = VCC,

IO = 0mA,

Operating Supply Current ICCOP VCC = 5.5V,

(Note 2),

E = 1MHz,

W = GND,

VI = VCC or GND

Standby Supply Current ICCSB VCC = 5.5V,

IO = 0mA,

VI = VCC or GND

NOTES:

1. All voltages referenced to device GND.

2. Typical derating 1.5mA/MHz increase in ICCOP.

1, 2, 3 -55oC ≤ TA≤ +125oC - 0.4 V

1, 2, 3 -55oC ≤ TA≤ +125oC 2.4 - V

1, 2, 3 -55oC ≤ TA≤ +125oC -1.0 +1.0 µA

1, 2, 3 -55oC ≤ TA≤ +125oC -1.0 +1.0 µA

1, 2, 3 -55oC ≤ TA≤ +125oC- 10 µA

1, 2, 3 -55oC ≤ TA≤ +125oC- 4 mA

1, 2, 3 -55oC ≤ TA≤ +125oC- 10 µA

6-119

Loading...

Loading...