Intersil Corporation HM-6516-883 Datasheet

HM-6516/883

March 1997

Features

• This Circuit is Processed in Accordance to MIL-STD883 and is Fully Conformant Under the Provisions of

Paragraph 1.2.1.

• Low Power Standby. . . . . . . . . . . . . . . . . . . 275µW Max

• Low Power Operation . . . . . . . . . . . . . 55mW/MHz Max

• Fast Access Time. . . . . . . . . . . . . . . . . . 120/200ns Max

• Industry Standard Pinout

• Single Supply. . . . . . . . . . . . . . . . . . . . . . . . . . 5.0V VCC

• TTL Compatible

• Static Memory Cells

• High Output Drive

• On-Chip Address Latches

• Easy Microprocessor Interfacing

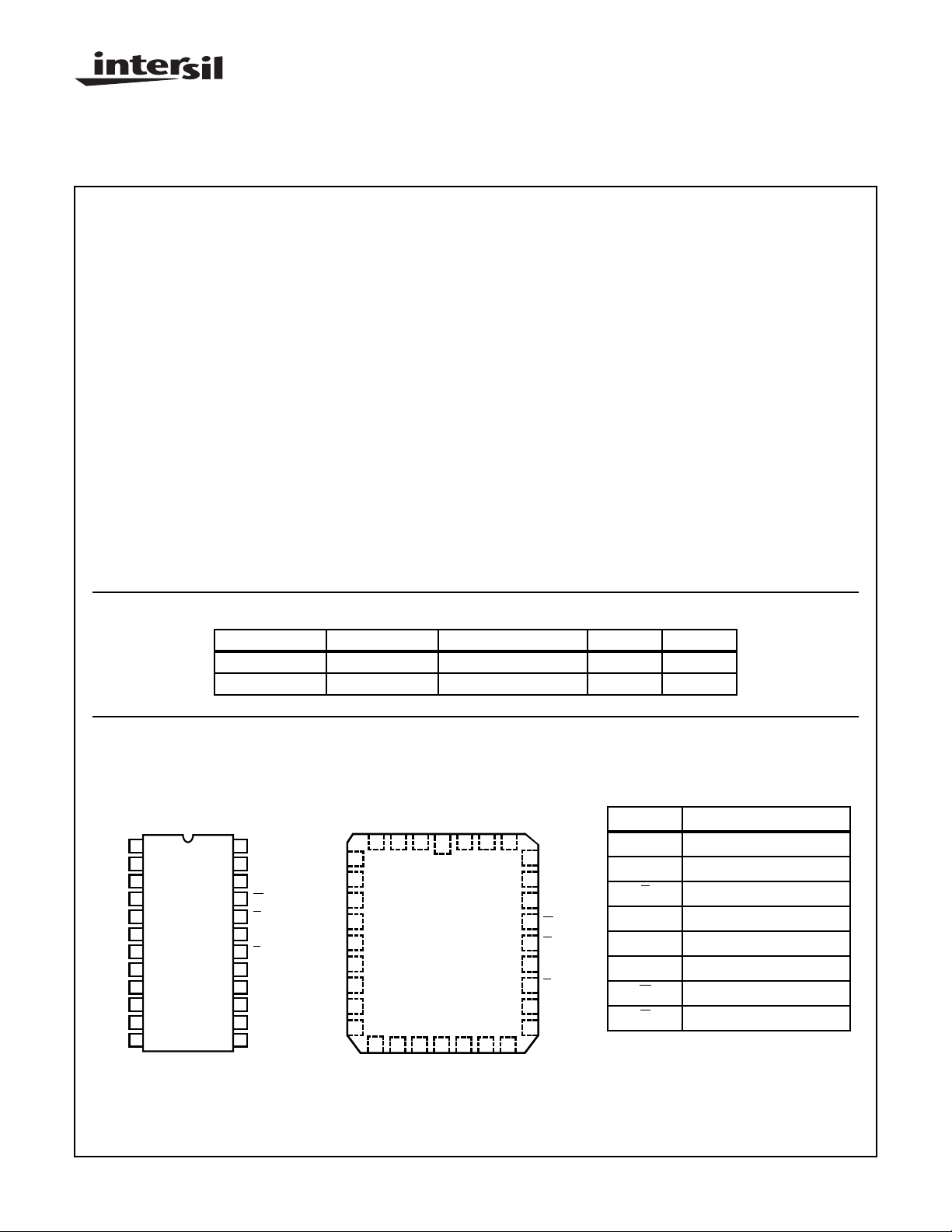

Ordering Information

2K x 8 CMOS RAM

Description

The HM-6516/883 is a CMOS 2048 x 8 Static Random

Access Memory. Extremely low power operation is achieved

by the use of complementary MOS design techniques. This

low power is further enhanced by the use of synchronous circuit techniques that keep the active (operating) power low,

which also gives fast access times. The pinout of the HM6516/883 is the popular 24 pin, 8-bit wide JEDEC Standard

which allows easy memory board layouts, flexible enough to

accommodate a variety of PROMs, RAMS, EPROMs, and

ROMs.

The HM-6516/883 is ideally suited for use in microprocessor

based systems. The byte wide organization simplifies the

memory array design, and keeps operating power down to a

minimum because only one device is enabled at a time. The

address latches allow very simple interfacing to recent generation microprocessors which employ a multiplexed

address/data bus. The convenient output enable control also

simplifies multiplexed bus interfacing by allowing the data

outputs to be controlled independent of the chip enable.

Pinouts

HM-6516/883

1

A7

2

A6

3

A5

4

A4

5

A3

6

A2

7

A1

8

A0

9

DQ0

10

DQ1

11

DQ2

12

GND

(CERDIP)

TOP VIEW

120ns 200ns TEMPERA TURE RANGE PACKAGE PKG. NO.

HM1-6516B/883 HM1-6516/883 -55oC to 125oC CERDIP F24.6

HM4-6516B/883 - -55oC to +125oC CLCC J32.A

HM-6516/883

(CLCC)

TOP VIEW

NC

1

3 2

24

VCC

23

A8

22

A9

21

W

20

G

19

A10

18

E

17

DQ7

16

DQ6

15

DQ5

14

DQ4

13

DQ3

NC

DQ0

4 32 31 30

A6

5

A5

6

A4

7

8

A3

9

A2

A1

10

A0

11

12

13

14

16 17 18 19 20

15

DQ1

DQ2

GND

NC

DQ3

NC

DQ4

NC

DQ5

29

A8

28

A9

27

NC

26

W

G

25

A10

24

E

23

22

DQ7

DQ6

21

VCC

NC

NC

A7

PIN DESCRIPTION

NC No Connect

A0 - A10 Address Inputs

E Chip Enable/Power Down

VSS/GND Ground

DQ0 - DQ7 Data In/Data Out

VCC Power (+5V)

W Write Enable

G Output Enable

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

http://www.intersil.com or 407-727-9207

| Copyright © Intersil Corporation 1999

6-173

File Number 2999.1

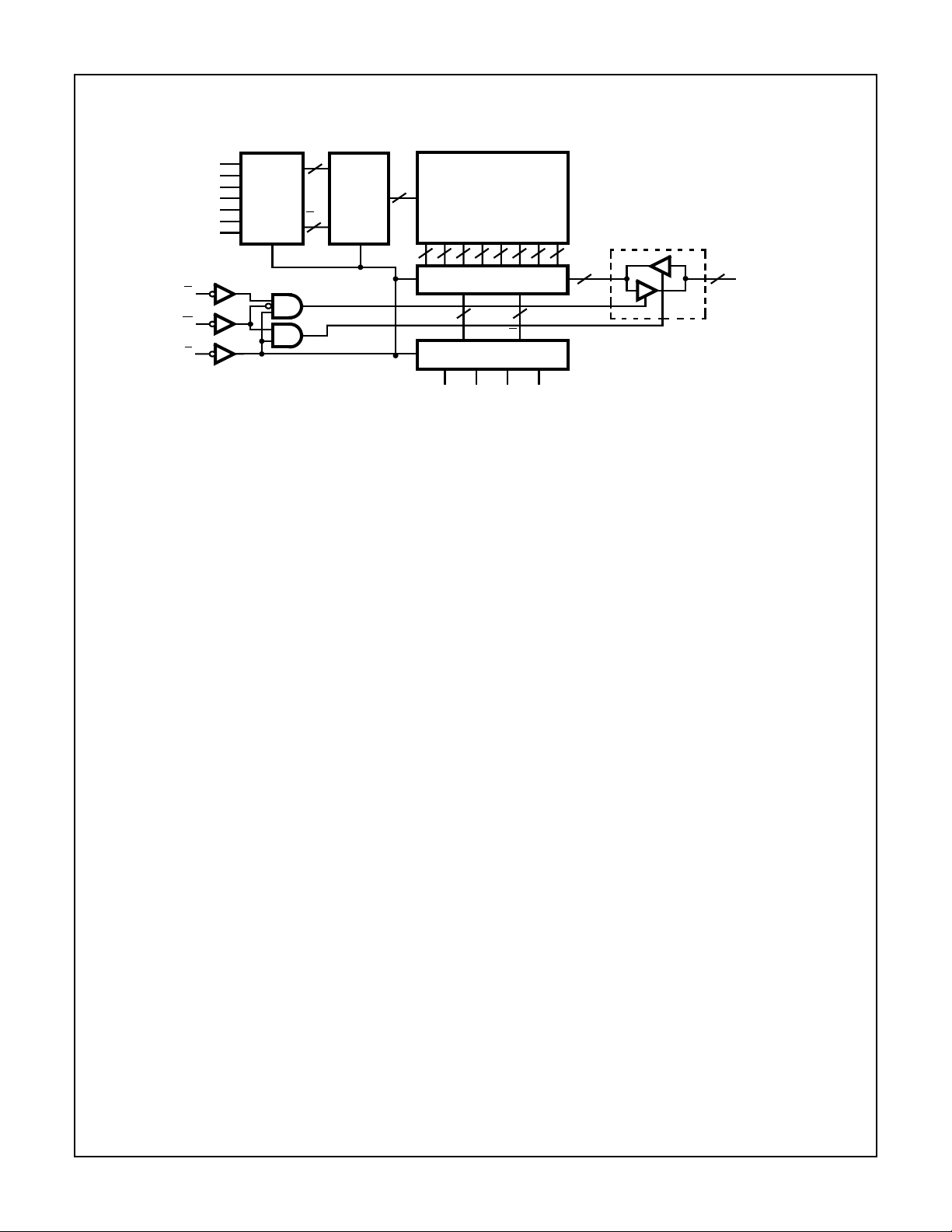

Functional Diagram

HM-6516/883

A10

A9

LATCHED

A8

ADDRESS

A7

A6

REGISTER

A5

A4

G

W

E

A

7

GATED

ROW

DECODER

A

7

LG

128

16

16

G

L

LATCHED ADDRESS

A3 A2 A1 A0

128 x 128

MATRIX

16

16

16

GATED COLUMN

DECODER

44

A

REGISTER

16 16

A

1 OF 8

16

A

8

A

DQ0

THRU

8

DQ7

6-174

HM-6516/883

Absolute Maximum Ratings Thermal Information

Supply Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .+7.0V

Input or Output Voltage Applied for all Grades. . . . . . .GND -0.3V to

VCC +0.3V

ESD Classification . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Class 1

CAUTION: Stresses above those listed in “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress only rating and operation

of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

Operating Conditions

Operating Voltage Range. . . . . . . . . . . . . . . . . . . . . +4.5V to +5.5V

Operating Temperature Range. . . . . . . . . . . . . . . .-55oC to +125oC

Input Low Voltage. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0V to +0.8V

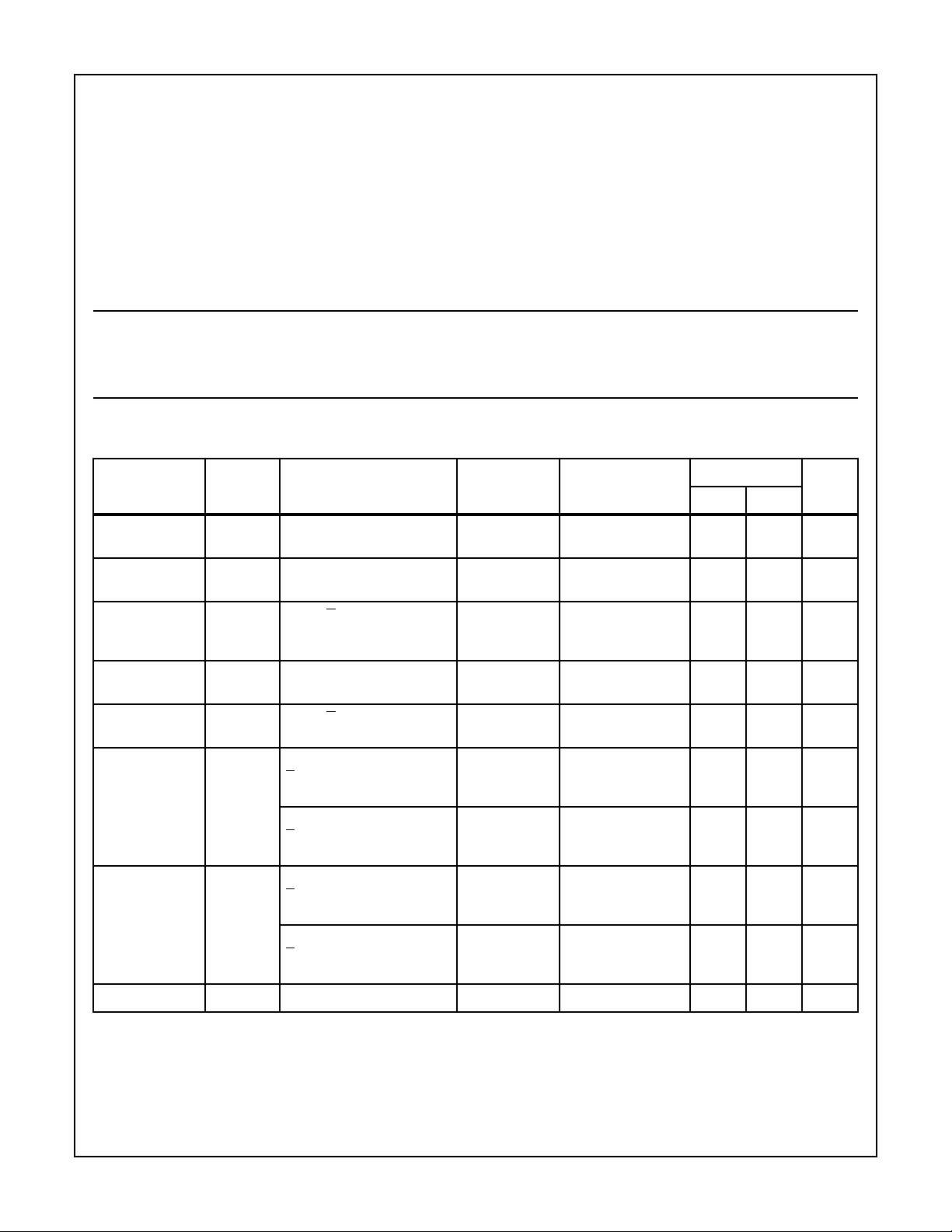

TABLE 1. HM-6516/883 DC ELECTRICAL PERFORMANCE SPECIFICATIONS

Device Guaranteed and 100% Tested

Thermal Resistance θ

CERDIP Package . . . . . . . . . . . . . . . . 48oC/W 8oC/W

CLCC Package . . . . . . . . . . . . . . . . . . 66oC/W 12oC/W

Maximum Storage Temperature Range . . . . . . . . .-65oC to +150oC

Maximum Junction Temperature. . . . . . . . . . . . . . . . . . . . . .+175oC

Maximum Lead Temperature (Soldering 10s). . . . . . . . . . . .+300oC

JA

θ

JC

Die Characteristics

Gate Count . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25953 Gates

Input High Voltage. . . . . . . . . . . . . . . . . . . . . . . . . . . . +2.4V to VCC

Data Retention Supply Voltage. . . . . . . . . . . . . . . . . . . 2.0V to 4.5V

Input Rise and Fall Time. . . . . . . . . . . . . . . . . . . . . . . . . . 40ns Max

PARAMETER SYMBOL

High Level

Output Voltage

Low Level

Output Voltage

High Impedance

Output Leakage

Current

Input Leakage

Current

Operating Supply

Current

Standby Supply

Current

Data Retention

Supply Current

VOH VCC = 4.5V

VOL VCC = 4.5V

IIOZ VCC =G = 5.5 V,

ICCOP VCC = G = 5.5V, (Note 2)

ICCSB1 VCC = 5.5V, HM-6516/883

ICCDR VCC = 2.0V, HM-6516/883

(NOTE 1)

CONDITIONS

IO = -1.0mA

IO = 3.2mA

VIO = GND or VCC

II VCC = 5.5V,

VI = GND or VCC

f = 1MHz, VI = GND or VCC

E = VCC-0.3V,

IO = 0mA, VI = GND or VCC

VCC = 5.5V, HM-6516B/883

E = VCC -0.3V,

IO = 0mA, VI = GND or VCC

E = VCC-0.3V,

IO = 0mA, VI = GND or VCC

GROUP A

LIMITS

SUBGROUPS TEMPERATURE

1, 2, 3 -55oC ≤ TA≤ +125oC 2.4 - V

1, 2, 3 -55oC ≤ TA≤ +125oC - 0.4 V

1, 2, 3 -55oC ≤ TA≤ +125oC -1.0 1.0 µA

1, 2, 3 -55oC ≤ TA≤ +125oC -1.0 1.0 µA

1, 2, 3 -55oC ≤ TA≤ +125oC - 10 mA

1, 2, 3 -55oC ≤ TA≤ +125oC - 100 µA

1, 2, 3 -55oC ≤ TA≤ +125oC- 50 µA

1, 2, 3 -55oC ≤ TA≤ +125oC- 50 µA

UNITSMIN MAX

VCC = 2.0V, HM-6516B/883

E = VCC-0.3V,

IO = 0mA, VI = GND or VCC

Functional Test FT VCC = 4.5V (Note 3) 7, 8A, 8B -55oC ≤ TA≤ +125oC---

NOTES:

1. All voltages referenced to device GND.

2. Typical derating 1.5mA/MHz increase in ICCOP.

3. Tested as follows: f = 2MHz, VIH = 2.4V, VIL = 0.4V, IOH = -4.0mA, IOL = 4.0mA, VOH ≥ 1.5V, and VOL ≤ 1.5V.

1, 2, 3 -55oC ≤ TA≤ +125oC- 25 µA

6-175

Loading...

Loading...