Intersil Corporation HM-6514 Datasheet

HM-6514

March 1997

Features

• Low Power Standby. . . . . . . . . . . . . . . . . . . 125µW Max

• Low Power Operation . . . . . . . . . . . . . 35mW/MHz Max

• Data Retention . . . . . . . . . . . . . . . . . . . . . . . at 2.0V Min

• TTL Compatible Input/Output

• Common Data Input/Output

• Three-State Output

• Standard JEDEC Pinout

Description

The HM-6514 is a 1024 x 4 static CMOS RAM fabricated

using self-aligned silicon gate technology. The device utilizes

synchronous circuitry to achieve high performance and low

power operation.

On-chip latches are provided for addresses allowing efficient

interfacing with microprocessor systems. The data output

can be forced to a high impedance state for use in expanded

memory arrays.

Gated inputs allow lower operating current and also elimi-

1024 x 4 CMOS RAM

nate the need for pull up or pull down resistors. The

• Fast Access Time. . . . . . . . . . . . . . . . . . 120/200ns Max

• 18 Pin Package for High Density

• On-Chip Address Register

HM-6514 is a fully static RAM and may be maintained in any

state for an indefinite period of time.

Data retention supply voltage and supply current are guaranteed over temperature.

• Gated Inputs - No Pull Up or Pull Down Resistors

Required

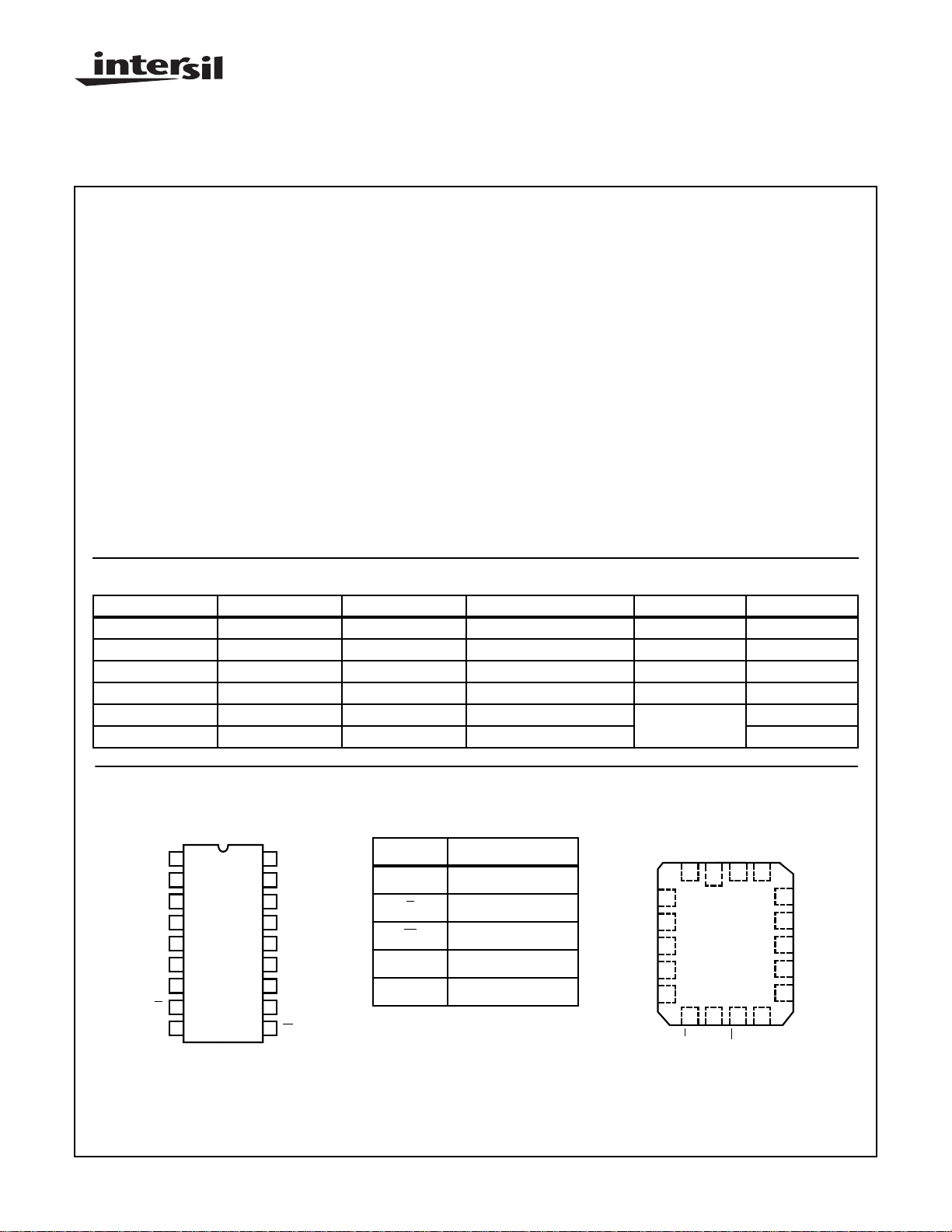

Ordering Information

120ns 200ns 300ns TEMPERATURE RANGE PACKAGE PKG. NO.

HM3-6514S-9 HM3-6514B-9 HM3-6514-9 -40oC to +85oC PDIP E18.3

HM1-6514S-9 HM1-6514B-9 HM1-6514-9 -40oC to +85oC CERDIP F18.3

24502BVA - - - JAN# F18.3

8102402VA 8102404VA 8102406VA - SMD# F18.3

----40

- - HM4-6514-B -55oC to +125oC J18.B

o

C to +85oC CLCC J18.B

Pinouts

HM-6514 (PDIP, CERDIP)

TOP VIEW

1

A6

2

A5

3

A4

4

A3

5

A0

6

A1

7

A2

8

E

9

GND

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

http://www.intersil.com or 407-727-9207

18

V

CC

17

A7

16

A8

15

A9

14

DQ0

13

DQ1

12

DQ2

11

DQ3

10

W

| Copyright © Intersil Corporation 1999

PIN DESCRIPTION

A Address Input

E Chip Enable

W Write Enable

D Data Input

Q Data Output

6-1

A4

A3

A0

A1

A2

3

4

5

6

7

HM-6514 (CLCC)

TOP VIEW

A6

GND

CC

V

18

W

A5

21 17

8 9 10 11

E

File Number 2995.1

A7

DQ3

16

A8

A9

15

14

DQ0

13

DQ1

12

DQ2

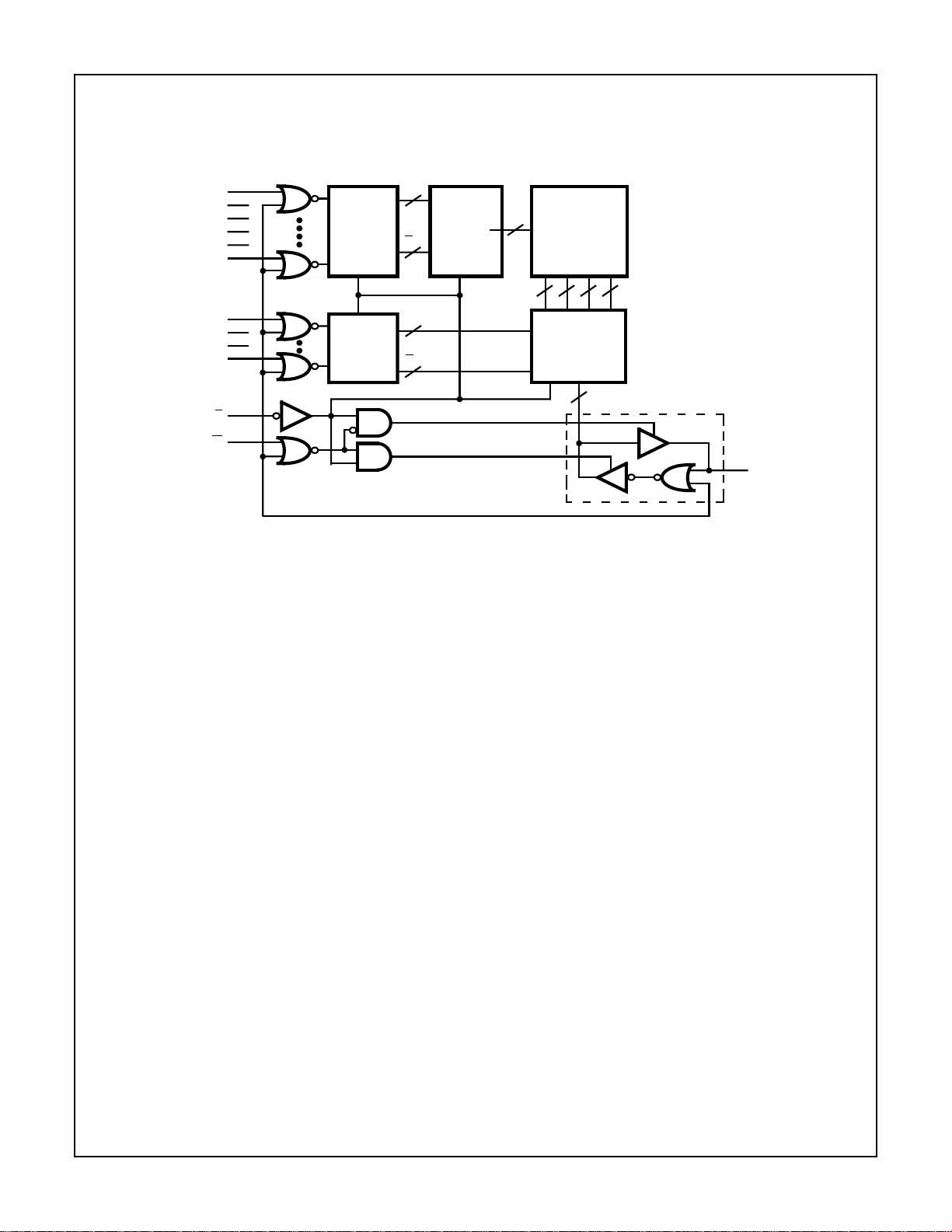

Functional Diagram

HM-6514

LSB

LSB

A9

A8

A7

A6

A5

A4

A2

A1

A0

A3

A

A

A

A

6

6

4

4

GATED

ROW

DECODER

G

64

16 16 16 16

I/O SELECT

G

64 x 64

MATRIX

GATED

COLUMN

4

1 OF 4

DQ

LATCHED

ADDRESS

REGISTER

L

L

LATCHED

ADDRESS

REGISTER

E

W

6-2

HM-6514

Absolute Maximum Ratings Thermal Information

Supply Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .+7.0V

Input, Output or I/O Voltage . . . . . . . . . . . GND -0.3V to VCC+0.3V

ESD Classification . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Class 1

Operating Conditions

Operating Voltage Range . . . . . . . . . . . . . . . . . . . . . +4.5V to +5.5V

Operating Temperature Ranges:

HM-6514S-9, HM-6514B-9, HM-6514-9. . . . . . . . -40oC to +85oC

HM-6514B-8, HM-6514-8 . . . . . . . . . . . . . . . . . . -55oC to +125oC

CAUTION: Stresses above those listed in “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress only rating and operation

of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

Thermal Resistance (Typical) θ

CERDIP Package . . . . . . . . . . . . . . . . 75oC/W 15oC/W

PDIP Package. . . . . . . . . . . . . . . . . . . 75oC/W N/A

CLCC Package . . . . . . . . . . . . . . . . . . 90oC/W 33oC/W

Maximum Storage Temperature Range . . . . . . . . .-65oC to +150oC

Maximum Junction Temperature

Ceramic Package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . +175oC

Plastic Package. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . +150oC

Maximum Lead Temperature (Soldering 10s). . . . . . . . . . . . +300oC

JA

θ

JC

Die Characteristics

Gate Count . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6910 Gates

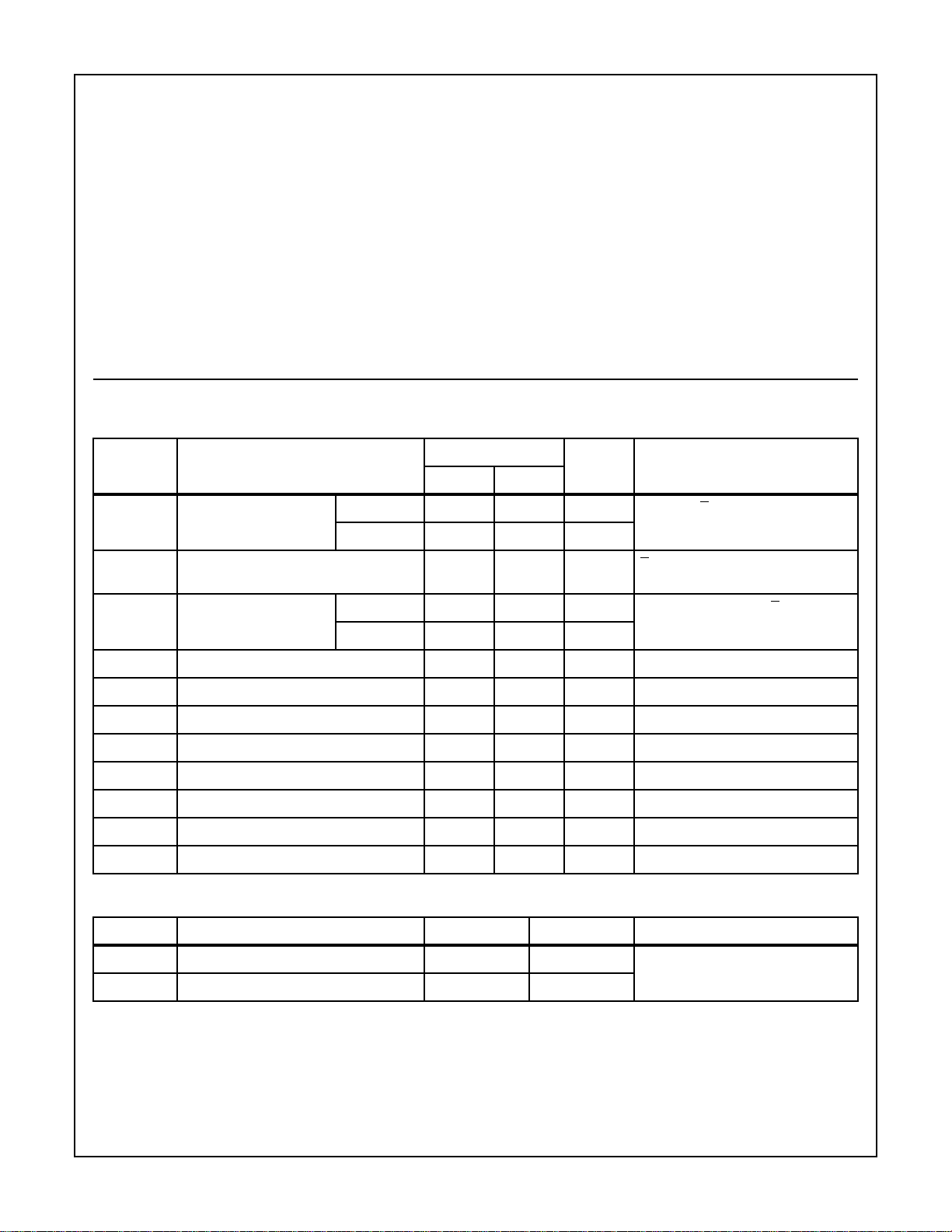

DC Electrical Specifications V

SYMBOL PARAMETER

ICCSB Standby Supply Current HM-6514-9 - 25 µA IO = 0mA, E = VCC-0.3V, VCC = 5.5V

ICCOP Operating Supply Current (Note 1) - 7 mA E = 1MHz, IO = 0mA, VI = GND,

ICCDR Data Retention Supply

Current

VCCDR Data Retention Supply Voltage 2.0 - V

II Input Leakage Current -1.0 +1.0 µA VI = VCC or GND, VCC = 5.5V

IIOZ Input/Output Leakage Current -1.0 +1.0 µA VIO = VCC or GND, VCC = 5.5V

VIL Input Low Voltage -0.3 0.8 V VCC = 4.5V

VIH Input High Voltage VCC -2.0 VCC +0.3 V VCC = 5.5V

VOL Output Low Voltage - 0.4 V IO = 2.0mA, VCC = 4.5V

VOH1 Output High Voltage 2.4 - V IO = -1.0mA, VCC = 4.5V

= 5V ±10%; TA = -40oC to +85oC (HM-6514S-9, HM-6514B-9, HM-6514-9)

CC

HM-6514-8 - 50 µA

HM-6514-9 - 15 µA IO = 0mA, VCC = 2.0V, E = V

HM-6514-8 - 25 µA

TA = -55oC to +125oC (HM-6514B-8, HM-6514-8)

LIMITS

UNITS TEST CONDITIONSMIN MAX

VCC = 5.5V

CC

VOH2 Output High Voltage (Note 2) VCC -0.4 - V IO = -100µA, VCC = 4.5V

Capacitance T

SYMBOL PARAMETER MAX UNITS TEST CONDITIONS

CI Input Capacitance (Note 2) 8 pF f = 1MHz, All measurements are

CIO Input/Output Capacitance (Note 2) 10 pF

NOTES:

1. Typical derating 5mA/MHz increase in ICCOP.

2. Tested at initial design and after major design changes.

= +25oC

A

referenced to device GND

6-3

Loading...

Loading...