Intersil Corporation HIP6503 Datasheet

TM

HIP6503

Data Sheet June 2000

Multiple Linear Power Controller with

ACPI Control Interface

The HIP6503 complements either an HIP6020 or an

HIP6021 in ACPI-compliant designs for microprocessor and

computer applications. The IC integrates four linear

controllers/regulators, switching, monitoring and control

functions into a 20 pin SOIC package. One linear controller

generates the 3.3V

supply’s 5VSB output, powering the south bridge and the

PCI slots through an external pass transistor during sleep

states (S3, S4/S5). A second transistor is used to switch in

the ATX 3.3V output for operation during S0 and S1/S2

(active) operating states. A linear controllers/regulator

supplies at choice either of 2.5V or 3.3V memory power

through external pass transistors (switch for 3.3V setting) in

active states. During sleep states, integrated pass

transistors supply the sleep power. Another controller

powers up the 5V

output in active states, and the ATX 5VSB in sleep states.

Two internal regulators output both a dedicated, noise-free

2.5V clock chip supply, as well as a 1.8V ICH2 resume well

voltage. The HIP6503’s operating mode (active outputs or

sleep outputs) is selectable through two digital control pins,

S3 and S5. Enabling sleep state support on the 5V

output is offeredthroughtheEN5VDL pin. In active state, the

3.3V

/3.3VSB and 2.5V

DUAL

use external N-channel pass MOSFETs to connect the

outputs directly to the 3.3V input supplied by an ATX power

supply, for minimal losses. In sleep state, power delivery on

both outputs is transferred to NPN transistors - external to

the controller on the 3.3V

2.5V

MEM

/3.3V

MEM

output is performed through an external NPN transistor. The

5V

output is powered through two external MOS

DUAL

transistors. In sleep states, a PMOS (or PNP) transistor

conducts the current from the ATX 5VSB output; while in

active state, current flow is transferred to an NMOS

transistor connected to the ATX 5V output. The operation of

the 5V

output is dictated not only by the status of the

DUAL

S3 and S5 pins, but that of the EN5VDL pin as well. The

3.3V

/3.3VSBand 1.8VSBoutputs are active for as long

DUAL

as the ATX 5VSB voltage is applied to the chip. The 2.5V

output is only active during S0 and S1/S2, and uses the 3V3

pin as input source for its internal pass element.

/3.3VSBvoltage plane from the ATX

DUAL

plane by switching in the ATX 5V

DUAL

/3.3V

MEM

/3.3VSB, internal on the

DUAL

linear regulators

MEM

. Active state regulation on the 2.5V

DUAL

MEM

CLK

File Number 4882.1

Features

• Provides 5 ACPI-Controlled Voltages

-5V

- 3.3V

- 2.5V

- 2.5V

- 1.8V

USB/Keyboard/Mouse (Active/Sleep)

DUAL

/3.3VSB PCI/Auxiliary/LAN (Active/Sleep)

DUAL

RDRAM or 3.3V

MEM

Clock/Processor Terminations (Active Only)

CLK

ICH2 Resume

SB

SDRAM (Active/Sleep)

MEM

• Excellent Output Voltage Regulation

- 3.3V

/3.3VSB Output: ±2.0% Over Temperature;

DUAL

Sleep State Only

- 2.5V

Both Operational States (3.3V

- 1.8V

MEM

, 2.5V

SB

/3.3V

Output: ±2.0% Over Temperature;

MEM

Outputs: ±2.0% Over Temperature

CLK

in sleep only)

MEM

• Small Size

- Very Low External Component Count

• Dual Memory Voltage Selection Via FAULT/MSEL Pin

- 2.5V for RDRAM Memory

- 3.3V for SDRAM Memory

• Undervoltage Monitoring of All Outputs with Centralized

FAULT Reporting and Temperature Shutdown

Applications

•

Motherboard Power Regulation for ACPI-Compliant

Computers

Pinout

HIP6503

(SOIC)

TOP VIEW

5VSB

1V8IN

1V8SB

3V3DLSB

3V3DL

VCLK

3V3

EN5VDL

S3

S5

1

2

3

4

5

6

7

8

9

10

20

VSEN2

19

DRV2

18

5V

17

12V

16

SS

5VDL

15

5VDLSB

14

13

DLA

12

FAULT/MSEL

11

GND

Ordering Information

TEMP.

PART NUMBER

HIP6503CB 0 to 70 20 Ld SOIC M20.3

HIP6503EVAL1 Evaluation Board

RANGE (oC) PACKAGE

1

1-888-INTERSIL or 321-724-7143 | Intersil and Design is a trademark of Intersil Corporation. | Copyright © Intersil Corporation 2000

PKG.

NO.

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

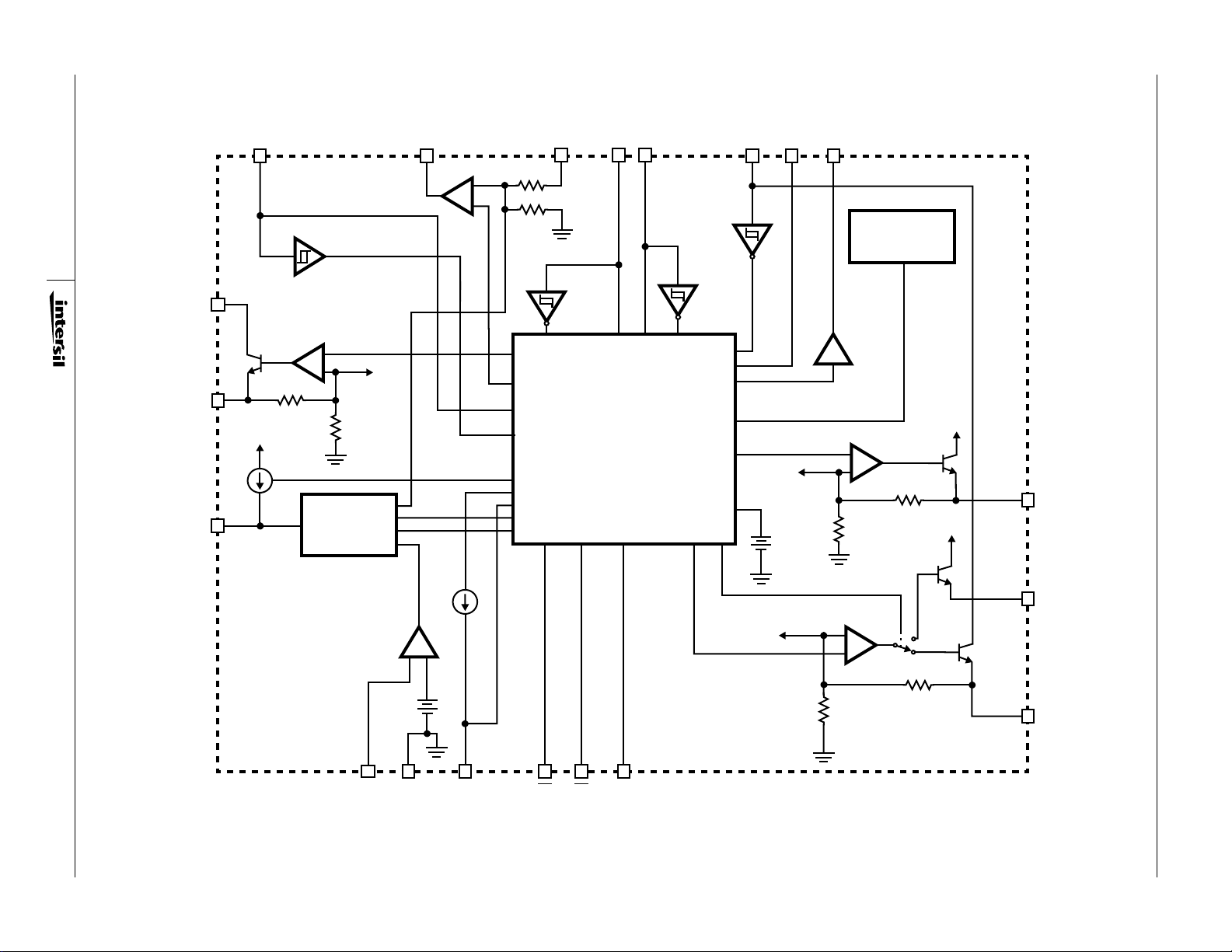

Block Diagram

12V

12V MONITOR

3V3DLSB

EA4

-

+

3V3DL

2

1V8IN

EA3

10.8V/9.8V

+

5V MONITOR

4.5V/4.25V

5V

3V3

3V3 MONITOR

5VSB POR

4.4V/3.4V

2.97V/2.8V

5VSB

DLA

5VDLSB

TEMPERATURE

MONITOR

(TMON)

-

TO UV

1V8SB

TO 5VSB

40µA

FAULT/MSEL

DETECTOR

UV DETECTOR

MONITOR AND CONTROL

TO

UV DETECTOR

+

1.265V

TO 3V3

EA3

+

HIP6503

-

VCLK

TO 5V

-

UV COMP

10µA

TO UV

DETECTOR

+

-

EA2

-

+

DRV2

5VDL

4.15V

GND

+

-

SS

S3

S5

EN5VDL

VSEN2

FIGURE 1.

Simplified Power System Diagram

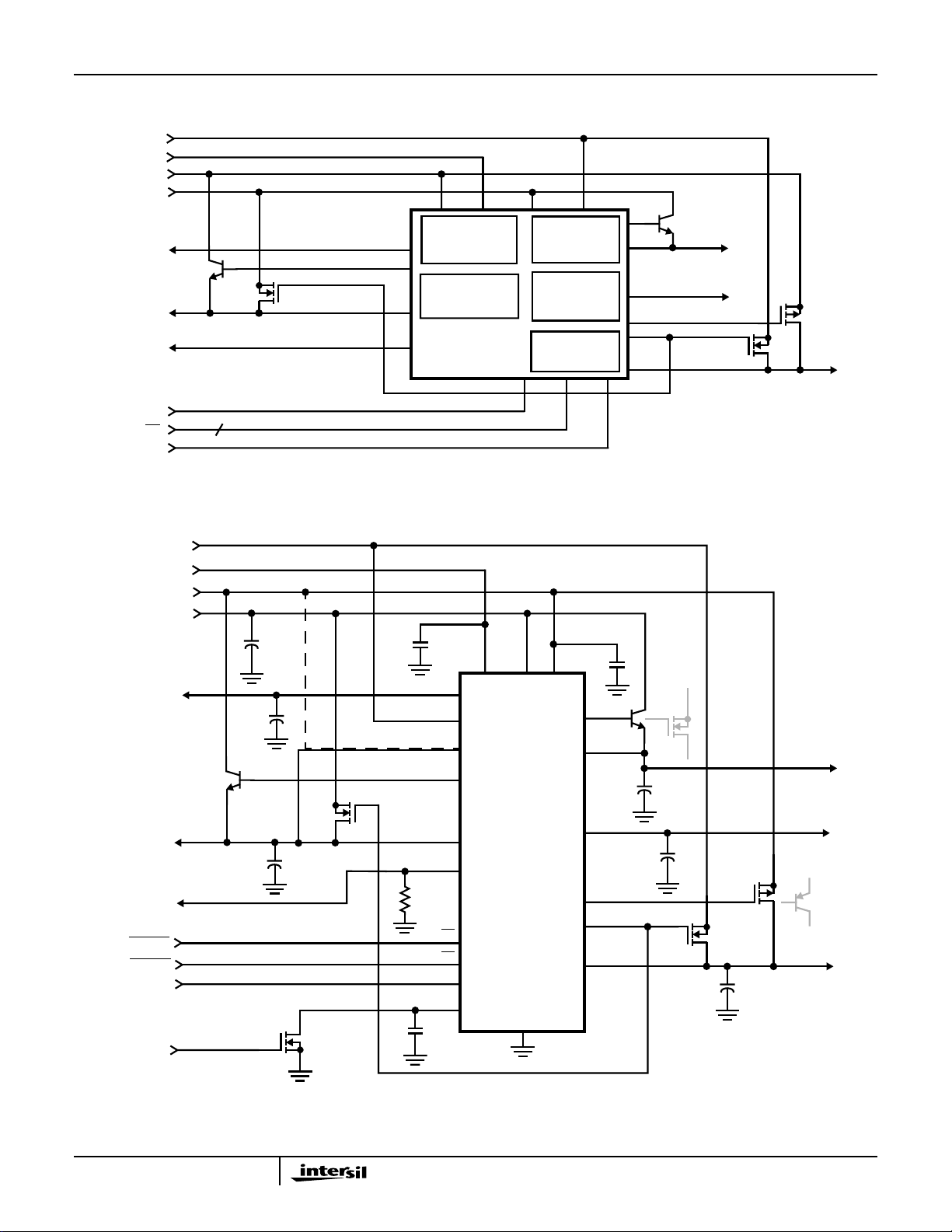

+5V

IN

+12V

IN

+5V

SB

+3.3V

IN

HIP6503

1.8V

SB

1.8V

Q2

3.3V

FAULT\MSEL

SHUTDOWN

DUAL

SX

EN5VDL

/3.3V

3.3V

SB

2

Typical Application

+5V

IN

+12V

IN

+5V

SB

+3.3V

IN

V

OUT1

1.8V

3.3V

DUAL

FAULT

SLP_S3

SLP_S5

EN5VDL

V

OUT3

SB

/3.3V

C

Q2

SB

Q3

OUT1

C

OUT3

Q3

REGULATOR

CONTROLLER

HIP6503

1V8SB

5V

1V8IN

3V3DLSB

3V3DL

FAULT/MSEL

R

SEL

S3

S5

EN5VDL

SS

LINEAR

LINEAR

FIGURE 2.

12V

HIP6503

3V3

LINEAR

CONTROLLER

LINEAR

REGULATOR

CONTROL

LOGIC

5VSB

DRV2

VSEN2

C

VCLK

5VDLSB

DLA

5VDL

OUT2

C

OUT4

Q1

Q1

C

OUT5

V

MEM

2.5V/3.3V

V

CLK

2.5V

Q5

Q5

2.5/3.3V

Q4

Q4

5V

V

V

2.5V

V

5V

DUAL

5V

OUT2

MEM

OUT4

CLK

OUT5

DUAL

SHUTDOWN

C

SS

GND

FIGURE 3.

3

HIP6503

Absolute Maximum Ratings Thermal Information

Supply Voltage, V

12V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . GND - 0.3V to +14.5V

DLA, DRV2. . . . . . . . . . . . . . . . . . . . . . . .GND - 0.3V to V

All Other Pins. . . . . . . . . . . . . . . . . . . . .GND - 0.3V to 5VSB + 0.3V

ESD Classification . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Class 3

Recommended Operating Conditions

Supply Voltage, V

Lowest 5VSB Supply Voltage Guaranteeing Parameters . . . . +4.5V

Digital Inputs, VSX,V

Ambient Temperature Range. . . . . . . . . . . . . . . . . . . . . 0oC to 70oC

Junction Temperature Range. . . . . . . . . . . . . . . . . . . .0oC to 125oC

CAUTION: Stresses above those listed in “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress only rating and operation of the

device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

NOTE:

1. θJA is measured with the component mounted on a high effective thermal conductivity test board in free air. See Tech Brief TB379 for details.

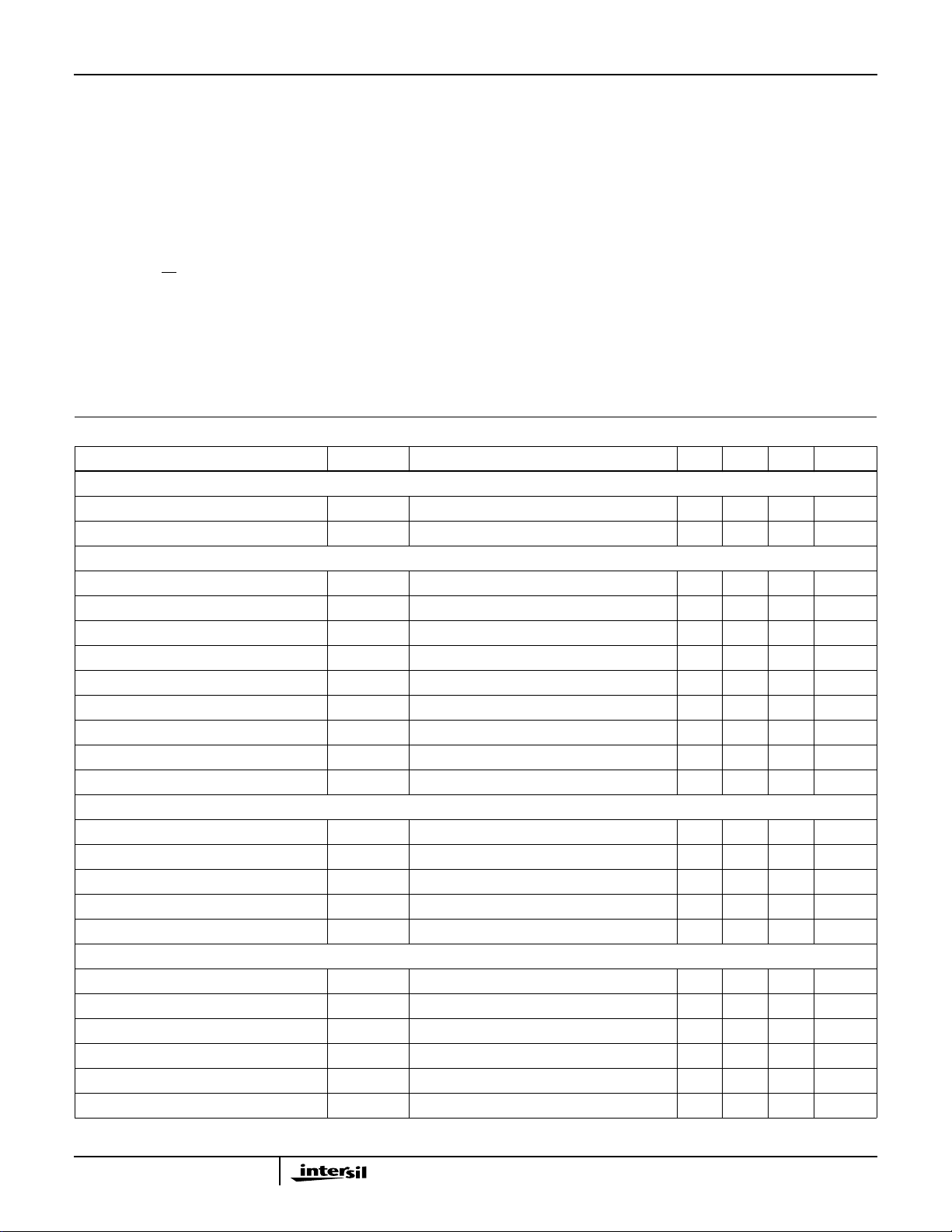

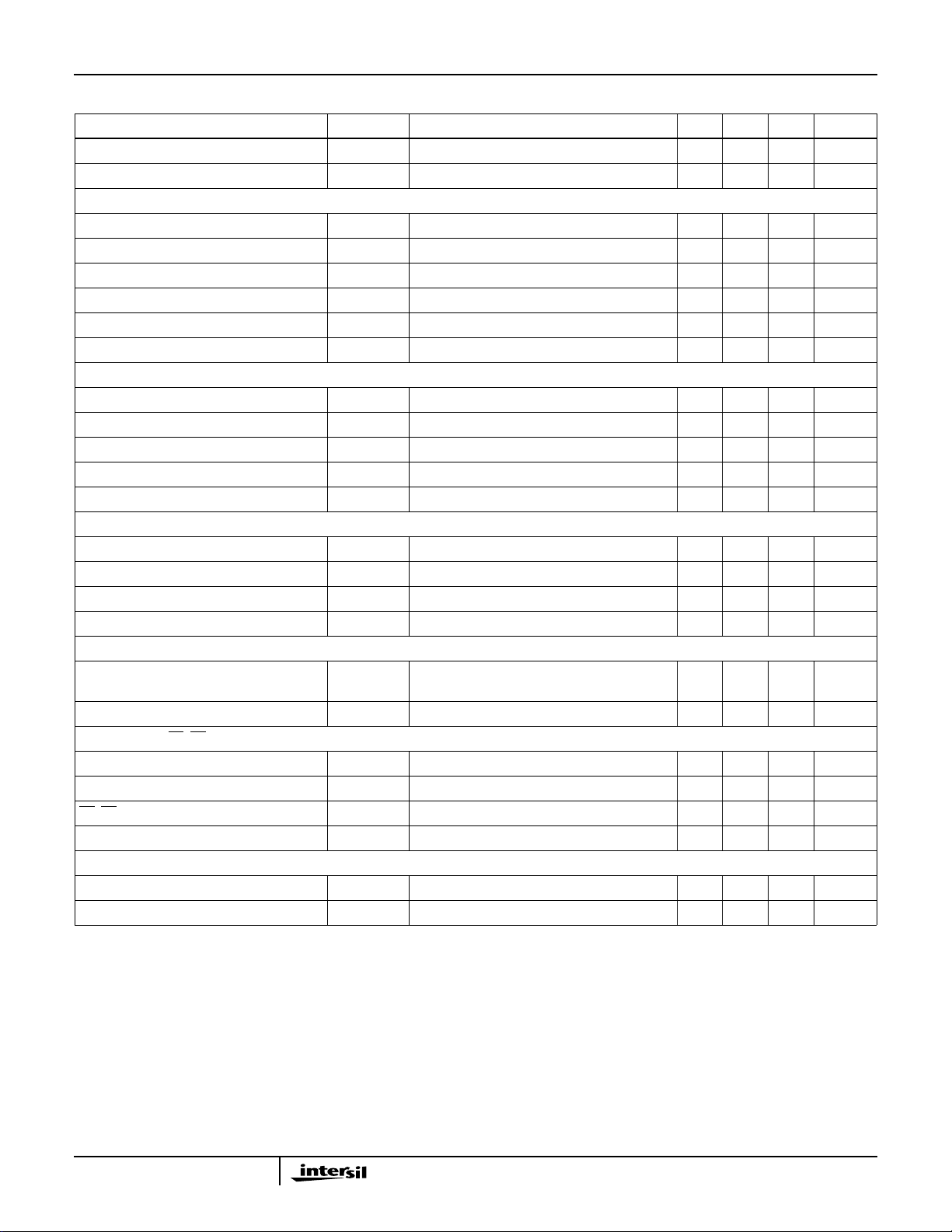

Electrical Specifications Recommended Operating Conditions, Unless Otherwise Noted Refer to Figures 1, 2 and 3

PARAMETER (Note 2) SYMBOL TEST CONDITIONS MIN TYP MAX UNITS

VCC SUPPLY CURRENT

Nominal Supply Current I

Shutdown Supply Current I

POWER-ON RESET, SOFT-START, AND VOLTAGE MONITORS

Rising 5VSB POR Threshold - - 4.5 V

5VSB POR Hysteresis - 1.0 - V

Rising 12V Threshold - - 10.8 V

12V Hysteresis - 1.0 - V

Rising 3V3 and 5V Thresholds -90- %

3V3 and 5V Hysteresis -5- %

Falling Threshold Timeout (All Monitors) -10- µs

Soft-Start Current I

Shutdown Voltage Threshold V

1.8VSB LINEAR REGULATOR (V

Regulation - - 2.0 %

1V8SB Nominal Voltage Level V

1V8SB Undervoltage Rising Threshold - 1.494 - V

1V8SB Undervoltage Hysteresis -54- mV

1V8SB Output Current I

2.5/3.3V

Regulation (Note 2) - - 2.0 %

VSEN2 Nominal Voltage Level V

VSEN2 Nominal Voltage Level V

VSEN2 Undervoltage Rising Threshold -83- %

VSEN2 Undervoltage Hysteresis (Note 3) - 3 - %

VSEN2 Output Current I

LINEAR REGULATOR (V

MEM

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . +7.0V

5VSB

. . . . . . . . . . . . . . . . . . . . . . . . . . . +5V ±5%

5VSB

. . . . . . . . . . . . . . . . . . . . . . 0 to +5.5V

EN5VDL

5VSB

5VSB(OFF)VSS

SS

SD

)

OUT1

1V8SB

1V8SB

)

OUT2

VSEN2RSEL

VSEN2RSEL

VSEN2

Thermal Resistance (Typical, Note 1) θJA (oC/W)

SOIC Package. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87

+0.3V

12V

Maximum Junction Temperature (Plastic Package) . . . . . . . .150oC

Maximum Storage Temperature Range. . . . . . . . . . -65oC to 150oC

Maximum Lead Temperature (Soldering 10s) . . . . . . . . . . . . .300oC

(SOIC - Lead Tips Only)

-30- mA

= 0.8V - 14 - mA

-10- µA

- - 0.8 V

- 1.8 - V

1V8IN = 3.3V 250 300 - mA

= 1kΩ - 2.5 - V

= 10kΩ - 3.3 - V

5VSB = 5V 250 300 - mA

4

HIP6503

Electrical Specifications Recommended Operating Conditions, Unless Otherwise Noted Refer to Figures 1, 2 and 3 (Continued)

PARAMETER (Note 2) SYMBOL TEST CONDITIONS MIN TYP MAX UNITS

DRV2 Output Drive Current I

DRV2

DRV2 Output Impedance R

3.3V

/3.3VSB LINEAR REGULATOR (V

DUAL

OUT3

)

Sleep State Regulation - - 2.0 %

3V3DL Nominal Voltage Level V

3V3DL

3V3DL Undervoltage Rising Threshold - 2.739 - V

3V3DL Undervoltage Hysteresis -99- mV

3V3DLSB Output Drive Current I

3V3DLSB

DLA Output Impedance -90- Ω

2.5V

LINEAR REGULATOR (V

CLK

OUT4

)

Regulation - - 2.0 %

VCLK Nominal Voltage Level V

VCLK

VCLK Undervoltage Rising Threshold - 2.075 - V

VCLK Undervoltage Hysteresis -75- mV

VCLK Output Current (Note 4) I

5V

SWITCH CONTROLLER (V

DUAL

OUT5

VCLK

)

5VDL Undervoltage Rising Threshold - 4.150 - V

5VDL Undervoltage Hysteresis - 150 - mV

5VDLSB Output Drive Current I

5VDLSB

5VDLSB Pull-Up Impedance to 5VSB - 350 - Ω

TIMING INTERVALS

Active State Assessment Past Input UV

Thresholds (Note 5)

Active-to-Sleep Control Input Delay - 200 - µs

CONTROL I/O (S3, S5, EN5VDL, FAULT/MSEL)

High Level Input Threshold - - 2.2 V

Low Level Input Threshold 0.8 - - V

S3, S5 Internal Pull-up Impedance to 5VSB - 50 - kΩ

FAULT Output Impedance FAULT = high - 100 - Ω

TEMPERATURE MONITOR

Fault-Level Threshold (Note 6) 125 - Shutdown-Level Threshold (Note 6) - 155 -

NOTES:

2. Sleep-State Only for 3.3V Setting

3. Parameters not guaranteed for 5VSB < 4.0V.

4. At Ambient Temperatures Less Than 50oC.

5. Guaranteed by Correlation.

6. Guaranteed by Design.

5VSB = 5V, R

= 10kΩ - 200 - Ω

SEL

= 1kΩ 220 - - mA

SEL

- 3.3 - V

5VSB = 5V 5 10 - mA

- 2.5 - V

V

= 3.3V 500 800 - mA

3V3

5VDLSB = 4V, 5VSB = 5V -20 - -40 mA

20 25 30 ms

o

o

C

C

5

Loading...

Loading...