Intersil Corporation HIP6304 Datasheet

TM

HIP6304

Data Sheet March 2000

Microprocessor CORE Voltage Regulator

Multi-Phase Buck PWM Controller

The HIP6304 multi-phase PWM control IC together with its

companion gate drivers, the HIP6601, HIP6602 or HIP6603

and Intersil MOSFETs provides a precision voltage

regulation system for advanced microprocessors.

Multiphase power conversion is a marked departure from

earlier single phase converter configurations previously

employed to satisfy the ever increasing current demands of

modern microprocessors. Multi-phase convertors, by

distributing the power and load current results in smaller and

lower cost transistors with fewerinputand output capacitors.

These reductions accrue from the higher effective

conversion frequency with higher frequency ripple current

due to the phase interleaving process of this topology. For

example, a two phase convertor operating at 350kHz will

have a ripple frequency of 700kHz. Moreover, greater

convertor bandwidth of this design results in faster response

to load transients.

Outstanding features of this controller IC include

programmable VID codes from the microprocessor that

range from 1.30V to 2.05V with a system accuracy of ±1%.

Pull up currents on these VID pins eliminates the need for

external pull up resistors. In addition “droop” compensation,

used to reduce the overshoot or undershoot of the CORE

voltage, is easily programmed with a single resistor.

Another feature of this controller IC is the PGOOD monitor

circuit which is held low until the CORE voltage increases,

during its Soft-Start sequence, to within 10% of the

programmedvoltage.Over-voltage,15%aboveprogrammed

CORE voltage, results in the converter shutting down and

turning the lower MOSFETs ON to clamp and protect the

microprocessor. Under voltage is also detected and results

in PGOOD low if the CORE voltage falls 10% below the

programmed level. Over-current protection reduces the

regulator current to less than 25% of the programmed trip

value. These features provide monitoring and protection for

the microprocessor and power system.

File Number 4840

Features

• AMD Athlon Compatible Multi-Phase Power Conversion

• Precision Channel Current Sharing

- Loss Less Current Sampling - Uses r

DS(ON)

• Precision CORE Voltage Regulation

- ±1% System Accuracy Over Temperature

• Microprocessor Voltage Identification Input

- 4-Bit VID Input

- 1.30V to 2.05V in 50mV Steps

- Programmable “Droop” Voltage

• Fast Transient Recovery Time

• Over Current Protection

• High Ripple Frequency, (Channel Frequency) Times

Number Channels . . . . . . . . . . . . . . . . . 100kHz to 3MHz

Ordering Information

PART NUMBER TEMP. (oC) PACKAGE PKG. NO.

HIP6304CB 0 to 70 16 Ld SOIC M16.15

HIP6304CB-T 16 Ld SOIC Tape and Reel

HIP6304EVAL1 Evaluation Platform

Pinout

HIP6304 (SOIC)

TOP VIEW

1

VID3

2

VID2

3

VID1

VID0

4

EN

5

COMP ISEN2

6

FB

7

FS/DIS

8

16

15

14

13

12

11

10

9

V

CC

PGOOD

ISEN1

PWM1

PWM2

VSEN

GND

1

1-888-INTERSIL or 321-724-7143 | Intersil and Design is a trademark of Intersil Corporation. | Copyright © Intersil Corporation 2000

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

Athlon™ is a trademark of Advanced Micro Devices, Inc.

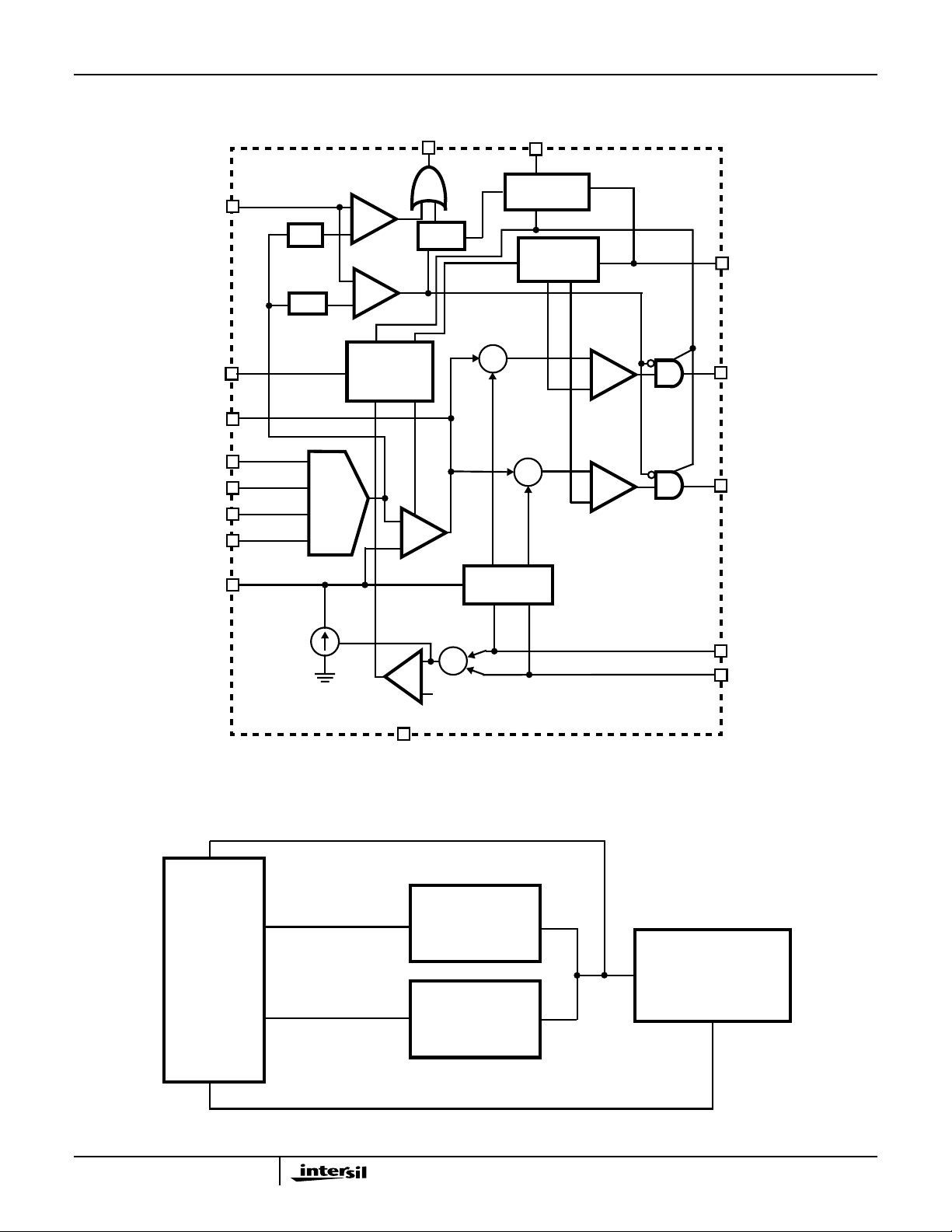

Block Diagram

HIP6304

VSEN

EN

COMP

VID0

VID1

VID2

VID3

FB

X 0.9

X1.15

D/A

UV

+

-

OVP

+

-

SOFT-

START

AND FAULT

LOGIC

PGOOD

OV

LATCH

S

+

E/A

-

V

POWER-ON

RESET (POR)

GENERATOR

+

∑

-

+

∑

CURRENT

CORRECTION

CC

CLOCK AND

SAWTOOTH

-

+

-

PWM

+

-

PWM

THREE

STATE

FS/EN

PWM1

PWM2

Simplified Power System Diagram

VSEN

PWM 1

HIP6304

PWM 2

OC

GND

I_TOT

+

-

I_TRIP

SYNCHRONOUS

RECTIFIED BUCK

SYNCHRONOUS

RECTIFIED BUCK

+

∑

+

CHANNEL

CHANNEL

ISEN1

ISEN2

MICROPROCESSOR

VID

2

HIP6304

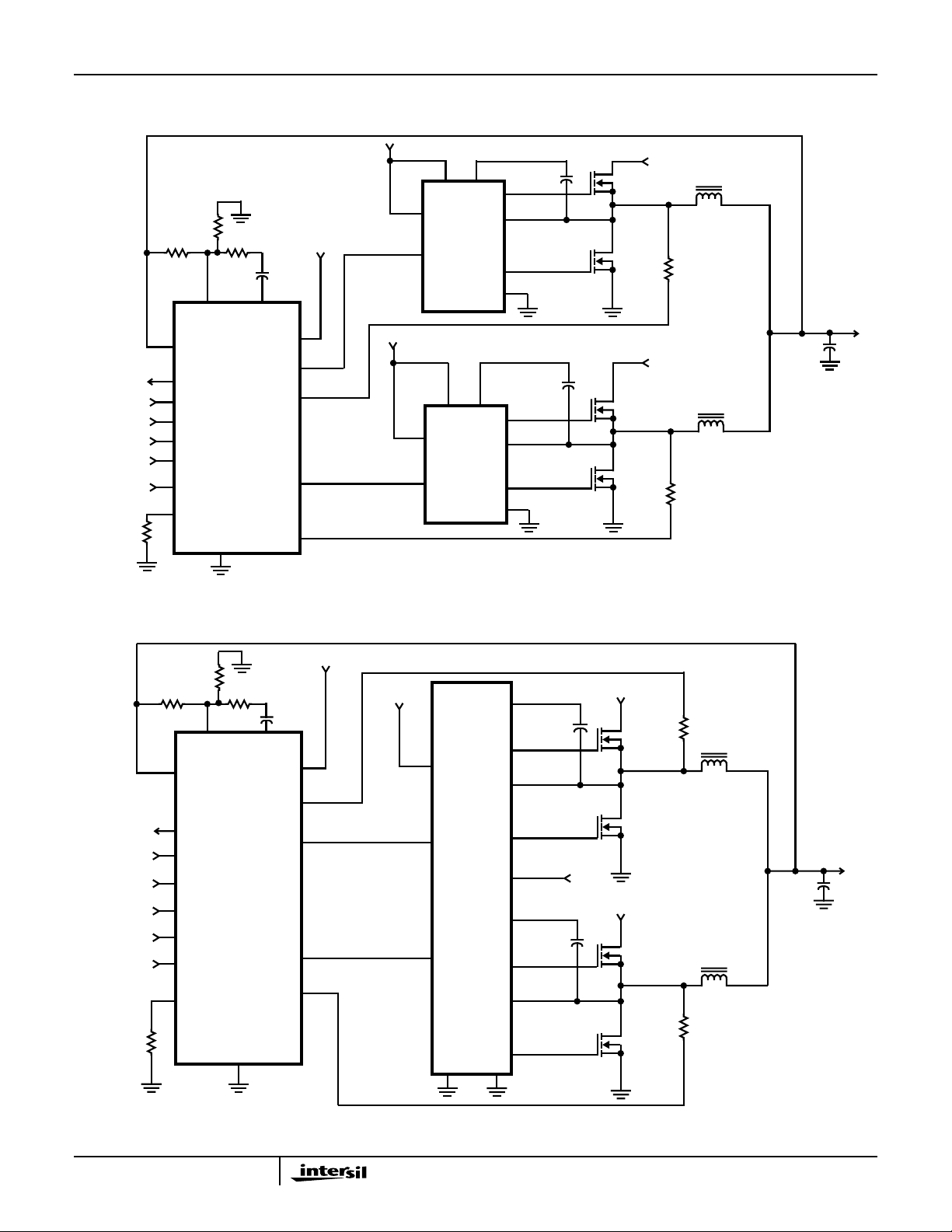

Typical Application - Two Phase Converter Using HIP6601 Gate Drivers

PGOOD

VID3

VID2

VID1

VID0

EN

FB

VSEN

CONTROL

HIP6304

FS/DIS

GND

MAIN

COMP

PWM2

ISEN2

PWM1

ISEN1

+12V

DRIVER

HIP6601

BOOT

UGATE

PHASE

LGATE

GND

BOOT

UGATE

PHASE

PVCC

VCC

+5V

V

CC

PWM

+12V

PVCC

VCC

VIN = +5V

V

= +5V

IN

+V

CORE

DRIVER

PWM

HIP6601

LGATE

GND

Typical Application - Two Phase Converter Using a HIP6602 Gate Driver

+5V

V

= +12V

+5V

IN

V

+12V

IN

PGOOD

EN

VID3

VID2

VID1

VID0

FB

VSEN

CONTROL

FS/DIS

MAIN

HIP6304

GND

COMP

ISEN1

PWM1

PWM2

ISEN2

+12V

V

CC

VCC

PWM1

DUAL

DRIVER

BOOT1

UGATE1

PHASE1

LGATE1

PVCC

HIP6602

BOOT2

PWM2

UGATE2

PHASE2

LGATE2

+V

CORE

GND

PGND

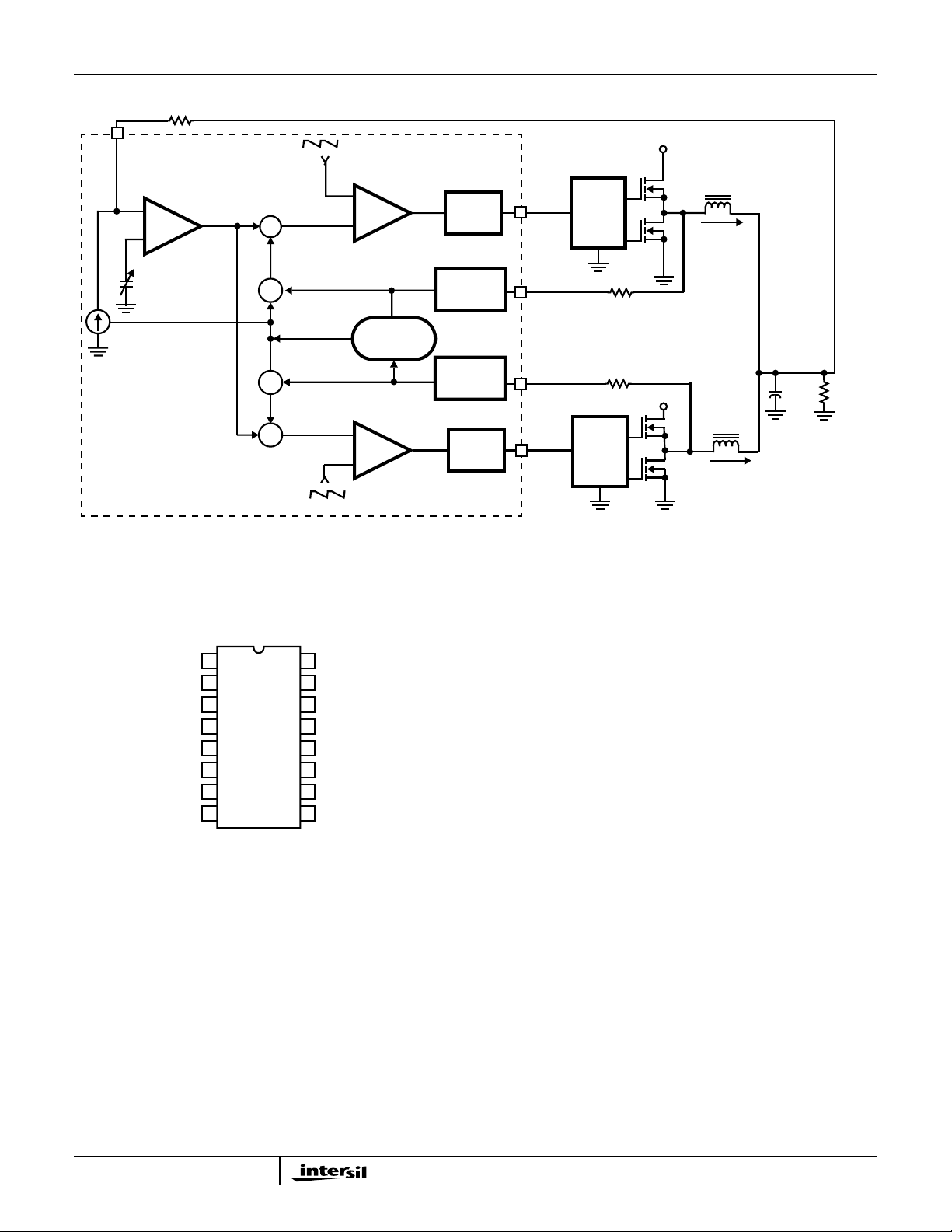

3

R

IN

FB

ERROR

AMPLIFIER

-

+

PROGRAMMABLE

REFERENCE

DAC

CORRECTION

∑

+

-

∑

-

I AVERAGE

-

∑

-

+

∑

CORRECTION

HIP6304

V

Q2

Q4

IN

L

Q1

V

IN

Q3

PHASE

PHASE

01

I

L1

V

CORE

C

L

02

I

L2

OUT

R

LOAD

HIP6304

COMPARATOR

-

+

+

CURRENT

AVERAGING

+

COMPARATOR

+

-

PWM

CIRCUIT

CURRENT

SENSING

CURRENT

SENSING

PWM

CIRCUIT

PWM1

I

SEN1

I

SEN2

PWM2

HIP6601

R

R

ISEN2

HIP6601

ISEN1

FIGURE 1. SIMPLIFIED BLOCK DIAGRAM OF THE HIP6304 VOLTAGE AND CURRENT CONTROL LOOPS FOR A TWO POWER

CHANNEL REGULATOR

Functional Pin Description

FS/DIS (Pin 8)

Channel frequency,FSW, select and disable. A resistor from

1

VID3

2

VID2

3

VID1

VID0

4

EN

5

COMP ISEN2

6

FB

7

FS/DIS

8

16

15

14

13

12

11

10

9

V

CC

PGOOD

ISEN1

PWM1

PWM2

VSEN

GND

this pin to ground sets the switching frequency of the

converter. Pulling this pin to ground disables the converter

and three states the PWM outputs. See Figure 10.

GND (Pin 9)

Bias and reference ground. All signals are referenced to this

pin.

VSEN (Pin 10)

Power good monitor input. Connect to the microprocessorCORE voltage.

VID3 (Pin 1), VID2 (Pin 2), VID1 (Pin 3) and VID0

(Pin 4)

V oltage Identification inputs from microprocessor. These pins

respond to TTL and 3.3V logic signals. The HIP6304 decodes

VID bits to establish the output voltage. See Table 1.

EN (Pin 5)

Enable pin normal operation is with input open or high. A low

input disables the regulator and three states the PWM outputs.

COMP (Pin 6)

Output of the internal error amplifier. Connect this pin to the

external feedback and compensation network.

FB (Pin 7)

Inverting input of the internal error amplifier.

ISEN2 (Pin 11) and ISEN1 (Pin 14)

Current sense inputs from the individual converter channel’s

phase nodes.

PWM2 (Pin 12) and PWM1 (Pin 13)

PWM outputs for each driven channel in use. Connect these

pins to the PWM input of a HIP6601/2/3 driver.

PGOOD (Pin 15)

Power good. This pin provides a logic-high signal when the

microprocessor CORE voltage (VSEN pin) is within specified

limits and Soft-Start has timed out.

VCC (Pin 16)

Bias supply. Connect this pin to a 5V supply.

4

HIP6304

Absolute Maximum Ratings

Supply Voltage, VCC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . +7V

Input, Output, or I/O Voltage . . . . . . . . . . GND -0.3V to VCC+ 0.3V

ESD Classification . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Class TBD

Recommended Operating Conditions

Supply Voltage. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . +5V ±5%

Ambient Temperature. . . . . . . . . . . . . . . . . . . . . . . . . . .0oC to 70oC

CAUTION: Stress above those listed in “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress only rating and operation of the

device at these or any other conditions above those indicated in the operational section of this specification is not implied.

NOTE:

1. θJA is measured with the component mounted on an evaluation PC board in free air.

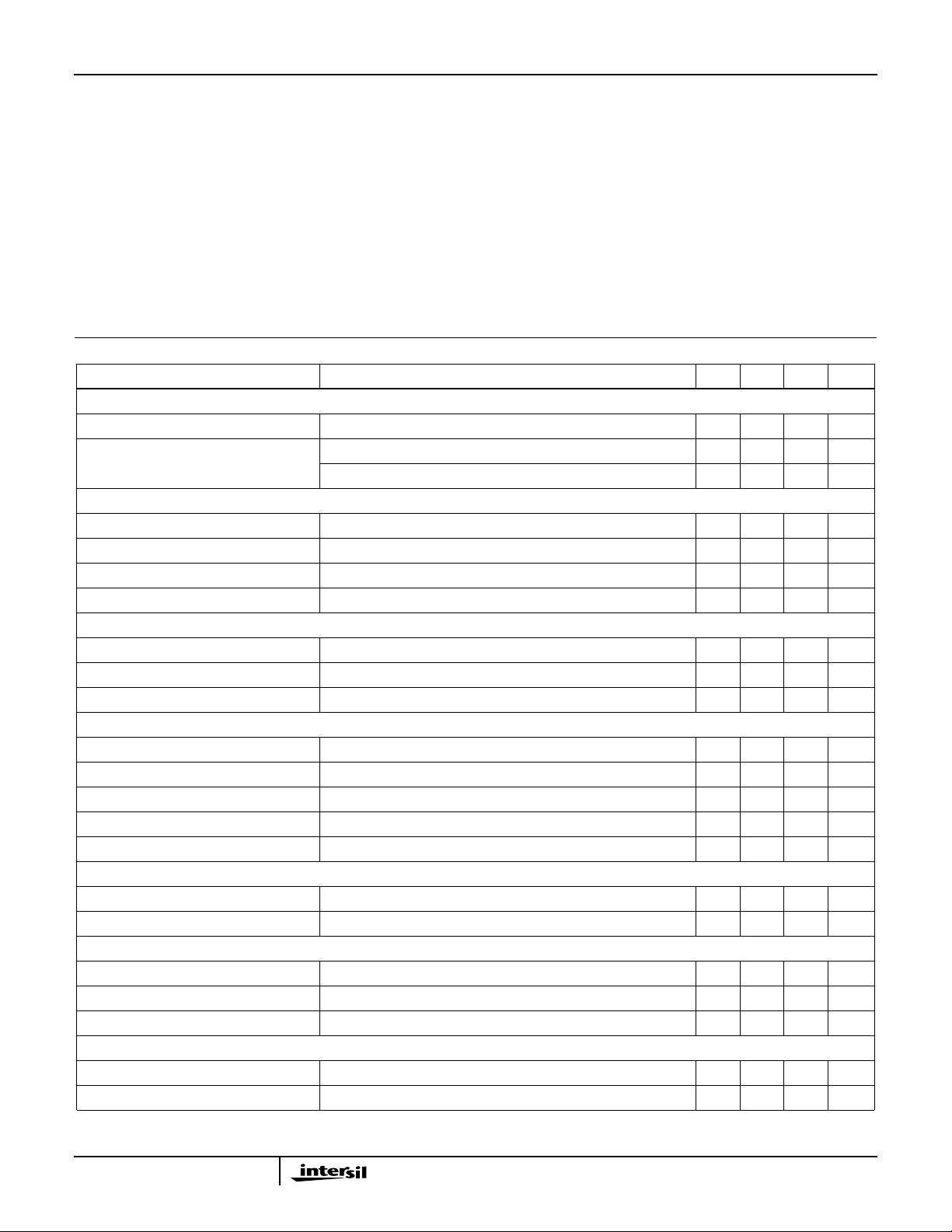

Electrical Specifications Operating Conditions: V

PARAMETER TEST CONDITIONS MIN TYP MAX UNITS

INPUT SUPPLY POWER

Input Supply Current RT= 100kΩ, Active and Disabled Maximum Limit - 10 15 mA

POR (Power-On Reset) Threshold VCC Rising 4.25 4.38 4.5 V

VCC Falling 3.75 3.88 4.00 V

REFERENCE AND DAC

System Accuracy Percent system deviation from programmed VID Codes -1 - 1 %

DAC (VID0 - VID3) Input Low Voltage DAC Programming Input Low Threshold Voltage - - 0.8 V

DAC (VID0 - VID3) Input High Voltage DAC Programming Input High Threshold Voltage 2.0 - - V

VID Pull-Up VIDx = 0V or VIDx = 3V 10 20 40 µA

CHANNEL GENERATOR

Frequency, F

Adjustment Range See Figure 10 0.05 - 1.5 MHz

Disable Voltage Maximum voltage at FS/DIS to disable controller. I

ERROR AMPLIFIER

DC Gain RL = 10K to Ground - 72 - dB

Gain-Bandwidth Product CL = 100pF, RL = 10K to Ground - 18 - MHz

Slew Rate CL = 100pF, Load = ±400µA - 5.3 - V/µs

Maximum Output Voltage RL = 10K to ground, Load = 400µA 3.6 4.1 - V

Minimum Output Voltage RL = 10K to ground, Load = -400µA - 0.16 0.5 V

I

SEN

Full Scale Input Current -50-µA

Over-Current Trip Level - 82.5 - µA

POWER GOOD MONITOR

Under-Voltage Threshold VSEN Rising - 0.92 - V

Under-Voltage Threshold VSEN Falling - 0.90 - V

PGOOD Low Output Voltage I

PROTECTION

Over-Voltage Threshold VSEN Rising 1.12 1.15 1.2 V

Percent Over-Voltage Hysteresis VSEN Falling after Over-Voltage - 2 - %

SW

RT = 100kΩ,±1% 245 275 305 kHz

= 4mA - 0.18 0.4 V

PGOOD

= 5V, TA = 0oC to 70oC, Unless Otherwise Specified

CC

Thermal Information

Thermal Resistance (Typical, Note 1) θJA (oC/W)

SOIC Package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 106

Maximum Junction Temperature . . . . . . . . . . . . . . . . . . . . . . .150oC

Maximum Storage Temperature Range. . . . . . . . . . -65oC to 150oC

Maximum Lead Temperature (Soldering 10s) . . . . . . . . . . . . .300oC

(SOIC - Lead Tips Only)

= 1mA. - - 1.0 V

FS/DIS

DAC

DAC

DAC

5

Loading...

Loading...