Intersil Corporation HIP6020 Datasheet

HIP6020

Data Sheet February 1999 File Number

Advanced Dual PWM and Dual Linear

Power Controller

The HIP6020 provides the power control and protection for

four output voltages in high-performance, graphics intensive

microprocessor and computer applications. The IC

integrates twoPWMcontrollersand two linear controllers, as

well as the monitoring and protection functions into a 28-pin

SOIC package. One PWM controller regulates the

microprocessor core voltage with a synchronous-rectified

buck converter. The second PWM controller supplies the

computer system’s AGP 1.5V or 3.3V bus power with a

standard buck converter. The linear controllers regulate

power for the 1.5V GTL bus and the 1.8V power for the

North/South Bridge core voltage and/or cache memory

circuits.

The HIP6020 includes an Intel-compatible, TTL 5-input

digital-to-analog converter (DAC)that adjusts the core PWM

output voltage from 1.3V

from 2.1V

to 3.5VDC in 0.1V increments. The precision

DC

reference and voltage-mode control provide±1% static

regulation. The second PWM controller’s output is userselectable, through a TTL-compatible signal applied at the

SELECT pin, for levels of 1.5V or 3.3V with ±3% accuracy.

The linear regulators use external N-Channel MOSFETs or

bipolar NPN pass transistors to provide fixed output voltages

of 1.5V ±3% (V

OUT3

The HIP6020 monitors all the output voltages. A single

Power Good signal is issued when the core is within ±10% of

the DAC setting and all other outputs are above their undervoltage levels. Additional built-in over-voltage protection for

the core output uses the lower MOSFET to prevent output

voltages above 115% of the DAC setting. The PWM

controllers’ over-current function monitors the output current

by using the voltage drop across the upper MOSFET’s

r

, eliminating the need for a current sensing resistor.

DS(ON)

to 2.05VDC in 0.05V steps and

DC

) and 1.8V ±3% (V

OUT4

).

4683

Features

• Provides 4 Regulated Voltages

- Microprocessor Core, AGP Bus, North/South Bridge

and/or Cache Memory, and GTL Bus Power

• Drives N-Channel MOSFETs

• Linear Regulator Drives Compatible with both MOSFET

and Bipolar Series Pass Transistors

• Simple Single-Loop Control Designs

- Voltage-Mode PWM Control

• Fast PWM Converter Transient Response

- High-Bandwidth Error Amplifiers

- Full 0% to 100% Duty Ratios

• Excellent Output Voltage Regulation

- Core PWM Output: ±1% Over Temperature

- AGP Bus PWM Output: ±3% Over Temperature

- Other Outputs: ±3% Over Temperature

• TTL-Compatible 5 Bit DAC Microprocessor Core Output

Voltage Selection

- Wide Range . . . . . . . . . . . . . . . . . . . 1.3V

DC

to 3.5V

• Power-Good Output Voltage Monitor

• Over-Voltage and Over-Current Fault Monitors

- Switching Regulators Do Not Require Extra Current

Sensing Elements, Use MOSFET’s r

DS(ON)

• Small Converter Size

- Constant Frequency Operation

- 200kHz Free-Running Oscillator; Programmable From

50kHz to Over 1MHz

- Small External Component Count

Applications

•

Motherboard Power Regulation for Computers

Pinout

HIP6020 (SOIC)

TOP VIEW

DC

Ordering Information

TEMP.

PART NUMBER

HIP6020CB 0 to 70 28 Ld SOIC M28.3

HIP6020EVAL1 Evaluation Board

RANGE (oC) PACKAGE

2-281

PKG.

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

NO.

UGATE2

PHASE2

PGOOD

OCSET2

SELECT

FAULT/RT

http://www.intersil.com or 407-727-9207

VID4

VID3

VID2

VID1

VID0

VSEN2

SS

VSEN4

1

2

3

4

5

6

7

8

9

10

11

12

13

14

28

VCC

UGATE1

27

PHASE1

26

25

LGATE1

24

PGND

23

OCSET1

VSEN1

22

21

FB1

20

COMP1

VSEN3

19

18

DRIVE3

GND

17

VAUX

16

DRIVE4

15

| Copyright © Intersil Corporation 1999

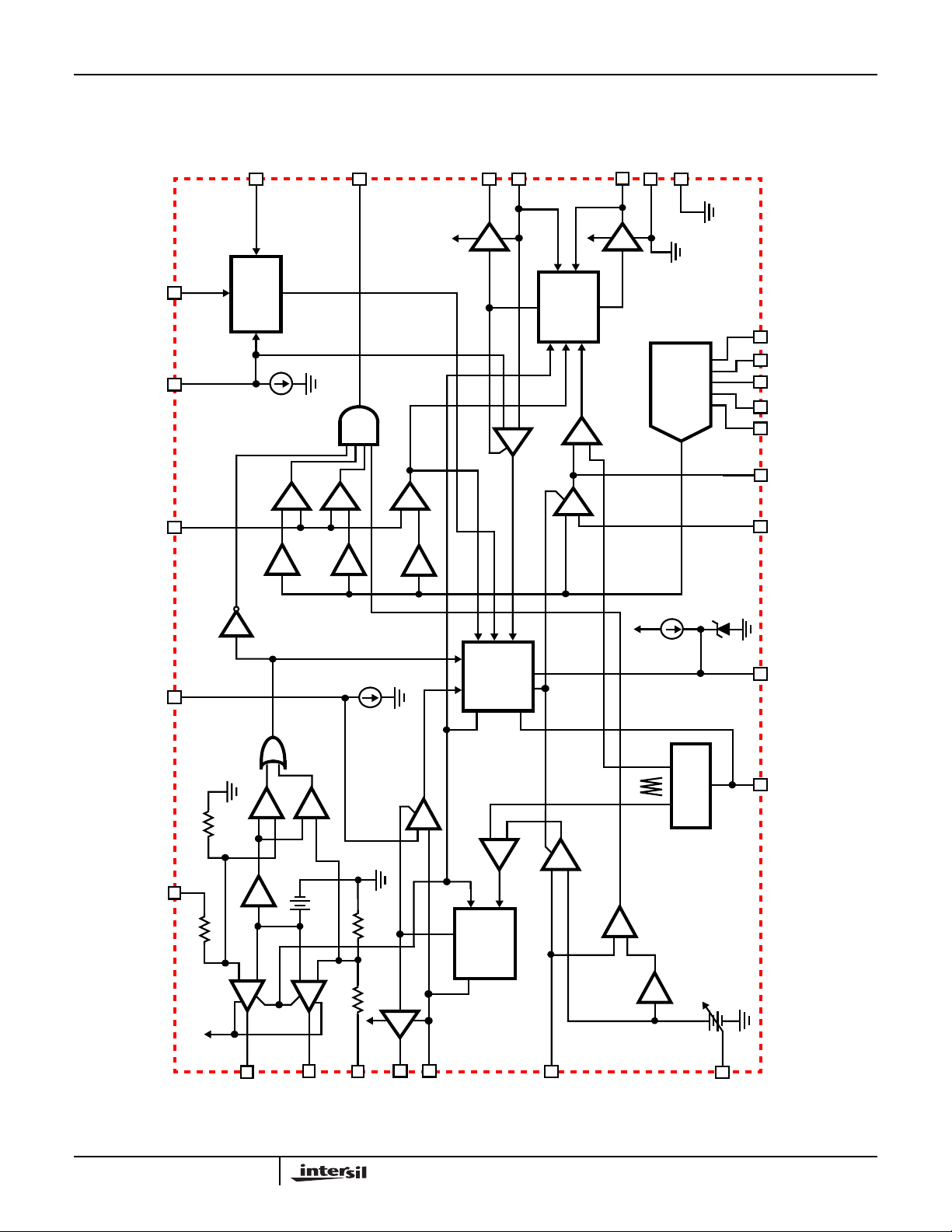

Block Diagram

HIP6020

VCC

OCSET1

VSEN1

OCSET2

VSEN3

VAUX

POWER-ON

RESET (POR)

200µA

1.10

x

LUV

-

+

0.75

x

-

+

LINEAR

-

+

UNDER-

VOLTAGE

-

+

1.26V

+

PGOOD

-

0.90

x

UGATE1

PHASE1

VCC

DRIVE1

-

+

OC1

-

+

1.15

x

OV

SOFT-

LOGIC

START

& FAULT

200µA

OC2

-

+

INHIBIT

INHIBIT

PWM

COMP2

-

FAULT

+

PWM2

VCC

GATE

CONTROL

PWM1

PWM

-

+

-

+

AMP1

ERROR

AMP2

ERROR

-

+

LGATE1

COMP1

+

-

PGND

DRIVE

SYNCH

VCC

TTL D/A

CONVERTER

DACOUT

28µA

OSCILLATOR

VID4

VID3

(DAC)

4.5V

VID2

VID1

VID0

COMP1

FB1

SS

FAULT / RT

GND

GATE

CONTROL

-

+

VAUX

DRIVE3

-

+

DRIVE4

VCC

VSEN4

DRIVE2

UGATE2

PHASE2

VSEN2

0.75

x

1.5V

+

or

3.3V

-

SELECT

2-282

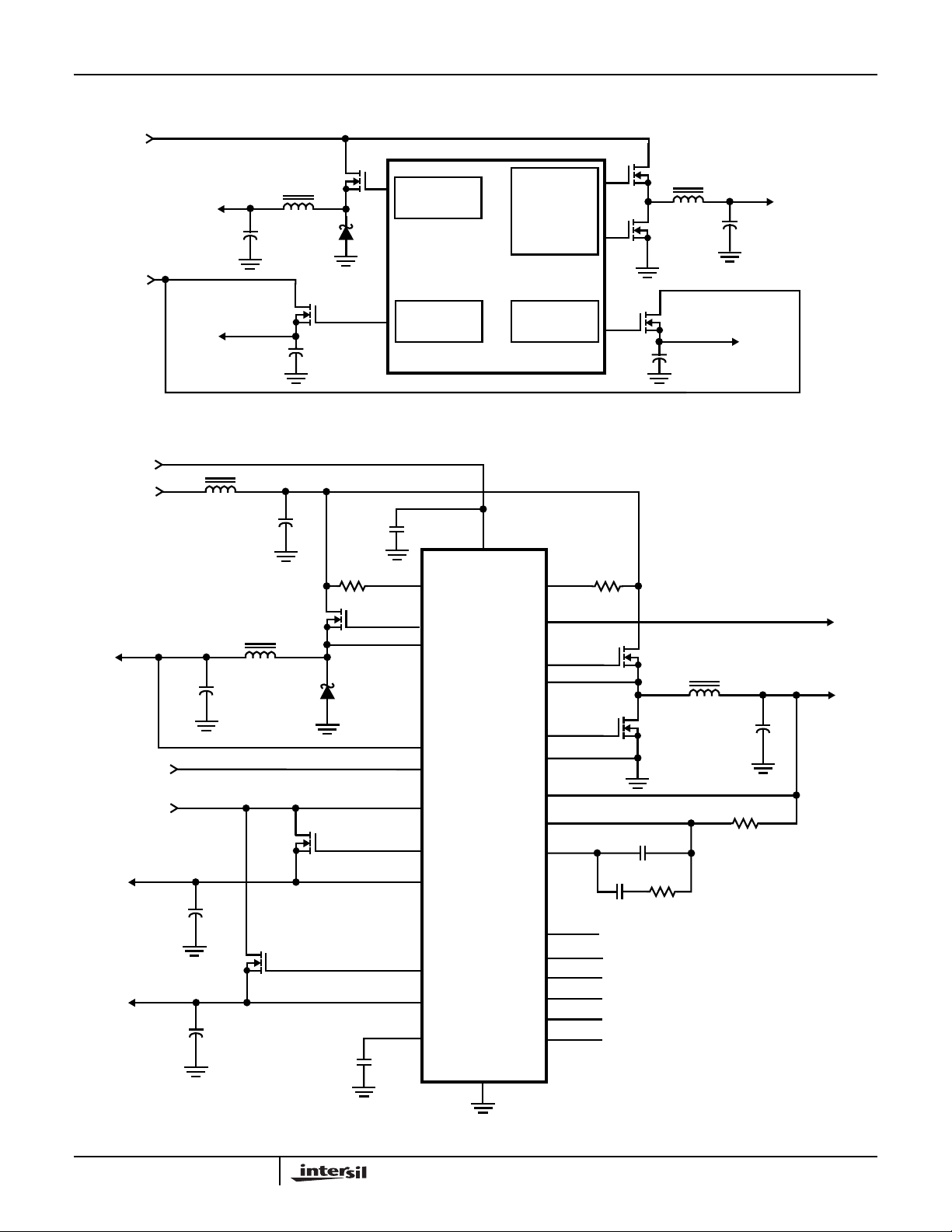

Simplified Power System Diagram

+5V

IN

HIP6020

V

OUT2

+3.3V

IN

V

OUT3

Typical Application

+12V

IN

+5V

IN

V

OUT2

1.5V OR 3.3V

L

IN

C

OUT2

L

OUT2

Q3

PWM2

CONTROLLER

PWM1

CONTROLLER

Q1

Q2

V

OUT1

HIP6020

Q4

C

IN

Q3

PHASE2

CR2

CONTROLLER

OCSET2

UGATE2

LINEAR

CONTROLLER

VCC

LINEAR

OCSET1

PGOOD

UGATE1

PHASE1

Q1

Q5

L

OUT1

V

OUT4

POWERGOOD

V

OUT1

1.3V TO 3.5V

TYPEDET

+3.3V

V

OUT3

1.5V

C

V

OUT4

1.8V

C

IN

OUT3

OUT4

Q5

2-283

Q4

VSEN2

SELECT

VAUX

HIP6020

DRIVE3

VSEN3

DRIVE4

VSEN4

SS

C

SS

GND

LGATE1

PGND

VSEN1

FB1

COMP1

FAULT / RT

VID0

VID1

VID2

VID3

VID4

Q2

C

OUT1

HIP6020

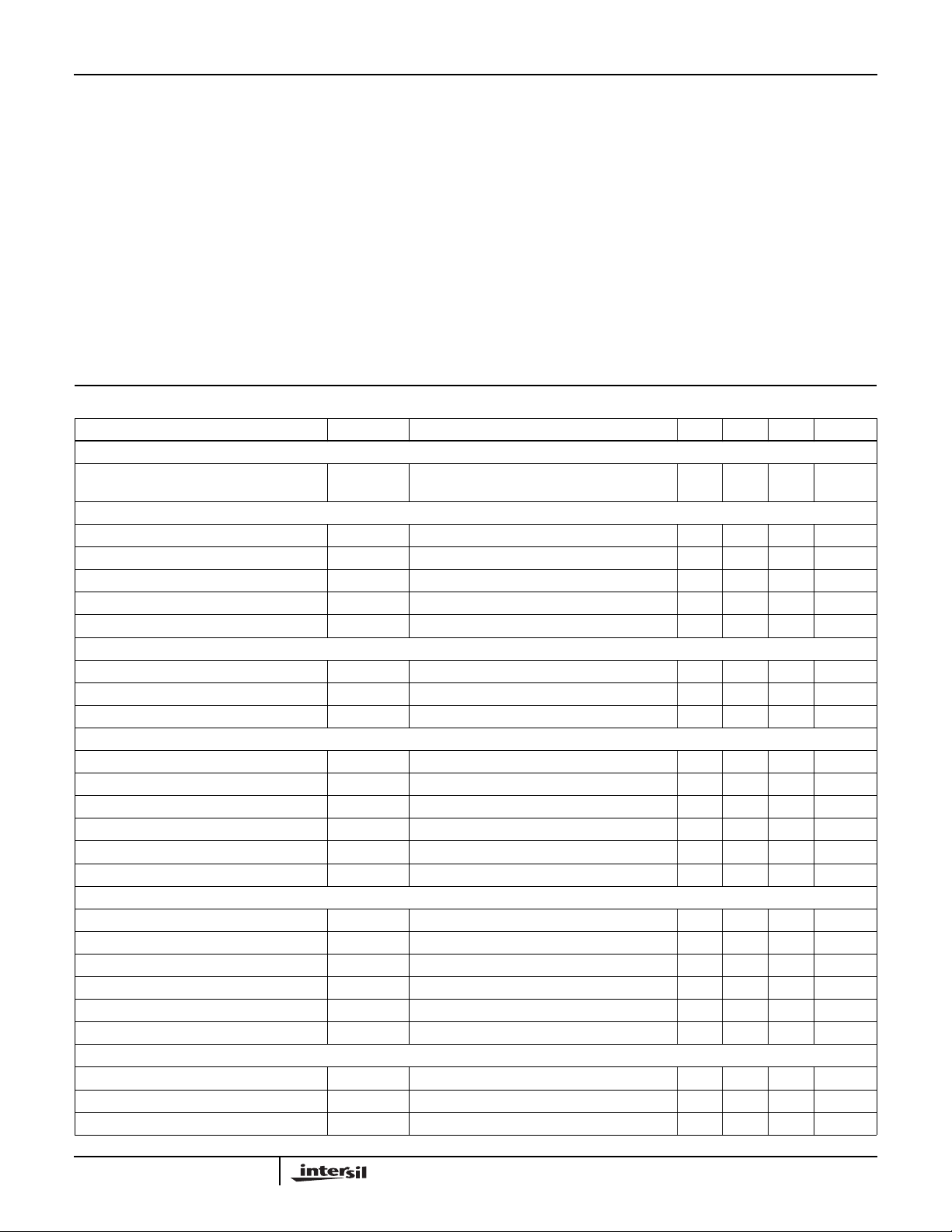

Absolute Maximum Ratings Thermal Information

Supply Voltage, VCC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . +15V

PGOOD, RT/FAULT, DRIVE, PHASE, and

GATE Voltage. . . . . . . . . . . . . . . . . . . GND - 0.3V to VCC + 0.3V

Input, Output or I/O Voltage. . . . . . . . . . . . . . . . . . GND -0.3V to 7V

ESD Classification . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Class 1

Operating Conditions

Supply Voltage, VCC . . . . . . . . . . . . . . . . . . . . . . . . . . . +12V ±10%

Ambient Temperature Range. . . . . . . . . . . . . . . . . . . . 0oC to 70oC

Junction Temperature Range. . . . . . . . . . . . . . . . . . . 0oC to 125oC

CAUTION: Stresses above those listed in “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress only rating and operationofthe

device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

NOTE:

1. θJA is measured with the component mounted on an evaluation PC board in free air.

Electrical Specifications Recommended Operating Conditions, Unless Otherwise Noted. Refer to Figures 1, 2 and 3

PARAMETER SYMBOL TEST CONDITIONS MIN TYP MAX UNITS

VCC SUPPLY CURRENT

Nominal Supply Current I

CC

POWER-ON RESET

Rising VCC Threshold V

Falling VCC Threshold V

Rising VAUX Threshold V

VAUX Threshold Hysteresis V

Rising V

Threshold - 1.26 - V

OCSET1

OSCILLATOR

Free Running Frequency F

OSC

Total Variation 6kΩ < RT to GND < 200kΩ -15 - +15 %

Ramp Amplitude ∆V

OSC

DAC AND STANDARD BUCK REGULATOR REFERENCE

DAC(VID0-VID4) Input Low Voltage - - 0.8 V

DAC(VID0-VID4) Input High Voltage 2.0 - V

DACOUT Voltage Accuracy -1.0 - +1.0 %

PWM2 Reference Voltage SELECT < 0.8V - 1.5 - V

PWM2 Reference Voltage SELECT > 2.0V - 3.3 - V

PWM2 Reference Voltage Tolerance -3- %

1.5V AND 1.8V LINEAR REGULATORS (V

OUT3

AND V

Regulation -3- %

VSEN3 Regulation Voltage VREG

VSEN4 Regulation Voltage VREG

VSEN3,4 Under-Voltage Level VSEN3

VSEN3,4 Under-Voltage Hysteresis VSEN3 Falling - 7 - %

Output Drive Current VAUX-V

SYNCHRONOUS PWM CONTROLLER ERROR AMPLIFIER

DC Gain -88- dB

Gain-Bandwidth Product GBWP - 15 - MHz

Slew Rate SR COMP1 = 10pF - 6 - V/µs

UGATE1, LGATE1, UGATE2, DRIVE3, and

DRIVE4 Open

OCSET

OCSET

OCSET

OCSET

RT = OPEN 185 200 215 kHz

RT = Open - 1.9 - V

)

OUT4

3

4

VSEN3 Rising - 75 - %

UV

Thermal Resistance (Typical, Note 1) θJA (oC/W)

SOIC Package. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

Maximum Junction Temperature (Plastic Package) . . . . . . . .150oC

Maximum Storage Temperature Range. . . . . . . . . . -65oC to 150oC

Maximum Lead Temperature (Soldering 10s) . . . . . . . . . . . . .300oC

(SOIC - Lead Tips Only)

-9- mA

= 4.5V - - 10.4 V

= 4.5V 8.2 - - V

= 4.5V - 2.5 - V

= 4.5V - 0.5 - V

- 1.5 - V

- 1.8 - V

> 0.6V 20 40 - mA

DRIVE

P-P

2-284

HIP6020

Electrical Specifications Recommended Operating Conditions, Unless Otherwise Noted. Refer to Figures 1, 2 and 3 (Continued)

PARAMETER SYMBOL TEST CONDITIONS MIN TYP MAX UNITS

PWM CONTROLLERS GATE DRIVERS

UGATE1,2 Source I

UGATE1,2 Sink R

LGATE Source I

LGATE Sink R

UGATE

UGATEVGATE-PHASE

LGATE

LGATEVLGATE

VCC = 12V, V

VCC = 12V, V

= 1V - 1.4 3.0 Ω

PROTECTION

VSEN1 Over-Voltage (VSEN1/DACOUT) VSEN1 Rising - 115 120 %

FAULT Sourcing Current I

OCSET1,2 Current Source I

Soft-Start Current I

OVP

OCSET

SS

V

FAULT/RT

V

OCSET

= 2.0V - 8.5 - mA

= 4.5V

POWER GOOD

VSEN1 Upper Threshold

VSEN1 Rising 108 - 110 %

(VSEN1/DACOUT)

VSEN1 Under-Voltage

VSEN1 Rising 92 - 94 %

(VSEN1/DACOUT)

VSEN1 Hysteresis (VSEN1/DACOUT) Upper/Lower Threshold - 2 - %

PGOOD Voltage Low V

PGOODIPGOOD

= -4mA - - 0.8 V

UGATE1

(or V

) = 6V - 1 - A

UGATE2

= 1V - 1.7 3.5 Ω

= 1V - 1 - A

LGATE1

DC

170 200 230 µA

-28- µA

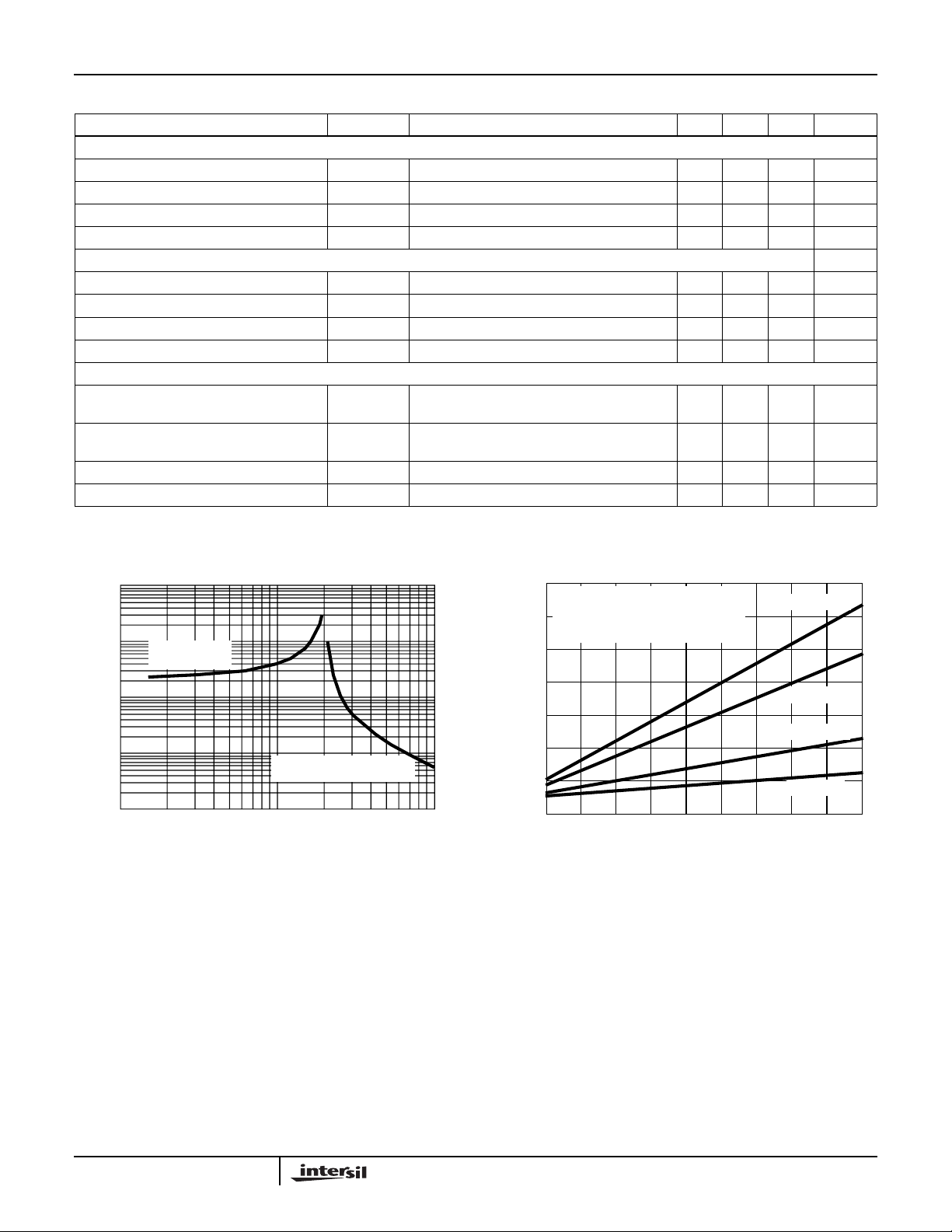

Typical Performance Curves

1000

100

RESISTANCE (kΩ)

10

RT PULLUP

TO +12V

RT PULLDOWN TO V

10 100 1000

SWITCHING FREQUENCY (kHz)

SS

FIGURE 1. RT RESISTANCE vs FREQUENCY FIGURE 2. BIAS SUPPLY CURRENT vs FREQUENCY

Functional Pin Descriptions

VCC (Pin 28)

Provide a 12V bias supply for the IC to this pin. This pin also

provides the gate bias charge for all the MOSFETs

controlled by the IC. The voltage at this pin is monitored for

Power-On Reset (POR) purposes.

GND (Pin 17)

Signal ground for the IC. All voltagelevels are measured with

respect to this pin.

140

C

VIN = 5V

120

V

100

80

(mA)

CC

60

I

40

20

0

100 200 300 400 500 600 700 800 900 1000

UGATE1

= 12V

CC

= C

= C

UGATE2

SWITCHING FREQUENCY (kHz)

LGATE1

= C

C = 4800pF

C = 3600pF

C = 1500pF

C = 660pF

PGND (Pin 24)

This is the power ground connection. Tie the synchronous

PWM converter’s lower MOSFET source to this pin.

VAUX (Pin 16)

The +3.3V input voltage at this pin is monitored for power-on

reset (POR) purposes. Connected to +5V input, this pin

provides boost current for the two linear regulator output

drives in the event bipolar NPN transistors (instead of

N-channel MOSFETs) are employed as pass elements.

2-285

Loading...

Loading...